### 88E1111 Product Brief

**Integrated 10/100/1000 Ultra Gigabit Ethernet Transceiver**

Doc. No. MV-S105540-00, Rev. --

March 4, 2009

Document Classification: Proprietary Information

| Docume                                                                                                                                                                                                                         | Document Conventions                                                                                                                                                                      |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                                                                                                                                                                                                                | Note: Provides related information or information of special importance.                                                                                                                  |  |  |  |  |  |  |

| !                                                                                                                                                                                                                              | Caution: Indicates potential damage to hardware or software, or loss of data.                                                                                                             |  |  |  |  |  |  |

| Ļ                                                                                                                                                                                                                              | Warning: Indicates a risk of personal injury.                                                                                                                                             |  |  |  |  |  |  |

| Docume                                                                                                                                                                                                                         | nt Status                                                                                                                                                                                 |  |  |  |  |  |  |

| Advance<br>Information                                                                                                                                                                                                         | This document contains design specifications for initial product development. Specifications may change without notice. Contact Marvell Field Application Engineers for more information. |  |  |  |  |  |  |

| Preliminary Information This document contains preliminary data, and a revision of this document will be published date. Specifications may change without notice. Contact Marvell Field Application Enginee more information. |                                                                                                                                                                                           |  |  |  |  |  |  |

| Final This document contains specifications on a product that is in final release. Specifications may change without notice. Contact Marvell Field Application Engineers for more information.                                 |                                                                                                                                                                                           |  |  |  |  |  |  |

| Doc Status: Advance Technical Publications: 1.00                                                                                                                                                                               |                                                                                                                                                                                           |  |  |  |  |  |  |

For more information, visit our website at: www.marvell.com

#### Disclaimer

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express written permission of Marvell. Marvell retains the right to make changes to this document at any time, without notice. Marvell makes no warranty of any kind, expressed or implied, with regard to any information contained in this document, including, but not limited to, the implied warranties of merchantability or fitness for any particular purpose. Further, Marvell does not warrant the accuracy or completeness of the information, text, graphics, or other items contained within this document. Marvell products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not use Marvell products in these types of equipment or applications.

With respect to the products described herein, the user or recipient, in the absence of appropriate U.S. government authorization, agrees.

- 1) Not to re-export or release any such information consisting of technology, software or source code controlled for national security reasons by the U.S. Export Control Regulations ("EAR"), to a national of EAR Country Groups D:1 or E:2;

- 2) Not to export the direct product of such technology or such software, to EAR Country Groups D:1 or E:2, if such technology or software and direct products thereof are controlled for national security reasons by the EAR; and,

- 3) In the case of technology controlled for national security reasons under the EAR where the direct product of the technology is a complete plant or component of a plant, not to export to EAR Country Groups D:1 or E:2 the direct product of the plant or major component thereof, if such direct product is controlled for national security reasons by the EAR, or is subject to controls under the U.S. Munitions List ("USML").

At all times hereunder, the recipient of any such information agrees that they shall be deemed to have manually signed this document in connection with their receipt of any such information

Copyright © 2009. Marvell International Ltd. All rights reserved. Marvell, the Marvell logo, Moving Forward Faster, Alaska, Fastwriter, Datacom Systems on Silicon, Libertas, Link Street, NetGX, PHAdvantage, Prestera, Raising The Technology Bar, The Technology Within, Virtual Cable Tester, and Yukon are registered trademarks of Marvell. Ants, AnyVoltage, Discovery, DSP Switcher, Feroceon, GalNet, GalTis, Horizon, Marvell Makes It All Possible, RADLAN, UniMAC, and VCT are trademarks of Marvell. All other trademarks are the property of their respective owners.

Doc. No. MV-S105540-00 Rev. --Copyright © 2009 Marvell

#### **OVERVIEW**

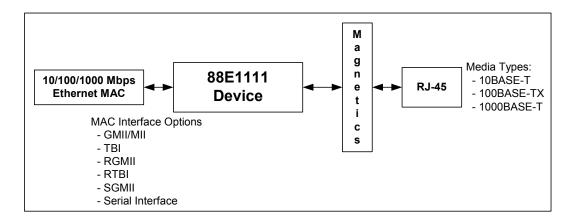

The Alaska<sup>®</sup> Ultra 88E1111 Gigabit Ethernet Transceiver is a physical layer device for Ethernet 1000BASE-T, 100BASE-TX, and 10BASE-T applications. It is manufactured using standard digital CMOS process and contains all the active circuitry required to implement the physical layer functions to transmit and receive data on standard CAT 5 unshielded twisted pair.

The 88E1111 device incorporates the Marvell Virtual Cable Tester<sup>®</sup> (VCT™) feature, which uses Time Domain Reflectometry (TDR) technology for the remote identification of potential cable malfunctions, thus reducing equipment returns and service calls. Using VCT, the Alaska 88E1111 device detects and reports potential cabling issues such as pair swaps, pair polarity and excessive pair skew. The device will also detect cable opens, shorts or any impedance mismatch in the cable and report accurately within one meter the distance to the fault.

The 88E1111 device supports the Gigabit Media Independent Interface (GMII), Reduced GMII (RGMII), Serial Gigabit Media Independent Interface (SGMII), the Ten-Bit Interface (TBI), and Reduced TBI (RTBI) for direct connection to a MAC/Switch port.

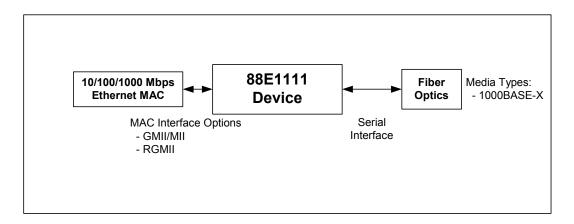

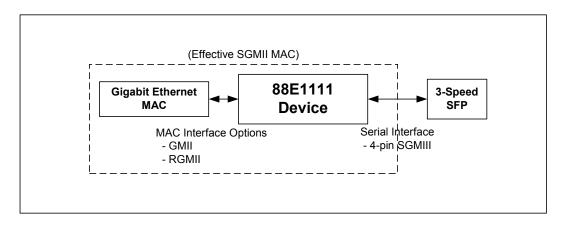

The 88E1111 device incorporates an optional 1.25 GHz SERDES (Serializer/Deserializer). The serial interface may be connected directly to a fiber-optic transceiver for 1000BASE-T/1000BASE-X media conversion applications. Additionally, the 88E1111 device may be used to implement 1000BASE-T Gigabit Interface Converter (GBIC) or Small Form Factor Pluggable (SFP) modules.

The 88E1111 device uses advanced mixed-signal processing to perform equalization, echo and crosstalk cancellation, data recovery, and error correction at a gigabit per second data rate. The device achieves robust performance in noisy environments with very low power dissipation.

The 88E1111 device is offered in three different package options including a 117-Pin TFBGA, a 96-pin BCC featuring a body size of only 9 x 9 mm, and a 128 PQFP package.

#### **FEATURES**

- 10/100/1000BASE-T IEEE 802.3 compliant

- Supports GMII, TBI, reduced pin count GMII (RGMII), reduced pin count TBI (RTBI), and serial GMII (SGMII) interfaces

- Integrated 1.25 GHz SERDES for 1000BASE-X fiber applications

- Four RGMII timing modes

- Energy Detect and Energy Detect+ low power modes

- Three loopback modes for diagnostics

- "Downshift" mode for two-pair cable installations

- Fully integrated digital adaptive equalizers, echo cancellers, and crosstalk cancellers

- Advanced digital baseline wander correction

- Automatic MDI/MDIX crossover at all speeds of operation

- Automatic polarity correction

- IEEE 802.3u compliant Auto-Negotiation

- Software programmable LED modes including LED testing

- Automatic detection of fiber or copper operation

- Supports IEEE 1149.1 JTAG

- Two-Wire Serial Interface (TWSI) and MDC/MDIO

- CRC checker, packet counter

- Packet generation

- Virtual Cable Tester (VCT)

- Auto-Calibration for MAC Interface outputs

- Requires only two supplies: 2.5V and 1.0V (with 1.2V option for the 1.0V supply)

- I/Os are 3.3V tolerant

- Low power dissipation Pave = 0.75W

- 117-Pin TFBGA, 96-Pin BCC, and 128 PQFP package options

- 117-Pin TFBGA and 96-Pin BCC packages available in Commercial or Industrial grade

- RoHS 6/6 compliant packages available

88E1111 Device used in Copper Application

88E1111 Device used in Fiber Application

#### 88E1111 RGMII/GMII MAC to SGMII MAC Conversion

Doc. No. MV-S105540-00, Rev. --

### **Table of Contents**

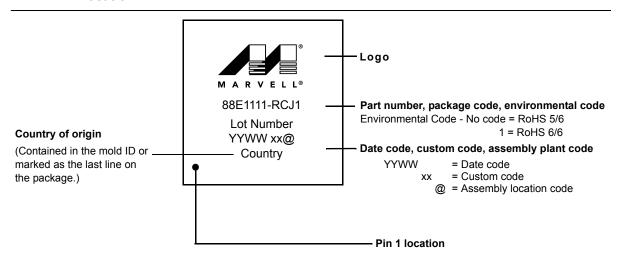

| 1.2       96-Pin BCC Package       .7         1.3       128-Pin PQFP Package       .8         1.4       Pin Description       .9         1.4.1       Pin Type Definitions       .9         1.5       I/O State at Various Test or Reset Modes       .33         1.6       117-Pin TFBGA Pin Assignment List - Alphabetical by Signal Name       .34         1.7       96-Pin BCC Pin Assignment List - Alphabetical by Signal Name       .36         1.8       128-Pin PQFP Pin Assignment List - Alphabetical by Signal Name       .38         2.1       117-pin TFBGA Package       .40         2.2       96-pin BCC Package - Top View       .42         2.3       96-Pin BCC Package - Bottom View       .43         2.4       128-Pin PQFP Package       .44         3.1       Cordering Part Numbers and Package Markings       .45         3.1.1       RoHS 5/6 Compliant Marking Examples       .46         3.1.2       RoHS 6/6 Compliant Marking Examples       .49 | 1.1 | 117-Pin TFBGA Package                                           | 6  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------|----|

| 1.4       Pin Description       9         1.4.1       Pin Type Definitions       9         1.5       I/O State at Various Test or Reset Modes       33         1.6       117-Pin TFBGA Pin Assignment List - Alphabetical by Signal Name       34         1.7       96-Pin BCC Pin Assignment List - Alphabetical by Signal Name       36         1.8       128-Pin PQFP Pin Assignment List - Alphabetical by Signal Name       38         2.1       117-pin TFBGA Package       40         2.2       96-pin BCC Package - Top View       42         2.3       96-Pin BCC Package - Bottom View       43         2.4       128-Pin PQFP Package       44         3.1       Ordering Part Numbers and Package Markings       45         3.1.1       RoHS 5/6 Compliant Marking Examples       46                                                                                                                                                                              | 1.2 | 96-Pin BCC Package                                              | 7  |

| 1.4.1 Pin Type Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1.3 | 128-Pin PQFP Package                                            | 8  |

| 1.6       117-Pin TFBGA Pin Assignment List - Alphabetical by Signal Name       34         1.7       96-Pin BCC Pin Assignment List - Alphabetical by Signal Name       36         1.8       128-Pin PQFP Pin Assignment List - Alphabetical by Signal Name       38         2.1       117-pin TFBGA Package       40         2.2       96-pin BCC Package - Top View       42         2.3       96-Pin BCC Package - Bottom View       43         2.4       128-Pin PQFP Package       44         3.1       Ordering Part Numbers and Package Markings       45         3.1.1       RoHS 5/6 Compliant Marking Examples       46                                                                                                                                                                                                                                                                                                                                             | 1.4 |                                                                 |    |

| 1.7       96-Pin BCC Pin Assignment List - Alphabetical by Signal Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.5 | I/O State at Various Test or Reset Modes                        | 33 |

| 1.8       128-Pin PQFP Pin Assignment List - Alphabetical by Signal Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.6 | 117-Pin TFBGA Pin Assignment List - Alphabetical by Signal Name | 34 |

| 2.1       117-pin TFBGA Package       40         2.2       96-pin BCC Package - Top View       42         2.3       96-Pin BCC Package - Bottom View       43         2.4       128-Pin PQFP Package       44         3.1       Ordering Part Numbers and Package Markings       45         3.1.1       RoHS 5/6 Compliant Marking Examples       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.7 | 96-Pin BCC Pin Assignment List - Alphabetical by Signal Name    | 36 |

| 2.2       96-pin BCC Package - Top View       42         2.3       96-Pin BCC Package - Bottom View       43         2.4       128-Pin PQFP Package       44         3.1       Ordering Part Numbers and Package Markings       45         3.1.1       RoHS 5/6 Compliant Marking Examples       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1.8 | 128-Pin PQFP Pin Assignment List - Alphabetical by Signal Name  | 38 |

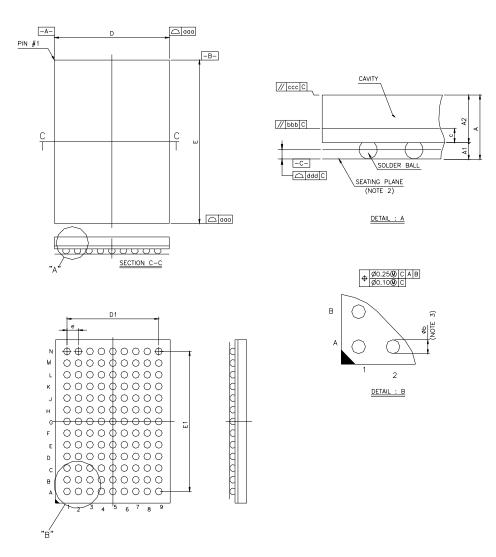

| 2.3       96-Pin BCC Package - Bottom View       43         2.4       128-Pin PQFP Package       44         3.1       Ordering Part Numbers and Package Markings       45         3.1.1       RoHS 5/6 Compliant Marking Examples       46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2.1 | 117-pin TFBGA Package                                           | 40 |

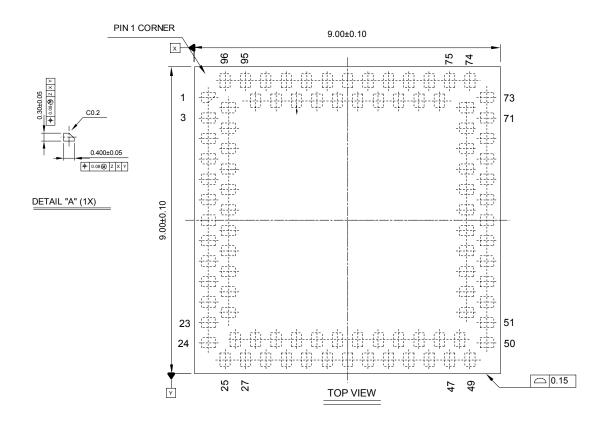

| 2.4 128-Pin PQFP Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.2 | 96-pin BCC Package - Top View                                   | 42 |

| 3.1 Ordering Part Numbers and Package Markings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.3 | 96-Pin BCC Package - Bottom View                                | 43 |

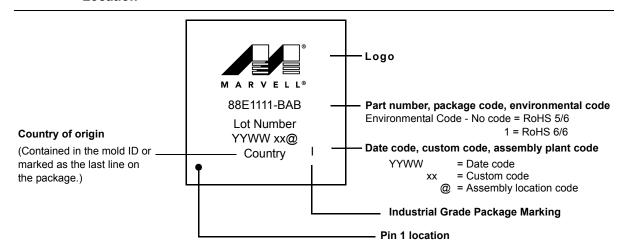

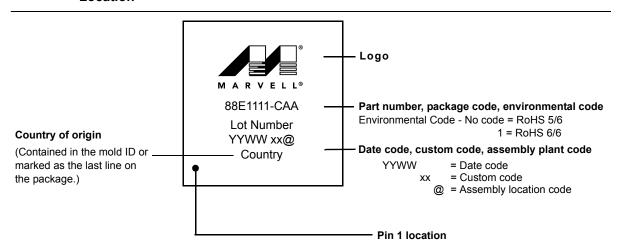

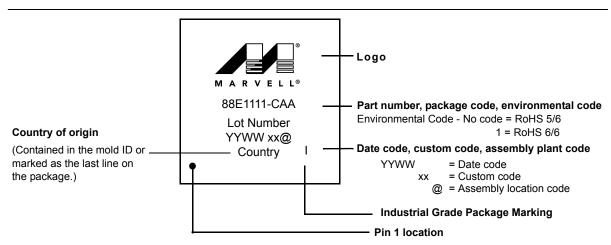

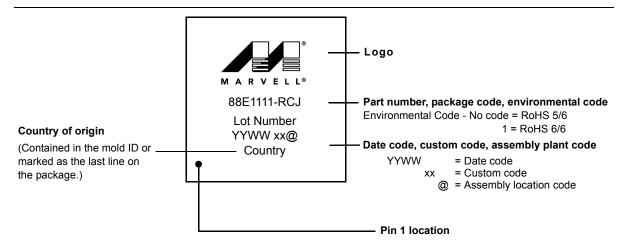

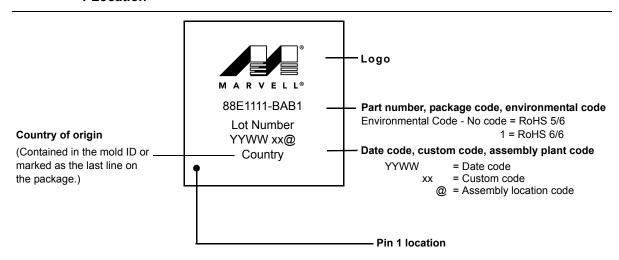

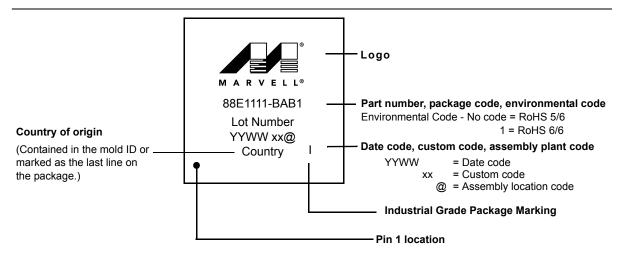

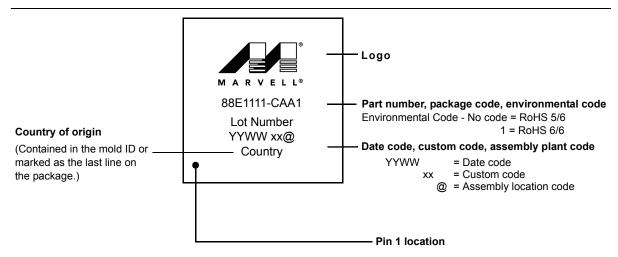

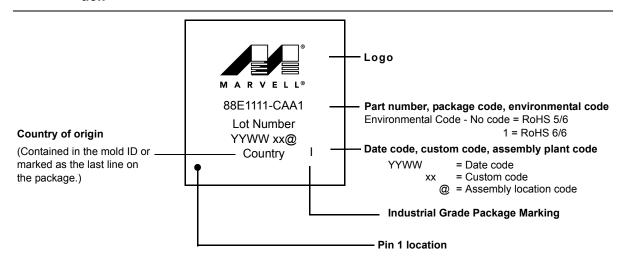

| 3.1.1 RoHS 5/6 Compliant Marking Examples46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2.4 | 128-Pin PQFP Package                                            | 44 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3.1 |                                                                 |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |                                                                 |    |

### **Section 1. Signal Description**

The 88E1111 device is a 10/100/1000BASE-T/1000BASE-X Gigabit Ethernet transceiver.

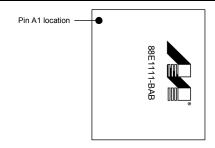

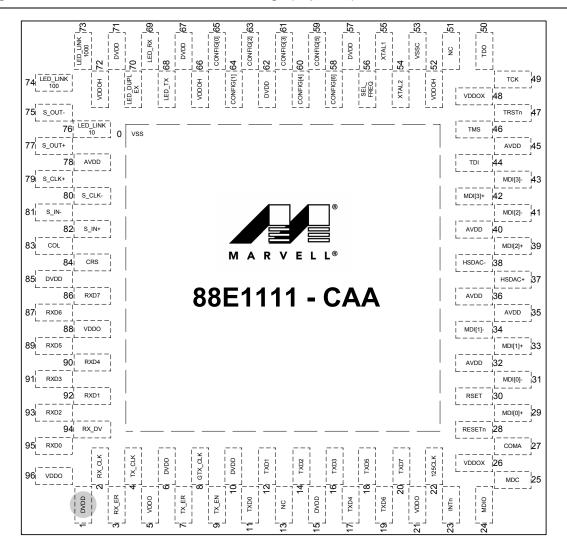

#### 1.1 117-Pin TFBGA Package

Figure 1: 88E1111 Device 117-Pin TFBGA Package (Top View)

|   | 1       | 2       | 3       | 4       | 5      | 6       | 7         | 8               | 9                |   |

|---|---------|---------|---------|---------|--------|---------|-----------|-----------------|------------------|---|

| Α | RXD5    | RXD6    | S_IN+   | S_IN-   | S_CLK+ | S_CLK-  | S_OUT+    | S_OUT-          | LED_<br>LINK1000 | А |

| В | RX_DV   | RXD0    | RXD3    | VDDO    | CRS    | COL     | AVDD      | LED_<br>LINK100 | VDDOH            | В |

| С | RX_CLK  | VDDO    | RXD2    | RXD4    | RXD7   | DVDD    | DVDD      | LED_<br>LINK10  | LED_RX           | С |

| D | TX_CLK  | RX_ER   | RXD1    | VSS     | VSS    | VSS     | DVDD      | CONFIG[0]       | LED_TX           | D |

| Е | TX_EN   | GTX_CLK | DVDD    | VSS     | VSS    | VSS     | DVDD      | LED_<br>DUPLEX  | CONFIG[1]        | E |

| F | TXD0    | TX_ER   | DVDD    | VSS     | VSS    | VSS     | VDDOH     | CONFIG[2]       | CONFIG[4]        | F |

| G | NC      | TXD1    | TXD2    | VSS     | VSS    | VSS     | CONFIG[3] | CONFIG[6]       | CONFIG[5]        | G |

| Н | TXD4    | TXD3    | TXD5    | VSS     | VSS    | VSS     | VSSC      | SEL_<br>FREQ    | XTAL1            | Н |

| J | TXD6    | TXD7    | DVDD    | VSS     | VSS    | VSS     | DVDD      | VDDOH           | XTAL2            | J |

| K | VDDO    | 125CLK  | RESETn  | VSS     | VSS    | VSS     | NC        | TDO             | VDDOX            | К |

| L | INTn    | VDDOX   | MDC     | COMA    | VSS    | VSS     | TDI       | TMS             | TCK              | L |

| М | MDIO    | RSET    | AVDD    | AVDD    | HSDAC+ | HSDAC-  | AVDD      | AVDD            | TRSTn            | М |

| N | MDI[0]+ | MDI[0]- | MDI[1]+ | MDI[1]- | AVDD   | MDI[2]+ | MDI[2]-   | MDI[3]+         | MDI[3]-          | N |

|   | 1       | 2       | 3       | 4       | 5      | 6       | 7         | 8               | 9                | 1 |

Figure 2: Pin A1 Location

Doc. No. MV-S105540-00, Rev. --

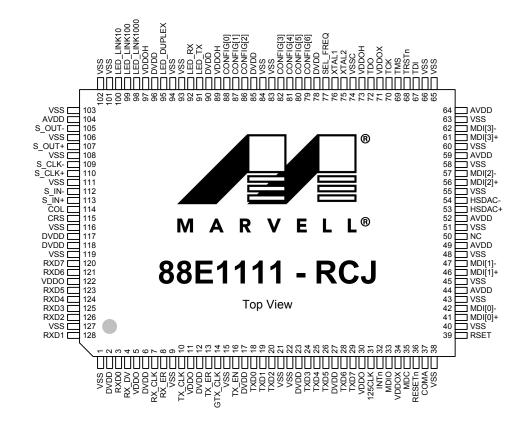

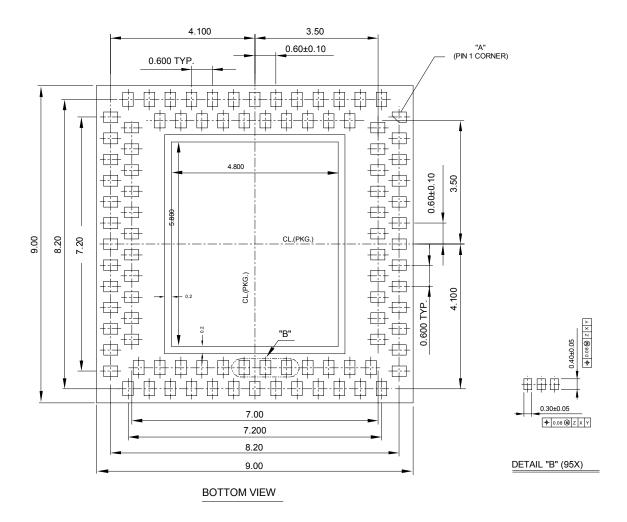

#### 1.2 96-Pin BCC Package

Figure 3: 88E1111 Device 96-Pin BCC Package (Top View)

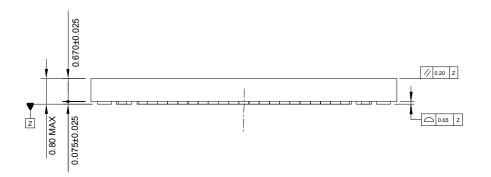

#### 1.3 128-Pin PQFP Package

Figure 4: 88E1111 Device 128-Pin PQFP Package (Top View)

### 1.4 Pin Description

#### 1.4.1 Pin Type Definitions

| Pin Type | Definition            |

|----------|-----------------------|

| Н        | Input with hysteresis |

| I/O      | Input and output      |

| 1        | Input only            |

| 0        | Output only           |

| PU       | Internal pull up      |

| PD       | Internal pull down    |

| D        | Open drain output     |

| Z        | Tri-state output      |

| mA       | DC sink capability    |

Table 1: Media Dependent Interface

| 117-TFBGA<br>Pin # | 96-BCC<br>Pin # | 128-PQFP<br>Pin # | Pin Name           | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                                                              |

|--------------------|-----------------|-------------------|--------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N1<br>N2           | 29<br>31        | 41<br>42          | MDI[0]+<br>MDI[0]- | I/O, D      | Media Dependent Interface[0].  In 1000BASE-T mode in MDI configuration, MDI[0]± correspond to BI_DA±.  In MDIX configuration, MDI[0]± correspond to BI_DB±.  In 100BASE-TX and 10BASE-T modes in MDI configuration, MDI[0]± are used for the transmit pair. In MDIX configuration, MDI[0]± are used for the receive pair.  MDI[0]± should be tied to ground if not used. |

| N3<br>N4           | 33<br>34        | 46<br>47          | MDI[1]+<br>MDI[1]- | I/O, D      | Media Dependent Interface[1].  In 1000BASE-T mode in MDI configuration, MDI[1]± correspond to BI_DB±.  In MDIX configuration, MDI[1]± correspond to BI_DA±.  In 100BASE-TX and 10BASE-T modes in MDI configuration, MDI[1]± are used for the receive pair. In MDIX configuration, MDI[1]± are used for the transmit pair.  MDI[1]± should be tied to ground if not used. |

Table 1: Media Dependent Interface (Continued)

| 117-TFBGA<br>Pin # | 96-BCC<br>Pin # | 128-PQFP<br>Pin # | Pin Name           | Pin<br>Type | Description                                                                                                                                                                                                                                                         |

|--------------------|-----------------|-------------------|--------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N6<br>N7           | 39<br>41        | 56<br>57          | MDI[2]+<br>MDI[2]- | I/O, D      | Media Dependent Interface[2].  In 1000BASE-T mode in MDI configuration, MDI[2]± correspond to BI_DC±. In MDIX configuration, MDI[2]± corresponds to BI_DD±.  In 100BASE-TX and 10BASE-T modes, MDI[2]± are not used.  MDI[2]± should be tied to ground if not used. |

| N8<br>N9           | 42 43           | 61<br>62          | MDI[3]+<br>MDI[3]- | I/O, D      | Media Dependent Interface[3].  In 1000BASE-T mode in MDI configuration, MDI[3]± correspond to BI_DD±. In MDIX configuration, MDI[3]± correspond to BI_DC±.  In 100BASE-TX and 10BASE-T modes, MDI[3]± are not used.  MDI[3]± should be tied to ground if not used.  |

The GMII interface supports both 1000BASE-T and 1000BASE-X modes of operation. The GMII interface pins are also used for the TBI interface. See Table 3 for TBI pin definitions. The MAC interface pins are 3.3V tolerant.

Table 2: GMII/MII Interfaces

| 117-TFBGA<br>Pin # | 96-BCC<br>Pin # | 128-PQFP<br>Pin # | Pin Name | Pin<br>Type | Description                                                                                                                                                                                                                                           |

|--------------------|-----------------|-------------------|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E2                 | 8               | 14                | GTX_CLK  | I           | GMII Transmit Clock. GTX_CLK provides a 125 MHz clock reference for TX_EN, TX_ER, and TXD[7:0]. This clock can be stopped when the device is in 10/100BASE-T modes, and also during Auto-Negotiation.                                                 |

| D1                 | 4               | 10                | TX_CLK   | O, Z        | MII Transmit Clock. TX_CLK provides a 25 MHz clock reference for TX_EN, TX_ER, and TXD[3:0] in 100BASE-TX mode, and a 2.5 MHz clock reference in 10BASE-T mode.                                                                                       |

|                    |                 |                   |          |             | TX_CLK provides a 25 MHz, 2.5 MHz, or 0 MHz clock during 1000 Mbps Good Link, Auto-Negotiation, and Link Lost states depending on the setting of register 20.6:4.                                                                                     |

|                    |                 |                   |          |             | The 2.5 MHz clock is the default rate, which may be programmed to another frequency by writing to register 20.6:4.                                                                                                                                    |

| E1                 | 9               | 16                | TX_EN    | I           | GMII and MII Transmit Enable. In GMII/MII mode when TX_EN is asserted, data on TXD[7:0] along with TX_ER is encoded and transmitted onto the cable.                                                                                                   |

|                    |                 |                   |          |             | TX_EN is synchronous to GTX_CLK, and synchronous to TX_CLK in 100BASE-TX and 10BASE-T modes.                                                                                                                                                          |

| F2                 | 7               | 13                | TX_ER    | I           | GMII and MII Transmit Error. In GMII/MII mode when TX_ER and TX_EN are both asserted, the transmit error symbol is transmitted onto the cable. When TX_ER is asserted with TX_EN de-asserted, carrier extension symbol is transmitted onto the cable. |

|                    |                 |                   |          |             | TX_ER is synchronous to GTX_CLK, and synchronous to TX_CLK in 100BASE-TX and 10BASE-T modes.                                                                                                                                                          |

Table 2: GMII/MII Interfaces (Continued)

| 117-TFBGA<br>Pin #                           | 96-BCC<br>Pin #                              | 128-PQFP<br>Pin #                      | Pin Name                                                                            | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------|----------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J2<br>J1<br>H3<br>H1<br>H2<br>G3<br>G2<br>F1 | 20<br>19<br>18<br>17<br>16<br>14<br>12<br>11 | 29<br>28<br>26<br>25<br>24<br>20<br>19 | TXD[7] TXD[6] TXD[5] TXD[4] TXD[3]/TXD[3] TXD[2]/TXD[2] TXD[1]/TXD[1] TXD[0]/TXD[0] | I           | GMII and MII Transmit Data. In GMII mode, TXD[7:0] present the data byte to be transmitted onto the cable in 1000BASE-T mode.  In MII mode, TXD[3:0] present the data nibble to be transmitted onto the cable in 100BASE-TX and 10BASE-T modes.  TXD[7:4] are ignored in these modes, but should be driven either high or low. These pins must not float.  TXD[7:0] are synchronous to GTX_CLK, and synchronous to TX_CLK in 100BASE-TX and 10BASE-T modes.  Inputs TXD[7:4] should be tied low if not used (e.g., RGMII mode). |

| C1                                           | 2                                            | 7                                      | RX_CLK                                                                              | O, Z        | GMII and MII Receive Clock. RX_CLK provides a 125 MHz clock reference for RX_DV, RX_ER, and RXD[7:0] in 1000BASE-T mode, a 25 MHz clock reference in 100BASE-TX mode, and a 2.5 MHz clock reference in 10BASE-T mode.  TX_TCLK comes from the RX_CLK pins used in jitter testing. Refer to Register 9 for jitter test modes.                                                                                                                                                                                                    |

| B1                                           | 94                                           | 4                                      | RX_DV                                                                               | O, Z        | GMII and MII Receive Data Valid. When RX_DV is asserted, data received on the cable is decoded and presented on RXD[7:0] and RX_ER.  RX_DV is synchronous to RX_CLK.                                                                                                                                                                                                                                                                                                                                                            |

| D2                                           | 3                                            | 8                                      | RX_ER                                                                               | O, Z        | GMII and MII Receive Error. When RX_ER and RX_DV are both asserted, the signals indicate an error symbol is detected on the cable.  When RX_ER is asserted with RX_DV deasserted, a false carrier or carrier extension symbol is detected on the cable.  RX_ER is synchronous to RX_CLK.                                                                                                                                                                                                                                        |

Table 2: GMII/MII Interfaces (Continued)

| 117-TFBGA<br>Pin #                           | 96-BCC<br>Pin #                              | 128-PQFP<br>Pin #                                  | Pin Name                                                                                                 | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------|----------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C5<br>A2<br>A1<br>C4<br>B3<br>C3<br>D3<br>B2 | 86<br>87<br>89<br>90<br>91<br>93<br>92<br>95 | 120<br>121<br>123<br>124<br>125<br>126<br>128<br>3 | RXD[7]<br>RXD[6]<br>RXD[5]<br>RXD[4]<br>RXD[3]/RXD[3]<br>RXD[2]/RXD[2]<br>RXD[1]/RXD[1]<br>RXD[0]/RXD[0] | O, Z        | GMII and MII Receive Data. Symbols received on the cable are decoded and presented on RXD[7:0] in 1000BASE-T mode.  In MII mode, RXD[3:0] are used in 100BASE-TX and 10BASE-T modes. In MII mode, RXD[7:4] are driven low.  RXD[7:0] is synchronous to RX_CLK.                                                                                                                                         |

| B5                                           | 84                                           | 115                                                | CRS                                                                                                      | O, Z        | GMII and MII Carrier Sense. CRS asserts when the receive medium is non-idle. In half-duplex mode, CRS is also asserted during transmission. CRS assertion during half-duplex transmit can be disabled by programming register 16.11 to 0.  CRS is asynchronous to RX_CLK, GTX_CLK, and TX_CLK.                                                                                                         |

| B6                                           | 83                                           | 114                                                | COL                                                                                                      | O, Z        | GMII and MII Collision. In 10/100/ 1000BASE-T full-duplex modes, COL is always low. In 10/100/1000BASE-T half-duplex modes, COL asserts only when both the transmit and receive media are non-idle.  In 10BASE-T half-duplex mode, COL is asserted to indicate signal quality error (SQE). SQE can be disabled by clearing register 16.2 to zero.  COL is asynchronous to RX_CLK, GTX_CLK, and TX_CLK. |

The TBI interface supports 1000BASE-T mode of operation. The TBI interface uses the same pins as the GMII interface. The MAC interface pins are 3.3V tolerant.

Table 3: TBI Interface

| 117-TFBGA<br>Pin #                           | 96-BCC<br>Pin #                              | 128-PQFP<br>Pin #                                  | Pin Name                                                                     | Pin<br>Type | Description                                                                                                                                                                                                                         |

|----------------------------------------------|----------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E2                                           | 8                                            | 14                                                 | GTX_CLK/<br>TBI_TXCLK                                                        | I           | TBI Transmit Clock. In TBI mode, GTX_CLK is used as TBI_TXCLK. TBI_TXCLK is a 125 MHz transmit clock.                                                                                                                               |

|                                              |                                              |                                                    |                                                                              |             | TBI_TXCLK provides a 125 MHz clock reference for TX_EN, TX_ER, and TXD[7:0].                                                                                                                                                        |

| D1                                           | 4                                            | 10                                                 | TX_CLK/RCLK1                                                                 | O, Z        | TBI 62.5 MHz Receive Clock- even code group. In TBI mode, TX_CLK is used as RCLK1.                                                                                                                                                  |

| J2<br>J1<br>H3                               | 20<br>19<br>18                               | 29<br>28<br>26                                     | TXD[7]<br>TXD[6]<br>TXD[5]                                                   | I           | TBI Transmit Data. TXD[7:0] presents the data byte to be transmitted onto the cable.                                                                                                                                                |

| H1<br>H2                                     | 17<br>16                                     | 25<br>24                                           | TXD[4]<br>TXD[3]                                                             |             | TXD[9:0] are synchronous to GTX_CLK.                                                                                                                                                                                                |

| G3<br>G2<br>F1                               | 14<br>12<br>11                               | 20<br>19<br>18                                     | TXD[2]<br>TXD[1]<br>TXD[0]                                                   |             | Inputs TXD[7:4] should be tied low if not used (e.g., RTBI mode).                                                                                                                                                                   |

| E1                                           | 9                                            | 16                                                 | TX_EN/<br>TXD8                                                               | I           | TBI Transmit Data. In TBI mode, TX_EN is used as TXD8.                                                                                                                                                                              |

|                                              |                                              |                                                    |                                                                              |             | TXD[9:0] are synchronous to GTX_CLK.                                                                                                                                                                                                |

| F2                                           | 7                                            | 13                                                 | TX_ER/<br>TXD9                                                               | I           | TBI Transmit Data. In TBI mode, TX_ER is used as TXD9.                                                                                                                                                                              |

|                                              |                                              |                                                    |                                                                              |             | TXD[9:0] are synchronous to GTX_CLK.                                                                                                                                                                                                |

|                                              |                                              |                                                    |                                                                              |             | TX_ER should be tied low if not used (e.g., RTBI mode).                                                                                                                                                                             |

| C1                                           | 2                                            | 7                                                  | RX_CLK/<br>RCLK0                                                             | O, Z        | TBI 62.5 MHz Receive Clock- odd code group. In the TBI mode, RX_CLK is used as RCLK0.                                                                                                                                               |

| C5<br>A2<br>A1<br>C4<br>B3<br>C3<br>D3<br>B2 | 86<br>87<br>89<br>90<br>91<br>93<br>92<br>95 | 120<br>121<br>123<br>124<br>125<br>126<br>128<br>3 | RXD[7]<br>RXD[6]<br>RXD[5]<br>RXD[4]<br>RXD[3]<br>RXD[2]<br>RXD[1]<br>RXD[0] | O, Z        | TBI Receive Data code group [7:0]. In the TBI mode, RXD[7:0] present the data byte to be transmitted to the MAC. Symbols received on the cable are decoded and presented on RXD[7:0].  RXD[7:0] are synchronous to RCLK0 and RCLK1. |

| B1                                           | 94                                           | 4                                                  | RX_DV/<br>RXD8                                                               | O, Z        | TBI Receive Data code group bit 8. In the TBI mode, RX_DV is used as RXD8.  RXD[9:0] are synchronous to RCLK0 and RCLK1.                                                                                                            |

Table 3: TBI Interface (Continued)

| 117-TFBGA<br>Pin # | 96-BCC<br>Pin # | 128-PQFP<br>Pin # | Pin Name       | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                                            |

|--------------------|-----------------|-------------------|----------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D2                 | 3               | 8                 | RX_ER/<br>RXD9 | O, Z        | TBI Receive Data code group bit 9. In the TBI mode, RX_ER is used as RXD9.  RXD[9:0] are synchronous to RCLK0 and RCLK1.                                                                                                                                                                                                                               |

| B5                 | 84              | 115               | CRS/<br>COMMA  | O, Z        | TBI Valid Comma Detect. In the TBI mode, CRS is used as COMMA.                                                                                                                                                                                                                                                                                         |

| B6                 | 83              | 114               | COL/LPBK       | 1           | TBI Mode Loopback. In the TBI mode, COL is used to indicate loopback on the TBI. When a "0 - 1" transition is sampled on this pin, bit 0.14 is set to 1. When a "1 - 0" is sampled on this pin, bit 0.14 is reset to 0.  If this feature is not used, the COL pin should be driven low on the board. This pin should not be left floating in TBI mode. |

The RGMII interface supports 10/100/1000BASE-T and 1000BASE-X modes of operation. The RGMII interface pins are also used for the RTBI interface. See Table 5 for RTBI pin definitions. The MAC interface pins are 3.3V tolerant.

Table 4: RGMII Interface

| 117-TFBGA<br>Pin #   | 96-BCC<br>Pin #      | 128-PQFP<br>Pin #      | Pin Name                                                     | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                      |

|----------------------|----------------------|------------------------|--------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E2                   | 8                    | 14                     | GTX_CLK/<br>TXC                                              | I           | RGMII Transmit Clock provides a 125 MHz, 25 MHz, or 2.5 MHz reference clock with ± 50 ppm tolerance depending on speed. In RGMII mode, GTX_CLK is used as TXC.                                                                                                                                                   |

| H2<br>G3<br>G2<br>F1 | 16<br>14<br>12<br>11 | 24<br>20<br>19<br>18   | TXD[3]/TD[3] TXD[2]/TD[2] TXD[1]/TD[1] TXD[0]/TD[0]          | I           | RGMII Transmit Data. In RGMII mode, TXD[3:0] are used as TD[3:0]. In RGMII mode, TXD[3:0] run at double data rate with bits [3:0] presented on the rising edge of GTX_CLK, and bits [7:4] presented on the falling edge of GTX_CLK. In this mode, TXD[7:4] are ignored.  In RGMII 10/100BASE-T modes, the trans- |

|                      |                      |                        |                                                              |             | mit data nibble is presented on TXD[3:0] on the rising edge of GTX_CLK.                                                                                                                                                                                                                                          |

| E1                   | 9                    | 16                     | TX_EN/<br>TX_CTL                                             | I           | RGMII Transmit Control. In RGMII mode, TX_EN is used as TX_CTL. TX_EN is presented on the rising edge of GTX_CLK.                                                                                                                                                                                                |

|                      |                      |                        |                                                              |             | A logical derivative of TX_EN and TX_ER is presented on the falling edge of GTX_CLK.                                                                                                                                                                                                                             |

| C1                   | 2                    | 7                      | RX_CLK/<br>RXC                                               | O, Z        | RGMII Receive Clock provides a 125 MHz, 25 MHz, or 2.5 MHz reference clock with ± 50 ppm tolerance derived from the received data stream depending on speed. In RGMII mode, RX_CLK is used as RXC.                                                                                                               |

| B1                   | 94                   | 4                      | RX_DV/<br>RX_CTL                                             | O, Z        | RGMII Receive Control. In RGMII mode, RX_DV is used as RX_CTL. RX_DV is presented on the rising edge of RX_CLK.                                                                                                                                                                                                  |

|                      |                      |                        |                                                              |             | A logical derivative of RX_DV and RX_ER is presented on the falling edge of RX_CLK.                                                                                                                                                                                                                              |

| B3<br>C3<br>D3<br>B2 | 91<br>93<br>92<br>95 | 125<br>126<br>128<br>3 | RXD[3]/RD[3]<br>RXD[2]/RD[2]<br>RXD[1]/RD[1]<br>RXD[0]/RD[0] | O, Z        | RGMII Receive Data. In RGMII mode, RXD[3:0] are used as RD[3:0]. In RGMII mode, RXD[3:0] run at double data rate with bits [3:0] presented on the rising edge of RX_CLK, and bits [7:4] presented on the falling edge of RX_CLK. In this mode, RXD[7:4] are ignored.                                             |

|                      |                      |                        |                                                              |             | In RGMII 10/100BASE-T modes, the receive data nibble is presented on RXD[3:0] on the rising edge of RX_CLK. RXD[3:0] are synchronous to RX_CLK.                                                                                                                                                                  |

The RTBI interface supports 1000BASE-T mode of operation. The RTBI interface uses the same pins as the RGMII interface. The MAC interface pins are 3.3V tolerant.

Table 5: RTBI Interface

| 117-TFBGA<br>Pin #   | 96-BCC<br>Pin #      | 128-PQFP<br>Pin #      | Pin Name                                                     | Pin<br>Type | Description                                                                                                                                                                                                                                           |

|----------------------|----------------------|------------------------|--------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E2                   | 8                    | 14                     | GTX_CLK/<br>TXC                                              | I           | RGMII Transmit Clock provides a 125 MHz reference clock with ± 50 ppm tolerance. In RTBI mode, GTX_CLK is used as TXC.                                                                                                                                |

| H2<br>G3<br>G2<br>F1 | 16<br>14<br>12<br>11 | 24<br>20<br>19<br>18   | TXD[3]/TD[3]<br>TXD[2]/TD[2]<br>TXD[1]/TD[1]<br>TXD[0]/TD[0] | I           | RTBI Transmit Data. In RTBI mode, TXD[3:0] are used as TD[3:0]. TD[3:0] run at double data rate with bits [3:0] presented on the rising edge of GTX_CLK, and bits [8:5] presented on the falling edge of GTX_CLK. In this mode, TXD[7:4] are ignored. |

| E1                   | 9                    | 16                     | TX_EN/<br>TD4_TD9                                            | I           | RTBI Transmit Data. In RTBI mode, TX_EN is used as TD4_TD9. TD4_TD9 runs at a double data rate with bit 4 presented on the rising edge of GTX_CLK, and bit 9 presented on the falling edge of GTX_CLK.                                                |

| C1                   | 2                    | 7                      | RX_CLK/<br>RXC                                               | O, Z        | RTBI Receive Clock provides a 125 MHz reference clock with ± 50 ppm tolerance derived from the received data stream. In RTBI mode, RX_CLK is used as RXC.                                                                                             |

| B3<br>C3<br>D3<br>B2 | 91<br>93<br>92<br>95 | 125<br>126<br>128<br>3 | RXD[3]/RD[3]<br>RXD[2]/RD[2]<br>RXD[1]/RD[1]<br>RXD[0]/RD[0] | O, Z        | RTBI Receive Data. In RTBI mode, RXD[3:0] are used as RD[3:0]. RD[3:0] runs at double data rate with bits [3:0] presented on the rising edge of RX_CLK, and bits [8:5] presented on the fall- ing edge of RX_CLK. In this mode, RXD[7:4] are ignored. |

| B1                   | 94                   | 4                      | RX_DV/<br>RD4_RD9                                            | O, Z        | RTBI Receive Data. In RTBI mode, RX_DV is used as RD4_RD9. RD4_RD9 runs at a double data rate with bit 4 presented on the rising edge of RX_CLK, and bit 9 presented on the fall- ing edge of RX_CLK.                                                 |

Table 6: SGMII Interface

| 117-TFBGA<br>Pin # | 96-BCC<br>Pin # | 128-PQFP<br>Pin # | Pin Name         | Pin<br>Type | Description                                                                                                                                                                                                                                                 |

|--------------------|-----------------|-------------------|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A3<br>A4           | 82<br>81        | 113<br>112        | S_IN+<br>S_IN-   | I           | SGMII Transmit Data. 1.25 GBaud input - Positive and Negative.                                                                                                                                                                                              |

|                    |                 |                   |                  |             | Input impedance on the S_IN± pins may be programmed for 50 ohm or 75 ohm impedance by setting register 26.6. The input impedance default setting is determined by the 75/50 OHM configuration pin.                                                          |

| A5<br>A6           | 79<br>80        | 110<br>109        | S_CLK+<br>S_CLK- | I/O         | SGMII 625 MHz Receive Clock.                                                                                                                                                                                                                                |

| 7.0                |                 |                   | <u>0_02</u> K    |             | For Serial Interface modes (HWCFG_MODE[3:0] = 1x00) the S_CLK± pins become Signal Detect± (SD±) inputs.                                                                                                                                                     |

| A7<br>A8           | 77<br>75        | 107<br>105        | S_OUT+<br>S_OUT- | O, Z        | SGMII Receive Data. 1.25 GBaud output - Positive and Negative.                                                                                                                                                                                              |

|                    |                 |                   |                  |             | Output impedance on the S_OUT± pins may be programmed for 50 ohm or 75 ohm impedance by setting register 26.5. Output amplitude can be adjusted via register 26.2:0. The output impedance default setting is determined by the 75/50 OHM configuration pin. |

Table 7: 1.25 GHz Serial High Speed Interface

| 117-TFBGA<br>Pin # | 96-BCC<br>Pin # | 128-PQFP<br>Pin # | Pin Name                 | Pin<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------|-----------------|-------------------|--------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A3<br>A4           | 82<br>81        | 113<br>112        | S_IN+<br>S_IN-           |             | 1.25 GHz input - Positive and Negative. When this interface is used as a MAC interface, the MAC transmitter's positive output connects to the S_IN+. The MAC transmitter's negative output connects to the S_IN  When this interface is used as a fiber interface, the fiber-optic transceiver's positive output connects to the S_IN+. The fiber-optic transceiver's negative output connects to the S_IN  Input impedance on the S_IN± pins may be programmed for 50 ohm or 75 ohm impedance by setting register 26.6. The input impedance default setting is determined by the 75/50 OHM configuration pin. |

| A5<br>A6           | 79<br>80        | 110<br>109        | S_CLK+/SD+<br>S_CLK-/SD- | I           | Signal Detect input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Аб                 | 80              | 109               | 3_CLR-/3D-               |             | For Serial Interface modes the S_CLK± pins become Signal Detect± (SD±) inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| A7<br>A8           | 77<br>75        | 107<br>105        | S_OUT+<br>S_OUT-         | O, Z        | 1.25 GHz output – Positive and Negative. When this interface is used as a MAC interface, S_OUT+ connects to the MAC receiver's positive input. S_OUT- connects to the MAC receiver's negative input.                                                                                                                                                                                                                                                                                                                                                                                                           |

|                    |                 |                   |                          |             | When this interface is used as a fiber interface, S_OUT+ connects to the fiber-optic transceiver's positive input. S_OUT- connects to the fiber-optic transceiver's negative input.                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                    |                 |                   |                          |             | Output impedance on the S_OUT± pins may be programmed for 50 ohm or 75 ohm impedance by setting register 26.5. Output amplitude can be adjusted via register 26.2:0. The output impedance default setting is determined by the 75/50 OHM configuration pin.                                                                                                                                                                                                                                                                                                                                                    |

| B3                 | 91              | 125               | RXD[3]                   | O, Z        | Serial MAC interface Copper Link Status[1] connection.  1 = Copper link up  0 = Copper link down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Table 7: 1.25 GHz Serial High Speed Interface (Continued)

| 117-TFBGA<br>Pin # | 96-BCC<br>Pin # | 128-PQFP<br>Pin # | Pin Name | Pin<br>Type | Description                                                                                                              |

|--------------------|-----------------|-------------------|----------|-------------|--------------------------------------------------------------------------------------------------------------------------|

| C3                 | 93              | 126               | RXD[2]   | O, Z        | Serial MAC interface Copper Link Status[0] connection.  1 = Copper link down  0 = Copper link up                         |

| D3                 | 92              | 128               | RXD[1]   | O, Z        | Serial MAC interface PHY_SIGDET[1] connection.  1 = S_OUT± valid code groups according to clause 36.  0 = S_OUT± invalid |

| B2                 | 95              | 3                 | RXD[0]   | O, Z        | Serial MAC interface PHY_SIGDET[0] connection.  1 = S_OUT± invalid  0 = S_OUT± valid code groups according to clause 36  |

Table 8: Management Interface and Interrupt

| 117-TFBGA<br>Pin # | 96-BCC<br>Pin # | 128-PQFP<br>Pin # | Pin Name | Pin<br>Type             | Description                                                                                                                                                                          |

|--------------------|-----------------|-------------------|----------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L3                 | 25              | 35                | MDC      | I<br>3.3V<br>Tolerant   | MDC is the management data clock reference for the serial management interface. A continuous clock stream is not expected. The maximum frequency supported is 8.3 MHz.               |

| M1                 | 24              | 33                | MDIO     | I/O<br>3.3V<br>Tolerant | MDIO is the management data. MDIO transfers management data in and out of the device synchronously to MDC. This pin requires a pull-up resistor in a range from 1.5 kohm to 10 kohm. |

| L1                 | 23              | 32                | INTn     | D                       | The polarity of the INTn pin may be programmed at hardware reset by setting the INT_POL bit.  Polarity: 0 = Active High 1 = Active Low                                               |

Table 9: Two-Wire Serial Interface

| 117-TFBGA<br>Pin # | 96-BCC<br>Pin # | 128-PQFP<br>Pin # | Pin Name | Pin<br>Type | Description                                                                                                                                                                                                                 |

|--------------------|-----------------|-------------------|----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L3                 | 25              | 35                | MDC/SCL  | I           | Two-Wire Serial Interface (TWSI) serial clock line. When the 88E1111 device is connected to the bus, MDC connects to the serial clock line (SCL).  Data is input on the rising edge of SCL, and output on the falling edge. |

| M1                 | 24              | 33                | MDIO/SDA | I/O         | TWSI serial data line. When the 88E1111 device is connected to the bus, MDIO connects to the serial data line (SDA). This pin is open-drain and may be wire-ORed with any number of open-drain devices.                     |

Table 10: LED Interface

| 117-TFBGA<br>Pin # | 96-BCC<br>Pin # | 128-PQFP<br>Pin # | Pin Name     | Pin<br>Type | Description                                                                                                                                                                                                               |

|--------------------|-----------------|-------------------|--------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C8                 | 76              | 100               | LED_LINK10   | O, mA       | Parallel LED output for 10BASE-T link or speed. This active low LED pin may be programmed in direct drive or combined LED modes by programming register LED_LINK Control register 24.4:3.                                 |

|                    |                 |                   |              |             | In direct drive LED mode, this pin indicates 10 Mbps link up or down.                                                                                                                                                     |

|                    |                 |                   |              |             | In combined LED mode, the output from LED_LINK10, LED_LINK100, and LED_LINK1000 must be read together to determine link and speed status.                                                                                 |

|                    |                 |                   |              |             | LED_LINK10 is a multi-function pin used to configure the 88E1111 device at the deassertion of hardware reset.                                                                                                             |

| В8                 | 74              | 99                | LED_LINK100  | O, mA       | Parallel LED output for 100BASE-TX link or speed. This active low LED pin may be programmed in direct drive or combined LED modes by programming register LED_LINK Control register 24.4:3.                               |

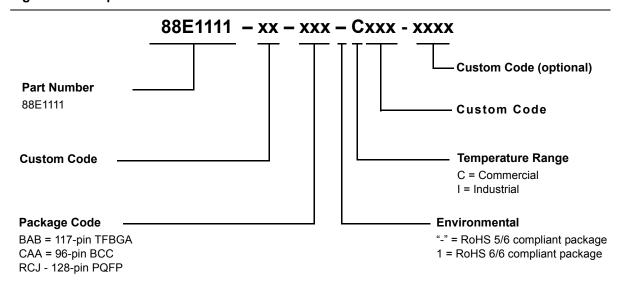

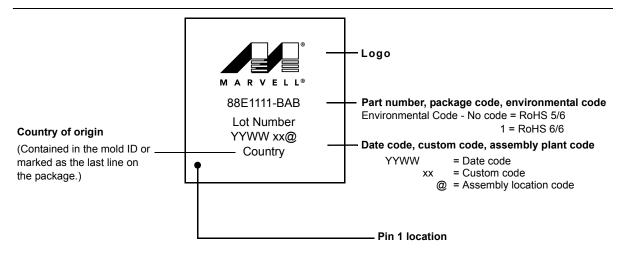

|                    |                 |                   |              |             | In direct drive LED mode, this pin indicates 100 Mbps link up or down.                                                                                                                                                    |