# T-49-17-32

# Advance information

# Am29005

# **Advanced** Micro **Devices**

# **Low-Cost Streamlined Instruction Microprocessor**

# **DISTINCTIVE CHARACTERISTICS**

- Full 32-bit, three-bus architecture

- Nine million instructions per second (MIPS) sustained at its 16-MHz operating frequency

- Efficient execution of high-level language programs

- **CMOS** technology

- Concurrent Instruction and data accesses

- **Burst-mode access support**

- 192 general-purpose registers

- Demultiplexed, pipelined address, instruction, and data buses

- Three-address instruction architecture

- On-chip byte-alignment support allows optional byte/half-word accesses

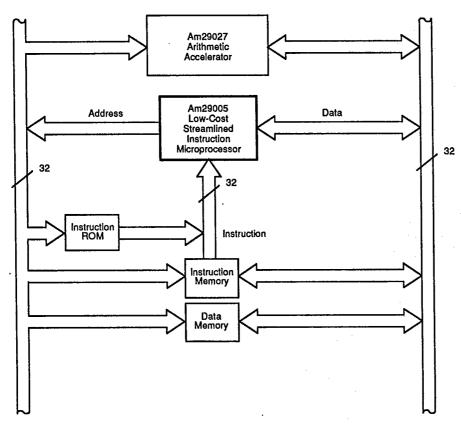

# SIMPLIFIED BLOCK DIAGRAM

09075B-003A

This document contains information on a product under development at Advanced Micro Devices, Inc. The information is intended to help you to evaluate this product. AMD reserves the right to change or discontinue work on this proposed product without notice.

Publication # 13089 Rev. B Issue Date: August 1990

|    | NCED<br>MAMD       | MICRO                          | DEVI              | ES<br>ADVAN                             | _ 28      | E       | D .         |           | 025       | 7525              |             |           |         |             |                  |    |

|----|--------------------|--------------------------------|-------------------|-----------------------------------------|-----------|---------|-------------|-----------|-----------|-------------------|-------------|-----------|---------|-------------|------------------|----|

| -  |                    | IVE CHARAC                     | TEDISTI           | 26                                      | <u> </u>  | - 113   |             | 1 W A     | 1 1 0     | <u>/ 14</u>       | T-49        | -17-      | -32     | <del></del> |                  |    |

|    |                    | D BLOCK D                      |                   |                                         |           |         |             |           |           |                   |             |           |         |             |                  |    |

|    |                    |                                |                   |                                         |           |         |             |           |           |                   |             |           |         |             |                  |    |

|    | JENEHAL            | DESCRIPTI                      | ON                | • • • • • • • • •                       | • • • •   | • • • • | • • • • •   | • • • • • | ••••      | • • • • • • •     | • • • • •   | • • • •   |         | ••••        | 2                |    |

|    | IN DESIG           | NATIONS.                       | • • • • • • •     | • • • • • • • • • •                     | • • • •   | • • •   | • • • • •   | • • • • • | ••••      | • • • • • • •     | • • • • •   | • • • •   | • • • • |             | 3                | Į. |

|    |                    | MBOL                           |                   |                                         |           |         |             |           |           |                   |             |           |         |             |                  |    |

| F  | PIN DESC           | RIPTION                        | • • • • • • •     | • • • • • • • • •                       | • • • •   | • • •   | • • • • •   | • • • • • | • • • • • |                   |             |           |         |             | 6                |    |

| F  | UNCTION:<br>Produc | NAL DESCRI                     | PTION             |                                         | ••••      | • • • • | • • • • •   | • • • • • | ••••      | • • • • • • •     |             | • • • •   | • • • • | •••         | . 10             |    |

|    | ARCHITEC           | TURE HIGH                      | II IGHTS          |                                         | • • • • • | • • • • | • • • • •   | • • • • • |           |                   | ••••        | • • • • • | • • • • |             | 10               |    |

| ٠  | Archite            | cture Overvi                   | ew                | · • • • • • • • • • •                   | • • • • • |         |             | • • • • • | • • • •   | • • • • • • •     | ••••        | • • • •   | • • • • | • •, •,     | 12               |    |

|    | Progra             | m Modes                        |                   |                                         |           |         |             |           |           |                   |             |           |         |             | . 12             |    |

|    | Visible            | Registers                      |                   |                                         |           |         |             |           |           |                   |             |           |         |             | 12               |    |

|    | Instruc            | tion Set Over                  | Miew<br>Jandlina  | • • • • • • • • • • • • • • • • • • • • | • • • • • | • • • • | • • • • •   | • • • • • |           |                   |             | • • • • • |         | • • • •     | 14               |    |

|    | interru            | ormats and H<br>pts and Traps  | anung.            |                                         |           | • • • • | • • • • •   | • • • • • | • • • • • |                   | • • • • • • | • • • • • | • • • • | • • • •     | 17               |    |

|    | Coproc             | essor Progra                   | amming            |                                         |           |         | . <b></b> . |           |           |                   |             |           |         |             | . 19             |    |

|    | Timer              | Facility                       |                   |                                         |           |         | . <b></b> . |           |           |                   |             |           |         |             | 19               |    |

|    | Trace              | Facility                       | • • • • • • • •   | • • • • • • • • • • • • • • • • • • • • | • • • • • | • • • • | · • • • •   | • • • • • |           |                   | • • • • •   |           |         |             | 19               |    |

| F  | UNCTION            | IAL OPERAT                     | TION              | • • • • • • • • • •                     | • • • •   | • • • • |             |           |           |                   |             |           |         |             | . 20             |    |

|    | Function           | tage Pipeline<br>on Organizati | )                 | • • • • • • • • • •                     | • • • • • | • • • • | • • • • •   |           | • • • • • | • • • • • • •     | • • • • •   | • • • •   |         | • • • •     | 20               |    |

|    | Systen             | n Interface                    |                   |                                         |           | ••••    | • • • • •   | • • • • • |           | • • • • • • •     | • • • • •   | • • • • • | • • • • | • • • •     | 20               |    |

|    | Progra             | m Modes                        |                   |                                         | <br>      |         |             |           |           | · • • • • • • • • |             |           | • • • • | • • • •     | 23               |    |

| F  | REGISTER           | DESCRIPTI                      | ION               |                                         |           |         |             |           |           |                   |             |           |         |             | 24               |    |

|    | Genera             | al-Purpose Re                  | egisters .        |                                         |           |         | . <b></b> . |           |           |                   |             |           |         |             | 24               |    |

|    | Specia             | I-Purpose Re                   | gisters           | • • • • • • • • •                       | • • • • • |         |             |           |           |                   |             |           |         |             | . , 27           |    |

| II | NSTRUCT            | ION SET                        | • • • • • • •     | • • • • • • • • •                       |           |         |             |           |           |                   |             |           |         |             | . 40             |    |

|    | Compa              | Arithmetic .                   | • • • • • • • • • | • • • • • • • • • •                     | • • • • • | • • • • | • • • • •   | • • • • • | • • • • • | • • • • • •       |             |           | • • • • | • • • •     | 40               |    |

|    | Logical            | re                             |                   |                                         | • • • • • | • • • • | • • • • •   | • • • • • | • • • • • | •••••             | • • • • • • | ••••      | • • • • | • • • •     | 40               |    |

|    | Shift .            |                                |                   |                                         | <br>      |         |             |           |           |                   |             | ••••      | • • • • | • • • •     | 40<br><i>A</i> n |    |

|    | Data M             | ovement                        |                   |                                         |           |         |             |           |           |                   |             |           |         |             | 40               | •  |

|    | Consta             | nt                             |                   |                                         |           |         |             |           |           |                   |             |           |         |             | 40               |    |

|    | Branch             | g-Point                        | • • • • • • • •   | • • • • • • • • • • •                   | • • • • • | • • • • |             | • • • • • | • • • • • |                   | • • • • • • | • • • •   |         |             | 43               |    |

|    | Miscell            | aneous                         |                   |                                         |           |         | • • • • •   | • • • • • | • • • • • | • • • • • • •     | • • • • • • | • • • •   | •       | • • • •     | 43               |    |

|    | Reserv             | ed Instruction                 | าร                |                                         | <br>      |         |             |           |           |                   |             |           |         | • • • • • • | 43               |    |

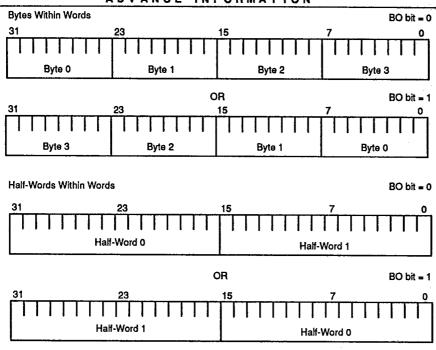

| D  | ATA FOR            | MATS AND                       | HANDLIN           | G                                       |           |         |             |           |           |                   |             |           |         | • • • •     | 40<br>A7         |    |

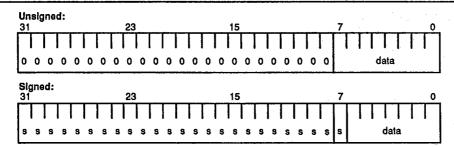

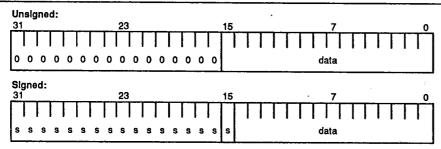

|    | Integer            | Data Types                     |                   |                                         |           |         |             |           |           |                   |             |           |         |             | . 47             |    |

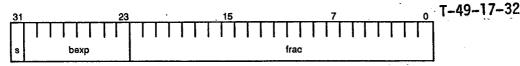

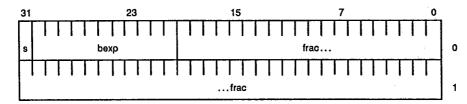

|    | rioating           | g-Point Data                   | Types             |                                         |           |         |             |           |           |                   |             |           |         |             | . 48             |    |

|    | Specia             | Floating-Poi                   | nt Values         | • • • • • • • • • •                     | • • • •   | • • • • | • • • • •   | • • • • • | • • • • • | • • • • • • •     | • • • • •   | • • • • • | • • • • | • • • •     | 49               |    |

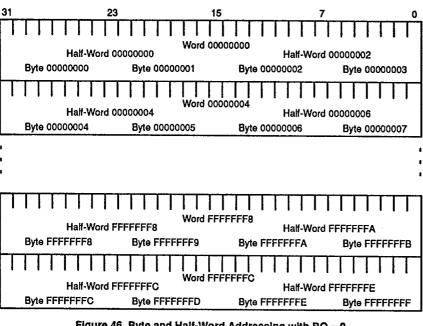

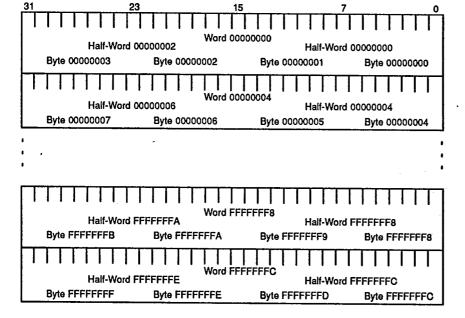

|    | Addres             | al Data Acces<br>sing and Alig | nment             |                                         | • • • • • | • • • • | • • • • •   | • • • • • | • • • • • | • • • • • • •     | • • • • • • | ••••      | • • • • | • • • • •   | 50               |    |

|    | Byte ar            | d Half-Word                    | Accesses          |                                         | · · · · · |         |             |           |           |                   |             |           | • • • • | • • • •     | 53<br>55         |    |

| I  |                    | TS AND TRA                     |                   |                                         |           |         |             |           |           |                   |             |           |         |             |                  |    |

|    | Interrup           | ots                            |                   |                                         |           |         |             |           |           |                   |             |           |         |             | 57               |    |

|    | Traps              |                                |                   |                                         |           |         |             |           |           |                   |             |           |         |             | 57               |    |

|    | Wait M             | ode                            | • • • • • • •     | • • • • • • • • • • •                   | • • • •   | • • • • | • • • • •   | • • • • • | • • • • • | • • • • • •       | • • • • • • | • • • • • |         |             | 57               |    |

|    | Internir           | Area<br>ot and Trap H          | andling           | • • • • • • • • • •                     | • • • •   | • • • • | • • • • •   | • • • • • | • • • • • | • • • • • •       | • • • • •   | • • • • • | • • • • | • • • •     | 58               |    |

|    | WARK               | Tran                           | anding .          | • • • • • • • • • •                     | • • • •   | • • • • | • • • • •   | • • • • • | • • • • • | • • • • • • •     | • • • • • • | • • • • • | • • •   | •••         | . 58             |    |

**Table of Contents**

Sequencing of Interrupts and Traps .......62

| DVANCED                                              | MICRO                                        | DEAICEZ                                      |      |       |     |     |                                       |                                         |        |                      |

|------------------------------------------------------|----------------------------------------------|----------------------------------------------|------|-------|-----|-----|---------------------------------------|-----------------------------------------|--------|----------------------|

|                                                      |                                              | ADV                                          | ANCE | INF   | ORM | ATI | ON T-                                 | .49-17-3                                | 2 AMD  | 4                    |

| Arithmetic                                           | Exceptions                                   | nd Restarting                                |      |       |     |     | · · · · · · · · · · · · · · · · · · · |                                         | 6<br>6 | 2<br>4               |

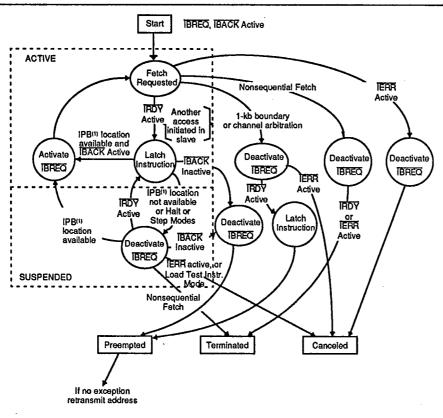

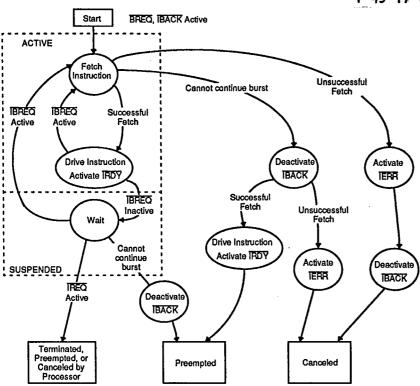

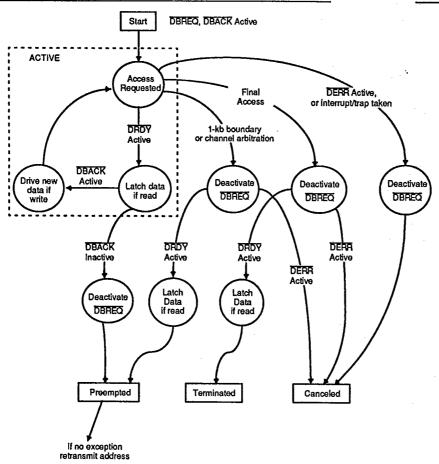

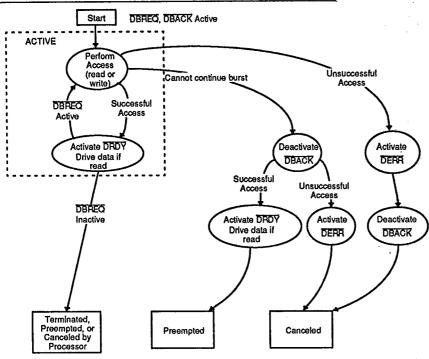

| CHANNEL DE<br>User-Defin<br>Instruction<br>Data Acce | SCRIPTION<br>ned Signals<br>Accesses .       |                                              |      | ••••• |     |     |                                       |                                         |        | i5<br>i5<br>i5<br>i6 |

| Access Pr<br>Simple Ac<br>Pipelined<br>Burst-Mod     | otocols<br>cesses<br>Accesses<br>de Accesses |                                              |      |       |     |     |                                       |                                         |        | 56<br>56<br>58<br>58 |

| Bus Shari<br>Channel E<br>Effect of the              | ng—Electrica<br>Behavior for I<br>he LOCK Ou | al Consideration<br>nterrupts and Ti<br>tput | raps |       |     |     |                                       | • • • • • • • • • • • • • • • • • • • • |        | 74<br>74<br>75       |

| ABSOLUTE N                                           | MAXIMUM R                                    | ATINGS                                       |      |       |     |     |                                       |                                         | 7      | 7                    |

| <b>OPERATING</b>                                     | RANGES .                                     |                                              |      |       |     |     |                                       |                                         | 7      | 77                   |

| DC CHARAC                                            | TERISTICS                                    |                                              |      |       |     |     |                                       |                                         | 7      | 77                   |

| CAPACITANO                                           | CE                                           |                                              |      |       |     |     |                                       |                                         | 7      | 77                   |

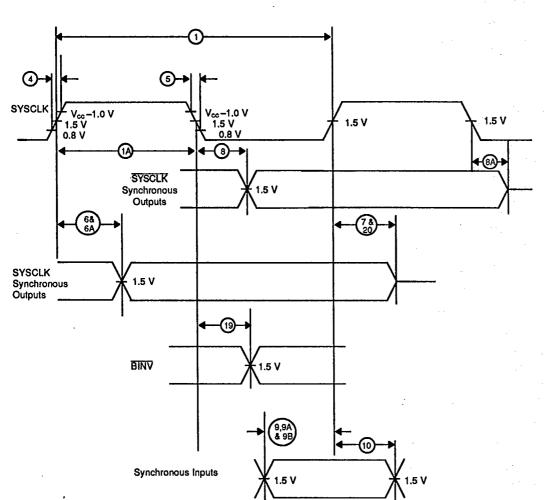

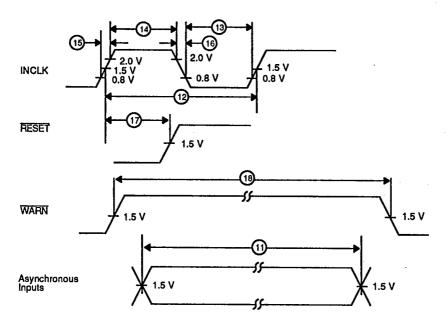

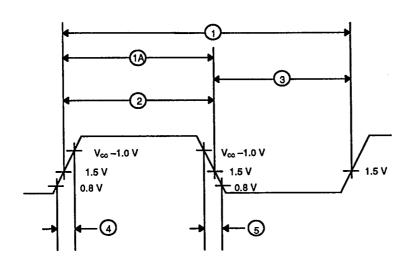

| SWITCHING                                            | CHARACTE                                     | RISTICS                                      |      |       |     |     |                                       |                                         | 7      | 78                   |

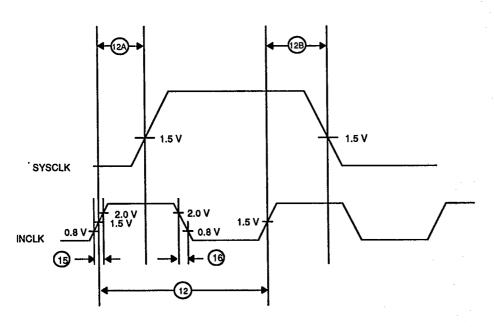

| SWITCHING                                            | WAVEFORM                                     | is                                           |      |       |     |     |                                       |                                         | 8      | 30                   |

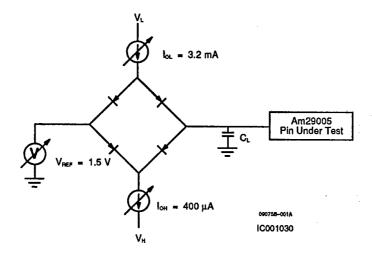

| SWITCHING                                            | TEST CIRCL                                   | JIT                                          |      |       |     |     |                                       |                                         |        | 33                   |

|                                                      |                                              |                                              |      |       |     |     |                                       |                                         |        |                      |

**Table of Contents**

# **GENERAL DESCRIPTION**

The Am29005™ Low-Cost Streamlined Instruction Processor is a high-performance, general-purpose, 32-bit microprocessor implemented in CMOS technology. It supports a variety of applications by virtue of a flexible architecture and rapid execution of simple instructions that are common to a wide range of tasks.

The Am29005 microprocessor efficiently performs operations common to all systems, while deferring most decisions on system policies to the system architect. It is well-suited for application in cost-sensitive embedded systems like laser printers, communications and graphics controllers, or other applications where high performance, flexibility, and the ability to program using standard software tools is important.

The Am29005 microprocessor instruction set has been influenced by the results of high-level language, optimizing compiler research. It is appropriate for a variety of languages because it efficiently executes operations that are common to all languages. Consequently, the Am29005 microprocessor is an ideal target for highlevel languages such as C, FORTRAN, Pascal, Ada®, and COBOL.

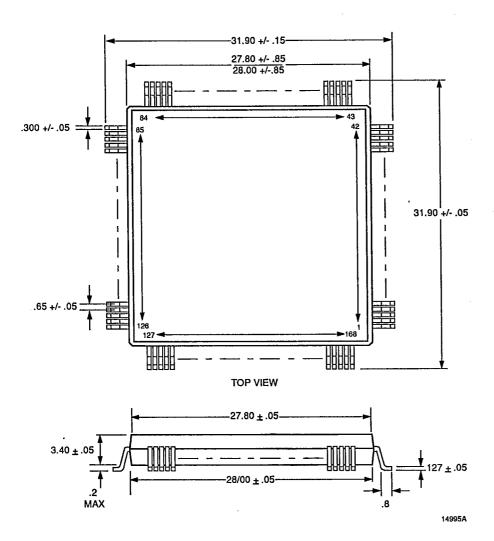

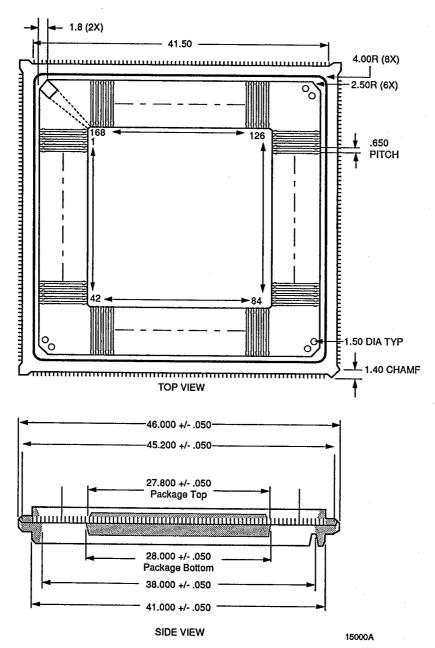

The processor is available in a 168-lead plastic-quadflat-pack (PQFP) package. The package has 141 signal pins and 27 power and ground pins. A representative system diagram is shown on page 1.

# 29K™ Family Development Support **Products**

Contact your local AMD® representative for information on AMD's complete set of development support tools.

Software development products on several hosts:

- Optimizing compilers for common high-level languages

- Assembler and utility packages

- Source- and assembly-level software debuggers

- Target-resident development monitors

- Simulators

# **RELATED AMD PRODUCTS**

Am29005 Microprocessor Peripheral Devices

| Description            |

|------------------------|

| Arithmetic Accelerator |

|                        |

# PQFP PIN DESIGNATIONS (Sorted by Pin Number)

| Pin No. | Pin Name          | Pin No. | Pin Name        | Pin No. | Pin Name          | Pin No. | Pin Name           |

|---------|-------------------|---------|-----------------|---------|-------------------|---------|--------------------|

| 1       | DRDY              | 43      | Vcc             | 85      | GND               | 127     | GND                |

| 2       | CDA               | 44      | 13              | 86      | A31               | 128     | OPT <sub>0</sub>   |

| 3       | INCLK             | 45      | l2              | 87      | A30               | 129     | OPT <sub>1</sub>   |

| 4       | PWRCLK            | 46      | l <sub>1</sub>  | 88      | A29               | 130     | OPT2               |

| 5       | SYSCLK            | 47      | GND             | 89      | A28               | 131     | SUP/US             |

| 6       | GND               | 48      | to              | 90      | A27               | 132     | IREQT              |

| 7       | V∞                | 49      | D <sub>0</sub>  | 91      | A <sub>26</sub>   | 133     | STAT <sub>0</sub>  |

| 8       | GND               | 50      | D <sub>1</sub>  | 92      | A25               | 134     | STAT <sub>1</sub>  |

| 9       | RESET             | 51      | D <sub>2</sub>  | 93      | A24               | 135     | STAT2              |

| 10      | CNTLo             | 52      | D <sub>3</sub>  | 94      | A23               | 136     | MSERR              |

| 11      | CNTL <sub>1</sub> | 53      | D <sub>4</sub>  | 95      | A22               | 137     | DREQT <sub>0</sub> |

| 12      | TEST              | 54      | D <sub>5</sub>  | 96      | A21               | 138     | DREQT              |

| 13      | l <sub>31</sub>   | 55      | De              | 97      | A20               | 139     | LOCK               |

| 14      | 130               | 56      | D <sub>7</sub>  | 98      | A19               | 140     | R/W                |

| 15      | 129               | 57      | D <sub>8</sub>  | 99      | A18               | 141     | DREQ               |

| 16      | 128               | 58      | D <sub>9</sub>  | 100     | A17               | 142     | PDA                |

| 17      | l <sub>27</sub>   | 59      | D10             | 101     | A16               | 143     | PIA                |

| 18      | 126               | 60      | Dii             | 102     | A15               | 144     | IREQ               |

| 19      | 125               | 61      | D12             | 103     | GND               | 145     | BGRT               |

| 20      | 124               | 62      | D13             | 104     | Vcc               | 146     | DBREQ              |

| 21      | GND               | 63      | D14             | 105     | Vcc               | 147     | IBREQ              |

| 22      | Vcc               | 64      | V∞              | 106     | A14               | 148     | BINV               |

| 23      | 123               | 65      | GND             | 107     | Аіз               | 149     | V∞                 |

| 24      | l <sub>22</sub>   | 66      | D15             | 108     | A12               | 150     | Vœ                 |

| 25      | 121               | 67      | Die             | 109     | A11               | 151     | GND                |

| 26      | 120               | 68      | D17             | 110     | A10               | 152     | Vœ                 |

| 27      | 119               | 69      | D18             | 111     | Aı                | 153     | GND                |

| 28      | 118               | 70      | D19             | 112     | Ao                | 154     | TRAP <sub>0</sub>  |

| 29      | l <sub>17</sub>   | 71      | D20             | 113     | MPGM <sub>0</sub> | 155     | TRAPi              |

| 30      | l <sub>16</sub>   | 72      | D21             | 114     | MPGM <sub>1</sub> | 156     | INTR₀              |

| 31 .    | l <sub>15</sub>   | 73      | D22             | 115     | Vcc               | 157     | INTR <sub>1</sub>  |

| 32      | 114               | 74      | D23             | 116     | Vcc               | 158     | INTR₂              |

| 33      | l13               | 75      | D24             | 117     | A9                | 159     | ĪNTR₃              |

| 34      | 112               | 76      | D <sub>25</sub> | 118     | A <sub>8</sub>    | 160     | WARN               |

| 35      | lss               | 77      | D26             | 119     | A7                | 161     | IBACK              |

| 36      | 110               | 78      | D27             | 120     | As                | 162     | IRDY               |

| 37      | lo lo             | 79      | D28             | 121     | A <sub>5</sub>    | 163     | ĪĒRR               |

| 38      | İs                | 80      | D29             | 122     | A4                | 164     | DERR               |

| 39      | 17                | 81      | D30             | 123     | Аз                | 165     | DBACK              |

| 40      | le                | 82      | D31             | 124     | A <sub>2</sub>    | 166     | PEN                |

| 41      | l <sub>5</sub>    | 83      | GND             | 125     | GND               | 167     | BREQ               |

| 42      | 14                | 84      | Vcc             | 126     | GND               | 168     | GND                |

# PQFP PIN DESIGNATIONS (Sorted by Pin Name)

| Pin Name       | Pin No. | Pin Name        | Pin No. | Pin Name        | Pin No. | Pin Name          | Pin No. |

|----------------|---------|-----------------|---------|-----------------|---------|-------------------|---------|

| Ao             | 112     | D4              | 53      | GND             | 103     | INCLK             | 3       |

| A <sub>1</sub> | 111     | D <sub>5</sub>  | 54      | GND             | 125     | <b>INTR</b> ₀     | 156     |

| A2             | 124     | Ds              | 55      | GND             | 126     | ĪNTR <sub>1</sub> | 157     |

| Аз             | 123     | D <sub>7</sub>  | 56      | GND             | 127     | INTR <sub>2</sub> | 158     |

| Aı             | 122     | Da              | 57      | GND             | 151     | INTR <sub>3</sub> | 159     |

| A5             | 121     | D <sub>0</sub>  | 58      | GND             | 153     | IRDY              | 162     |

| As             | 120     | Dto             | 59      | GND             | 168     | IREQ              | 144     |

| A7             | 119     | Dii             | 60      | lo              | 48      | IREQT             | 132     |

| _As            | 118     | D <sub>12</sub> | 61      | lı .            | 46      | LOCK              | 139     |

| A.             | 117     | D13             | 62      | 12              | 45      | MPGM <sub>0</sub> | 113     |

| A10            | 110     | D14             | 63      | la              | 44      | MPGM <sub>1</sub> | 114     |

| A11            | 109     | D15             | 66      | 4               | 42      | MSERR             | 136     |

| A12            | 108     | D16             | 67      | ls              | 41      | OPT <sub>0</sub>  | 128     |

| A13            | 107     | D <sub>17</sub> | 68      | 16              | 40      | OPT <sub>1</sub>  | 129     |

| A14            | 106     | D <sub>18</sub> | 69      | 17              | 39      | OPT <sub>2</sub>  | 130     |

| A15            | 102     | D19             | 70      | la              | 38      | PDA               | 142     |

| A16            | 101     | D <sub>20</sub> | 71      | le le           | 37      | PEN               | 166     |

| A17            | 100     | D <sub>21</sub> | 72      | l10             | 36      | PIA               | 143     |

| Ate            | 99      | D22             | 73      | l11             | 35      | PWRCLK            | 4       |

| Ate            | 98      | D23             | 74      | 112             | 34      | R/W               | 140     |

| A20            | 97      | D24             | 75      | l13             | 33      | RESET             | 9       |

| A21            | 96      | D <sub>25</sub> | 76      | l <sub>14</sub> | 32      | STAT <sub>0</sub> | 133     |

| A22            | 95      | D26             | 77      | 115             | 31      | STAT              | 134     |

| A23            | 94      | D <sub>27</sub> | 78      | l16             | 30      | STAT2             | 135     |

| A24            | 93      | D <sub>28</sub> | 79      | l <sub>17</sub> | 29      | SUP/US            | 131     |

| A25            | 92      | D <sub>29</sub> | 80      | lse             | 28      | SYSCLK            | 5       |

| A26            | 91      | D30             | 81      | f19             | 27      | TEST              | 12      |

| A27            | 90      | Dat             | 82      | 120             | 26      | TRAP <sub>0</sub> | 154     |

| A28            | 89      | DBACK           | 165     | l <sub>21</sub> | 25      | TRAP <sub>1</sub> | 155     |

| A29            | 88      | DBREQ           | 146     | 122             | 24      | Vcc               | 7       |

| A30            | 87      | DERR            | 164     | 123             | 23      | Vcc               | 22      |

| A31            | 86      | DRDY            | 1       | 124             | 20      | Vcc               | 43      |

| BGRT           | 145     | DREQ            | 141     | 125             | 19      | Vcc               | 64      |

| BINV           | 148     | DREQT₀          | 137     | 126             | 18      | Vcc               | 84      |

| BREQ           | 167     | DREQT           | 138     | 127             | 17      | Vcc               | 104     |

| CDA            | 2       | GND             | 6       | 128             | 16      | Vcc               | 105     |

| CNTL           | 10      | GND             | 8       | 129             | 15      | Vcc               | 115     |

| CNTL           | 11      | GND             | 21      | 130             | 14      | Vcc               | 116     |

| D₀             | 49      | GND             | 47      | l <sub>31</sub> | 13      | Vcc               | 149     |

| D <sub>1</sub> | 50      | GND             | 65      | IBACK           | 161     | Vcc               | 150     |

| D <sub>2</sub> | 51      | GND             | 83      | IBREQ           | 147     | Vcc               | 152     |

| D <sub>3</sub> | 52      | GND             | 85      | IERR            | 163     | WARN              | 160     |

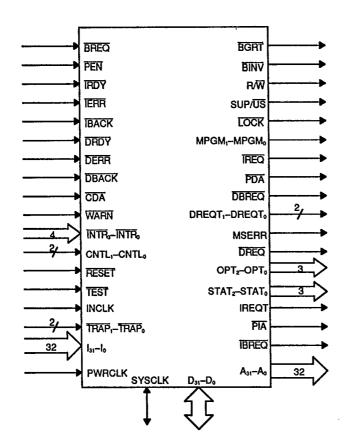

LOGIC SYMBOL

T-49-17-32

#### PIN DESCRIPTION

Although certain outputs are described as being threestate or bidirectional outputs, all outputs (except MSERR) may be placed in a high-impedance state by the Test mode. The three-state and bidirectional terminology in this section is for those outputs (except SYSCLK) that are disabled when the processor grants the channel to another master.

### A<sub>31</sub>--A<sub>0</sub>

# Address Bus (Three-state Outputs, Synchronous)

The Address Bus transfers the byte address for all accesses except burst-mode accesses. For burst-mode accesses, it transfers the address for the first access in the sequence.

### **BGRT**

### **Bus Grant (Output, Synchronous)**

This output signals to an external master that the processor is relinquishing control of the channel in response to BREQ.

## BINV

# **Bus Invalid (Output, Synchronous)**

This output indicates that the address bus and related controls are invalid. It defines an idle cycle for the channel.

#### BREQ

# **Bus Request (Input, Synchronous)**

This input allows other masters to arbitrate for control of the processor channel.

# CDA

## Coprocessor Data Accept (Input, Synchronous)

This signal allows the coprocessor to indicate the acceptance of operands or operation codes. For transfers to the coprocessor, the processor does not expect a DRDY response; an active level on CDA performs the function normally performed by DRDY. CDA may be active whenever the coprocessor is able to accept transfers.

# CNTL1-CNTL0

# **CPU Control (Inputs, Asynchronous)**

These inputs control the processor mode:

| CNTL, | CNTL₀ | Mode        |

|-------|-------|-------------|

| 0     | 0     | Load Test   |

|       |       | Instruction |

| 0     | 1     | Step        |

| 1     | 0     | Halt        |

| 1     | 1     | Normal      |

# D<sub>31</sub>-D<sub>0</sub>

# Data Bus (Bidirectionals, Synchronous)

The Data Bus transfers data to and from the processor for load and store operations.

# Data Burst Acknowledge (Input, Synchronous)

This input is active whenever a burst-mode data access has been established. It may be active even though no data are currently being accessed.

### DBREQ

#### Data Burst Request (Three-state Output, Synchronous)

This signal is used to establish a burst-mode data access and to request data transfers during a burst-mode data access. DBREQ may be active even though the address bus is being used for an instruction access. This signal becomes valid late in the cycle, with respect to DREQ.

### DERR

# Data Error (Input, Synchronous)

This input indicates that an error occurred during the current data access. For a load, the processor ignores the content of the data bus. For a store, the access is terminated. In either case, a Data Access Exception trap occurs. The processor ignores this signal if there is no pending data access.

# DRDY

# Data Ready (Input, Synchronous)

For loads, this input indicates that valid data is on the data bus. For stores, it indicates that the access is complete, and that data need no longer be driven on the data bus. The processor ignores this signal if there is no pending data access.

# DREQ

# Data Request (Three-state Output, Synchronous)

This signal requests a data access. When it is active, the address for the access appears on the address bus.

## DREQT\_-DREQTo

# **Data Request Type**

# (Three-state Outputs, Synchronous)

These signals specify the address space of a data access, as follows (the value "x" is a "don't care"):

| DREQT <sub>1</sub> | DREQT. | Meaning                       |

|--------------------|--------|-------------------------------|

| 0                  | 0      | Instruction/data              |

| 0                  | 1      | memory access<br>Input/output |

| 1                  | x      | access<br>Coprocessor         |

|                    |        | transfer                      |

An interrupt/trap vector request is indicated as a datamemory read. If required, the system can identify the vector fetch by the STAT2-STATo outputs. DREQT:-DREQTo are valid only when DREQ is active.

# 131-10

# Instruction Bus (inputs, Synchronous)

The Instruction Bus transfers instructions to the processor.

# **IBACK**

#### Instruction Burst Acknowledge (Input, Synchronous)

This input is active whenever a burst-mode instruction access has been established. It may be active even though no instructions are currently being accessed.

## Instruction Burst Request (Three-state **Output, Synchronous**)

This signal is used to establish a burst-mode instruction access and to request instruction transfers during a burst-mode instruction access. IBREQ may be active even though the address bus is being used for a data access. This signal becomes valid late in the cycle with respect to IREQ.

# **IERR**

#### Instruction Error (input, Synchronous)

This input indicates that an error occurred during the current instruction access. The processor ignores the content of the instruction bus, and an Instruction Access Exception trap occurs if the processor attempts to execute the invalid instruction. The processor ignores this signal if there is no pending instruction access.

### Input Clock (input)

When the processor generates the clock for the system, this is an oscillator input to the processor at twice the processor's operating frequency. In systems where the clock is not generated by the processor, this signal must be tied High or Low, except in certain master/slave configurations.

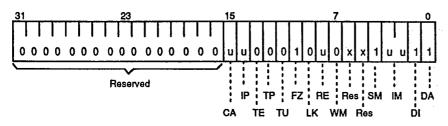

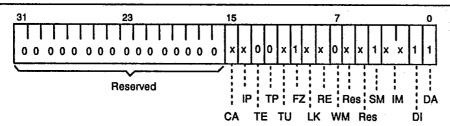

# INTR<sub>3</sub>-INTR<sub>0</sub>

# Interrupt Request (Inputs, Asynchronous)

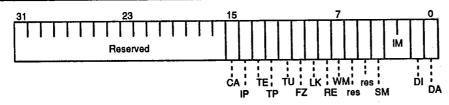

These inputs generate prioritized interrupt requests. The interrupt caused by  $\overline{INTR}_0$  has the highest priority, and the interrupt caused by INTRs has the lowest priority. The interrupt requests are masked in prioritized order by the Interrupt Mask field in the Current Processor Status Register.

# **IRDY**

# Instruction Ready (Input, Synchronous)

This input indicates that a valid instruction is on the instruction bus. The processor ignores this signal if there is no pending instruction access.

# **IREQ**

### **Instruction Request** (Three-state Output, Synchronous)

This signal requests an instruction access. When it is active, the address for the access appears on the address bus.

## **IREQT**

#### **Instruction Request Type** (Three-state Output, Synchronous)

This signal specifies the address space of an instruction request when IREQ is active:

| IREQT | Meaning                        |  |  |  |

|-------|--------------------------------|--|--|--|

| 0     | Instruction/data memory access |  |  |  |

| 1     | Instruction read-only memory   |  |  |  |

|       | access                         |  |  |  |

### LOCK

### Lock (Three-state Output, Synchronous)

This output allows the implementation of various channel and device interlocks. It may be active only for the duration of an access, or active for an extended period of time under control of the Lock bit in the Current Processor Status.

#### **MSERR**

### Master/Slave Error (Output, Synchronous)

This output shows the result of the comparison of processor outputs with the signals provided internally to the off-chip drivers. If there is a difference for any enabled driver, this line is asserted.

### MPGM,-MPGMo

# **MMU Programmable**

# (Three-state Outputs, Synchronous)

These outputs have no function in the Am29005 microprocessor, and always are driven Low on an access. They are defined to ensure pin compatibility with the Am29000™ microprocessor.

T-49-17-32

# OPT2-OPT₀

**Option Control**

(Three-state Outputs, Synchronous)

These outputs reflect the value of bits 18-16 of the load or store instruction that begins an access. Bit 18 of the instruction is reflected on OPT2, bit 17 on OPT1, and bit 16 on OPTo.

The standard definitions of these signals (based on DREQT) are as follows (the value "x" is a "don't care"):

| DREQT, | DREQT.   | OPT <sub>2</sub> | OPT, | OPT. | Meaning                                                   |

|--------|----------|------------------|------|------|-----------------------------------------------------------|

| 0      | ×        | 0                | 0    | 0    | Word-<br>length                                           |

| 0      | x        | 0                | 0    | 1    | access<br>Byte<br>access                                  |

| 0      | x        | 0                | 1    | 0    | Half-word access                                          |

| 0      | 0        | 1                | 0    | 0    | Instruction<br>ROM<br>access<br>(as data)                 |

| 0      | 0        | 1                | 0    | 1    | Cache<br>control                                          |

| 0      | 0<br>-al | 1<br>I others-   |      | 0    | Hardware-<br>developmen<br>system<br>accesses<br>Reserved |

During an interrupt/trap vector fetch, the OPT2-OPT0 signals indicate a word-length access (000). Also, the system should return an entire aligned word for a read, regardless of the indicated data length.

The Am29005 microprocessor does not explicitly prevent a store to the instruction ROM. OPT3-OPTo are valid only when DREQ is active.

# **Pipelined Data Access** (Three-state Output, Synchronous)

If DREQ is not active, this output indicates that a data access is pipelined with another in-progress data access. The indicated access cannot be completed until the first access is complete. The completion of the first access is signaled by the assertion of DREQ.

# Pipeline Enable (Input, Synchronous)

This signal allows devices that can support pipelined accesses (i.e., that have input latches for the address and required controls) to signal that a second access may begin while the first is being completed.

# **Pipelined Instruction Access** (Three-state Output, Synchronous)

If IREQ is not active, this output indicates that an instruction access is pipelined with another in-progress instruction access. The indicated access cannot be completed

until the first access is complete. The completion of the first access is signaled by the assertion of IREQ.

# Read/Write (Three-state Output, Synchronous)

This signal indicates whether data is being transferred from the processor to the system, or from the system to the processor. R/W is valid only when the address bus is valid. R/W will be High when IREQ is active.

### Reset (Input, Asynchronous)

This input places the processor in the Reset mode.

# STAT2-STAT

# CPU Status (Outputs, Synchronous)

These outputs indicate the state of the processor's execution stage on the previous cycle. They are encoded as follows:

| STAT <sub>2</sub> | STAT, | STAT. | Condition                                       |

|-------------------|-------|-------|-------------------------------------------------|

| 0                 | 0     | 0     | Halt or Step Modes                              |

| O                 | 0     | 1     | Pipeline Hold Mode                              |

| 0                 | 1     | 0.    | Load Test Instruc-<br>tion Mode,<br>Halt/Freeze |

| 0                 | 1     | 1     | Wait Mode                                       |

| 1                 | 0     | Ó     | Interrupt Return                                |

| 1                 | 0     | 1     | Taking Interrupt or<br>Trap                     |

| 1                 | 1     | 0     | Non-sequential<br>Instruction Fetch             |

| 1                 | 1     | 1     | Executing Mode                                  |

# SUP/US

# Supervisor/User Mode

(Three-state Output, Synchronous)

This output indicates the program mode for an access.

The processor does not relinquish the channel (in response to BREQ) when LOCK is active.

# SYSCLK

# System Clock (Bidirectional)

This is either a clock output with a frequency that is half that of INCLK, or an input from an external clock generator at the processor's operating frequency.

# TEST

# Test Mode (Input, Asynchronous)

When this input is active, the processor is in Test mode. All outputs and bidirectional lines, except MSERR, are forced to the high-impedance state.

# TRAP,-TRAP

# Trap Request (Inputs, Asynchronous)

These inputs generate prioritized trap requests. The trap caused by TRAPo has the highest priority. These trap requests are disabled by the DA bit of the Current Processor Status Register.

# WARN

# Warn (Input, Asynchronous, Edge-sensitive)

A High-to-Low transition on this input causes a non-maskable WARN trap to occur. This trap bypasses the normal trap vector fetch sequence, and is useful in situations where the vector fetch may not work (e.g., when data memory is faulty).

The following pin is not a signal pin, but is named in Am29005 microprocessor documentation because of its special role in the processor and system.

# **PWRCLK**

T-49-17-32

# **Power Supply for SYSCLK Driver**

This pin is a power supply for the SYSCLK output driver. It isolates the SYSCLK driver, and is used to determine whether or not the Am29005 microprocessor generates the clock for the system. If power (+5 V) is applied to this pin, the Am29005 microprocessor generates a clock on the SYSCLK output. If this pin is grounded, the Am29005 microprocessor accepts a clock generated by the system on the SYSCLK input.

T-49-17-32

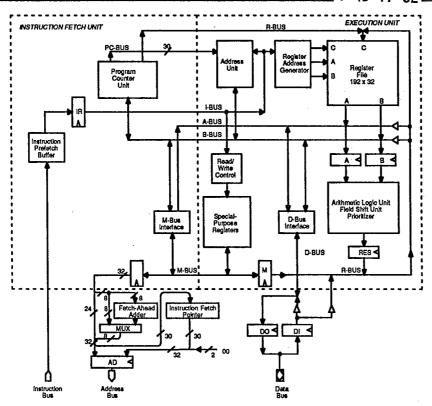

# **FUNCTIONAL DESCRIPTION Product Overview**

The Am29005 microprocessor contains a high-function execution unit, a large register file (192 locations), and a high-bandwidth, pipelined external channel with separate instruction and data buses. The flexible register file may be used as a cache for run-time variables during program execution, or as a collection of register banks allocated to separate tasks in multitasking applications.

The Am29005 microprocessor provides a significant margin of performance over other processors designed for cost-sensitive situations, since the majority of processor features were defined with the maximum achievable performance in mind. This section describes the features of the Am29005 microprocessor from the point of view of system performance.

# **Cycle Time**

The processor operates at a frequency of 16 MHz. The processor cycle time is a single, 62.5-ns clock period. The processor interface drivers can drive 80-pF loads at this frequency (for loads greater than 80 pF, refer to the Capacitive Output Delay table).

The Am29005 microprocessor architecture and system interfaces are designed so that the processor cycle time can decrease with technology improvements.

### Four-Stage Pipeline

The Am29005 microprocessor utilizes a four-stage pipeline, allowing it to execute one instruction every clock cycle. The processor can complete an instruction on every cycle, even though four cycles are required from the beginning of an instruction to its completion.

At the 16-MHz operating frequency, the maximum instruction execution rate is 16 million instructions per second (MIPS). The Am29005 microprocessor pipeline is designed so that the Am29005 microprocessor can operate at the maximum instruction execution rate a significant portion of the time.

Pipeline interlocks are implemented by processor hardware. Except for a few special cases, it is not necessary to rearrange programs to avoid pipeline dependencies.

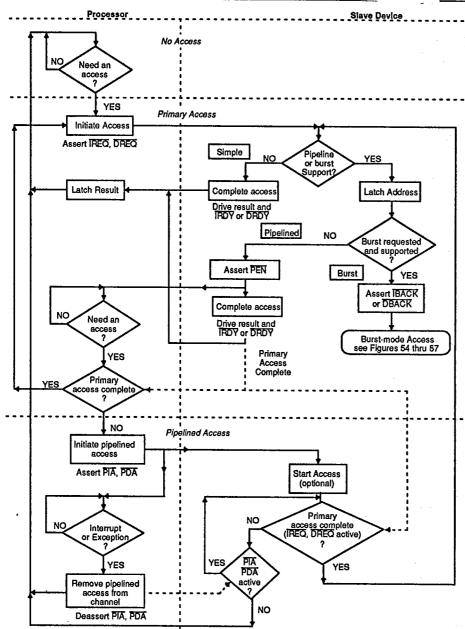

# System Interface

The Am29005 microprocessor accesses external instructions and data using three non-multiplexed buses. These buses are referred to collectively as the channel. The channel protocol minimizes the logic chains involved in a transfer, and provides a maximum transfer rate of 128 Mb/s.

# Separate Address, Instruction, and Data Buses

The Am29005 microprocessor incorporates two 32-bit buses for instruction and data transfers, and a third address bus that is shared between instruction and data accesses. This bus structure allows simultaneous instruction and data transfers, even though the address

bus is shared. The channel achieves the performance of four separate 32-bit buses at a much-reduced pin count.

### **Pipelined Addresses**

The Am29005 microprocessor address bus is pipelined so that it can be released before an instruction or data transfer is completed. This allows a subsequent access to begin before the first has been completed, and allows the processor to have two accesses in progress simultaneously.

# Support of Burst Devices and Memories

Burst-mode accesses provide high transfer rates for instructions and data at sequential addresses. For such accesses, the address of the first instruction or datum is sent, and subsequent requests for instructions or data at sequential addresses do not require additional address transfers. These instructions or data are transferred until either party involved in the transfer terminates the access.

Burst-mode accesses can occur at the rate of one access per cycle after the first address has been processed. At 16 MHz, the maximum achievable transfer bandwidth for either instructions or data is 64 Mb/s.

Burst-mode accesses may occur to input/output devices if the system design permits.

#### Interface to Fast Devices and Memories

The processor can be interfaced to devices and memories that complete accesses within one cycle. The channel protocol takes maximum advantage of such devices and memories by allowing data to be returned to the processor during the cycle in which the address is transmitted. This allows a full range of memory-speed tradeoffs to be made within a particular system.

# Register File

An on-chip Register File containing 192 generalpurpose registers allows most instruction operands to be fetched without the delay of an external access. The Register File incorporates several features that aid the retention of data required by an executing program. Because of the number of general-purpose registers, the frequency of external references for the Am29005 microprocessor is significantly lower than the frequency of references in processors having only 16 or 32 registers.

Triple-port access to the Register File allows two source operands to be fetched in one cycle while a previously computed result is written. Three 32-bit internal buses prevent contention in the routing of operands. All operand fetches and result write-backs for instruction execution can be performed in a single cycle.

The registers allow efficient procedure linkage by caching a portion of a compiler's run-time stack. On the average, procedure calls and returns can be executed 5 to 10 times faster (on a cycle-by-cycle basis) than in

T-49-17-32 AMD

processors that require the implementation of a run-time stack in external memory (with the attendant loading and storing of registers on procedure call and return).

The registers can contain variables, constants, addresses, and operating-system values. In multitasking applications, they can be used to hold the processor status and variables for as many as eight different tasks. A register-banking option allows the Register File to be divided into segments, which can be individually protected. In this configuration, a task switch can occur in as few as 17 cycles.

#### Instruction Execution

The Am29005 microprocessor uses an Arithmetic/Logic Unit, a Field Shift Unit, and a Prioritizer to execute most instructions. Each of these is organized to operate on 32-bit operands and provide a 32-bit result. All operations are performed in a single cycle.

Instruction operations are overlapped with operand fetch and result write-back to the Register File. Pipeline forwarding logic detects pipeline dependencies and routes data as required, avoiding delays that might arise from these dependencies.

# **Branching**

Branch conditions in the Am29005 microprocessor are based on Boolean data contained in general-purpose registers rather than on arithmetic condition codes. Using a condition-code register for the purpose of branching-which is common in other processors-inhibits certain compiler optimizations because the conditioncode register is modified by many different instructions. It is difficult for an optimizing compiler to schedule this shared use. By treating branch conditions as any other instruction operand, the Am29005 microprocessor avoids this problem.

### **Loads and Stores**

The performance degradation of load and store operations is minimized in the Am29005 microprocessor by overlapping them with instruction execution, by taking advantage of pipelining, and by organizing the flow of external data onto the processor so that the impact of external accesses is minimized.

# Overlapped Loads and Stores

In the Am29005 microprocessor, a load or store is performed concurrently with execution of instructions that do not have dependencies on the load or store operation. An optimizing compiler can schedule loads and stores in the instruction sequence so that, in most cases, data accesses are overlapped with instruction execution.

Overlapped load and store operations can achieve up to a 30% improvement in performance when data memory has a two-cycle access time. Processor hardware detects dependencies while overlapped loads and stores are being performed, so dependencies have no software implications.

The Am29005 microprocessor exception restart mechanism automatically saves information required to restart any load or store until the operation is successfully completed. Thus, it allows the overlapped execution of loads and stores while properly handling address-translation exceptions.

The Am29005 microprocessor data-flow organization avoids the one-cycle penalty that would result from the contention between load data and the results of overlapped instruction execution. Load data is buffered in a latch while awaiting an opportunity to be written into the register file. This opportunity is guaranteed to arise before the next load is executed. While the data is buffered in this latch, it may be used as an instruction operand in place of the destination register for the load.

#### Load Multiple and Store Multiple.

Load Multiple and Store Multiple instructions allow the transfer of the contents of multiple registers to or from external memories or devices. This transfer can occur at a rate of one register content per cycle.

The advantage of Load Multiple and Store Multiple is best seen in task switching, in register-file saving and restoring, and in block data moves. In many systems, such operations require a significant percentage of execution time.

The Load Multiple and Store Multiple sequences are interruptible so that they do not affect interrupt latency.

### Forwarding of Load Data

Data that are sent to the processor at the completion of a load are forwarded directly to the appropriate execution unit if the data are required immediately by an instruction. This avoids the common one-cycle delay from bus transfer to use of data, and reduces the access latency of external data by one cycle.

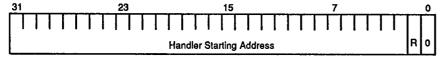

# Interrupts and Traps

When the Am29005 microprocessor takes an interrupt or trap, it does not automatically save its current state information. This greatly improves the performance of temporary interruptions such as floating-point emulation or other simple operating-system calls that require no saving of state information.

In cases where the processor state must be saved, the saving and restoring of state information is under the control of software. The methods and data structures used to handle interrupts-and the amount of state saved-may be tailored to the needs of a particular system.

Interrupts and traps are dispatched through a 256-entry Vector Area, which directs the processor to a routine to handle a given interrupt or trap. The Vector Area may be

T-49-17-32

relocated in memory by the modification of a processor register. There may be multiple Vector Areas in the system, though only one is active at any given time.

The Vector Area is either a table of pointers to the interrupt and trap handlers, or a segment of instruction memory (possibly read-only memory) containing the handlers themselves. The choice between the two possible Vector Area definitions is determined by the cost/performance trade-offs made for a particular system.

If the Vector Area is a table of vectors in data memory, it requires only 1 kb of memory. However, this structure requires that the processor perform a vector fetch every time an interrupt or trap is taken. The vector fetch requires at least three cycles in addition to the number of cycles required for the basic memory access.

If the Vector Area is a segment of instruction memory, it requires a maximum of 64 kb of memory. The advantage of this structure is that the processor begins the execution of the interrupt or trap handler in the minimum amount of time.

# Floating-Point Arithmetic Unit

The Am29027 arithmetic accelerator is a double-precision, floating-point arithmetic unit for the Am29005 microprocessor. It can provide an order-of-magnitude performance increase over floating-point operations performed in software. It performs both single-precision and double-precision operations using IEEE and other floating-point formats. The Am29027 arithmetic accelerator also supports 32- and 64-bit integer functions.

The Am29027 arithmetic accelerator performs floatingpoint operations using combinatorial-rather than sequential-logic; therefore, operations with the Am29027 arithmetic accelerator require only five Am29005 microprocessor cycles. Floating-point operations may be overlapped with other processor operations. Furthermore, the Am29027 arithmetic accelerator incorporates pipeline registers and eight operand registers, permitting very high throughput for certain types of operations (such as array computations).

The Am29027 arithmetic accelerator attaches directly to the Am29005 microprocessor using the coprocessor interface. The Am29005 microprocessor can transfer two 32-bit quantities to the Am29027 arithmetic accelerator in one cycle.

The Am29027 arithmetic accelerator is described in detail in the Am29027 Arithmetic Accelerator Data Sheet (order #09114) and the Am29027 Handbook (order #11852).

# **ARCHITECTURE HIGHLIGHTS**

This section introduces the principle architectural elements, hardware features, and system interfaces of the Am29005 microprocessor.

# **Architecture Overview**

This section gives a brief description of the Am29005 microprocessor from a programmer's point of view. It introduces the processor's program modes, registers, and instructions. An overview of the processor's data formats and handling is given. This section also briefly describes interrupts and traps, and the coprocessor interface. Finally, the Timer Facility and Trace Facility are introduced.

# **Program Modes**

There are two mutually exclusive modes of program execution: the Supervisor mode and the User mode. In the Supervisor mode, executing programs have access to all processor resources. In the User mode, certain processor resources may not be accessed; any attempted access causes a trap.

# **Visible Registers**

The Am29005 microprocessor incorporates two classes of registers that are accessed and manipulated by instructions: general-purpose registers, and special-purpose registers. (Refer to the Register Description section for greater detail of the register categories.)

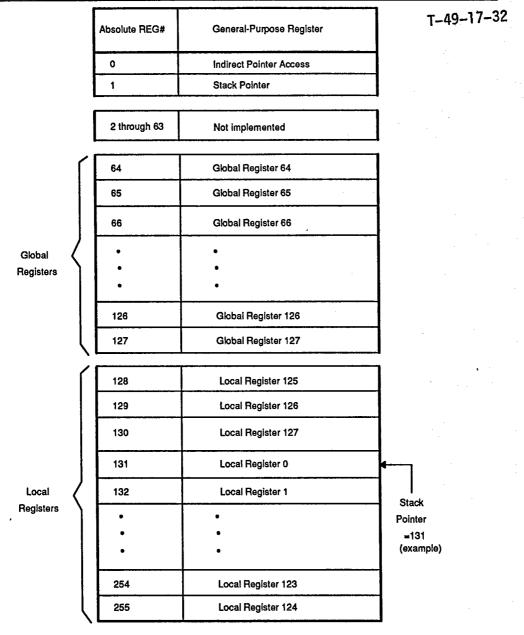

#### **General-Purpose Registers**

The Am29005 microprocessor has 192 generalpurpose registers. With a few exceptions, generalpurpose registers are not dedicated to any special use and are available for any appropriate program use.

Most processor instructions are three-address instructions. An instruction specifies any three of the 192 registers for use in instruction execution. Normally, two of these registers contain source operands for the instruction, and a third stores the result of the instruction.

The 192 registers are divided into 64 global and 128 local registers. Global registers are addressed with absolute register numbers, while local registers are addressed relative to an internal Stack Pointer.

For fast procedure calling, a portion of a compiler's runtime stack can be mapped into the local registers. Statically allocated variables, temporary values, and operating-system parameters are kept in the global registers.

The Stack Pointer for local registers is mapped to Global Register 1. The Stack Pointer is a full 32-bit virtual address for the top of the run-time stack.

The general-purpose registers may be accessed indirectly, with the register number specified by the content of a special-purpose register (see below) rather than by an instruction field. Three independent indirect register numbers are contained in three separate special-purpose registers. Indirect addressing is accomplished by specifying Global Register 0 as an

instruction operand or result register. An instruction can specify an indirect register access for any or all of the source operands or result.

General-purpose registers may be partitioned into segments of 16 registers for the purpose of access protection. A register in a protected segment may be accessed only by a program executing in the Supervisor mode. An attempted access (either read or write) by a User-mode program causes a trap to occur.

#### Special-Purpose Registers

The Am29005 microprocessor contains 25 special-purpose registers. These registers provide controls and data for certain processor functions.

Special-purpose registers are accessed by data movement only. Any special-purpose register can be written with the contents of any general-purpose register, and any general-purpose register can be written with the contents of any special-purpose register. Operations cannot be performed directly on the contents of specialpurpose registers.

Some special-purpose registers are protected, and can be accessed only in the Supervisor mode. This restriction applies to both read and write accesses. An attempt by a User-mode program to access a protected register causes a trap to occur.

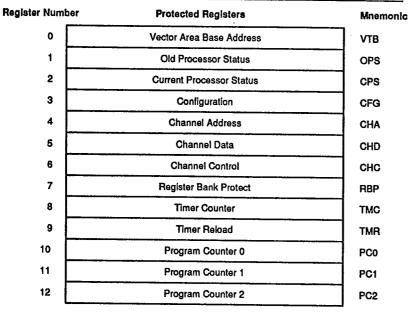

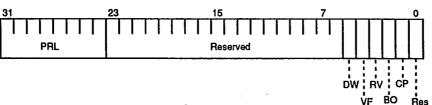

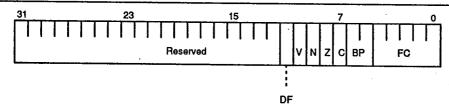

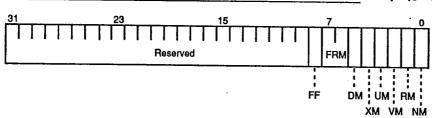

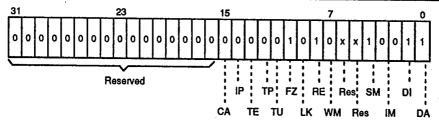

The protected special-purpose registers are defined as follows:

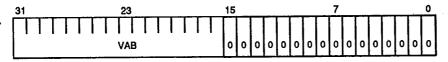

- 1. Vector Area Base Address-Defines the beginning of the interrupt/trap Vector Area.

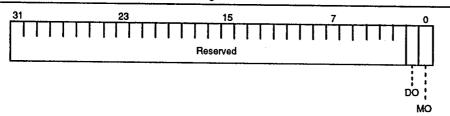

- 2. Old Processor Status-Receives a copy of the Current Processor Status (see below) when an interrupt or trap is taken, it is later used to restore the Current Processor Status on an interrupt

- Current Processor Status—Contains control information associated with the currently executing process, such as interrupt disables and the Supervisor Mode bit.

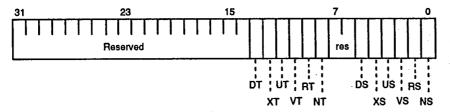

- 4. Configuration—Contains control tion that normally varies only from system to system, and usually is set only during system initialization.

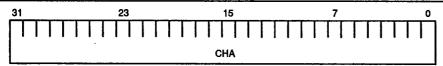

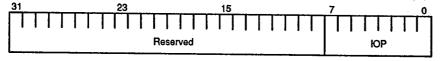

- 5. Channel Address—Contains the address associated with an external access, and retains the address if the access is not completed successfully. The Channel Address Register, in conjunction with the Channel Data and Channel Control registers described below, allows the restarting of unsuccessful external accesses. This might be necessary for an access encountering a page fault in a demand-paged environment, for example.

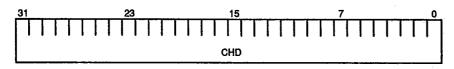

- 6. Channel Data---Contains data associated with a store operation, and retains the data if the operation is not completed successfully.

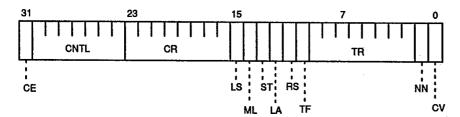

- 7. Channel Control—Contains control information associated with a channel operation, and retains this information if the operation is not completed successfully.

- 8. Register Bank Protect-Restricts access of user-mode programs to specified groups of 16 registers. This facilitates register banking for multitasking applications, and protects operating system parameters kept in the global registers from corruption by user-mode programs.

- 9. Timer Counter-Supports real-time control and other timing-related functions.

- 10. Timer Reload-Maintains synchronization of the Timer Counter. It includes control bits for the Timer Facility.

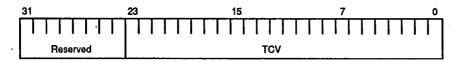

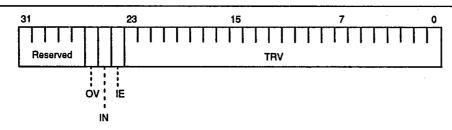

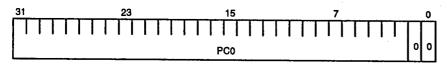

- 11. Program Counter 0-Contains the address of the instruction being decoded when an interrupt or trap is taken. The processor restarts this instruction upon interrupt return.

- 12. Program Counter 1—Contains the address of the instruction being executed when an interrupt or trap is taken. The processor restarts this instruction upon interrupt return.

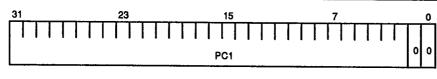

- 13. Program Counter 2-Contains the address of the instruction just completed when an interrupt or trap is taken. This address is provided for information only, and does not participate in an interrupt return.

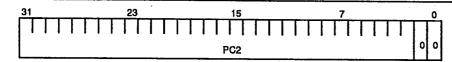

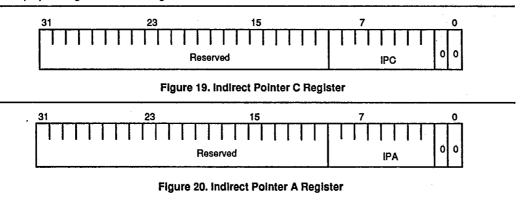

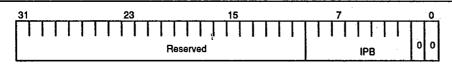

The unprotected special-purpose registers are defined as follows:

- 1. Indirect Pointer C-Allows the indirect access of a general-purpose register.

- 2. Indirect Pointer A-Allows the indirect access of a general-purpose register.

- 3. Indirect Pointer B-Allows the indirect access of a general-purpose register.

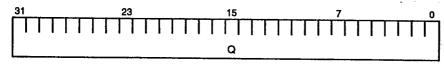

- 4. Q-Provides additional operand bits for multiply step, divide step, and divide operations.

- 5. ALU Status-Contains information about the outcome of integer arithmetic and logical operations, and holds residual control for certain instruction operations.

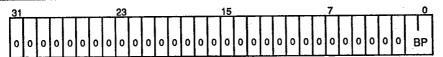

- 6. Byte Pointer-Contains an index of a byte or half-word within a word. This register is also accessible via the ALU Status Register.

instructions and a general-purpose register. Relative

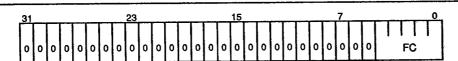

- 7. Funnel Shift Count—Provides a bit offset for the extraction of word-length fields from doubleword operands. This register is also accessible via the ALU Status Register.

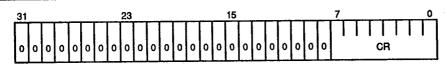

- 8. Load/Store Count Remaining-Maintains a count of the number of loads and stores remaining for Load Multiple and Store Multiple operations. The count is initialized to the total number of loads or stores to be performed before the operation is initiated. This register is also accessible via the Channel Control Register.

- 9. Floating-Point Environment-Controls the operation of floating-point arithmetic, such as rounding modes and exception reporting.

- 10. Integer Environment—Enables and disables the reporting of exceptions that occur during integer multiply and divide operations.

- 11. Floating-Point Status-Contains information about the outcome of floating-point operations.

- 12. Exception Opcode—Reports the operation code of an instruction causing a trap. This register is provided primarily for recovery from floatingpoint exceptions, but is also set for other instructions that cause traps.

# Instruction Set Overview

The three-address architecture of the Am29005 microprocessor instruction set allows a compiler or assemblylanguage programmer to prevent the destruction of operands, and aids register allocation and operand reuse. Instruction operands may be contained in any 2 of the 192 general purpose registers, and instruction results may be stored in any of the 192 general-purpose

The compiler or assembly-language programmer has complete freedom to allocate register usage. There is no dedication of a particular register or register group to a particular class of operations. The instruction set is designed to minimize the number of side effects and implicit operations of instructions.

Most Am29005 microprocessor instructions can specify an 8-bit constant as one of the source operands. Larger constants are constructed using one or two additional branch instructions specify a 16-bit, signed, word offset. Absolute branches specify a 16-bit word address.

The Am29005 microprocessor instruction set contains 113 instructions. These instructions are divided into nine classes:

- 1. Integer Arithmetic-Perform integer add, subtract, multiply, and divide operations.

- 2. Compare—Perform arithmetic and logical comparisons. Some instructions in this class allow the generation of a trap if the comparison condition is not met.

- 3. Logical-Perform a set of bit-wise Boolean operations.

- 4. Shift—Perform arithmetic and logical shifts, and allow the extraction of 32-bit words from 64-bit double words.

- 5. Data Movement-Perform movement of data fields between registers, and the movement of data to and from external devices and memories.

- 6. Constant-Allow the generation of large constant values in registers.

- 7. Floating-Point—Included for floating-point arithmetic, comparisons, and format conversions. These instructions are not currently implemented directly in processor hardware.

- 8. Branch-Perform program jumps and subroutine calls.

- 9. Miscellaneous—Perform miscellaneous control functions and operations not provided by other classes

The Am29005 microprocessor executes all instructions in a single cycle, except for interrupt returns, Load Multiple, and Store Multiple.

Figure 1 shows a complete list of Am29005 microprocessor instructions, listed alphabetically by instruction mnemonic (refer to the Instruction Set section for more

| Mnemonic      | Instruction Name                                                                                        |

|---------------|---------------------------------------------------------------------------------------------------------|

| ADD           | Add                                                                                                     |

| ADDC          | Add with Carry                                                                                          |

| ADDCS         | Add with Carry, Signed                                                                                  |

| ADDCU         | Add with Carry, Unsigned                                                                                |

| ADDS          | Add, Signed                                                                                             |

| ADDU<br>AND   | Add, Unsigned<br>AND Logical                                                                            |

| ANDN          | AND-NOT Logical                                                                                         |

| ASEQ          | Assert Equal To                                                                                         |

| ASGE          | Assert Greater Than or Equal To                                                                         |

| ASGEU         | Assert Greater Than or Equal To, Unsigned                                                               |

| ASGT          | Assert Greater Than                                                                                     |

| ASGTU         | Assert Greater Than, Unsigned                                                                           |

| ASLE<br>ASLEU | Assert Less Than or Equal To Assert Less Than or Equal To, Unsigned                                     |

| ASLE          | Assert Less Than or Equal 10, Onsigned  Assert Less Than                                                |

| ASLTU         | Assert Less Than, Unsigned                                                                              |

| ASNEQ         | Assert Not Equal To                                                                                     |

| CALL          | Call Subroutine                                                                                         |

| CALLI         | Call Subroutine, Indirect                                                                               |

| CLASS         | Classify Floating-Point Operand                                                                         |

| CLZ           | Count Leading Zeros                                                                                     |

| CONST         | Constant Constant, High                                                                                 |

| CONSTH        | Constant, Right Constant, Negative                                                                      |

| CONVERT       | Convert Data Format                                                                                     |

| CPBYTE        | Compare Bytes                                                                                           |

| CPEQ          | Compare Equal To                                                                                        |

| CPGE          | Compare Greater Than or Equal To                                                                        |

| CPGEU         | Compare Greater Than or Equal To, Unsigned                                                              |

| CPGT          | Compare Greater Than                                                                                    |

| CPGTU<br>CPLE | Compare Greater Than, Unsigned Compare Less Than or Equal To                                            |

| CPLEU         | Compare Less Than or Equal To, Unsigned                                                                 |

| CPLT          | Compare Less Than                                                                                       |

| CPLTU         | Compare Less Than, Unsigned                                                                             |

| CPNEQ         | Compare Not Equal To                                                                                    |

| DADD          | Floating-Point Add, Double-Precision                                                                    |

| DDIV          | Floating-Point Divide, Double-Precision                                                                 |

| DEQ           | Floating-Point Equal To, Double-Precision                                                               |

| DGE           | Floating-Point Greater Than or Equal To, Double-Precision Floating-Point Greater Than, Double-Precision |

| DIV           | Divide Step                                                                                             |

| OVIG          | Divide Initialize                                                                                       |

| DIVIDE        | Integer Divide, Signed                                                                                  |

| DIVIDU        | Integer Divide, Unsigned                                                                                |

| DIVL          | Divide Last Step                                                                                        |

| DIVREM        | Divide Remainder                                                                                        |

| DMUL          | Floating-Point Multiply, Double-Precision Floating-Point Subtract, Double-Precision                     |

| EMULATE       | Trap to Software Emulation Routine                                                                      |

| EXBYTE        | Extract Byte                                                                                            |

| EXHW          | Extract Half-Word                                                                                       |

| EXHWS         | Extract Half-Word, Sign-Extended                                                                        |

| EXTRACT       | Extract Word, Bit-Aligned                                                                               |

| FADD          | Floating-Point Add, Single-Precision                                                                    |

| FDIV          | Floating-Point Divide, Single-Precision                                                                 |

| FDMUL         | Floating-Point Multiply, Single-to-Double Precision Floating-Point Equal To, Single-Precision           |

| FEQ<br>FGE    | Floating-Point Equal To, Single-Precision Floating-Point Greater Than or Equal To, Single-Precision     |

| 100           | - Mainig-1 ont Greater Than or Equal to, Single-Treosoft                                                |

Figure 1. Am29005 Microprocessor Instruction Set

- T-49-17-32

| Mnemonic     | Instruction Name                                 |

|--------------|--------------------------------------------------|

|              |                                                  |

| FGT          | Floating-Point Greater Than, Single-Precision    |

| FMUL         | Floating-Point Multiply, Single-Precision        |

| FSUB<br>HALT | Floating-Point Subtract, Single-Precision        |

| INBYTE       | Enter Halt Mode                                  |

| INHW         | Insert Byte Insert Half-Word                     |

| IRET         | Insert Hair-vyord Interrupt Return               |

| JMP          | Jump                                             |

| JMPF         | Jump Faise                                       |

| JMPFDEC      | Jump False and Decrement                         |

| JMPFI        | Jump False Indirect                              |

| JMPI         | Jump Indirect                                    |

| JMPT         | Jump True                                        |

| JMPTI        | Jump True Indirect                               |

| LOAD         | Load                                             |

| LOADL        | Load and Lock                                    |

| LOADM        | Load Multiple                                    |

| LOADSET      | Load and Set                                     |

| MFSR         | Move from Special Register                       |

| MTSR         | Move to Special Register                         |

| MTSRIM       | Move to Special Register Immediate               |

| MUL          | Multiply Step                                    |

| MULL         | Multiply Last Step                               |

| MULTIPLU     | Integer Multiply, Unsigned                       |

| MULTIPLY     | Integer Multiply, Signed                         |

| MULTM        | Integer Multiply Most-Significant Bits, Signed   |

| MULTMU       | Integer Multiply Most-Significant Bits, Unsigned |

| MULU         | Multiply Step, Unsigned                          |

| NAND<br>NOR  | NAND Logical                                     |

| OR           | NOR Logical                                      |

| SETIP        | OR Logical Set Indirect Pointers                 |

| SLL          | Shift Left Logical                               |