# 8-Bit, 1 GSPS, JESD204B, Quad Analog-to-Digital Converter

**Preliminary Technical Data**

AD9094

#### **FEATURES**

JESD204B (Subclass 1) coded serial digital outputs

Lane rates up to 15 Gbps

1.74 W total power at 1 GSPS

435 mW per ADC channel

SFDR = TBD dBFS at 305 MHz (1.80 V p-p input range)

SNR = TBD dBFS at 305 MHz (1.80 V p-p input range)

Noise density = -151.5 dBFS/Hz (1.80 V p-p input range)

0.975 V, 1.8 V, and 2.5 V dc supply operation

No missing codes

Internal ADC voltage reference

Analog input buffer

On-chip dithering to improve small signal linearity

1.44 V p-p to 2.16 V p-p (1.80 V p-p nominal)

Flexible differential input range

1.4 GHz analog input full power bandwidth

Amplitude detect bits for efficient AGC implementation

4 integrated wideband digital processors

48-bit NCO, up to 4 cascaded half-band filters

Differential clock input

Integer clock divide by 1, 2, 4, or 8

On-chip temperature diode

Flexible JESD204B lane configurations

#### **APPLICATIONS**

LIDAR

Communications

DSO

Ultrawideband satellite receivers

Instrumentation

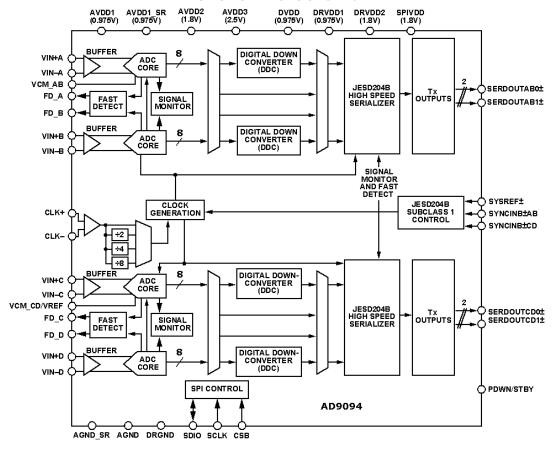

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

Rev. PrC

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2019 Analog Devices, Inc. All rights reserved.

Technical Support www.analog.com

## **Preliminary Technical Data**

### **TABLE OF CONTENTS**

| Features                                    | 1 |

|---------------------------------------------|---|

| Applications                                | 1 |

| Functional Block Diagram                    | 1 |

| General Description                         | 3 |

| Product Highlights                          | 3 |

| Specifications                              | 4 |

| DC Specifications                           | 4 |

| Digital Specifications                      | 5 |

| Timing Specifications                       | 6 |

| Absolute Maximum Ratings                    | 7 |

| Thermal Resistance                          | 7 |

| ESD Caution                                 | 7 |

| Pin Configuration and Function Descriptions | 8 |

| Typical Performance Characteristics         | 0 |

| Equivalent Circuits                                   | ١I |

|-------------------------------------------------------|----|

| ADC Overrange and Fast Detect 1                       | 13 |

| ADC Overrange1                                        | 13 |

| Fast Threshold Detection (FD_A, FD_B, FD_C, and FD_D) |    |

|                                                       | 13 |

| Configuring the JESD204B Link1                        |    |

| Latency 1                                             | 15 |

| End to End Total Latency                              | 15 |

| Example Latency Calculations 1                        | 15 |

| LMFC referenced Latency 1                             | 15 |

| Memory Map 1                                          | 6  |

| Reading the Memory Map Register Table 1               | 16 |

| Memory Map Register Table—Details 1                   | 17 |

| Outline Dimensions                                    | 10 |

#### **GENERAL DESCRIPTION**

The AD9094 is a quad, 8-bit, 1 GSPS analog-to-digital converter (ADC). The device has an on-chip buffer and a sample-and-hold circuit designed for low power, small size, and ease of use. This device is designed for sampling wide bandwidth analog signals of up to 1.4 GHz. The AD9094 is optimized for wide input bandwidth, high sampling rate, excellent linearity, and low power in a small package.

The quad ADC cores feature a multistage, differential pipelined architecture with integrated output error correction logic. Each ADC features wide bandwidth inputs supporting a variety of user-selectable input ranges. An integrated voltage reference eases design considerations.

The analog inputs and clock signals are differential inputs. Each pair of ADC data outputs is internally connected to two DDCs through a crossbar mux. Each DDC consists of up to five cascaded signal processing stages: a 48-bit frequency translator, NCO, and up to four half-band decimation filters.

In addition to the DDC blocks, the AD9094 has several functions that simplify the automatic gain control (AGC) function in the communications receiver. The programmable threshold detector allows monitoring of the incoming signal power using the fast detect output bits of the ADC. If the input signal level exceeds the programmable threshold, the fast detect indicator goes high. Because this threshold indicator has low latency, the user can quickly turn down the system gain to avoid an overrange condition at the ADC input.

Users can configure each pair of intermediate frequency (IF) receiver outputs onto either one or two lanes of Subclass 1 JESD204B-based high speed serialized outputs, depending on the decimation ratio and the acceptable lane rate of the receiving logic device. Multiple device synchronization is supported through the SYSREF±, SYNCINB±AB, and SYNCINB±CD input pins.

The AD9094 has flexible power-down options that allow significant power savings when desired. All of these features can be programmed using the 1.8 V capable, 3-wire SPI.

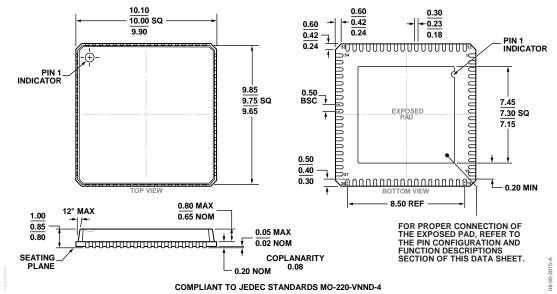

The AD9094 is available in a Pb-free, 72-lead LFCSP and is specified over the  $-40^{\circ}$ C to  $+105^{\circ}$ C junction temperature range. This product may be protected by one or more U.S. or international patents.

#### **PRODUCT HIGHLIGHTS**

- 1. Low power consumption per channel.

- 2. JESD204B lane rate support up to 15 Gbps.

- 3. Wide full power bandwidth supports IF sampling of signals up to 1.4 GHz.

- 4. Buffered inputs ease filter design and implementation.

- Four integrated wideband decimation filters and numerically controlled oscillator (NCO) blocks supporting multiband receivers.

- 6. Programmable fast overrange detection.

- 7. On-chip temperature diode for system thermal management.

## SPECIFICATIONS DC SPECIFICATIONS

$AVDD1 = 0.975\ V,\ AVDD1\_SR = 0.975\ V,\ AVDD2 = 1.8\ V,\ AVDD3 = 2.5\ V,\ DVDD = 0.975\ V,\ DRVDD1 = 0.975\ V,\ DRVDD2 = 1.8\ V,\ SPIVDD = 1.8\ V,\ 500$  MSPS, clock divider = 4, 1.80 V p-p full-scale differential input, 0.5 V internal reference,  $A_{IN} = -1.0$  dBFS, default SPI settings, unless otherwise noted. Minimum and maximum specifications are guaranteed for the full operating junction temperature ( $T_{IJ}$ ) range of  $-40^{\circ}$ C to  $+105^{\circ}$ C. Typical specifications represent performance at  $T_{IJ} = 50^{\circ}$ C ( $T_{A} = 25^{\circ}$ C).

Table 1.

| Parameter                                                       | Min  | Тур      | Max  | Unit    |

|-----------------------------------------------------------------|------|----------|------|---------|

| RESOLUTION                                                      | 14   |          |      | Bits    |

| ACCURACY                                                        |      |          |      |         |

| No Missing Codes                                                |      | Guarante | ed   |         |

| Offset Error                                                    |      | 0        |      | % FSR   |

| Offset Matching                                                 |      | 0        |      | % FSR   |

| Gain Error                                                      | TBD  |          | TBD  | % FSR   |

| Gain Matching                                                   |      | TBD      | TBD  | % FSR   |

| Differential Nonlinearity (DNL)                                 | TBD  | TBD      | TBD  | LSB     |

| Integral Nonlinearity (INL)                                     | TBD  | TBD      | TBD  | LSB     |

| TEMPERATURE DRIFT                                               |      |          |      |         |

| Offset Error                                                    |      | TBD      |      | ppm/°C  |

| Gain Error                                                      |      | TBD      |      | ppm/°C  |

| INTERNAL VOLTAGE REFERENCE                                      |      | 0.5      |      | V       |

| INPUT REFERRED NOISE                                            |      | 2.6      |      | LSB rms |

| ANALOG INPUTS                                                   |      |          |      |         |

| Differential Input Voltage Range (Programmable)                 | 1.44 | 1.80     | 2.16 | V p-p   |

| Common-Mode Voltage (V <sub>CM</sub> )                          |      | 1.34     |      | V       |

| Differential Input Capacitance <sup>1</sup>                     |      | 1.75     |      | pF      |

| Differential Input Resistance                                   |      | 200      |      | Ω       |

| Analog Input Full Power Bandwidth                               |      | 1.4      |      | GHz     |

| POWER SUPPLY                                                    |      |          |      |         |

| AVDD1                                                           | 0.95 | 0.975    | 1.00 | V       |

| AVDD1_SR                                                        | 0.95 | 0.975    | 1.00 | V       |

| AVDD2                                                           | 1.71 | 1.8      | 1.89 | V       |

| AVDD3                                                           | 2.44 | 2.5      | 2.56 | V       |

| DVDD                                                            | 0.95 | 0.975    | 1.00 | V       |

| DRVDD1                                                          | 0.95 | 0.975    | 1.00 | V       |

| DRVDD2                                                          | 1.71 | 1.8      | 1.89 | V       |

| SPIVDD                                                          | 1.71 | 1.8      | 1.89 | V       |

| I <sub>AVDD1</sub>                                              |      | 470      | TBD  | mA      |

| lavdd1_sr                                                       |      | 20       | TBD  | mA      |

| l <sub>AVDD2</sub>                                              |      | 453      | TBD  | mA      |

| I <sub>AVDD3</sub>                                              |      | 40       | TBD  | mA      |

| I <sub>DVDD</sub> <sup>2</sup>                                  |      | 201      | TBD  | mA      |

| I <sub>DRVDD1</sub> <sup>1</sup>                                |      | 112      | TBD  | mA      |

| I <sub>DRVDD2</sub> <sup>1</sup>                                |      | 25       | TBD  | mA      |

| IspivDD                                                         |      | <1       | TBD  | mA      |

| POWER CONSUMPTION                                               |      |          | _    |         |

| Total Power Dissipation (Including Output Drivers) <sup>2</sup> |      | 1.74     | TBD  | W       |

| Power-Down Dissipation                                          |      | TBD      |      | mW      |

| Standby <sup>3</sup>                                            |      | TBD      |      | W       |

$<sup>^{\</sup>rm 1}$  All lanes running. Power dissipation on DRVDD1 changes with lane rate and number of lanes used.

<sup>&</sup>lt;sup>2</sup> Full bandwidth mode.

<sup>&</sup>lt;sup>3</sup> Standby mode is controlled by the SPI.

#### **DIGITAL SPECIFICATIONS**

AVDD1 = 0.975 V, AVDD1\_SR = 0.975 V, AVDD2 = 1.8 V, AVDD3 = 2.5 V, DVDD = 0.975 V, DRVDD1 = 0.975 V, DRVDD2 = 1.8 V, SPIVDD = 1.8 V, 500 MSPS, clock divider = 4, 1.80 V p-p full-scale differential input, 0.5 V internal reference,  $A_{\rm IN}$  = -1.0 dBFS, default SPI settings, unless otherwise noted. Minimum and maximum specifications are guaranteed for the full operating junction temperature ( $T_{\rm I}$ ) range of -40°C to +105°C. Typical specifications represent performance at  $T_{\rm I}$  = 50°C ( $T_{\rm A}$  = 25°C).

Table 2.

| Parameter                                                        | Min             | Тур           | Max           | Unit   |

|------------------------------------------------------------------|-----------------|---------------|---------------|--------|

| CLOCK INPUTS (CLK+, CLK-)                                        |                 |               |               |        |

| Logic Compliance                                                 |                 | LVDS/LVPEC    | :L            |        |

| Differential Input Voltage                                       | 600             | 800           | 1600          | mV p-p |

| Input Common-Mode Voltage                                        |                 | 0.69          |               | V      |

| Input Resistance (Differential)                                  |                 | 32            |               | kΩ     |

| Input Capacitance                                                |                 |               | 0.9           | pF     |

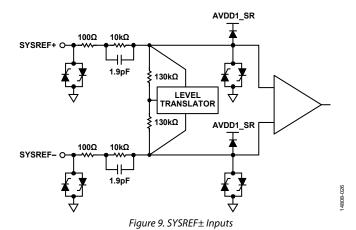

| SYSTEM REFERENCE (SYSREF) INPUTS (SYSREF+, SYSREF-) <sup>1</sup> |                 |               |               |        |

| Logic Compliance                                                 |                 | LVDS/LVPEC    | ïL            |        |

| Differential Input Voltage                                       | 400             | 800           | 1800          | mV p-p |

| Input Common-Mode Voltage                                        | 0.6             | 0.69          | 2.2           | V      |

| Input Resistance (Differential)                                  | 18              | 22            |               | kΩ     |

| Input Capacitance (Single-Ended per Pin)                         |                 | 0.7           |               | pF     |

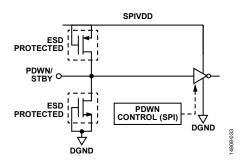

| LOGIC INPUTS (PDWN/STBY)                                         |                 |               |               |        |

| Logic Compliance                                                 |                 | CMOS          |               |        |

| Logic 1 Voltage                                                  | 0.65 × SPIVDD   |               |               | V      |

| Logic 0 Voltage                                                  | 0               |               | 0.35 × SPIVDD | V      |

| Input Resistance                                                 |                 | 10            |               | ΜΩ     |

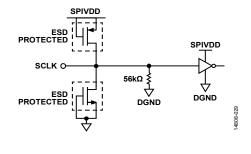

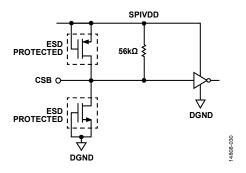

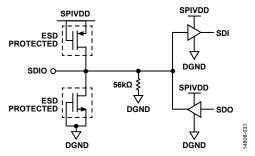

| LOGIC INPUTS (SDIO, SCLK, CSB)                                   |                 |               |               |        |

| Logic Compliance                                                 |                 | CMOS          |               |        |

| Logic 1 Voltage                                                  | 0.65 × SPIVDD   |               |               | V      |

| Logic 0 Voltage                                                  | 0               |               | 0.35 × SPIVDD | V      |

| Input Resistance                                                 |                 | 56            |               | kΩ     |

| LOGIC OUTPUT (SDIO)                                              |                 |               |               |        |

| Logic Compliance                                                 |                 | CMOS          |               |        |

| Logic 1 Voltage (I <sub>OH</sub> = 800 μA)                       | SPIVDD – 0.45 V |               |               | V      |

| Logic 0 Voltage ( $I_{OL} = 50 \mu A$ )                          | 0               |               | 0.45          | V      |

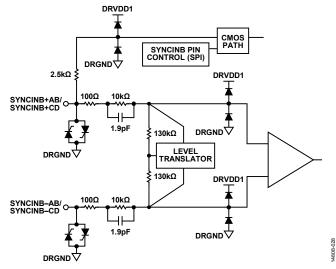

| SYNCIN INPUT (SYNCINB+AB/SYNCINB-AB/<br>SYNCINB+CD/SYNCINB-CD)   |                 |               |               |        |

| Logic Compliance                                                 |                 | LVDS/LVPECL/C | MOS           |        |

| Differential Input Voltage                                       | 400             | 800           | 1800          | mV p-p |

| Input Common-Mode Voltage                                        | 0.6             | 0.69          | 2.2           | V      |

| Input Resistance (Differential)                                  | 18              | 22            |               | kΩ     |

| Input Capacitance (Single Ended per Pin)                         |                 | 0.7           |               | pF     |

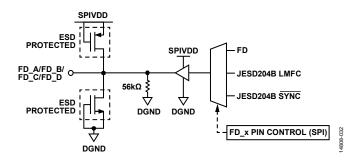

| LOGIC OUTPUTS (FD_A, FD_B, FD_C, FD_D)                           |                 |               |               |        |

| Logic Compliance                                                 |                 | CMOS          |               |        |

| Logic 1 Voltage                                                  | 0.8 × SPIVDD    |               |               | V      |

| Logic 0 Voltage                                                  | 0               |               | 0.5           | V      |

| Input Resistance                                                 |                 | 56            |               | kΩ     |

| DIGITAL OUTPUTS (SERDOUTABx±/SERDOUTCDx±, x = 0 OR 1)            |                 |               |               |        |

| Logic Compliance                                                 |                 | CML           |               |        |

| Differential Output Voltage                                      |                 | 455.8         |               | mV p-p |

| Short-Circuit Current (ID SHORT)                                 |                 | 15            |               | mA     |

| Differential Termination Impedance                               |                 | 100           |               | Ω      |

<sup>&</sup>lt;sup>1</sup> DC-coupled input only.

#### **TIMING SPECIFICATIONS**

Table 3.

| Parameter                           | Test Conditions/Comments                                                                                                    | Min | Тур   | Max | Unit |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

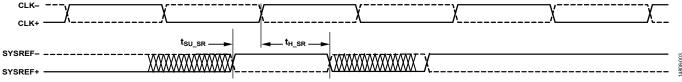

| CLK+ to SYSREF+ TIMING REQUIREMENTS | See Figure 3                                                                                                                |     |       |     |      |

| t <sub>SU_SR</sub>                  | Device clock to SYSREF+ setup time                                                                                          |     | -44.8 |     | ps   |

| t <sub>H_SR</sub>                   | Device clock to SYSREF+ hold time                                                                                           |     | 64.4  |     | ps   |

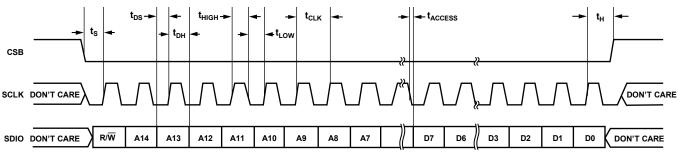

| SPITIMING REQUIREMENTS              | See Figure 4                                                                                                                |     |       |     |      |

| t <sub>DS</sub>                     | Setup time between the data and the rising edge of SCLK                                                                     | 4   |       |     | ns   |

| t <sub>DH</sub>                     | Hold time between the data and the rising edge of SCLK                                                                      | 2   |       |     | ns   |

| t <sub>clk</sub>                    | Period of the SCLK                                                                                                          | 40  |       |     | ns   |

| ts                                  | Setup time between CSB and SCLK                                                                                             | 2   |       |     | ns   |

| tн                                  | Hold time between CSB and SCLK                                                                                              | 2   |       |     | ns   |

| tніgн                               | Minimum period that SCLK must be in a logic high state                                                                      | 10  |       |     | ns   |

| t <sub>LOW</sub>                    | Minimum period that SCLK must be in a logic low state                                                                       | 10  |       |     | ns   |

| taccess                             | Maximum time delay between falling edge of SCLK and output data valid for a read operation                                  |     | 6     | 10  | ns   |

| t <sub>DIS_SDIO</sub>               | Time required for the SDIO pin to switch from an output to an input relative to the CSB rising edge (not shown in Figure 4) | 10  |       |     | ns   |

#### **Timing Diagrams**

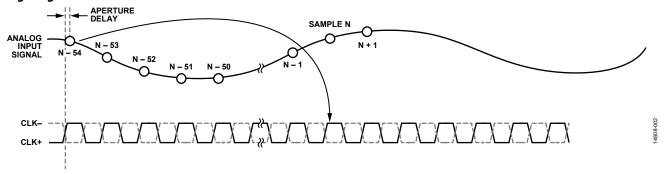

Figure 2. Data Output Timing (Full Bandwidth Mode; L=4, M=2, F=1)

Figure 3. SYSREF± Setup and Hold Timing

Figure 4. Serial Port Interface Timing Diagram

#### **ABSOLUTE MAXIMUM RATINGS**

Table 4.

| Parameter                               | Rating                   |

|-----------------------------------------|--------------------------|

|                                         | Katilig                  |

| Electrical                              |                          |

| AVDD1 to AGND                           | 1.05 V                   |

| AVDD1_SR to AGND                        | 1.05 V                   |

| AVDD2 to AGND                           | 2.00 V                   |

| AVDD3 to AGND                           | 2.70 V                   |

| DVDD to DGND                            | 1.05 V                   |

| DRVDD1 to DRGND                         | 1.05 V                   |

| DRVDD2 to DRGND                         | 2.00 V                   |

| SPIVDD to AGND                          | 2.00 V                   |

| VIN±x to AGND                           | -0.3 V to AVDD3 + 0.3 V  |

| CLK± to AGND                            | -0.3 V to AVDD1 + 0.3 V  |

| SCLK, SDIO, CSB to DGND                 | -0.3 V to SPIVDD + 0.3 V |

| PDWN/STBY to DGND                       | -0.3 V to SPIVDD + 0.3 V |

| SYSREF± to AGND_SR                      | 0 V to 2.5 V             |

| SYNCINB±AB/SYNCINB±CD to DRGND          | 0 V to 2.5 V             |

| Environmental                           |                          |

| Operating Junction Temperature<br>Range | -40°C to +105°C          |

| Maximum Junction Temperature            | 125°C                    |

| Storage Temperature Range<br>(Ambient)  | −65°C to +150°C          |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.

$\theta_{JC\_BOT}$  is the bottom junction to case thermal resistance.

**Table 5. Thermal Resistance**

| PCB Type       | Airflow Velocity (m/sec) | $\theta_{JA}$         | $\theta_{\text{JC\_BOT}}$ | Unit |

|----------------|--------------------------|-----------------------|---------------------------|------|

| JEDEC          | 0.0                      | 21.581,2              | 1.951,4                   | °C/W |

| 2s2p Board     | 1.0                      | 17.94 <sup>1, 2</sup> | N/A <sup>3</sup>          | °C/W |

|                | 2.5                      | 16.58 <sup>1, 2</sup> | N/A <sup>3</sup>          | °C/W |

| 10-Layer Board | 0.0                      | 9.74                  | 1.00                      | °C/W |

<sup>&</sup>lt;sup>1</sup> Per JEDEC 51-7, plus JEDEC 51-5 2s2p test board.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> Per JEDEC JESD51-2 (still air) or JEDEC JESD51-6 (moving air).

<sup>&</sup>lt;sup>3</sup> N/A means not applicable.

<sup>&</sup>lt;sup>4</sup> Per MIL-STD 883, Method 1012.1.

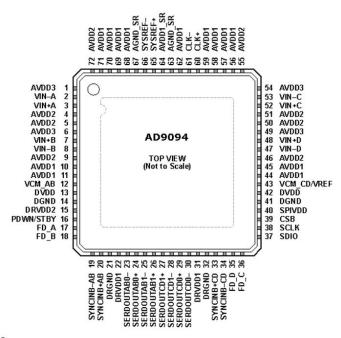

#### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

NOTES

1. EXPOSED PAD. ANALOG GROUND. THE EXPOSED THERMAL PAD ON THE BOTTOM OF THE PACKAGE PROVIDES THE GROUND REFERENCE FOR AVDDX, SPIVDD, DVDD, DRVDD1, AND DRVDD2. THIS EXPOSED PAD MUST BE CONNECTED TO GROUND FOR PROPER OPERATION.

Figure 5. Pin Configuration (Top View)

**Table 6. Pin Function Descriptions**

| Pin No.                                            | Mnemonic               | Туре   | Description                                                                                                                                                                                                                    |

|----------------------------------------------------|------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                                                  | AGND/EPAD              | Ground | Exposed Pad. Analog Ground. The exposed thermal pad on the bottom of the package provides the ground reference for AVDDx, SPIVDD, DVDD, DRVDD1, and DRVDD2. This exposed pad must be connected to ground for proper operation. |

| 1, 6, 49, 54                                       | AVDD3                  | Supply | Analog Power Supply (2.5 V Nominal).                                                                                                                                                                                           |

| 2, 3                                               | VIN-A, VIN+A           | Input  | ADC A Analog Input Complement/True.                                                                                                                                                                                            |

| 4, 5, 9, 46, 50, 51, 55, 72                        | AVDD2                  | Supply | Analog Power Supply (1.8 V Nominal).                                                                                                                                                                                           |

| 7,8                                                | VIN+B, VIN-B           | Input  | ADC B Analog Input True/Complement.                                                                                                                                                                                            |

| 10, 11, 44, 45, 56, 57, 58, 59, 62, 68, 69, 70, 71 | AVDD1                  | Supply | Analog Power Supply (0.975 V Nominal).                                                                                                                                                                                         |

| 12                                                 | VCM_AB                 | Output | Common-Mode Level Bias Output for Analog Input Channel A and Channel B.                                                                                                                                                        |

| 13, 42                                             | DVDD                   | Supply | Digital Power Supply (0.975 V Nominal).                                                                                                                                                                                        |

| 14, 41                                             | DGND                   | Ground | Ground Reference for DVDD and SPIVDD.                                                                                                                                                                                          |

| 15                                                 | DRVDD2                 | Supply | Digital Power Supply for JESD204B PLL (1.8 V Nominal).                                                                                                                                                                         |

| 16                                                 | PDWN/STBY              | Input  | Power-Down Input/Standby (Active High). The operation of this pin depends on the SPI mode and can be configured as power-down or standby. This pin requires external 10 k $\Omega$ pull-down resistor.                         |

| 17, 18, 35, 36                                     | FD_A, FD_B, FD_D, FD_C | Output | Fast Detect Outputs for Channel A, Channel B, Channel C, and Channel D.                                                                                                                                                        |

| 19                                                 | SYNCINB-AB             | Input  | Active Low JESD204B LVDS Sync Input Complement for Channel A and Channel B.                                                                                                                                                    |

| 20                                                 | SYNCINB+AB             | Input  | Active Low JESD204B LVDS/CMOS Sync Input True for Channel A and Channel B.                                                                                                                                                     |

| Pin No. | Mnemonic                    | Туре         | Description                                                                                                                                                                                                                                                                                                                                                  |

|---------|-----------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21, 32  | DRGND                       | Ground       | Ground Reference for DRVDD1 and DRVDD2.                                                                                                                                                                                                                                                                                                                      |

| 22, 31  | DRVDD1                      | Supply       | Digital Power Supply for SERDOUTABx±/SERDOUTCDx± Pins (0.975 V Nominal).                                                                                                                                                                                                                                                                                     |

| 23, 24  | SERDOUTABO-,<br>SERDOUTABO+ | Output       | Lane 0 Output Data Complement/True for Channel A and Channel B.                                                                                                                                                                                                                                                                                              |

| 25, 26  | SERDOUTAB1–,<br>SERDOUTAB1+ | Output       | Lane 1 Output Data Complement/True for Channel A and Channel B.                                                                                                                                                                                                                                                                                              |

| 27, 28  | SERDOUTCD1+,<br>SERDOUTCD1- | Output       | Lane 1 Output Data True/Complement for Channel C and Channel D.                                                                                                                                                                                                                                                                                              |

| 29, 30  | SERDOUTCD0+,<br>SERDOUTCD0- | Output       | Lane 0 Output Data True/Complement for Channel C and Channel D.                                                                                                                                                                                                                                                                                              |

| 33      | SYNCINB+CD                  | Input        | Active Low JESD204B LVDS/CMOS/LVPECL Sync Input True for Channel C and Channel D.                                                                                                                                                                                                                                                                            |

| 34      | SYNCINB-CD                  | Input        | Active Low JESD204B LVDS/CMOS/LVPECL Sync Input Complement for Channel C and Channel D.                                                                                                                                                                                                                                                                      |

| 37      | SDIO                        | Input/output | SPI Serial Data Input/Output.                                                                                                                                                                                                                                                                                                                                |

| 38      | SCLK                        | Input        | SPI Serial Clock.                                                                                                                                                                                                                                                                                                                                            |

| 39      | CSB                         | Input        | SPI Chip Select (Active Low).                                                                                                                                                                                                                                                                                                                                |

| 40      | SPIVDD                      | Supply       | Digital Power Supply for SPI (1.8 V Nominal).                                                                                                                                                                                                                                                                                                                |

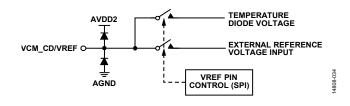

| 43      | VCM_CD/VREF                 | Output/input | Common-Mode Level Bias Output for Analog Input Channel C and Channel D/0.5 V Reference Voltage Input. This pin is configurable through the SPI as an output or an input. Use this pin as the common-mode level bias output if using the internal reference. This pin requires a 0.5 V reference voltage input if using an external voltage reference source. |

| 47, 48  | VIN-D, VIN+D                | Input        | ADC D Analog Input Complement/True.                                                                                                                                                                                                                                                                                                                          |

| 52, 53  | VIN+C, VIN-C                | Input        | ADC C Analog Input True/Complement.                                                                                                                                                                                                                                                                                                                          |

| 60, 61  | CLK+, CLK-                  | Input        | Clock Input True/Complement.                                                                                                                                                                                                                                                                                                                                 |

| 63, 67  | AGND_SR                     | Ground       | Ground Reference for SYSREF±.                                                                                                                                                                                                                                                                                                                                |

| 64      | AVDD1_SR                    | Supply       | Analog Power Supply for SYSREF± (0.975 V Nominal).                                                                                                                                                                                                                                                                                                           |

| 65, 66  | SYSREF+, SYSREF-            | Input        | Active Low JESD204B LVDS System Reference Input True/Complement. DC-coupled input only.                                                                                                                                                                                                                                                                      |

|         | EPAD                        |              | Exposed Pad. Analog ground. The exposed thermal pad on the bottom of the package provides the ground reference for AVDDX, SPIVDD, DVDD, DRVDD1, and DRVDD2. This exposed pad must be connected to ground for proper operation.                                                                                                                               |

#### TYPICAL PERFORMANCE CHARACTERISTICS

AVDD1 = 0.975 V, AVDD1\_SR = 0.975 V, AVDD2 = 1.80 V, AVDD3 = 2.5 V, DVDD = 0.975 V, DRVDD1 = 0.975 V, DRVDD2 = 1.8 V, SPIVDD = 1.8 V, specified maximum sampling rate, clock divider = 4, 1.80 V p-p full-scale differential input, 0.5 V internal reference,  $A_{IN} = -1.0$  dBFS, default SPI settings, unless otherwise noted. Minimum and maximum specifications are guaranteed for the full operating junction temperature ( $T_I$ ) range of  $-40^{\circ}$ C to  $+105^{\circ}$ C. Typical specifications represent performance at  $T_I = 50^{\circ}$ C ( $T_A = 25^{\circ}$ C).

Figure 6.

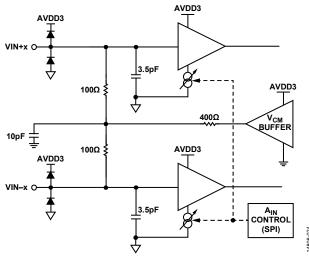

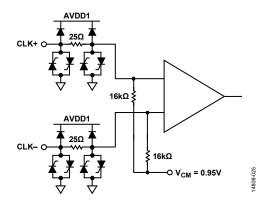

## **EQUIVALENT CIRCUITS**

Figure 7. Analog Inputs

Figure 8. Clock Inputs

DATA+

DATA+

DATA

DRIVER

DR

Figure 10. Digital Outputs

Figure 11. SYNCINB±AB, SYNCINB±CD Inputs

Figure 12. SCLK Input

Figure 13. CSB Input

Figure 14. SDIO Input

Figure 15. FD\_A/FD\_B/FD\_C/FD\_D Outputs

Figure 16. PDWN/STBY Input

Figure 17. VCM\_CD/VREF Input/Output

Figure 18. Temperature Diode Voltage vs. Junction Temperature

#### ADC OVERRANGE AND FAST DETECT

In receiver applications, it is desirable to have a mechanism to reliably determine when the converter is about to be clipped. The standard overrange bit in the JESD204B outputs provides information on the state of the analog input that is of limited usefulness. Therefore, it is helpful to have a programmable threshold below full scale that allows time to reduce the gain before the clip actually occurs. In addition, because input signals can have significant slew rates, the latency of this function is of major concern. Highly pipelined converters can have significant latency. The AD9094 contains fast detect circuitry for individual channels to monitor the threshold and to assert the FD\_A, FD\_B, FD\_C, and FD\_D pins.

#### **ADC OVERRANGE**

The ADC overrange indicator is asserted when an overrange is detected on the input of the ADC. The overrange indicator can be embedded within the JESD204B link as a control bit (when CSB > 0). The latency of this overrange indicator matches the sample latency.

## FAST THRESHOLD DETECTION (FD\_A, FD\_B, FD\_C, AND FD\_D)

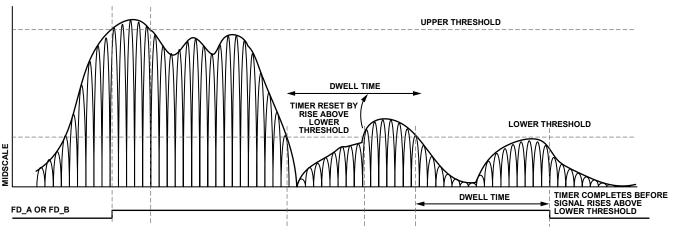

The fast detect (FD) bits in Register 0x0040 are immediately set whenever the absolute value of the input signal exceeds the programmable upper threshold level. The FD bits are cleared only when the absolute value of the input signal drops below the lower threshold level for greater than the programmable dwell time. This feature provides hysteresis and prevents the FD bits from excessively toggling.

The operation of the upper threshold and lower threshold registers, along with the dwell time registers, is shown in Figure 19.

The FD indicator is asserted if the input magnitude exceeds the value programmed in the fast detect upper threshold registers, located at Register 0x0247 and Register 0x0248. The selected threshold register is compared with the signal magnitude at the output of the ADC. The fast upper threshold detection has a latency of 30 clock cycles (maximum). The approximate upper threshold magnitude is defined by

*Upper Threshold Magnitude* (dBFS) = 20log (*Threshold Magnitude*/2<sup>13</sup>)

The FD indicators are not cleared until the signal drops below the lower threshold for the programmed dwell time. The lower threshold is programmed in the fast detect lower threshold registers, located at Register 0x0249 and Register 0x024A. The fast detect lower threshold register is a 13-bit register that is compared with the signal magnitude at the output of the ADC. This comparison is subject to the ADC pipeline latency, but is accurate in terms of converter resolution. The lower threshold magnitude is defined by

Lower Threshold Magnitude (dBFS) = 20log (Threshold Magnitude/2<sup>13</sup>)

For example, to set an upper threshold of –6 dBFS, write 0xFFF to Register 0x0247 and Register 0x0248. To set a lower threshold of –10 dBFS, write 0xA1D to Register 0x0249 and Register 0x024A.

The dwell time can be programmed from 1 to 65,535 sample clock cycles by placing the desired value in the fast detect dwell time registers, located at Register 0x024B and Register 0x024C. See the Memory Map section (Register 0x0040, and Register 0x0245 to Register 0x024C in Table 11) for more details.

Figure 19. Threshold Settings for the FD\_A and FD\_B Signals

#### **CONFIGURING THE JESD204B LINK**

The AD9094 has two JESD204B links. The device offers an easy way to set up the JESD204B link through the JESD204B JTX quick configuration register (Register 0x570). One link consists of the SERDOUTAB0± and SERDOUTAB1± serial outputs and the second link consists of the SERDOUTCD0± and SERDOUTCD1± serial outputs. The basic parameters that determine the link setup are

- Number of lanes per link (L)

- Number of converters per link (M)

- Number of octets per frame (F)

If the internal DDCs are used for on-chip digital processing, M represents the number of virtual converters.

The maximum lane rate allowed by the JESD204B specification is 15 Gbps. The lane line rate is related to the JESD204B parameters using the following equation:

$$Lane\ Line\ Rate = \frac{M \times N' \times \left(\frac{10}{8}\right) \times f_{OUT}}{L}$$

where:

$$f_{OUT} = \frac{f_{ADC\_CLOCK}}{Decimation \ Ratio}$$

he decimation ratio (DCM) is

The decimation ratio (DCM) is the parameter programmed in Register 0x0201.

Use the following steps to configure the output:

- 1. Power down the link.

- 2. Select the quick configuration options.

- 3. Configure any detailed options.

- 4. Set the output lane mapping (optional).

- 5. Set additional driver configuration options (optional).

- 6. Power up the link.

If the lane line rate calculated is less than 6.75 Gbps, select the low line rate option by programming a value of 0x10 to Register 0x056E.

Table 8 shows the JESD204B output configurations supported for N'=8 for a given number of virtual converters. Take care to ensure that the serial line rate for a given configuration is within the supported range of 1.6875 Gbps to 15 Gbps.

Table 7. Virtual Converter Mapping (Per Link)

| Number of Virtual           | Chip Application Mode        | Chip Q Ignore            | Vi                  | rtual Converter     | Mapping         |                    |

|-----------------------------|------------------------------|--------------------------|---------------------|---------------------|-----------------|--------------------|

| <b>Converters Supported</b> | (Register 0x0200, Bits[3:0]) | (Register 0x0200, Bit 5) | 0                   | 1                   | 2               | 3                  |

| 1 to 2                      | Full bandwidth mode (0x0)    | Real or complex (0x0)    | ADC A/ADC C samples | ADC B/ADC D samples | Unused          | Unused             |

| 1                           | One DDC mode (0x1)           | Real (I only) (0x1)      | DDC 0 I<br>samples  | Unused              | Unused          | Unused             |

| 2                           | One DDC mode (0x1)           | Complex (I/Q) (0x0)      | DDC 0 I<br>samples  | DDC 0 Q<br>samples  | Unused          | Unused             |

| 2                           | Two DDC mode (0x2)           | Real (I only) (0x1)      | DDC 0 I<br>samples  | DDC 1 I<br>samples  | Unused          | Unused             |

| 4                           | Two DDC mode (0x2)           | Complex (I/Q) (0x0)      | DDC 0 I<br>samples  | DDC 0 Q<br>samples  | DDC 1 I samples | DDC 1 Q<br>samples |

Table 8. JESD204B Output Configurations for N' = 8 (Per Link)

| Number of Virtual                      | JESD204B Quick                  | JESD204B Transport Layer Settings |   |   |   |   |    |        |    |        |                       |

|----------------------------------------|---------------------------------|-----------------------------------|---|---|---|---|----|--------|----|--------|-----------------------|

| Converters Supported (Same Value as M) | Configuration (Register 0x0570) | Serial Lane Rate <sup>1</sup>     | L | М | F | s | HD | N      | N' | cs     | K²                    |

| 1                                      | 0x00                            | 10 × f <sub>оит</sub>             | 1 | 1 | 1 | 1 | 0  | 7 to 8 | 8  | 0 to 1 | Only valid K          |

|                                        | 0x01                            | $10 \times f_{OUT}$               | 1 | 1 | 2 | 2 | 0  | 7 to 8 | 8  | 0 to 1 | values which          |

|                                        | 0x40                            | $5 \times f_{OUT}$                | 2 | 1 | 1 | 2 | 0  | 7 to 8 | 8  | 0 to 1 | are divisible         |

|                                        | 0x41                            | 5 × f <sub>OUT</sub>              | 2 | 1 | 2 | 4 | 0  | 7 to 8 | 8  | 0 to 1 | by 4 are<br>supported |

|                                        | 0x42                            | $5 \times f_{OUT}$                | 2 | 1 | 4 | 8 | 0  | 7 to 8 | 8  | 0 to 1 |                       |

| 2                                      | 0x09                            | 20 × f <sub>оит</sub>             | 1 | 2 | 2 | 1 | 0  | 7 to 8 | 8  | 0 to 1 |                       |

|                                        | 0x48                            | 10 × f <sub>оит</sub>             | 2 | 2 | 1 | 1 | 0  | 7 to 8 | 8  | 0 to 1 |                       |

|                                        | 0x49                            | $10 \times f_{OUT}$               | 2 | 2 | 2 | 2 | 0  | 7 to 8 | 8  | 0 to 1 |                       |

$<sup>^1</sup>$  f<sub>OUT</sub> = output sample rate is the ADC sample rate/chip decimation ratio. The JESD204B serial line rate must be ≥1687.5 Mbps and ≤15,000 Mbps. When the serial lane rate is ≤15 Gbps and >13.5 Gbps, set Bits[7:4] to 0x3 in Register 0x056E. When the serial lane rate is ≤13.5 Gbps and >6.75 Gbps, set Bits[7:4] to 0x0 in Register 0x056E. When the serial lane rate is ≤6.75 Gbps and >3.375 Gbps, set Bits[7:4] to 0x1 in Register 0x056E. When the serial lane rate is ≤3.375 Gbps and ≥1687.5 Mbps, set Bits[7:4] to 0x5 in Register 0x056E.

<sup>&</sup>lt;sup>2</sup> For F = 1, K = 20, 24, 28, and 32. For F = 2, K = 12, 16, 20, 24, 28, and 32. For F = 4, K = 8, 12, 16, 20, 24, 28, and 32. For F = 8 and F = 16, K = 4, 8, 12, 16, 20, 24, 28, and 32.

#### **LATENCY**

#### **END TO END TOTAL LATENCY**

Total latency in the AD9094 is dependent on the chip application mode and the JESD204B configuration. For any given combination of these parameters, the latency is deterministic, however, the value of this deterministic latency must be calculated as described in the Example Latency Calculations section.

Table 9 shows the combined latency through the ADC and DSP for the different chip application modes supported by the AD9094. Table 10 shows the latency through the JESD204B block for each application mode based on the M/L ratio. For both Table 9 and Table 10, latency is typical and is in units of the encode clock. The latency through the JESD204B block does not depend on the output data type (real or complex). Therefore, data type is not included in Table 10.

To determine the total latency, select the appropriate ADC + DSP latency from Table 9 and add it to the appropriate JESD204B latency from Table 10. Example calculations are provided in the following section.

#### **EXAMPLE LATENCY CALCULATIONS**

#### **Example Configuration 1**

In this example, the ADC application mode is full bandwidth with the following conditions:

- Real outputs

- L = 4, M = 2, F = 1, S = 1 (JESD204B mode)

- M/L ratio = 0.5

Latency = 31 + 25 = 56 encode clocks

#### **Example Configuration 2**

In this example, the ADC application mode is decimate by 4, DCM4, with the following conditions:

- Complex outputs

- L = 4, M = 2, F = 1, S = 1 (JESD204B mode)

- M/L ratio = 0.5

Latency = 162 + 88 = 250 encode clocks

#### LMFC REFERENCED LATENCY

Some FPGA vendors may require the end user to know the LMFC referenced latency to make the appropriate deterministic latency adjustments. If they are required, the latency values in Table 9 and Table 10 can be used for the analog input to LMFC latency value and the LMFC to data output latency value.

Table 9. Latency Through the ADC + DSP Blocks (Number of Sample Clocks)

| Chip Application<br>Mode <sup>1</sup> | Enabled<br>Filters | ADC and DSP Latency |

|---------------------------------------|--------------------|---------------------|

| Full Bandwidth                        | Not<br>applicable  | 31                  |

<sup>&</sup>lt;sup>1</sup> DCMx indicates the decimation ratio.

Table 10. Latency Through JESD204B Block (Number of Sample Clocks)

|               |     | M/L | Ratio <sup>1, 2</sup> | 4 8 |   |

|---------------|-----|-----|-----------------------|-----|---|

| Chip App Mode | 0.5 | 1   | 2                     | 4   | 8 |

| Full BW       | 25  | 14  | 7                     | 4   | 2 |

<sup>&</sup>lt;sup>1</sup> M/L ratio is the number of converters divided by the number of lanes for the configuration.

<sup>&</sup>lt;sup>2</sup> N/A means not applicable, indicating the application mode is not supported at the M/L ratio listed.

#### MEMORY MAP

#### **READING THE MEMORY MAP REGISTER TABLE**

Each row in the memory map register table has eight bit locations. The memory map is divided into four sections: the Analog Devices SPI registers (Register 0x0000 to Register 0x000D and Register 0x18A6 to Register 0x1A4D, the ADC function registers (Register 0x003F to Register 0x027A, Register 0x0701, and Register 0x073B), the DDC function registers (Register 0x0300 to Register 0x0347), and the digital outputs and test modes registers (Register 0x0550 to Register 0x1262).

Table 11 (see the Memory Map section) documents the default hexadecimal value for each hexadecimal address shown. The column with the heading Bit 7 (MSB) is the start of the default hexadecimal value given. For example, Address 0x0561, the output sample mode register, has a hexadecimal default value of 0x01. This default value means that Bit 0=1, and the remaining bits are 0s. This setting is the default output format value, which is twos complement. For more information on this function and others, see Table 11.

#### **Unassigned and Reserved Locations**

All address and bit locations that are not included in Table 11 are not currently supported for this device. Write unused bits of a valid address location with 0s unless the default value is set otherwise. Writing to these locations is required only when part of an address location is unassigned (for example, Address 0x0561). If the entire address location is open (for example, Address 0x0013), do not write to this address location.

#### **Default Values**

After the AD9094 is reset, critical registers are loaded with default values. The default values for the registers are given in the memory map register table, Table 11.

#### Logic Levels

An explanation of logic level terminology follows:

- "Bit is set" is synonymous with "bit is set to Logic 1" or "writing Logic 1 for the bit."

- "Clear a bit" is synonymous with "bit is set to Logic 0" or "writing Logic 0 for the bit."

- X denotes a don't care bit.

#### **ADC Pair Addressing**

The AD9094 functionally operates as two pairs of dual IF receiver channels. There are two ADCs and two DDCs in each pair making for a total of four of each for the AD9094 device. To access the SPI registers for each pair, the pair index must be written in Register 0x0009. The pair index register must be written prior to any other SPI write to the AD9094.

#### **Channel Specific Registers**

Some channel setup functions, such as the fast detect control (Register 0x0247), can be programmed to a different value for each channel. In these cases, channel address locations are internally duplicated for each channel. These registers and bits are designated in Table 11 as local. These local registers and bits can be accessed by setting the appropriate Channel A/Channel C or Channel B/Channel D bits in Register 0x0008. The particular channel that is addressed is dependent upon the pair selection written to Register 0x0009. If both bits are set, the subsequent write affects the registers of both channels. In a read cycle, set only Channel A/Channel C or Channel B/Channel D to read one of the two registers. If both bits are set during an SPI read cycle, the device returns the value for Channel A. If both pairs and both channels are selected via Register 0x0009 and Register 0x0008, the device returns the value for Channel A.

The names of the registers listed Table 11 are prefixed with either global map, channel map, JESD204B map, or pair map. Registers in the pair map and JESD204B map apply to a pair of channels, either Pair A/B or Pair C/D. To write registers in the pair map and JESD204B map, the pair index register (Register 0x0009) must be written to address the appropriate pair. The SPI Configuration A (Register 0x0000), SPI Configuration B (Register 0x0001), and pair index (Register 0x0009) registers are the only registers that reside in the global map. Registers in the channel map are local to each channel: Channel A, Channel B, Channel C, or Channel D. To write registers in the channel map, the pair index register (Register 0x0009) must be written first to address the desired pair (Pair A/B or Pair C/D) followed by writing the device index register (Register 0x0008) to select the desired channel (Channel A/Channel C or Channel B/Channel D).

For example, to write Channel A to a test mode (set by Register 0x0550), first write 0x01 to Register 0x0009 to select Pair A/B, followed by writing 0x01 to Register 0x0008 to select Channel A. Then, write Register 0x0550 to the value for the desired test mode. To write all channels to a test mode (set by Register 0x0550), first write Register 0x0009 to a value of 0x03 to select both Pair A/B and Pair C/D, followed by writing Register 0x0008 to a value of 0x03 to select Channel A, Channel B, Channel C, and Channel D. Next, write Register 0x0550 to the value for the desired test mode.

#### SPI Soft Reset

After issuing a soft reset by programming 0x81 to Register 0x0000, the AD9094 requires 5 ms to recover. When programming the AD9094 for application setup, ensure that an adequate delay is programmed into the firmware after asserting the soft reset and before starting the device setup.

#### **MEMORY MAP REGISTER TABLE—DETAILS**

All address locations that are not included in Table 11 are not currently supported for this device and must not be written.

Table 11. Memory Map Details

| Addr   | Name                              | Bits  | Bit Name                            | Settings | Description                                                                                                                                                    | Reset | Access |

|--------|-----------------------------------|-------|-------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|

| 0x0000 | Global map SPI<br>Configuration A | 7     | Soft reset (self clearing)          |          | When a soft reset is issued, the user must wait 5 ms before writing to any other register. This wait provides sufficient time for the boot loader to complete. | 0x0   | R/W    |

|        |                                   |       |                                     | 0        | Do nothing.                                                                                                                                                    |       |        |

|        |                                   |       |                                     | 1        | Reset the SPI and registers (self clearing).                                                                                                                   |       |        |

|        |                                   | 6     | LSB first mirror                    |          |                                                                                                                                                                | 0x0   | R/W    |

|        |                                   |       |                                     | 1        | LSB shifted first for all SPI operations.                                                                                                                      |       |        |

|        |                                   |       |                                     | 0        | MSB shifted first for all SPI operations.                                                                                                                      |       |        |

|        |                                   | 5     | Address ascension mirror            |          |                                                                                                                                                                | 0x0   | R/W    |

|        |                                   |       |                                     | 0        | Multibyte SPI operations cause addresses to auto-increment.                                                                                                    |       |        |

|        |                                   |       |                                     | 1        | Multibyte SPI operations cause addresses to auto-increment.                                                                                                    |       |        |

|        |                                   | 4     | Reserved                            |          | Reserved.                                                                                                                                                      | 0x0   | R      |

|        |                                   | 3     | Reserved                            |          | Reserved.                                                                                                                                                      | 0x0   | R      |

|        |                                   | 2     | Address ascension                   |          |                                                                                                                                                                | 0x0   | R/W    |

|        |                                   |       |                                     | 0        | Multibyte SPI operations cause addresses to auto-increment.                                                                                                    |       |        |

|        |                                   |       |                                     | 1        | Multibyte SPI operations cause addresses to auto-increment.                                                                                                    |       |        |

|        |                                   | 1     | LSB first                           |          |                                                                                                                                                                | 0x0   | R/W    |

|        |                                   |       |                                     | 1        | MSB shifted first for all SPI operations.                                                                                                                      |       |        |

|        |                                   |       |                                     | 0        | MSB shifted first for all SPI operations.                                                                                                                      |       |        |

|        |                                   | 0     | Soft reset (self clearing)          |          | When a soft reset is issued, the user must wait 5 ms before writing to any other register. This wait provides sufficient time for the boot loader to complete. | 0x0   | R/W    |

|        |                                   |       |                                     | 0        | Do nothing.                                                                                                                                                    |       |        |

|        |                                   |       |                                     | 1        | Reset the SPI and registers (self clearing).                                                                                                                   |       |        |

| 0x0001 | Global map SPI                    | 7     | Single instruction                  |          |                                                                                                                                                                | 0x0   | R/W    |

|        | Configuration B                   |       |                                     | 0        | SPI streaming enabled.                                                                                                                                         |       |        |

|        |                                   |       |                                     | 1        | Streaming (multibyte read/write) is disabled. Only one read or write operation is performed regardless of the state of the CSB line.                           |       |        |

|        |                                   | [6:2] | Reserved                            |          | Reserved.                                                                                                                                                      | 0x0   | R      |

|        |                                   | 1     | Datapath soft reset (self clearing) |          |                                                                                                                                                                | 0x0   | R/W    |

|        |                                   |       | _                                   | 0        | Normal operation.                                                                                                                                              |       |        |

|        |                                   |       |                                     | 1        | Datapath soft reset (self clearing)                                                                                                                            |       |        |

|        |                                   | 0     | Reserved                            |          | Reserved.                                                                                                                                                      | 0x0   | R      |

| Name                      | Bits                                                                                                                                                                      | Bit Name                                                                                                                                                                                                                                                                                                                                                                   | Settings                                                                                                                                                                                                                                                                                                                                                                                                                     | Description                                                                                                                                                           | Reset                                                           | Access                                             |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------|

| Channel map               | [7:2]                                                                                                                                                                     | Reserved                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                              | Reserved.                                                                                                                                                             | 0x0                                                             | R                                                  |

| chip                      | [1:0]                                                                                                                                                                     | Channel power modes                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                              | Channel power modes.                                                                                                                                                  | 0x0                                                             | R/W                                                |

| configuration             |                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                            | 00                                                                                                                                                                                                                                                                                                                                                                                                                           | Normal mode (power up).                                                                                                                                               |                                                                 |                                                    |

|                           |                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                            | 10                                                                                                                                                                                                                                                                                                                                                                                                                           | Standby mode. The digital data path clocks are disabled, the JESD204B interface is enabled, and the outputs are enabled.                                              |                                                                 |                                                    |

|                           |                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                            | 11                                                                                                                                                                                                                                                                                                                                                                                                                           | Power-down mode. The digital data path clocks are disabled, the digital data path is held in reset, the JESD204B interface is disabled, and the outputs are disabled. |                                                                 |                                                    |

| Pair map chip<br>type     | [7:0]                                                                                                                                                                     | CHIP_TYPE                                                                                                                                                                                                                                                                                                                                                                  | 0x3                                                                                                                                                                                                                                                                                                                                                                                                                          | Chip type.                                                                                                                                                            | 0x3                                                             | R                                                  |