# ANALOG 12-Bit, 160 MSPS, 2×/4×/8× Interpolating DEVICES **Dual TxDAC D/A Converter**

AD9773

#### **FEATURES**

12-bit resolution, 160 MSPS/400 MSPS input/output data rate Selectable 2×/4×/8× interpolating filter Programmable channel gain and offset adjustment f<sub>s</sub>/2, f<sub>s</sub>/4, f<sub>s</sub>/8 digital quadrature modulation capability Direct IF transmission mode for 70 MHz + IFs **Enables image rejection architecture Fully compatible SPI port Excellent ac performance** SFDR -69 dBc @ 2 MHz to 35 MHz WCDMA ACPR -69 dB @ IF = 19.2 MHz Internal PLL clock multiplier Selectable internal clock divider Versatile clock input Differential/single-ended sine wave or

TTL/CMOS/LVPECL compatible

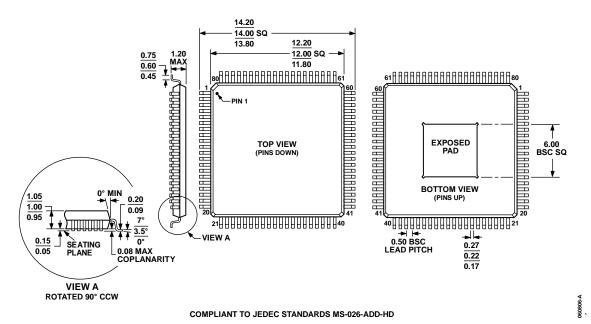

Versatile input data interface Twos complement/straight binary data coding Dual-port or single-port interleaved input data Single 3.3 V supply operation Power dissipation: typical 1.2 W @ 3.3 V On-chip 1.2 V reference 80-lead thin quad flat package, exposed pad (TQFP\_EP)

## **APPLICATIONS**

**Communications**

Analog quadrature modulation architecture 3G, multicarrier GSM, TDMA, CDMA systems Broadband wireless, point-to-point microwave radios Instrumentation/ATE

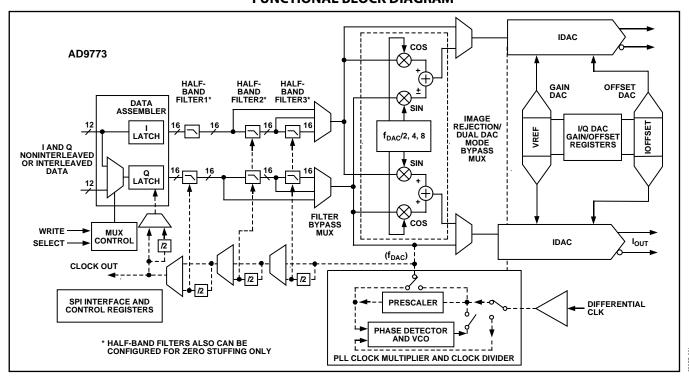

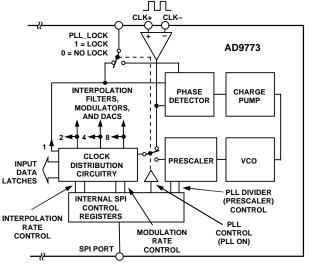

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

#### TABLE OF CONTENTS Applications......1 Functional Block Diagram ......1 DATACLK Driver Strength......31 PLL Enabled, One-Port Mode ......31 Product Highlights ......4 ONEPORTCLK Inversion......31 Specifications......5 DC Specifications ...... 5 Dynamic Specifications ...... 6 Absolute Maximum Ratings.......9 Modulation, No Interpolation......34 ESD Caution 9 Pin Configuration and Function Descriptions......10 Mode Control (Via SPI Port)......18 Interpolating (Complex Mix Mode)......38 Complex Modulation and Image Rejection of Baseband Serial Interface for Register Control......22 Image Rejection and Sideband Suppression of Modulated Carriers .......41 Instruction Byte ......23 Applying the Output Configurations.......46 Differential Coupling Using an Op Amp.......47 Interfacing the AD9773 with the AD8345 Quadrature Ordering Guide ......58 Sleep/Power-Down Modes......29 **REVISION HISTORY** Changes to Figure 108 ......54 10/07—Rev. C to Rev. D Updated Outline Dimensions ...... 58 Changes to Figure 32 ......22

| 1/06—Rev. B to Rev. C                          |           |

|------------------------------------------------|-----------|

| Updated Formatting                             | Universal |

| Changes to Figure 32                           | 22        |

| Changes to Figure 108                          | 55        |

| Updated Outline Dimensions                     | 58        |

| Changes to Ordering Guide                      | 58        |

|                                                |           |

| 4/04—Data Sheet Changed from Rev. A to Rev. B. |           |

| Update Layout                                  | Universal |

| Changes to DC Specifications                   | 5         |

| Changes to Absolute Maximum Ratings            | 9         |

| Changes to DAC Operation Section               | 25        |

| Inserted Figure 38                             | 25        |

| Changes to Figure 40                           |           |

| Changes to Table 11                            | 28        |

| Changes to Programmable PLL Section            | 29        |

| Changes to Power Dissipation Section           | 29        |

| Changes to Figures 49, 50, and 51              | 29        |

| Changes to PLL Enabled, One-Port Mode Section  | 31        |

| Changes to PLL Disabled, One-Port Mode Section | 32        |

| Changes to Figure 102                          | 49        |

| Changes to Figure 104                          | 50        |

| Updated Ordering Guide                         | 58        |

| Updated Outline Dimensions                     | 58        |

| 3/03—Data Sheet Changed from Rev. 0 to Rev. A.         |    |

|--------------------------------------------------------|----|

| Edits to Features                                      | 1  |

| Edits to DC Specifications                             |    |

| Edits to Dynamic Specifications                        |    |

| Edits to Pin Function Descriptions                     |    |

| Edits to Table I                                       | 14 |

| Edits to Register Description—Address 02h Section      | 15 |

| Edits to Register Description—Address 03h Section      |    |

| Edits to Register Description—Address 07h, 0Bh Section | 16 |

| Edits to Equation 1                                    | 16 |

| Edits to MSB/LSB Transfers Section                     | 18 |

| Changes to Figure 8                                    | 20 |

| Edits to Programmable PLL Section                      |    |

| Added New Figure 14                                    |    |

| Renumbered Figures 15 through 69                       | 22 |

| Add Two-Port Data Input Mode Section                   | 23 |

| Edits to PLL Enabled, Two-Port Mode Section            | 24 |

| Edits to Figure 19                                     | 24 |

| Edits to Figure 21                                     | 25 |

| Edits to PLL Disabled, Two-Port Mode Section           | 25 |

| Edits to Figure 22                                     | 25 |

| Edits to Figure 23                                     | 26 |

| Edits to Figure 26a                                    | 27 |

| Edits to Complex Modulation and Image Rejection of     |    |

| Baseband Signals Section                               | 31 |

| Changes to Figures 53 and 54                           | 38 |

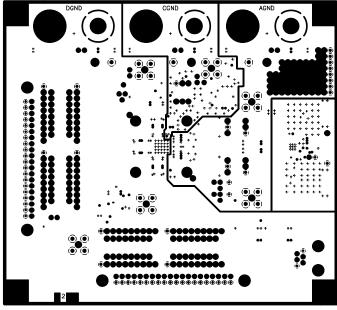

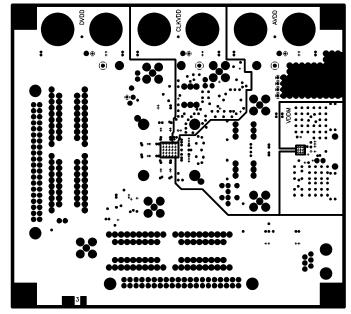

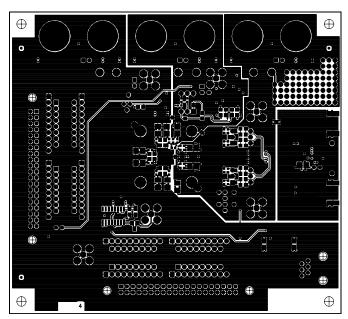

| Edits to Evaluation Board Section                      | 39 |

| Changes to Figures 56 through 59                       | 40 |

| Replaced Figures 60 through 69                         | 42 |

| Updated Outline Dimensions                             | 49 |

## **GENERAL DESCRIPTION**

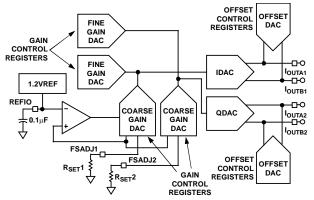

The AD9773  $^{1}$  is the 12-bit member of the AD977x pincompatible, high performance, programmable  $2\times/4\times/8\times$  interpolating TxDAC+ $^{\circ}$  family. The AD977x family features a serial port interface (SPI) that provides a high level of programmability, thus allowing for enhanced system-level options. These options include selectable  $2\times/4\times/8\times$  interpolation filters; fs/2, fs/4, or fs/8 digital quadrature modulation with image rejection; a direct IF mode; programmable channel gain and offset control; programmable internal clock divider; straight binary or twos complement data interface; and a single-port or dual-port data interface.

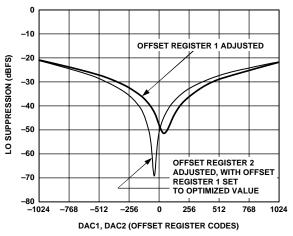

The selectable  $2\times/4\times/8\times$  interpolation filters simplify the requirements of the reconstruction filters while simultaneously enhancing the TxDAC+ family's pass-band noise/distortion performance. The independent channel gain and offset adjust registers allow the user to calibrate LO feedthrough and sideband suppression errors associated with analog quadrature modulators. The 6 dB of gain adjustment range can also be used to control the output power level of each DAC.

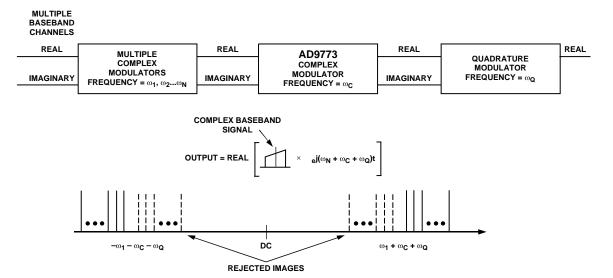

The AD9773 features the ability to perform fs/2, fs/4, and fs/8 digital modulation and image rejection when combined with an analog quadrature modulator. In this mode, the AD9773 accepts I and Q complex data (representing a single or multicarrier waveform), generates a quadrature modulated IF signal along with its orthogonal representation via its dual DACs, and presents these two reconstructed orthogonal IF carriers to an analog quadrature modulator to complete the image rejection upconversion process. Another digital modulation mode (for example, the direct IF mode) allows the original baseband signal representation to be frequency translated such that pairs of images fall at multiples of one-half the DAC update rate.

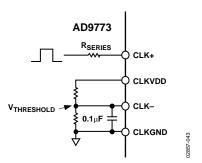

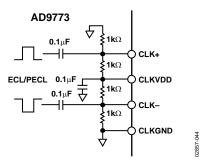

The AD977x family includes a flexible clock interface accepting differential or single-ended sine wave or digital logic inputs. An internal PLL clock multiplier is included and generates the necessary on-chip high frequency clocks. It can also be disabled to allow the use of a higher performance external clock source. An internal programmable divider simplifies clock generation in the converter when using an external clock source. A flexible data input interface allows for straight binary or twos complement formats and supports single-port interleaved or dual-port data.

Dual high performance DAC outputs provide a differential current output programmable over a 2 mA to 20 mA range. The AD9773 is manufactured on an advanced 0.35 micron CMOS process, operates from a single supply of 3.1 V to 3.5 V, and consumes 1.2 W of power.

Targeted at a wide dynamic range, multicarrier, and multistandard systems, the superb baseband performance of the AD9773 is ideal for wide band CDMA, multicarrier CDMA, multicarrier TDMA, multicarrier GSM, and high performance systems employing high order QAM modulation schemes. The image rejection feature simplifies and can help to reduce the number of signal band filters needed in a transmit signal chain. The direct IF mode helps to eliminate a costly mixer stage for a variety of communications systems.

## **PRODUCT HIGHLIGHTS**

- 1. The AD9773 is the 12-bit member of the AD977x pin compatible, high performance, programmable 2×/4×/8× interpolating TxDAC+ family.

- 2. Direct IF transmission is possible for 70 MHz + IFs through a novel digital mixing process.

- 3.  $f_s/2$ ,  $f_s/4$ , and  $f_s/8$  digital quadrature modulation and user selectable image rejection simplify/remove cascaded SAW filter stages.

- 4. A  $2\times/4\times/8\times$  user selectable interpolating filter eases data rate and output signal reconstruction filter requirements.

- 5. User selectable twos complement/straight binary data coding.

- User programmable channel gain control over 1 dB range in 0.01 dB increments.

- 7. User programmable channel offset control  $\pm 10\%$  over the FSR.

- 8. Ultrahigh speed 400 MSPS DAC conversion rate.

- 9. Internal clock divider provides data rate clock for easy interfacing.

- 10. Flexible clock input with single-ended or differential input, CMOS, or 1 V p-p LO sine wave input capability.

- 11. Low power: Complete CMOS DAC operates on 1.2 W from a 3.1 V to 3.5 V single supply. The 20 mA full-scale current can be reduced for lower power operation, and several sleep functions reduce power during idle periods.

- 12. On-chip voltage reference: The AD9773 includes a 1.20 V temperature compensated band gap voltage reference.

- 13. 80-lead thin quad flat package, exposed pad (TQFP\_EP).

<sup>&</sup>lt;sup>1</sup> Protected by U.S. Patent Numbers 5,568,145; 5,689,257; and 5,703,519. Other patents pending.

# **SPECIFICATIONS DC SPECIFICATIONS**

$T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , AVDD = 3.3 V, CLKVDD = 3.3 V, DVDD = 3.3 V, PLLVDD = 3.3 V,  $I_{\text{OUTFS}} = 20 \text{ mA}$ , unless otherwise noted.

Table 1.

| Table 1.  Parameter                                      | Min   | Тур       | Max        | Unit                |

|----------------------------------------------------------|-------|-----------|------------|---------------------|

| RESOLUTION                                               | 12    | -75       |            | Bits                |

| DC Accuracy <sup>1</sup>                                 |       |           |            |                     |

| Integral Nonlinearity                                    | -1.5  | ±0.4      | +1.5       | LSB                 |

| Differential Nonlinearity                                | -1    | ±0.2      | +1         | LSB                 |

| Monotonicity                                             |       |           |            | d temperature range |

| ANALOG OUTPUT (for IR and 2R Gain Setting Modes)         |       |           | этс. эрссс |                     |

| Offset Error                                             | -0.02 | ±0.01     | +0.02      | % of FSR            |

| Gain Error (with Internal Reference)                     | -1.0  | _0.0.     | +1.0       | % of FSR            |

| Gain Matching                                            | -1.0  | ±0.1      | +1.0       | % of FSR            |

| Full-Scale Output Current <sup>2</sup>                   | 2     | _0        | 20         | mA                  |

| Output Compliance Range                                  | -1.0  |           | +1.25      | V                   |

| Output Resistance                                        | 1.0   | 200       | 11.23      | kΩ                  |

| Output Capacitance                                       |       | 3         |            | pF                  |

| Gain, Offset Cal DACs, Monotonicity Guaranteed           |       | J         |            |                     |

| REFERENCE OUTPUT                                         |       |           |            |                     |

| Reference Voltage                                        | 1.14  | 1.20      | 1.26       | V                   |

| Reference Output Current <sup>3</sup>                    | ''' ' | 100       | 1.20       | nA                  |

| REFERENCE INPUT                                          |       | 100       |            |                     |

| Input Compliance Range                                   | 0.1   |           | 1.25       | V                   |

| Reference Input Resistance                               | 0.1   | 7         | 1.23       | kΩ                  |

| Small Signal Bandwidth                                   |       | 0.5       |            | MHz                 |

| TEMPERATURE COEFFICIENTS                                 |       | 0.5       |            | 141112              |

| Offset Drift                                             |       | 0         |            | ppm of FSR/°C       |

| Gain Drift (With Internal Reference)                     |       | 50        |            | ppm of FSR/°C       |

| Reference Voltage Drift                                  |       | ±50       |            | ppm/°C              |

| POWER SUPPLY                                             |       | ±30       |            | ррпі, с             |

| AVDD                                                     |       |           |            |                     |

| Voltage Range                                            | 3.1   | 3.3       | 3.5        | V                   |

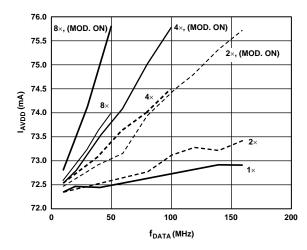

| Analog Supply Current (I <sub>AVDD</sub> ) <sup>4</sup>  | 3.1   | 72.5      | 76         | mA                  |

| l <sub>AVDD</sub> in Sleep Mode                          |       | 23.3      | 26         | mA                  |

| CLKVDD                                                   |       | 23.3      | 20         |                     |

| Voltage Range                                            | 3.1   | 3.3       | 3.5        | V                   |

| Clock Supply Current (I <sub>CLKVDD</sub> ) <sup>4</sup> | 3.1   | 8.5       | 10.0       | mA                  |

| CLKVDD (PLL ON)                                          |       | 0.5       | 10.0       |                     |

| Clock Supply Current (I <sub>CLKVDD</sub> )              |       | 23.5      |            | mA                  |

| DVDD                                                     |       | 23.3      |            | 11174               |

| Voltage Range                                            | 3.1   | 3.3       | 3.5        | V                   |

| Digital Supply Current (I <sub>DVDD</sub> ) <sup>4</sup> | 3.1   | 3.5<br>34 | 3.5<br>41  | mA                  |

| Nominal Power Dissipation                                |       | 380       | 410        | mW                  |

| P <sub>DIS</sub> <sup>5</sup>                            |       | 1.75      | 710        | W                   |

| P <sub>DIS</sub> in PWDN                                 |       | 6.0       |            | mW                  |

| Power Supply Rejection Ratio—AVDD                        |       | ±0.4      |            | % of FSR/V          |

| OPERATING RANGE                                          | -40   | ±0.4      | +85        | % OI F3N/V          |

| OFENATING KANGE                                          | -40   |           | +00        | 1 -                 |

<sup>&</sup>lt;sup>1</sup> Measured at I<sub>OUTA</sub> driving a virtual ground.

<sup>&</sup>lt;sup>2</sup> Nominal full-scale current, l<sub>OUTFS</sub>, is 32× the l<sub>REF</sub> current. <sup>3</sup> Use an external amplifier to drive any external load.

$<sup>^4</sup>$  100 MSPS  $f_{DAC}$  with  $f_{OUT} = 1$  MHz, all supplies = 3.3 V, no interpolation, no modulation.

$<sup>^{5}</sup>$  400 MSPS  $f_{DAC}$ ,  $f_{DATA} = 50$  MSPS,  $f_{S}/2$  modulation, PLL enabled.

## **DYNAMIC SPECIFICATIONS**

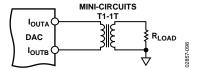

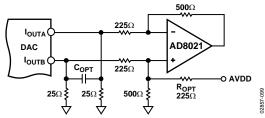

$T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , AVDD = 3.3 V, CLKVDD = 3.3 V, DVDD = 3.3 V, PLLVDD = 0 V,  $I_{\text{OUTFS}}$  = 20 mA, interpolation = 2×, differential transformer-coupled output, 50  $\Omega$  doubly terminated, unless otherwise noted.

Table 2.

| Parameter                                                                                          | Min | Тур Мах | Unit  |

|----------------------------------------------------------------------------------------------------|-----|---------|-------|

| DYNAMIC PERFORMANCE                                                                                |     |         |       |

| Maximum DAC Output Update Rate (fDAC)                                                              | 400 |         | MSPS  |

| Output Settling Time (t <sub>st</sub> ) (to 0.025%)                                                |     | 11      | ns    |

| Output Rise Time (10% to 90%) <sup>1</sup>                                                         |     | 0.8     | ns    |

| Output Fall Time (10% to 90%) <sup>1</sup>                                                         |     | 0.8     | ns    |

| Output Noise (loutfs = 20 mA)                                                                      |     | 50      | pA√Hz |

| AC LINEARITY—BASEBAND MODE                                                                         |     |         |       |

| Spurious-Free Dynamic Range (SFDR) to Nyquist ( $f_{OUT} = 0$ dBFS)                                |     |         |       |

| $f_{DATA} = 100 \text{ MSPS, } f_{OUT} = 1 \text{ MHz}$                                            | 70  | 84.5    | dBc   |

| $f_{DATA} = 65$ MSPS, $f_{OUT} = 1$ MHz                                                            |     | 83      | dBc   |

| $f_{DATA} = 65$ MSPS, $f_{OUT} = 15$ MHz                                                           |     | 79      | dBc   |

| $f_{DATA} = 78 \text{ MSPS}, f_{OUT} = 1 \text{ MHz}$                                              |     | 83      | dBc   |

| $f_{DATA} = 78 \text{ MSPS}, f_{OUT} = 15 \text{ MHz}$                                             |     | 77      | dBc   |

| $f_{DATA} = 160 \text{ MSPS, } f_{OUT} = 1 \text{ MHz}$                                            |     | 75      | dBc   |

| $f_{DATA} = 160 \text{ MSPS, } f_{OUT} = 15 \text{ MHz}$                                           |     | 77      | dBc   |

| Spurious-Free Dynamic Range Within a 1 MHz Window                                                  |     |         |       |

| $f_{OUT} = 0$ dBFS, $f_{DATA} = 100$ MSPS, $f_{OUT} = 1$ MHz                                       | 72  | 92.6    | dBc   |

| Two-Tone Intermodulation (IMD) to Nyquist ( $f_{OUT1} = f_{OUT2} = -6 \text{ dBFS}$ )              |     |         |       |

| $f_{DATA} = 65$ MSPS, $f_{OUT1} = 10$ MHz; $f_{OUT2} = 11$ MHz                                     |     | 80      | dBc   |

| $f_{DATA} = 65$ MSPS, $f_{OUT1} = 20$ MHz; $f_{OUT2} = 21$ MHz                                     |     | 75      | dBc   |

| $f_{DATA} = 78$ MSPS, $f_{OUT1} = 10$ MHz; $f_{OUT2} = 11$ MHz                                     |     | 80      | dBc   |

| $f_{DATA} = 78$ MSPS, $f_{OUT1} = 20$ MHz; $f_{OUT2} = 21$ MHz                                     |     | 75      | dBc   |

| $f_{DATA} = 160 \text{ MSPS}$ , $f_{OUT1} = 10 \text{ MHz}$ ; $f_{OUT2} = 11 \text{ MHz}$          |     | 80      | dBc   |

| $f_{DATA} = 160 \text{ MSPS}$ , $f_{OUT1} = 20 \text{ MHz}$ ; $f_{OUT2} = 21 \text{ MHz}$          |     | 75      | dBc   |

| Total Harmonic Distortion (THD)                                                                    |     |         |       |

| $f_{DATA} = 100 \text{ MSPS}, f_{OUT} = 1 \text{ MHz}; 0 \text{ dBFS}$                             | -70 | -82.4   | dB    |

| Signal-to-Noise Ratio (SNR)                                                                        |     |         |       |

| $f_{DATA} = 78 \text{ MSPS}, f_{OUT} = 5 \text{ MHz}; 0 \text{ dBFS}$                              |     | 70      | dB    |

| $f_{DATA} = 160 \text{ MSPS}, f_{OUT} = 5 \text{ MHz}; 0 \text{ dBFS}$                             |     | 69      | dB    |

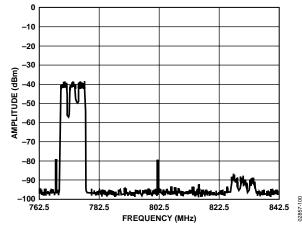

| Adjacent Channel Power Ratio (ACPR)                                                                |     |         |       |

| WCDMA with 3.84 MHz BW, 5 MHz Channel Spacing                                                      |     |         |       |

| $IF = Baseband, f_{DATA} = 76.8 MSPS$                                                              |     | 69      | dBc   |

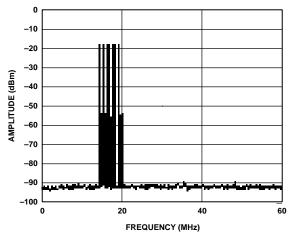

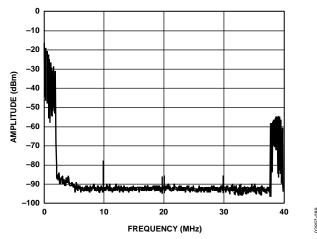

| $IF = 19.2 \text{ MHz}, f_{DATA} = 76.8 \text{ MSPS}$                                              |     | 69      | dBc   |

| Four-Tone Intermodulation                                                                          |     |         |       |

| 21 MHz, 22 MHz, 23 MHz, and 24 MHz at $-12$ dBFS ( $f_{DATA} = MSPS$ , Missing Center)             |     | 73      | dBFS  |

| AC LINEARITY—IF MODE                                                                               |     |         |       |

| Four-Tone Intermodulation at IF = 200 MHz                                                          |     |         |       |

| 201 MHz, 202 MHz, 203 MHz, and 204 MHz at $-12$ dBFS ( $f_{DATA} = 160$ MSPS, $f_{DAC} = 320$ MHz) |     | 69      | dBFS  |

$<sup>^{\</sup>mbox{\tiny 1}}$  Measured single-ended into 50  $\Omega$  load.

# **DIGITAL SPECIFICATIONS**

$T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , AVDD = 3.3 V, CLKVDD = 3.3 V, PLLVDD = 0 V, DVDD = 3.3 V,  $I_{\text{OUTFS}} = 20$  mA, unless otherwise noted.

Table 3.

| Parameter                                              | Min       | Тур | Max  | Unit |

|--------------------------------------------------------|-----------|-----|------|------|

| DIGITAL INPUTS                                         |           |     |      |      |

| Logic 1 Voltage                                        | 2.1       | 3   |      | V    |

| Logic 0 Voltage                                        |           | 0   | 0.9  | V    |

| Logic 1 Current                                        | -10       |     | +10  | μΑ   |

| Logic 0 Current                                        | -10       |     | +10  | μΑ   |

| Input Capacitance                                      |           | 5   |      | pF   |

| CLOCK INPUTS                                           |           |     |      |      |

| Input Voltage Range                                    | 0         |     | 3    | V    |

| Common-Mode Voltage                                    | 0.75      | 1.5 | 2.25 | V    |

| Differential Voltage                                   | 0.5       | 1.5 |      | V    |

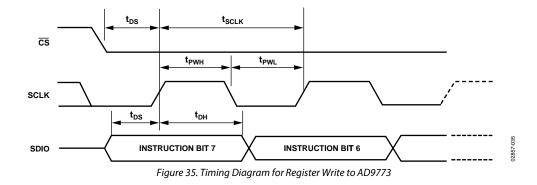

| SERIAL CONTROL BUS                                     |           |     |      |      |

| Maximum SCLK Frequency (fslck)                         | 15        |     |      | MHz  |

| Minimum Clock Pulse Width High (t <sub>PWH</sub> )     | 30        |     |      | ns   |

| Minimum Clock Pulse Width Low (t <sub>PWL</sub> )      | 30        |     |      | ns   |

| Maximum Clock Rise/Fall Time                           |           |     | 1    | ms   |

| Minimum Data/Chip Select Setup Time (t <sub>DS</sub> ) | 25        |     |      | ns   |

| Minimum Data Hold Time (t <sub>DH</sub> )              | 0         |     |      | ns   |

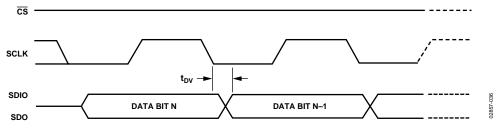

| Maximum Data Valid Time (t <sub>DV</sub> )             |           |     | 30   | ns   |

| RESET Pulse Width                                      | 1.5       |     |      | ns   |

| Inputs (SDI, SDIO, SCLK, CSB)                          |           |     |      |      |

| Logic 1 Voltage                                        | 2.1       | 3   |      | V    |

| Logic 0 Voltage                                        |           | 0   | 0.9  | V    |

| Logic 1 Current                                        | -10       |     | +10  | μΑ   |

| Logic 0 Current                                        | -10       |     | +10  | μΑ   |

| Input Capacitance                                      |           | 5   |      | pF   |

| SDIO Output                                            |           |     |      |      |

| Logic 1 Voltage                                        | DRVDD – 0 | .6  |      | V    |

| Logic 0 Voltage                                        |           |     | 0.4  | V    |

| Logic 1 Current                                        | 30        | 50  |      | mA   |

| Logic 0 Current                                        | 30        | 50  |      | mA   |

## **DIGITAL FILTER SPECIFICATIONS**

Table 4. Half-Band Filter No. 1 (43 Coefficients)

| Table 4. Hall-Band Filter No. 1 (43 Coefficients) |             |  |  |  |  |

|---------------------------------------------------|-------------|--|--|--|--|

| Тар                                               | Coefficient |  |  |  |  |

| 1, 43                                             | 8           |  |  |  |  |

| 2, 42                                             | 0           |  |  |  |  |

| 3, 41                                             | -29         |  |  |  |  |

| 4, 40                                             | 0           |  |  |  |  |

| 5, 39                                             | 67          |  |  |  |  |

| 6, 38                                             | 0           |  |  |  |  |

| 7, 37                                             | -134        |  |  |  |  |

| 8, 36                                             | 0           |  |  |  |  |

| 9, 35                                             | 244         |  |  |  |  |

| 10, 34                                            | 0           |  |  |  |  |

| 11, 33                                            | -414        |  |  |  |  |

| 12, 32                                            | 0           |  |  |  |  |

| 13, 31                                            | 673         |  |  |  |  |

| 14, 30                                            | 0           |  |  |  |  |

| 15, 29                                            | -1079       |  |  |  |  |

| 16, 28                                            | 0           |  |  |  |  |

| 17, 27                                            | 1772        |  |  |  |  |

| 18, 26                                            | 0           |  |  |  |  |

| 19, 25                                            | -3280       |  |  |  |  |

| 20, 24                                            | 0           |  |  |  |  |

| 21, 23                                            | 10,364      |  |  |  |  |

| 22                                                | 16,384      |  |  |  |  |

Table 5. Half-Band Filter No. 2 (19 Coefficients)

| 1 4010 0 1 1 1 4 1 1 1 4 1 1 | 1101 1 (1) 0001110101100) |

|------------------------------|---------------------------|

| Тар                          | Coefficient               |

| 1, 19                        | 19                        |

| 2, 18                        | 0                         |

| 3, 17                        | -120                      |

| 4, 16                        | 0                         |

| 5, 15                        | 438                       |

| 6, 14                        | 0                         |

| 7, 13                        | -1288                     |

| 8, 12                        | 0                         |

| 9, 11                        | 5047                      |

| 10                           | 8192                      |

|                              |                           |

Table 6. Half-Band Filter No. 3 (11 Coefficients)

| Тар   | Coefficient |

|-------|-------------|

| 1, 11 | 7           |

| 2, 10 | 0           |

| 3, 9  | <b>-53</b>  |

| 4, 8  | 0           |

| 5, 7  | 302         |

| 6     | 512         |

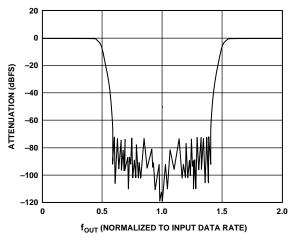

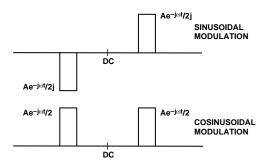

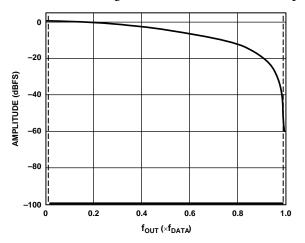

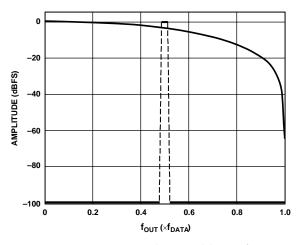

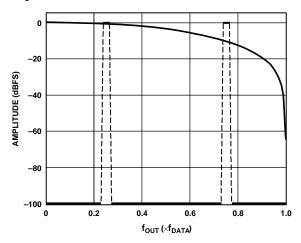

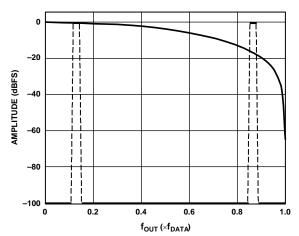

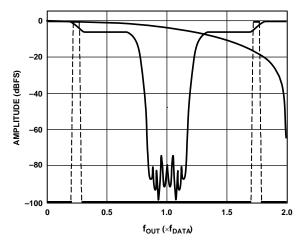

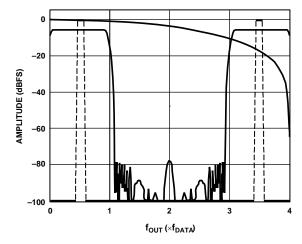

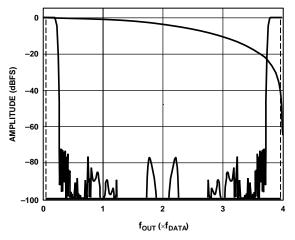

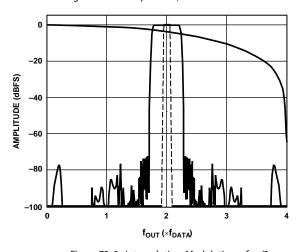

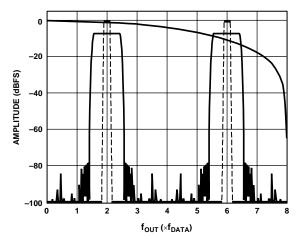

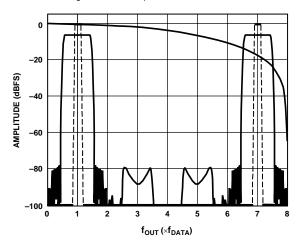

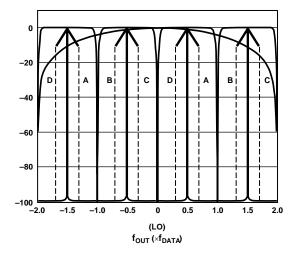

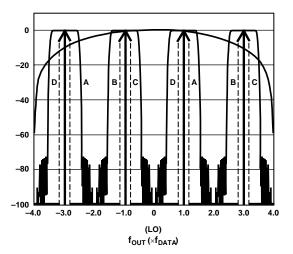

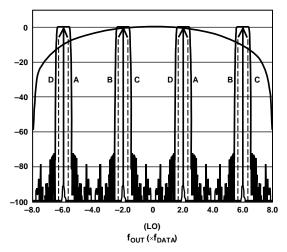

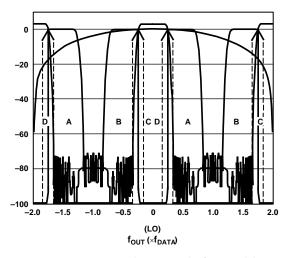

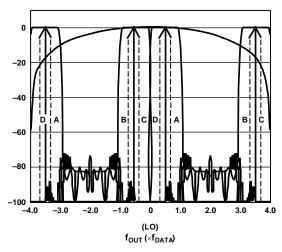

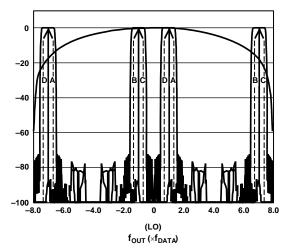

Figure 2. 2× Interpolating Filter Response

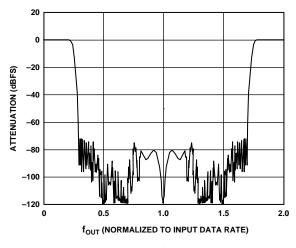

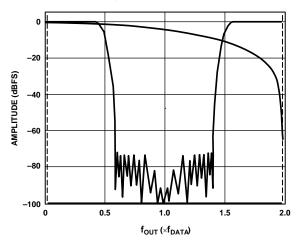

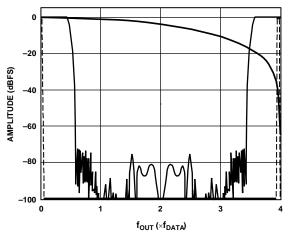

Figure 3.  $4 \times$  Interpolating Filter Response

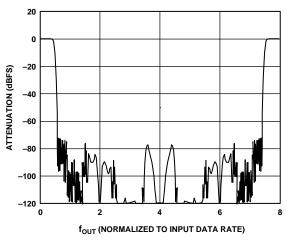

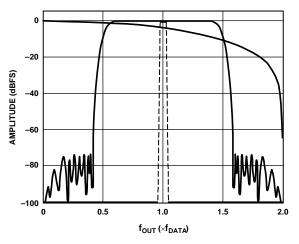

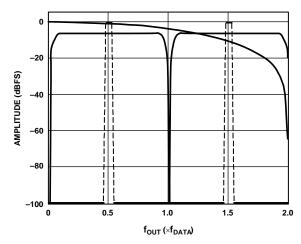

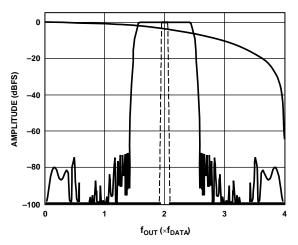

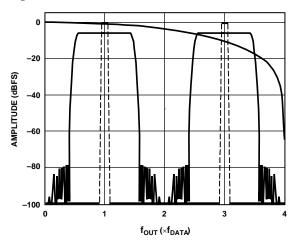

Figure 4. 8× Interpolating Filter Response

02857-004

02857-003

# **ABSOLUTE MAXIMUM RATINGS**

Table 7.

| Parameter                             | With Respect To    | Min  | Max          | Unit |

|---------------------------------------|--------------------|------|--------------|------|

| AVDD, DVDD, CLKVDD                    | AGND, DGND, CLKGND | -0.3 | +4.0         | V    |

| AVDD, DVDD, CLKVDD                    | AVDD, DVDD, CLKVDD | -4.0 | +4.0         | V    |

| AGND, DGND, CLKGND                    | AGND, DGND, CLKGND | -0.3 | +0.3         | V    |

| REFIO, FSADJ1/FSADJ2                  | AGND               | -0.3 | AVDD + 0.3   | V    |

| I <sub>OUTA</sub> , I <sub>OUTB</sub> | AGND               | -1.0 | AVDD + 0.3   | V    |

| P1B11 to P1B0, P2B11 to P2B0, RESET   | DGND               | -0.3 | DVDD + 0.3   | V    |

| DATACLK, PLL_LOCK                     | DGND               | -0.3 | DVDD + 0.3   | V    |

| CLK+, CLK-                            | CLKGND             | -0.3 | CLKVDD + 0.3 | V    |

| LPF                                   | CLKGND             | -0.3 | CLKVDD + 0.3 | V    |

| SPI_CSB, SPI_CLK, SPI_SDIO, SPI_SDO   | DGND               | -0.3 | DVDD + 0.3   | V    |

| Junction Temperature                  |                    |      | 125          | °C   |

| Storage Temperature                   |                    | -65  | +150         | °C   |

| Lead Temperature (10 sec)             |                    |      | 300          | °C   |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

## THERMAL CHARACTERISTICS

Thermal Resistance

80-lead thin quad flat package, exposed pad (TQFP\_EP)  $\theta_{JA}=23.5^{\circ}\text{C/W}$  (with thermal pad soldered to PCB)

## **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

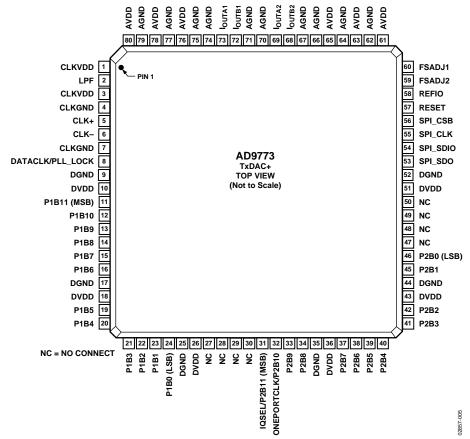

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 5. Pin Configuration

**Table 8. Pin Function Descriptions**

| Pin No.                                         | Function Descriptions  Mnemonic | Description                                                                                                                                                                                                                                                |

|-------------------------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3                                            | CLKVDD                          | Clock Supply Voltage.                                                                                                                                                                                                                                      |

| 2                                               | LPF                             | PLL Loop Filter.                                                                                                                                                                                                                                           |

| 2<br>4, 7                                       | CLKGND                          | Clock Supply Common.                                                                                                                                                                                                                                       |

| 5                                               | CLK+                            | Differential Clock Input.                                                                                                                                                                                                                                  |

| 6                                               | CLK-                            | Differential Clock Input.                                                                                                                                                                                                                                  |

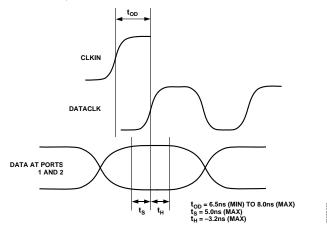

| 8                                               | DATACLK/PLL_LOCK                | With the PLL enabled, this pin indicates the state of the PLL. A read of a Logic 1 indicates the                                                                                                                                                           |

| 0                                               | DAMELINI EL_ESCR                | PLL is in the locked state. Logic 0 indicates the PLL has not achieved lock. This pin can also be programmed to act as either an input or output (Address 02h, Bit 3) DATACLK signal running at the input data rate.                                       |

| 9, 17, 25,<br>35, 44, 52                        | DGND                            | Digital Common.                                                                                                                                                                                                                                            |

| 10, 18, 26,<br>36, 43, 51                       | DVDD                            | Digital Supply Voltage.                                                                                                                                                                                                                                    |

| 11 to 16,<br>19 to 24,                          | P1B11 (MSB) to P1B0 (LSB)       | Port 1 Data Inputs.                                                                                                                                                                                                                                        |

| 27 to 30,<br>47 to 50                           | NC                              | No Connect.                                                                                                                                                                                                                                                |

| 31                                              | IQSEL/P2B11 (MSB)               | In one-port mode, IQSEL = 1 followed by a rising edge of the differential input clock latches the data into the I channel input register. IQSEL = 0 latches the data into the Q channel input register. In two-port mode, this pin becomes the Port 2 MSB. |

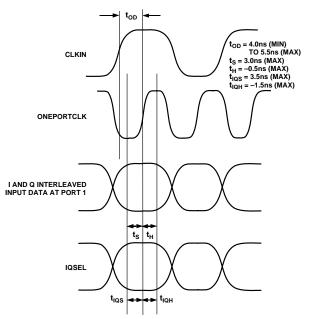

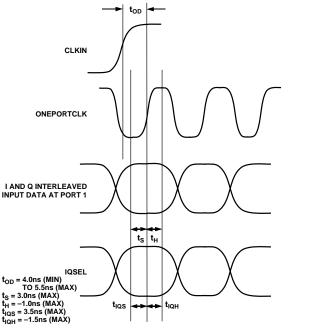

| 32                                              | ONEPORTCLK/P2B10                | With the PLL disabled and the AD9773 in one-port mode, this pin becomes a clock output that runs at twice the input data rate of the I and Q channels. This allows the AD9773 to accept and demux interleaved I and Q data to the I and Q input registers. |

| 33, 34, 37 to<br>42, 45, 46                     | P2B9 to P2B0 (LSB)              | Port 2 Data Inputs.                                                                                                                                                                                                                                        |

| 53                                              | SPI_SDO                         | In the case where SDIO is an input, SDO acts as an output. When SDIO becomes an output, SDO enters a high-Z state. This pin can also be used as an output for the data rate clock. For more information, see the Two-Port Data Input Mode section.         |

| 54                                              | SPI_SDIO                        | Bidirectional Data Pin. Data direction is controlled by Bit 7 of Register Address 00h. The default setting for this bit is 0, which sets SDIO as an input.                                                                                                 |

| 55                                              | SPI_CLK                         | Data input to the SPI port is registered on the rising edge of SPI_CLK. Data output on the SPI port is registered on the falling edge.                                                                                                                     |

| 56                                              | SPI_CSB                         | Chip Select/SPI Data Synchronization. On momentary logic high, resets SPI port logic and initializes instruction cycle.                                                                                                                                    |

| 57                                              | RESET                           | Logic 1 resets all of the SPI port registers, including Address 00h, to their default values. A software reset can also be done by writing a Logic 1 to SPI Register 00h, Bit 5. However, the software reset has no effect on the bits in Address 00h.     |

| 58                                              | REFIO                           | Reference Output, 1.2 V Nominal.                                                                                                                                                                                                                           |

| 59                                              | FSADJ2                          | Full-Scale Current Adjust, Q Channel.                                                                                                                                                                                                                      |

| 60                                              | FSADJ1                          | Full-Scale Current Adjust, I Channel.                                                                                                                                                                                                                      |

| 61, 63, 65,<br>76, 78, 80                       | AVDD                            | Analog Supply Voltage.                                                                                                                                                                                                                                     |

| 62, 64, 66,<br>67, 70, 71,<br>74, 75, 77,<br>79 | AGND                            | Analog Common.                                                                                                                                                                                                                                             |

| 68, 69                                          | IOUTB2, IOUTA2                  | Differential DAC Current Outputs, Q Channel.                                                                                                                                                                                                               |

| 72, 73                                          | IOUTB1, IOUTA1                  | Differential DAC Current Outputs, I Channel.                                                                                                                                                                                                               |

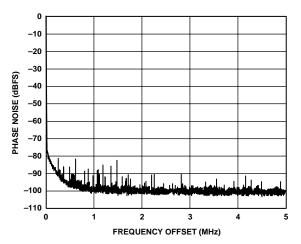

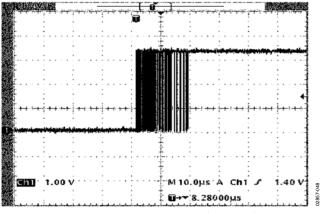

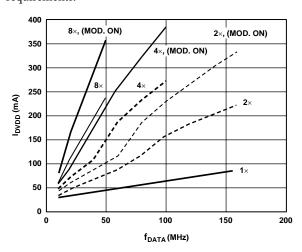

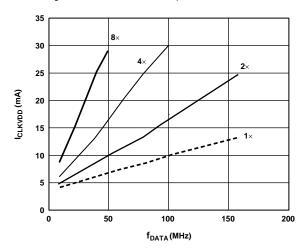

# TYPICAL PERFORMANCE CHARACTERISTICS

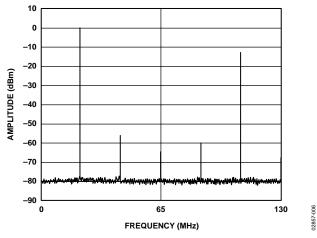

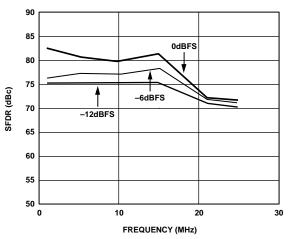

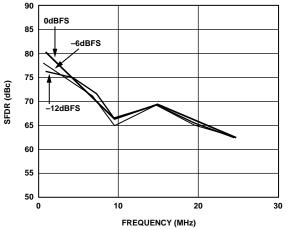

T = 25°C, AVDD = 3.3 V, CLKVDD = 3.3 V, DVDD = 3.3 V, I<sub>OUTFS</sub> = 20 mA, interpolation = 2×, differential transformer-coupled output, 50  $\Omega$  doubly terminated, unless otherwise noted.

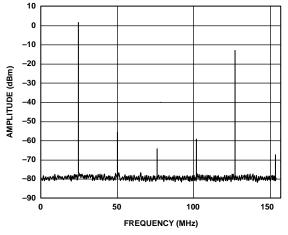

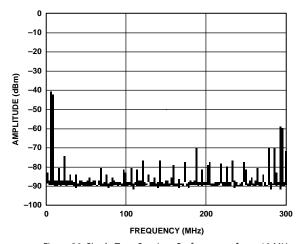

Figure 6. Single-Tone Spectrum @  $f_{DATA} = 65$  MSPS with  $f_{OUT} = f_{DATA}/3$

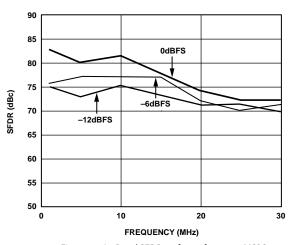

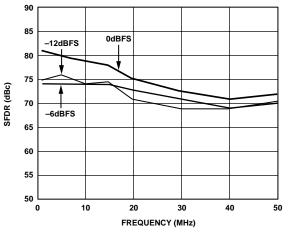

Figure 7. In-Band SFDR vs.  $f_{OUT} @ f_{DATA} = 65 \text{ MSPS}$

Figure 8. Out-of-Band SFDR vs.  $f_{OUT} @ f_{DATA} = 65 \text{ MSPS}$

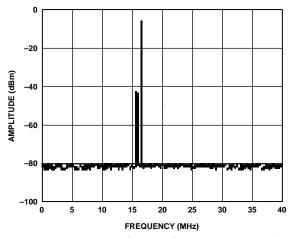

Figure 9. Single-Tone Spectrum @  $f_{DATA} = 78$  MSPS with  $f_{OUT} = f_{DATA}/3$

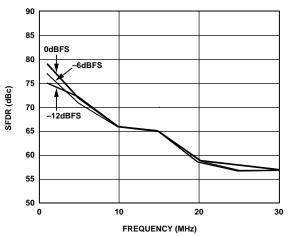

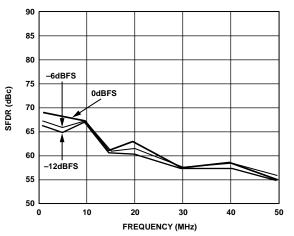

Figure 10. In-Band SFDR vs. f<sub>OUT</sub> @ f<sub>DATA</sub> = 78 MSPS

Figure 11. Out-of-Band SFDR vs.  $f_{OUT}$  @  $f_{DATA} = 78$  MSPS

02857-015

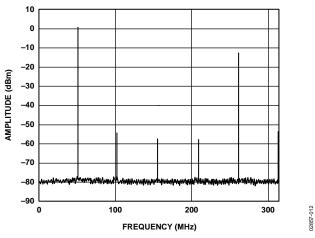

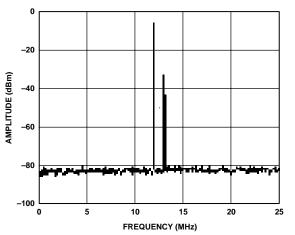

Figure 12. Single-Tone Spectrum @  $f_{DATA} = 160$  MSPS with  $f_{OUT} = f_{DATA}/3$

Figure 13. In-Band SFDR vs.  $f_{OUT} @ f_{DATA} = 160 \text{ MSPS}$

Figure 14. Out-of-Band SFDR vs.  $f_{OUT}$  @  $f_{DATA} = 160$  MSPS

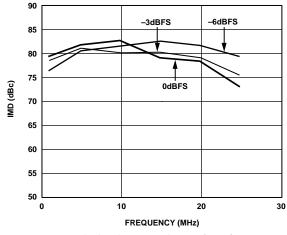

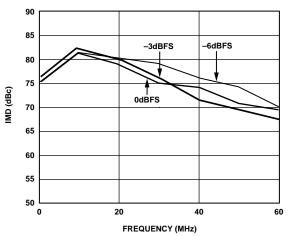

Figure 15. Third-Order IMD Products vs.  $f_{OUT} @ f_{DATA} = 65 \text{ MSPS}$

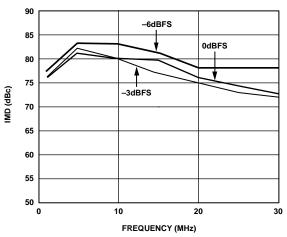

Figure 16. Third-Order IMD Products vs.  $f_{OUT} @ f_{DATA} = 78 \text{ MSPS}$

Figure 17. Third-Order IMD Products vs. f<sub>OUT</sub> @ f<sub>DATA</sub> = 160 MSPS

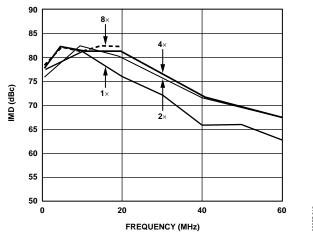

Figure 18. Third-Order IMD Products vs.  $f_{OUT}$  and Interpolation Rate,  $1 \times f_{DATA} = 160$  MSPS,  $2 \times f_{DATA} = 160$  MSPS,  $4 \times f_{DATA} = 80$  MSPS,  $8 \times f_{DATA} = 50$  MSPS

Figure 19. Third-Order IMD Products vs.  $A_{OUT}$  and Interpolation Rate,  $f_{DATA} = 50$  MSPS for All Cases,  $1 \times f_{DAC} = 50$  MSPS,  $2 \times f_{DAC} = 100$  MSPS,  $4 \times f_{DAC} = 200$  MSPS,  $8 \times f_{DAC} = 400$  MSPS

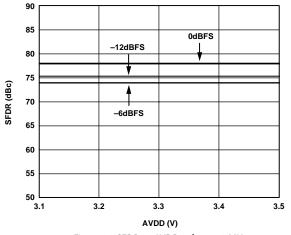

Figure 20. SFDR vs. AVDD @  $f_{OUT} = 10$  MHz,  $f_{DAC} = 320$  MSPS,  $f_{DATA} = 160$  MSPS

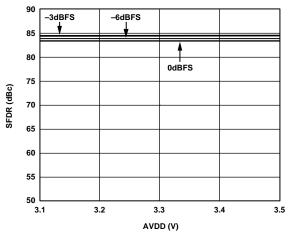

Figure 21. Third-Order IMD Products vs. AVDD @  $f_{OUT} = 10$  MHz,  $f_{DAC} = 320$  MSPS,  $f_{DATA} = 160$  MSPS

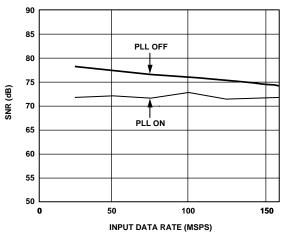

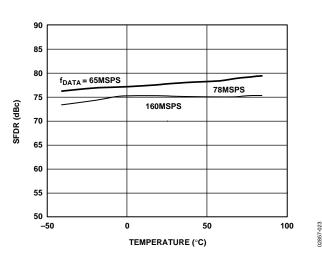

Figure 22. SNR vs. Data Rate for  $f_{OUT} = 5$  MHz

Figure 23. SFDR vs. Temperature @  $f_{OUT} = f_{DATA}/11$

Rev. D | Page 14 of 60

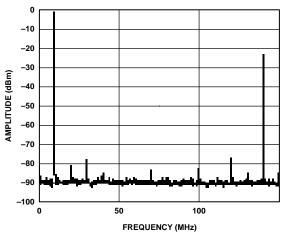

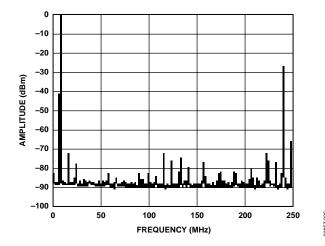

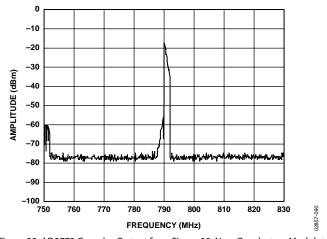

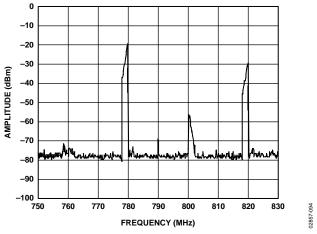

Figure 24. Single-Tone Spurious Performance,  $f_{OUT} = 10$  MHz,  $f_{DATA} = 150$  MSPS, No Interpolation

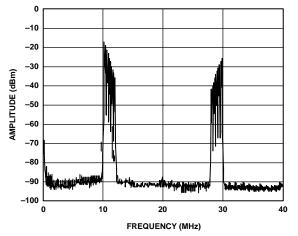

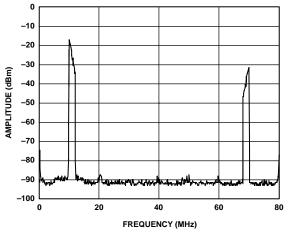

Figure 25. Two-Tone IMD Performance,  $f_{DATA} = 150$  MSPS, No Interpolation

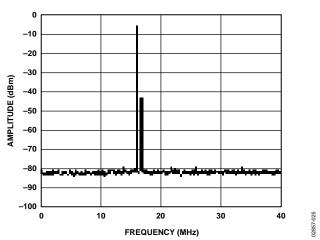

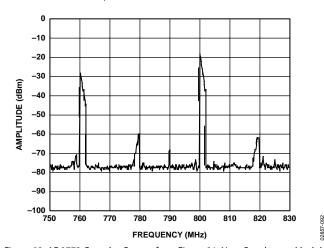

Figure 26. Single-Tone Spurious Performance,  $f_{OUT} = 10$  MHz,  $f_{DATA} = 150$  MSPS, Interpolation =  $2 \times$

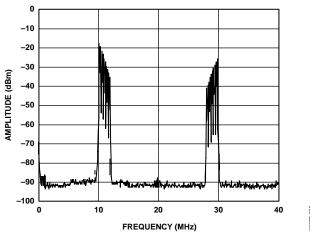

Figure 27. Two-Tone IMD Performance,  $f_{DATA} = 150$  MSPS, Interpolation =  $4 \times$

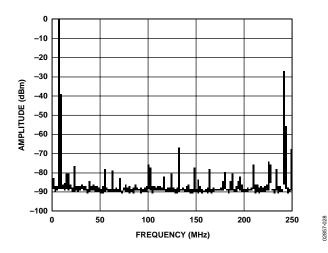

Figure 28. Single-Tone Spurious Performance,  $f_{OUT} = 10$  MHz,  $f_{DATA} = 80$  MSPS, Interpolation =  $4 \times$

Figure 29. Two-Tone IMD Performance,  $f_{OUT} = 10$  MHz,  $f_{DATA} = 50$  MSPS, Interpolation =  $8 \times$

Figure 30. Single-Tone Spurious Performance,  $f_{\text{OUT}}$  = 10 MHz,  $f_{\text{DATA}}$  = 50 MSPS, Interpolation = 8×

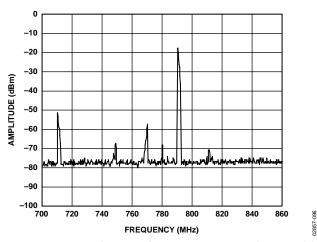

Figure 31. Eight-Tone IMD Performance,  $f_{DATA} = 160$  MSPS, Interpolation =  $8 \times$

Rev. D | Page 16 of 60

## **TERMINOLOGY**

## Adjacent Channel Power Ratio (ACPR)

A ratio, in dBc, between the measured power within a channel relative to its adjacent channel.

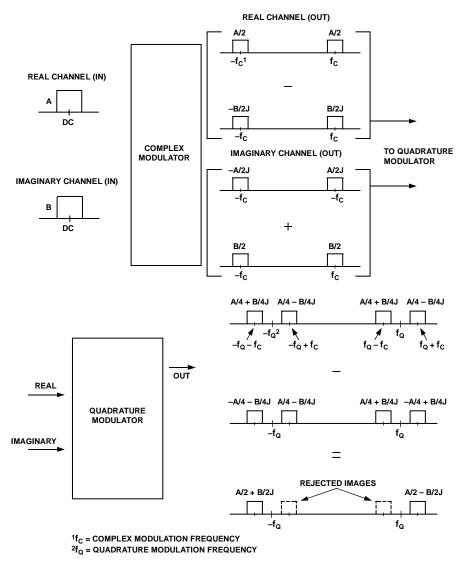

#### **Complex Image Rejection**

In a traditional two-part upconversion, two images are created around the second IF frequency. These images are redundant and have the effect of wasting transmitter power and system bandwidth. By placing the real part of a second complex modulator in series with the first complex modulator, either the upper or lower frequency image near the second IF can be rejected.

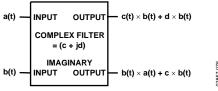

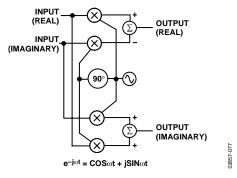

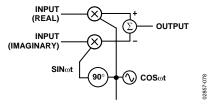

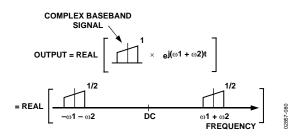

## **Complex Modulation**

The process of passing the real and imaginary components of a signal through a complex modulator (transfer function =  $e^{j\omega t}$  =  $cos\omega t$  +  $jsin\omega t$ ) and realizing real and imaginary components on the modulator output.

#### Differential Nonlinearity (DNL)

DNL is the measure of the variation in analog value, normalized to full scale, associated with a 1 LSB change in digital input code.

#### Gain Error

The difference between the actual and ideal output span. The actual span is determined by the output when all inputs are set to 1 minus the output when all inputs are set to 0.

## **Glitch Impulse**

Asymmetrical switching times in a DAC give rise to undesired output transients that are quantified by a glitch impulse. It is specified as the net area of the glitch in pV-s.

## **Group Delay**

Number of input clocks between an impulse applied at the device input and the peak DAC output current. A half-band FIR filter has constant group delay over its entire frequency range.

## Impulse Response

Response of the device to an impulse applied to the input.

## **Interpolation Filter**

If the digital inputs to the DAC are sampled at a multiple rate of  $f_{\text{DATA}}$  (interpolation rate), a digital filter can be constructed with a sharp transition band near  $f_{\text{DATA}}/2$ . Images that would typically appear around  $f_{\text{DAC}}$  (output data rate) can be greatly suppressed.

## **Linearity Error**

Also called integral nonlinearity (INL), linearity error is defined as the maximum deviation of the actual analog output from the ideal output, determined by a straight line drawn from 0 to full scale.

## Monotonicity

A DAC is monotonic if the output either increases or remains constant as the digital input increases.

#### **Offset Error**

The deviation of the output current from the ideal of 0 is called offset error. For  $I_{\text{OUTA}}$ , 0 mA output is expected when the inputs are all 0s. For  $I_{\text{OUTB}}$ , 0 mA output is expected when all inputs are set to 1.

## **Output Compliance Range**

The range of allowable voltage at the output of a current output DAC. Operation beyond the maximum compliance limits may cause either output stage saturation or breakdown, resulting in nonlinear performance.

#### **Pass Band**

Frequency band in which any input applied therein passes unattenuated to the DAC output.

## **Power Supply Rejection**

The maximum change in the full-scale output as the supplies are varied from minimum to maximum specified voltages.

## **Settling Time**

The time required for the output to reach and remain within a specified error band about its final value, measured from the start of the output transition.

## Signal-to-Noise Ratio (SNR)

SNR is the ratio of the rms value of the measured output signal to the rms sum of all other spectral components below the Nyquist frequency, excluding the first six harmonics and dc. The value for SNR is expressed in decibels.

## Spurious-Free Dynamic Range

The difference, in dB, between the rms amplitude of the output signal and the peak spurious signal over the specified bandwidth.

## **Stop-Band Rejection**

The amount of attenuation of a frequency outside the pass band applied to the DAC, relative to a full-scale signal applied at the DAC input within the pass band.

## **Temperature Drift**

It is specified as the maximum change from the ambient (25°C) value to the value at either  $T_{\text{MIN}}$  or  $T_{\text{MAX}}$ . For offset and gain drift, the drift is reported in ppm of full-scale range (FSR) per °C. For reference drift, the drift is reported in ppm per °C.

## **Total Harmonic Distortion (THD)**

THD is the ratio of the rms sum of the first six harmonic components to the rms value of the measured fundamental. It is expressed as a percentage or in decibels (dB).

# **MODE CONTROL (VIA SPI PORT)**

Table 9. Mode Control via SPI Port<sup>1</sup>

| Address | Bit 7                                                            | Bit 6                                                          | Bit 5                                                      | Bit 4                                                                                             | Bit 3                                                                              | Bit 2                                                                                               | Bit 1                                                                                                           | Bit 0                                                         |

|---------|------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 00h     | SDIO Bidirectional <b>0 = Input</b> 1 = I/O                      | LSB, MSB First <b>0 = MSB</b> 1 = LSB                          | Software<br>Reset<br>on Logic 1                            | Sleep<br>Mode<br>Logic 1<br>Shuts<br>Down the<br>DAC<br>Output<br>Currents                        | Power-Down<br>Mode Logic 1<br>Shuts Down<br>All Digital and<br>Analog<br>Functions | 1R/2R Mode<br>DAC Output<br>Current Set by<br>One or Two<br>External<br>Resistors<br>0 = 2R, 1 = 1R | PLL_LOCK<br>Indicator                                                                                           |                                                               |

| 01h     | Filter<br>Interpolation<br>Rate<br>(1×, 2×, 4×, 8×)              | Filter<br>Interpolation<br>Rate<br>(1×, 2×, 4×, 8×)            | Modulation<br>Mode<br>( <b>None</b> , fs/2,<br>fs/4, fs/8) | Modulation<br>Mode<br>( <b>None</b> , f <sub>s</sub> /2,<br>f <sub>s</sub> /4, f <sub>s</sub> /8) | 0 = No Zero Stuffing on Interpolation Filters, Logic 1 Enables Zero Stuffing       | 1 = Real Mix<br>Mode<br>0 = Complex<br>Mix Mode                                                     | $0 = \mathbf{e}^{-\mathbf{j}\mathbf{\omega}\mathbf{t}}$ $1 = \mathbf{e}^{+\mathbf{j}\mathbf{\omega}\mathbf{t}}$ | DATACLK/ PLL_LOCK <sup>2</sup> Select 0 = PLLLOCK 1 = DATACLK |

| 02h     | 0 = Signed<br>Input Data<br>1 = Unsigned                         | <b>0 = Two-Port</b><br><b>Mode</b><br>1 = One-Port<br>Mode     | DATACLK<br>Driver<br>Strength                              | DATACLK<br>Invert<br>0 = No<br>Invert<br>1 = Invert                                               |                                                                                    | ONEPORTCLK<br>Invert<br>0 = No Invert<br>1 = Invert                                                 | IQSEL<br>Invert<br>0 = No<br>Invert<br>1 = Invert                                                               | Q First <b>0 = I First</b> 1 = Q First                        |

| 03h     | Data Rate <sup>2</sup><br>Output Clock                           |                                                                |                                                            |                                                                                                   |                                                                                    |                                                                                                     | PLL Divide<br>(Prescaler)<br>Ratio                                                                              | PLL Divide<br>(Prescaler)<br>Ratio                            |

| 04h     | 0 = PLL OFF <sup>2</sup><br>1 = PLL ON                           | 0 = Automatic<br>Charge Pump<br>Control<br>1 =<br>Programmable |                                                            |                                                                                                   |                                                                                    | PLL Charge<br>Pump<br>Control                                                                       | PLL Charge<br>Pump<br>Control                                                                                   | PLL Charge<br>Pump<br>Control                                 |

| 05h     | IDAC<br>Fine Gain<br>Adjustment                                  | IDAC<br>Fine Gain<br>Adjustment                                | IDAC<br>Fine Gain<br>Adjustment                            | IDAC<br>Fine Gain<br>Adjustment                                                                   | IDAC<br>Fine Gain<br>Adjustment                                                    | IDAC<br>Fine Gain<br>Adjustment                                                                     | IDAC<br>Fine Gain<br>Adjustment                                                                                 | IDAC<br>Fine Gain<br>Adjustment                               |

| 06h     |                                                                  |                                                                |                                                            |                                                                                                   | IDAC<br>Coarse Gain<br>Adjustment                                                  | IDAC<br>Coarse Gain<br>Adjustment                                                                   | IDAC<br>Coarse<br>Gain<br>Adjustment                                                                            | IDAC<br>Coarse<br>Gain<br>Adjustment                          |

| 07h     | IDAC Offset<br>Adjustment<br>Bit 9                               | IDAC Offset<br>Adjustment<br>Bit 8                             | IDAC Offset<br>Adjustment<br>Bit 7                         | IDAC Offset<br>Adjustment<br>Bit 6                                                                | IDAC Offset<br>Adjustment<br>Bit 5                                                 | IDAC Offset<br>Adjustment<br>Bit 4                                                                  | IDAC Offset<br>Adjustment<br>Bit 3                                                                              | IDAC Offset<br>Adjustment<br>Bit 2                            |

| 08h     | IDAC IOFFSET Direction 0 = IOFFSET on IOUTA 1 = IOFFSET on IOUTB |                                                                |                                                            |                                                                                                   |                                                                                    |                                                                                                     | IDAC Offset<br>Adjustment<br>Bit 1                                                                              | IDAC Offset<br>Adjustment<br>Bit 0                            |

| 09h     | QDAC<br>Fine Gain<br>Adjustment                                  | QDAC<br>Fine Gain<br>Adjustment                                | QDAC<br>Fine Gain<br>Adjustment                            | QDAC<br>Fine Gain<br>Adjustment                                                                   | QDAC<br>Fine Gain<br>Adjustment                                                    | QDAC<br>Fine Gain<br>Adjustment                                                                     | QDAC<br>Fine Gain<br>Adjustment                                                                                 | QDAC<br>Fine Gain<br>Adjustment                               |

| Address | Bit 7                                                            | Bit 6                                 | Bit 5                                 | Bit 4                                 | Bit 3                                 | Bit 2                                 | Bit 1                                 | Bit 0                                 |

|---------|------------------------------------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|

| 0Ah     |                                                                  |                                       |                                       |                                       | QDAC<br>Coarse Gain<br>Adjustment     | QDAC<br>Coarse Gain<br>Adjustment     | QDAC<br>Coarse Gain<br>Adjustment     | QDAC<br>Coarse Gain<br>Adjustment     |

| 0Bh     | QDAC<br>Offset<br>Adjustment<br>Bit 9                            | QDAC<br>Offset<br>Adjustment<br>Bit 8 | QDAC<br>Offset<br>Adjustment<br>Bit 7 | QDAC<br>Offset<br>Adjustment<br>Bit 6 | QDAC<br>Offset<br>Adjustment<br>Bit 5 | QDAC<br>Offset<br>Adjustment<br>Bit 4 | QDAC<br>Offset<br>Adjustment<br>Bit 3 | QDAC<br>Offset<br>Adjustment<br>Bit 2 |

| 0Ch     | QDAC loffset Direction 0 = loffset on louta 1 = loffset on loutb |                                       |                                       |                                       |                                       |                                       | QDAC<br>Offset<br>Adjustment<br>Bit 1 | QDAC<br>Offset<br>Adjustment<br>Bit 0 |

| 0Dh     |                                                                  |                                       |                                       |                                       | Version<br>Register                   | Version<br>Register                   | Version<br>Register                   | Version<br>Register                   |

<sup>&</sup>lt;sup>1</sup> Default values are shown in bold.

<sup>&</sup>lt;sup>2</sup> See the Two-Port Data Input Mode section for more information.

#### REGISTER DESCRIPTION

#### Address 00h

**Bit 7:** Logic 0 (default) causes the SPI\_SDIO pin to act as an input during the data transfer (Phase 2) of the communications cycle. When set to 1, SPI\_SDIO can act as an input or output, depending on Bit 7 of the instruction byte.

**Bit 6:** Logic 0 (default) determines the direction (LSB/MSB first) of the communications and data transfer communications cycles. Refer to the MSB/LSB Transfers section for more details.

**Bit 5:** Writing a 1 to this bit resets the registers to their default values and restarts the chip. The RESET bit always reads back 0. Register Address 00h bits are not cleared by this software reset. However, a high level at the RESET pin forces all registers, including those in Address 00h, to their default state.

**Bit 4:** Sleep Mode. A Logic 1 to this bit shuts down the DAC output currents.

**Bit 3:** Power-Down Mode. Logic 1 shuts down all analog and digital functions except for the SPI port.

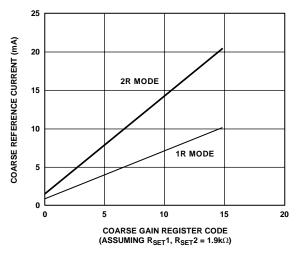

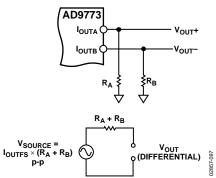

Bit 2: 1R/2R Mode. The default (0) places the AD9773 in two-resistor mode. In this mode, the  $I_{REF}$  currents for the I and Q DAC references are set separately by the  $R_{SET}$  resistors on FSADJ1 and FSADJ2 (Pin 59 and Pin 60). In 2R mode, assuming the coarse gain setting is full scale and the fine gain setting is zero,  $I_{FULLSCALE1} = 32 \times V_{REF}/FSADJ1$  and  $I_{FULLSCALE2} = 32 \times V_{REF}/FSADJ2$ . With this bit set to 1, the reference currents for both I and Q DACs are controlled by a single resistor on Pin 60.  $I_{FULLSCALE}$  in one-resistor mode for both I and Q DACs is half of what it would be in 2R mode, assuming all other conditions ( $R_{SET}$ , register settings) remain unchanged. The full-scale current of each DAC can still be set to 20 mA by choosing a resistor of half the value of the  $R_{SET}$  value used in 2R mode.

**Bit 1:** PLL\_LOCK Indicator. When the PLL is enabled, reading this bit gives the status of the PLL. A Logic 1 indicates the PLL is locked. A Logic 0 indicates an unlocked state.

#### Address 01h

**Bit 7 and Bit 6:** This is the filter interpolation rate according to Table 10.

## Table 10.

| 00 | 1× |

|----|----|

| 01 | 2× |

| 10 | 4× |

| 11 | 8× |

**Bit 5 and Bit 4**: This is the modulation mode according to Table 11.

#### Table 11.

| 00 | none    |

|----|---------|

| 01 | fs/2    |

| 10 | $f_s/4$ |

| 11 | $f_s/8$ |

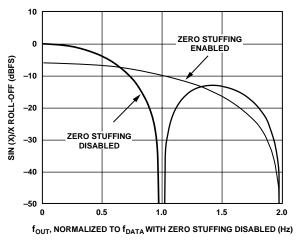

**Bit 3:** Logic 1 enables zero stuffing mode for interpolation filters.

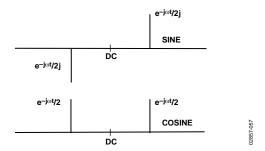

Bit 2: Default (1) enables the real mix mode. The I and Q data channels are individually modulated by  $f_s/2$ ,  $f_s/4$ , or  $f_s/8$  after the interpolation filters. However, no complex modulation is done. In the complex mix mode (Logic 0), the digital modulators on the I and Q data channels are coupled to create a digital complex modulator. When the AD9773 is applied in conjunction with an external quadrature modulator, rejection can be achieved of either the higher or lower frequency image around the second IF frequency (that is, the LO of the analog quadrature modulator external to the AD9773) according to the bit value of Register 01h, Bit 1.

**Bit 1:** Logic 0 (default) causes the complex modulation to be of the form  $e^{-j\omega t}$ , resulting in the rejection of the higher frequency image when the AD9773 is used with an external quadrature modulator. A Logic 1 causes the modulation to be of the form  $e^{+j\omega t}$ , which causes rejection of the lower frequency image.

**Bit 0:** In two-port mode, a Logic 0 (default) causes Pin 8 to act as a lock indicator for the internal PLL. A Logic 1 in this register causes Pin 8 to act as a DATACLK. For more information, see the Two-Port Data Input Mode section.

#### Address 02h

**Bit 7:** Logic 0 (default) causes data to be accepted on the inputs as twos complement. Logic 1 causes data to be accepted as straight binary.

**Bit 6:** Logic 0 (default) places the AD9773 in two-port mode. I and Q data enters the AD9773 via Port 1 and Port 2, respectively. A Logic 1 places the AD9773 in one-port mode in which interleaved I and Q data is applied to Port 1. See Table 8 for detailed information on the DATACLK/PLL\_LOCK, IQSEL, and ONEPORTCLK modes.

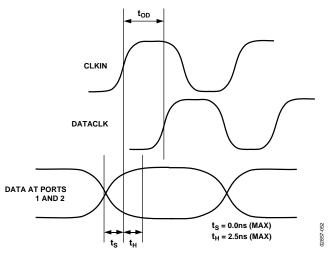

**Bit 5:** DATACLK Driver Strength. With the internal PLL disabled and this bit set to Logic 0, it is recommended that DATACLK be buffered. When this bit is set to Logic 1, DATACLK acts as a stronger driver capable of driving small capacitive loads.

Bit 4: Logic 0 (default). A value of 1 inverts DATACLK at Pin 8.

Bit 2: Logic 0 (default). A value of 1 inverts ONEPORTCLK at Pin 32.

**Bit 1:** The Logic 0 (default) causes IQSEL = 0 to direct input data to the I channel, while IQSEL = 1 directs input data to the Q channel.

**Bit 0:** The Logic 0 (default) defines IQ pairing as IQ, IQ, ... while programming a Logic 1 causes the pair ordering to be QI, QI, ....

#### Address 03h

**Bit 7:** Allows the data rate clock (divided down from the DAC clock) to be output at either the DATACLK pin (Pin 8) or at the SPI\_SDO pin (Pin 53). The default of 0 in this bit enables the data rate clock at DATACLK, while a 1 in this bit causes the data rate clock to be output at SPI\_SDO. For more information, see the Two-Port Data Input Mode section.

**Bit 1 and Bit 0:** Setting this divide ratio to a higher number allows the VCO in the PLL to run at a high rate (for best performance), while the DAC input and output clocks run substantially slower. The divider ratio is set according to Table 12.

#### Table 12.

| 00 | ÷1 |

|----|----|

| 01 | ÷2 |

| 10 | ÷4 |

| 11 | ÷8 |

#### Address 04h

**Bit 7:** Logic 0 (default) disables the internal PLL. Logic 1 enables the PLL.

**Bit 6:** Logic 0 (default) sets the charge pump control to automatic. In this mode, the charge pump bias current is controlled by the divider ratio defined in Address 03h, Bits 1 and 0. Logic 1 allows the user to manually define the charge pump bias current using Address 04h, Bits 2, 1, and 0. Adjusting the charge pump bias current allows the user to optimize the noise/settling performance of the PLL.

**Bit 2, Bit 1, and Bit 0**: With the charge pump control set to manual, these bits define the charge pump bias current according to Table 13.

#### Table 13.

| 000 | 50 μΑ  |

|-----|--------|

| 001 | 100 μΑ |

| 010 | 200 μΑ |

| 011 | 400 μΑ |

| 111 | 800 μΑ |

#### Address 05h, 09h

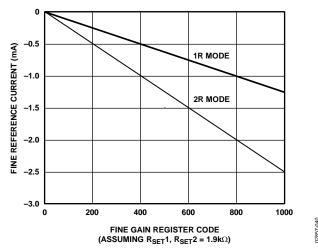

**Bit 7, Bit 6, Bit 5, Bit 4, Bit 3, Bit 2, Bit 1, and Bit 0:** These bits represent an 8-bit binary number (Bit 7 MSB) that defines the fine gain adjustment of the I (05h) and Q (09h) DAC according to Equation 1.

#### Address 06h, 0Ah

Bit 3, Bit 2, Bit 1, and Bit 0: These bits represent a 4-bit binary number (Bit 3 MSB) that defines the coarse gain adjustment of the I (06h) and Q (0Ah) DACs according to Equation 1.

## Address 07h, 0Bh

Bit 7, Bit 6, Bit 5, Bit 4, Bit 3, Bit 2, Bit 1, and Bit 0: These bits are used in conjunction with Address 08h, Address 0Ch, Bits [1:0].

## Address 08h, 0Ch

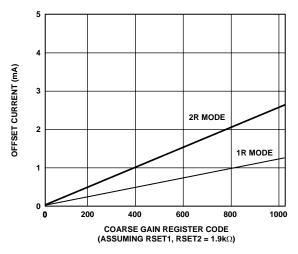

**Bit 1 and Bit 0:** The 10 bits from these two address pairs (07h, 08h and 0Bh, 0Ch) represent a 10-bit binary number that defines the offset adjustment of the I and Q DACs according to Equation 1: (07h, 0Bh: Bit 7 MSB; 08h, 0Ch: Bit 0 LSB).

#### Address 08h, 0Ch

**Bit 7:** This bit determines the direction of the offset of the I (08h) and Q (0Ch) DACs. A Logic 0 applies a positive offset current to I<sub>OUTA</sub>, while a Logic 1 applies a positive offset current to I<sub>OUTB</sub>. The magnitude of the offset current is defined by the bits in Addresses 07h, 0Bh, 08h, and 0Ch according to Equation 1.

Equation 1 shows  $I_{\text{OUTA}}$  and  $I_{\text{OUTB}}$  as a function of fine gain, coarse gain, and offset adjustment when using 2R mode. In 1R mode, the current  $I_{\text{REF}}$  is created by a single FSADJ1 resistor (Pin 60). This current is divided equally into each channel so that a scaling factor of one-half must be added to these equations for full-scale currents for both DACs and the offset.

$$\begin{split} I_{OUTA} = & \left[ \left( \frac{6 \times I_{REF}}{8} \right) \left( \frac{COARSE + 1}{16} \right) - \left( \frac{3 \times I_{REF}}{32} \right) \left( \frac{FINE}{256} \right) \right] \times \left[ \left( \frac{1024}{24} \right) \left( \frac{DATA}{2^{12}} \right) \right] (A) \\ I_{OUTB} = & \left[ \left( \frac{6 \times I_{REF}}{8} \right) \left( \frac{COARSE + 1}{16} \right) - \left( \frac{3 \times I_{REF}}{32} \right) \left( \frac{FINE}{256} \right) \right] \times \left[ \left( \frac{1024}{24} \right) \left( \frac{2^{12} - DATA - 1}{2^{12}} \right) \right] (A) \\ I_{OFFSET} = 4 \times I_{REF} \left( \frac{OFFSET}{1024} \right) (A) \end{split}$$

## **FUNCTIONAL DESCRIPTION**

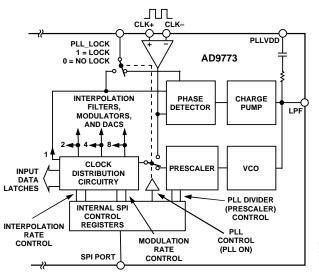

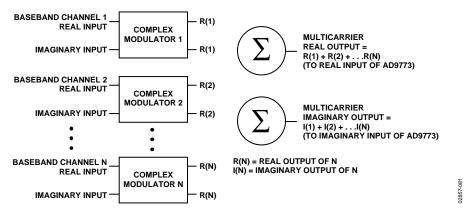

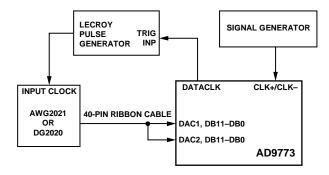

The AD9773 dual interpolating DAC consists of two data channels that can be operated completely independently or coupled to form a complex modulator in an image reject transmit architecture. Each channel includes three FIR filters, making the AD9773 capable of  $2\times$ ,  $4\times$ , or  $8\times$  interpolation. High speed input and output data rates can be achieved within the limitations shown in Table 14.

Table 14.

| Interpolation Rate (MSPS) | Input Data Rate<br>(MSPS) | DAC Sample Rate<br>(MSPS) |

|---------------------------|---------------------------|---------------------------|

| 1×                        | 160                       | 160                       |

| 2×                        | 160                       | 320                       |

| 4×                        | 100                       | 400                       |

| 8×                        | 50                        | 400                       |

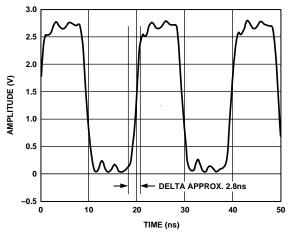

Both data channels contain a digital modulator capable of mixing the data stream with an LO of  $f_{DAC}/2$ ,  $f_{DAC}/4$ , or  $f_{DAC}/8$ , where  $f_{DAC}$  is the output data rate of the DAC. A zero stuffing feature is also included and can be used to improve pass-band flatness for signals being attenuated by the SIN(x)/x characteristic of the DAC output. The speed of the AD9773, combined with its digital modulation capability, enables direct IF conversion architectures at 70 MHz and higher.

The digital modulators on the AD9773 can be coupled to form a complex modulator. By using this feature with an external analog quadrature modulator, such as Analog Devices' AD8345, an image rejection architecture can be enabled. To optimize the image rejection capability, as well as LO feedthrough in this architecture, the AD9773 offers programmable (via the SPI port) gain and offset adjust for each DAC.

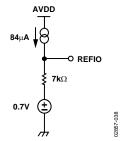

Also included on the AD9773 are a phase-locked loop (PLL) clock multiplier and a 1.20 V band gap voltage reference. With the PLL enabled, a clock applied to the CLK+/CLK- inputs is frequency multiplied internally and generates all necessary internal synchronization clocks. Each 12-bit DAC provides two complementary current outputs whose full-scale currents can be determined either from a single external resistor or independently from two separate resistors (see the 1R/2R Mode section). The AD9773 features a low jitter, differential clock input that provides excellent noise rejection while accepting a sine or square wave input. Separate voltage supply inputs are provided for each functional block to ensure optimum noise and distortion performance.

Sleep and power-down modes can be used to turn off the DAC output current (sleep) or the entire digital and analog sections (power-down) of the chip. An SPI-compliant serial port is used to program the many features of the AD9773. Note that in power-down mode, the SPI port is the only section of the chip still active.

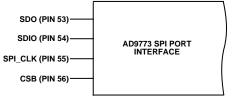

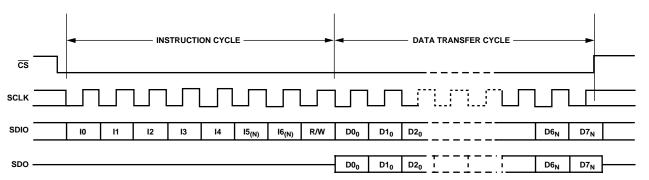

Figure 32. SPI Port Interface

## SERIAL INTERFACE FOR REGISTER CONTROL

The AD9773 serial port is a flexible, synchronous serial communications port that allows an easy interface to many industry-standard microcontrollers and microprocessors. The serial I/O is compatible with most synchronous transfer formats, including both the Motorola SPI and Intel® SSR protocols. The interface allows read/write access to all registers that configure the AD9773. Single- or multiple-byte transfers are supported as well as MSB first or LSB first transfer formats. The AD9773's serial interface port can be configured as a single pin I/O (SDIO) or two unidirectional pins for I/O (SDIO/SDO).

#### **GENERAL OPERATION OF THE SERIAL INTERFACE**

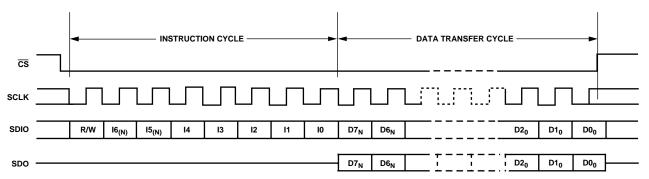

There are two phases to a communication cycle with the AD9773. Phase 1 is the instruction cycle, which is the writing of an instruction byte into the AD9773 coincident with the first eight SCLK rising edges. The instruction byte provides the AD9773 serial port controller with information regarding the data transfer cycle, which is Phase 2 of the communication cycle. The Phase 1 instruction byte defines whether the upcoming data transfer is read or write, the number of bytes in the data transfer, and the starting register address for the first byte of the data transfer. The first eight SCLK rising edges of each communication cycle are used to write the instruction byte into the AD9773.

A Logic 1 on the SPI\_CSB pin, followed by a logic low, resets the SPI port timing to the initial state of the instruction cycle. This is true regardless of the present state of the internal registers or the other signal levels present at the inputs to the SPI port. If the SPI port is in the middle of an instruction cycle or a data transfer cycle, none of the present data is written.

The remaining SCLK edges are for Phase 2 of the communication cycle. Phase 2 is the actual data transfer between the AD9773 and the system controller. Phase 2 of the communication cycle is a transfer of one to four data bytes, as determined by the instruction byte. Normally, using one multibyte transfer is the preferred method. However, single byte data transfers are useful to reduce CPU overhead when register access requires one byte only. Registers change immediately upon writing to the last bit of each transfer byte.

#### **INSTRUCTION BYTE**

The instruction byte contains the information shown in Table 15.

Table 15.

| N1 | N0 | Description      |

|----|----|------------------|

| 0  | 0  | Transfer 1 Byte  |

| 0  | 1  | Transfer 2 Bytes |

| 1  | 0  | Transfer 3 Bytes |

| 1  | 1  | Transfer 4 Bytes |

#### R/W

Bit 7 of the instruction byte determines whether a read or a write data transfer occurs after the instruction byte write. Logic 1 indicates read operation. Logic 0 indicates a write operation.

#### N1, N0

Bits 6 and 5 of the instruction byte determine the number of bytes to be transferred during the data transfer cycle. The bit decodes are shown in the following table.

|   | MSB |    |    |    |    |    |    | LSB |

|---|-----|----|----|----|----|----|----|-----|

| • | 17  | 16 | 15 | 14 | 13 | 12 | I1 | 10  |

|   | R/W | N1 | N0 | A4 | А3 | A2 | A1 | A0  |

#### A4, A3, A2, A1, and A0

Bits 4, 3, 2, 1, and 0 of the instruction byte determine which register is accessed during the data transfer portion of the communications cycle. For multibyte transfers, this address is the starting byte address. The remaining register addresses are generated by the AD9773.

#### SERIAL INTERFACE PORT PIN DESCRIPTIONS

#### SPI\_CLK (Pin 55)—Serial Clock

The serial clock pin is used to synchronize data to and from the AD9773 and to run the internal state machines. The SPI\_CLK maximum frequency is 15 MHz. All data input to the AD9773 is registered on the rising edge of SPI\_CLK. All data is driven out of the AD9773 on the falling edge of SPI\_CLK.

## SPI\_CSB (Pin 56)—Chip Select

Active low input starts and gates a communication cycle. It allows more than one device to be used on the same serial communications lines.

The SPI\_SDO and SPI\_SDIO pins go to a high impedance state when this input is high. Chip select should stay low during the entire communication cycle.

## SPI\_SDIO (Pin 54)—Serial Data I/O

Data is always written into the AD9773 on this pin. However, this pin can be used as a bidirectional data line. The configuration of this pin is controlled by Bit 7 of Register Address 00h. The default is Logic 0, which configures the SDIO pin as unidirectional.

## SPI\_SDO (Pin 53)—Serial Data Out

Data is read from this pin for protocols that use separate lines for transmitting and receiving data. In the case where the AD9773 operates in a single bidirectional I/O mode, this pin does not output data and is set to a high impedance state.

#### MSB/LSB TRANSFERS

The AD9773 serial port can support both most significant bit (MSB) first or least significant bit (LSB) first data formats. This functionality is controlled by the first LSB bit in Register 0. The default is MSB first.

When this bit is set active high, the AD9773 serial port is in LSB first format. In LSB first mode, the instruction byte and data bytes must be written from LSB to MSB. In LSB first mode, the serial port internal byte address generator increments for each byte of the multibyte communication cycle.

When this bit is set default low, the AD9773 serial port is in MSB first format. In MSB first mode, the instruction byte and data bytes must be written from MSB to LSB. In MSB first mode, the serial port internal byte address generator decrements for each byte of the multibyte communication cycle.

When incrementing from 1Fh, the address generator changes to 00h. When decrementing from 00h, the address generator changes to 1Fh.

Figure 33. Serial Register Interface Timing MSB First

Figure 34. Serial Register Interface Timing LSB First

Figure 36. Timing Diagram for Register Read from AD9773

#### **NOTES ON SERIAL PORT OPERATION**

The AD9773 serial port configuration bits reside in Bits 6 and 7 of Register Address 00h. It is important to note that the configuration changes immediately upon writing to the last bit of the register. For multibyte transfers, writing to this register can occur during the middle of the communication cycle. Care must be taken to compensate for this new configuration for the remaining bytes of the current communication cycle.

The same considerations apply to setting the reset bit in Register Address 00h. All other registers are set to their default values, but the software reset does not affect the bits in Register Address 00h.

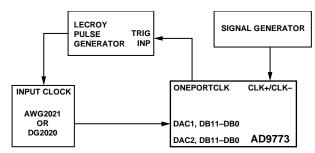

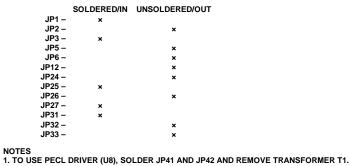

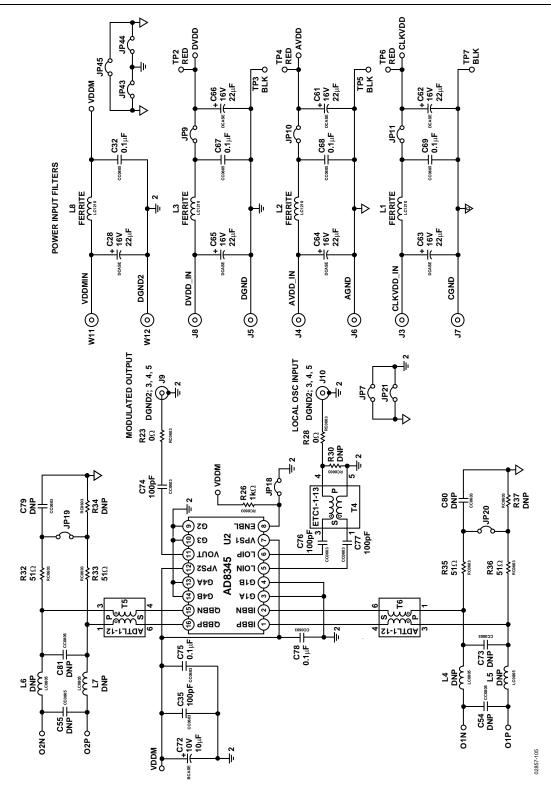

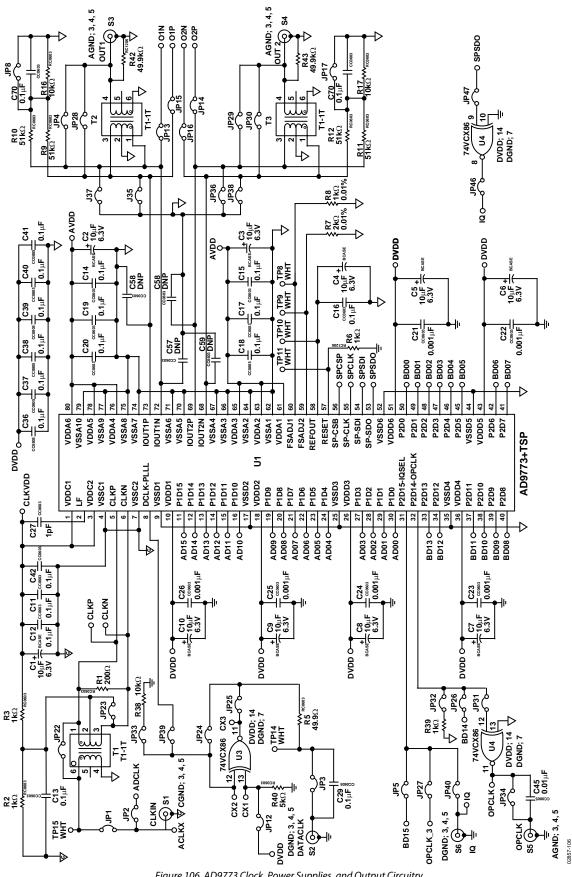

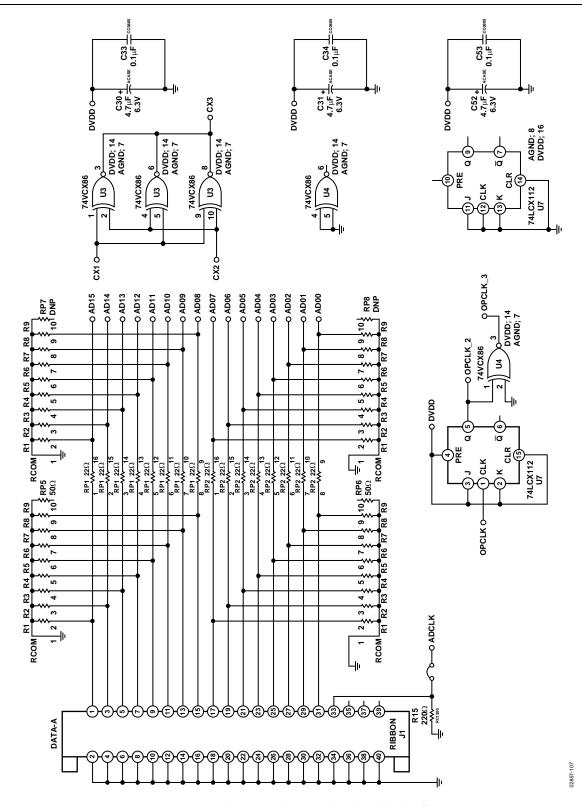

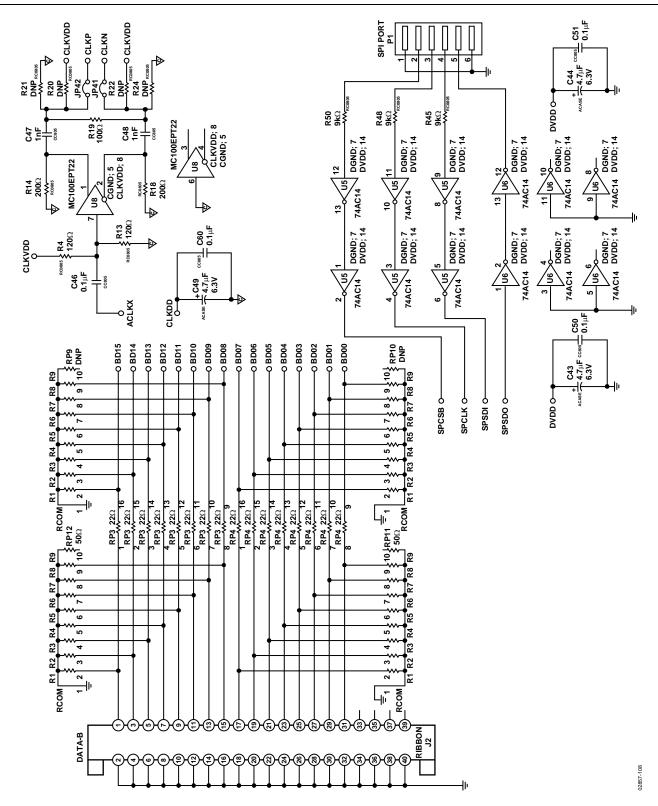

It is recommended to use only single-byte transfers when changing serial port configurations or initiating a software reset.