# Configurable, Dual 2 A/Single 4 A, Synchronous Step-Down DC-to-DC Regulator

Data Sheet ADP2114

#### **FEATURES**

Configurable 2 A/2 A or 3 A/1 A dual output load combinations or 4 A combined single output High efficiency: up to 95% Input voltage V<sub>IN</sub>: 2.75 V to 5.5 V Selectable fixed output: 0.8 V, 1.2 V, 1.5 V, 1.8 V, 2.5 V, 3.3 V or adjustable output voltage to 0.6 V minimum ±1.5% accurate reference voltage Selectable switching frequency: 300 kHz, 600 kHz, 1.2 MHz or synchronized from 200 kHz to 2 MHz Optimized gate slew rate for reduced EMI External synchronization input or internal clock output Dual-phase, 180° phase shifted PWM channels **Current mode for fast transient response** Pulse skip under light load or forced PWM operation Input undervoltage lockout (UVLO) Independent enable inputs and PGOOD outputs Overcurrent and thermal overload protection **Externally programmable soft start** 32-lead 5 mm × 5 mm LFCSP package Supported by ADIsimPower™ design tool

#### **APPLICATIONS**

Point of load regulation

Telecommunications and networking systems

Consumer electronics

Industrial and Instrumentation

Medical

#### **GENERAL DESCRIPTION**

The ADP2114 is a versatile, synchronous step-down, switching regulator that satisfies a wide range of customer point-of-load requirements. The two PWM channels can be configured to deliver independent outputs at 2 A and 2 A (or 3 A/1 A) or can be configured as a single interleaved output capable of delivering 4 A. The two PWM channels are 180° phase shifted to reduce input ripple current and to reduce input capacitance. The ADP2114 provides high efficiency and operates at switching frequencies of up to 2 MHz. At light loads, the ADP2114 can be set to operate in pulse skip mode for higher efficiency or in forced PWM mode to reduce EMI.

The ADP2114 is designed with an optimized gate slew rate to reduce EMI emissions, allowing it to power sensitive, high performance signal chain circuits. The switching frequency can be set to 300 kHz, 600 kHz, or 1.2 MHz and can be synchronized to an external clock that minimizes the system noise. The bidirectional synchronization pin is also configurable as a 90° out-of-phase output clock, providing the possibility for a stackable multiphase power solution.

#### Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

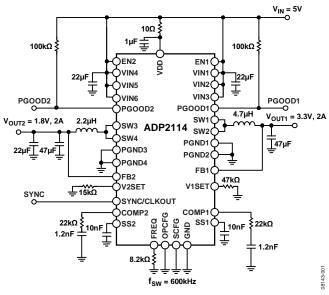

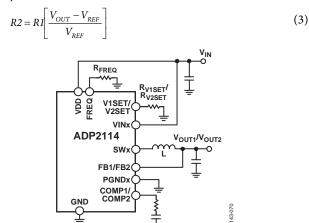

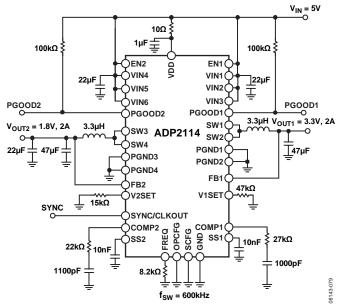

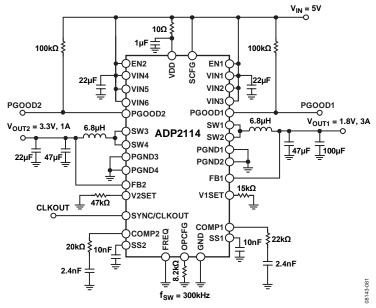

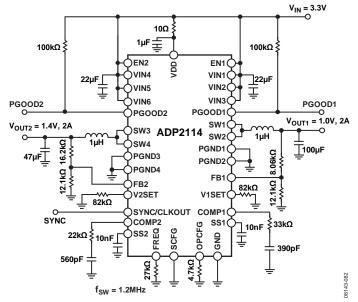

#### TYPICAL APPLICATION CIRCUIT

Figure 1.

The ADP2114 input voltage range is from 2.75 V to 5.5 V, and it converts to fixed outputs of 0.8 V, 1.2 V, 1.5 V, 1.8 V, 2.5 V, or 3.3 V that can be set independently for each channel using external resistors. Using a resistor divider, it is also possible to set the output voltage as low as 0.6 V. The ADP2114 operates over the  $-40^{\circ}$ C to  $+125^{\circ}$ C junction temperature range.

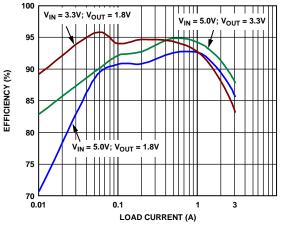

Figure 2. Typical Efficiency vs. Load Current

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 ©2009–2012 Analog Devices, Inc. All rights reserved.

### **TABLE OF CONTENTS**

| reatures                                     |

|----------------------------------------------|

| Applications1                                |

| General Description1                         |

| Typical Application Circuit1                 |

| Revision History2                            |

| Specifications3                              |

| Absolute Maximum Ratings5                    |

| ESD Caution5                                 |

| Pin Configuration and Function Descriptions6 |

| Typical Performance Characteristics          |

| Supply Current                               |

| Load Transient Response14                    |

| Bode Plots                                   |

| Simplified Block Diagram20                   |

| Theory of Operation21                        |

| ADIsimPower Design Tool21                    |

| Control Architecture                         |

| Undervoltage Lockout (UVLO)21                |

| Enable/Disable Control21                     |

| Soft Start                                   |

| Power Good                                   |

| Pulse Skip Mode                              |

| Hiccup Mode Current Limit23                  |

| REVISION HISTORY                             |

| 8/12—Rev. 0 to Rev. A                        |

| Change to Features Section 1                 |

| Thermal Overload Protection                         |

|-----------------------------------------------------|

| Maximum Duty Cycle Operation23                      |

| Synchronization                                     |

| Converter Configuration                             |

| Selecting the Output Voltage24                      |

| Setting the Oscillator Frequency                    |

| Synchronization and CLKOUT25                        |

| Operation Mode Configuration26                      |

| External Components Selection                       |

| Input Capacitor Selection                           |

| VDD RC Filter                                       |

| Inductor Selection                                  |

| Output Capacitor Selection                          |

| Control Loop Compensation28                         |

| Design Example                                      |

| Channel 1 Configuration and Components Selection 30 |

| Channel 2 Configuration and Components Selection 31 |

| System Configuration                                |

| Application Circuits                                |

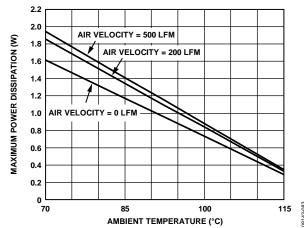

| Power Dissipation, Thermal Considerations35         |

| Circuit Board Layout Recommendations                |

| Outline Dimensions                                  |

| Change to Features Section            | 1 |

|---------------------------------------|---|

| Added ADIsimPower Design Tool Section |   |

| Updated Outline Dimensions            |   |

7/09—Revision 0: Initial Version

### **SPECIFICATIONS**

If unspecified, VDD = VINx = EN1 = EN2 = 5.0 V. The minimum and maximum specifications are valid for  $T_J$  = -40°C to +125°C, unless otherwise specified. Typical values are at  $T_J$  = 25°C. All limits at temperature extremes are guaranteed via correlation using standard statistical quality control (SQC).

Table 1.

| Parameter                       | Symbol                 | Conditions                                                                                                                                                                             | Min   | Тур   | Max   | Unit |

|---------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| POWER SUPPLY                    |                        |                                                                                                                                                                                        |       |       |       |      |

| VDD Bias Voltage                | VDD                    |                                                                                                                                                                                        | 2.75  |       | 5.5   | V    |

| Undervoltage Lockout Threshold  | UVLO                   | V <sub>DD</sub> rising                                                                                                                                                                 |       | 2.65  | 2.75  | V    |

|                                 |                        | V <sub>DD</sub> falling                                                                                                                                                                | 2.35  | 2.47  |       |      |

| Undervoltage Lockout Hysteresis |                        |                                                                                                                                                                                        |       | 0.18  |       | V    |

| Quiescent Current               | IDD <sub>Ch1</sub>     | $EN1 = VDD = 5 V$ , $EN2 = GND$ , $V_{FB1} = VDD$ , $OPCFG = GND$                                                                                                                      |       | 1.7   | 2.5   | mA   |

|                                 | IDD <sub>Ch2</sub>     | $EN2 = VDD = 5V$ , $EN1 = GND$ , $V_{FB2} = VDD$ , $OPCFG = GND$                                                                                                                       |       | 1.7   | 2.5   | mA   |

|                                 | IDD <sub>Ch1+Ch2</sub> | $EN1 = EN2 = VDD = 5 \text{ V}, V_{FB2} = V_{FB1} = VDD,$ $OPCFG = GND$                                                                                                                |       | 3.0   | 4.0   | mA   |

| Shutdown Current                | IDD <sub>SD</sub>      | EN1 = EN2 = GND, VDD = VINx = 2.75 V to 5.5 V,<br>$T_J = -40$ °C to +115°C                                                                                                             |       | 1.0   | 10    | μΑ   |

| ERROR INTEGRATOR (OTA)          |                        |                                                                                                                                                                                        |       |       |       |      |

| FB1, FB2 Input Bias Current     | I <sub>FB</sub>        | Adjustable output, $V_{FBx} = 0.6 \text{ V}$ , V1SET, V2SET = VDD or via 82 k $\Omega$ to GND                                                                                          |       | 1     | 65    | nA   |

|                                 |                        | Fixed output; $V_{FBx} = 1.2 \text{ V}$ , V1SET, V2SET via 4.7 k $\Omega$ to GND                                                                                                       |       | 11    | 15    | μΑ   |

| Transconductance                | $g_{M}$                |                                                                                                                                                                                        |       | 550   |       | μA/V |

| COMPx VOLTAGE RANGE             |                        |                                                                                                                                                                                        |       |       |       |      |

| COMPx Zero-Current Threshold    | $V_{COMP, ZCT}$        | Guaranteed by design                                                                                                                                                                   |       | 1.12  |       | V    |

| COMPx Clamp High Voltage        | V <sub>COMP, HI</sub>  | VDD = VINx = 2.75 V to 5.5 V                                                                                                                                                           |       | 2.36  | 2.45  | V    |

| COMPx Clamp Low Voltage         | $V_{COMP, LO}$         | VDD = VINx = 2.75 V to 5.5 V                                                                                                                                                           | 0.65  | 0.70  |       | V    |

| OUTPUT CHARACTERISTICS          |                        |                                                                                                                                                                                        |       |       |       |      |

| Output Voltage Accuracy         | $V_{FB}$               | Adjustable output, $T_J = 25^{\circ}$ C,<br>V1SET, V2SET = VDD or via 82 k $\Omega$ to GND                                                                                             | 0.597 | 0.600 | 0.603 | V    |

|                                 |                        | Adjustable output, $T_J = -40^{\circ}\text{C}$ to $+125^{\circ}\text{C}$ , V1SET, V2SET = VDD or via 82 k $\Omega$ to GND                                                              | 0.594 | 0.600 | 0.606 | V    |

|                                 | $V_{FB  ERROR}$        | Fixed output, T <sub>J</sub> = 25°C, V1SET, V2SET = GND or via 4.7 k $\Omega$ , 8.2 k $\Omega$ , 15 k $\Omega$ , 27 k $\Omega$ , 47 k $\Omega$ to GND                                  | -1.0  |       | +1.0  | %    |

|                                 |                        | Fixed output, $T_J = -40^{\circ}\text{C}$ to $+125^{\circ}\text{C}$ , V1SET, V2SET = GND or via 4.7 k $\Omega$ , 8.2 k $\Omega$ , 15 k $\Omega$ , 27 k $\Omega$ , 47 k $\Omega$ to GND | -1.5  |       | +1.5  | %    |

| Line Regulation                 |                        | VDD = VINx = 2.75 V to 5.5 V                                                                                                                                                           |       | 0.05  |       | %/V  |

| Load Regulation                 |                        | VDD = VINx = 2.75 V to 5.5 V                                                                                                                                                           |       | 0.03  |       | %/A  |

| OSCILLATOR                      |                        | All oscillator parameters provided for VDD = 2.75 V to 5.5 V                                                                                                                           |       |       |       |      |

| Switching Frequency             | f <sub>sw</sub>        | FREQ tied to GND                                                                                                                                                                       | 255   | 300   | 345   | kHz  |

| <b>3</b> , ,                    | 5                      | FREQ via 8.2 kΩ to GND                                                                                                                                                                 | 510   | 600   | 690   | kHz  |

|                                 |                        | FREQ via 27 kΩ to GND                                                                                                                                                                  | 1020  | 1200  | 1380  | kHz  |

| SYNC Frequency Range            | f <sub>SYNC</sub>      | $f_{SYNC} = 2 \times f_{SW}$                                                                                                                                                           |       |       |       |      |

| , , , , ,                       | STINC                  | FREQ tied to GND                                                                                                                                                                       | 400   |       | 1000  | kHz  |

|                                 |                        | FREQ via 8.2 kΩ to GND                                                                                                                                                                 | 800   |       | 2000  | kHz  |

|                                 |                        | FREQ via 27 kΩ to GND                                                                                                                                                                  | 1600  |       | 4000  | kHz  |

| SYNC Input Pulse Width          |                        |                                                                                                                                                                                        | 100   |       |       | ns   |

| Parameter                                            | Symbol                | Conditions                                                                                                | Min  | Тур  | Max  | Unit   |

|------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------|------|------|------|--------|

| SYNC Pin Capacitance to GND                          | C <sub>SYNC</sub>     |                                                                                                           |      | 5    |      | pF     |

| SYNC Input Logic Low                                 | $V_{IL\_SYNC}$        |                                                                                                           |      |      | 8.0  | V      |

| SYNC Input Logic High                                | $V_{\text{IH\_SYNC}}$ |                                                                                                           | 2.0  |      |      | V      |

| Phase Shift Between Channels                         |                       |                                                                                                           |      | 180  |      | Degree |

| CLKOUT Frequency                                     | f <sub>CLKOUT</sub>   | $f_{CLKOUT} = 2 \times f_{SW}$                                                                            |      |      |      |        |

| . ,                                                  | CEROOT                | FREQ tied to GND                                                                                          | 510  | 600  | 690  | kHz    |

|                                                      |                       | FREQ via 8.2 kΩ to GND                                                                                    | 1020 | 1200 | 1380 | kHz    |

|                                                      |                       | FREQ via 27 kΩ to GND                                                                                     | 2040 | 2400 | 2760 | kHz    |

| CLKOUT Positive Pulse Time                           | t <sub>CLKOUT</sub>   |                                                                                                           | 100  |      |      | ns     |

| CLKOUT Rise or Fall Time                             | CLKOUT                | С <sub>ськоит</sub> = 20 pF                                                                               | 100  | 10   |      | ns     |

| CURRENT LIMIT                                        |                       | All current limit parameters provided for                                                                 |      | 10   |      | 113    |

| COUNTENT ENVIR                                       |                       | VDD = VINx = 2.75  V to  5.5  V                                                                           |      |      |      |        |

| Peak Output Current Limit, Channel 1                 | I <sub>LIMIT1</sub>   | OPCFG tied to GND or via 4.7 kΩ to GND                                                                    | 2.4  | 3.3  | 4.0  | Α      |

|                                                      | LIMITI                | OPCFG via 8.2 kΩ or 15 kΩ to GND                                                                          | 3.5  | 4.5  | 5.3  | Α      |

| Peak Output Current Limit, Channel 2                 | I <sub>LIMIT2</sub>   | OPCFG tied to GND or via 4.7 kΩ to GND                                                                    | 2.4  | 3.3  | 4.0  | A      |

| reak output current Emily chainer 2                  | LIMIT2                | OPCFG via 8.2 k $\Omega$ or 15 k $\Omega$ to GND                                                          | 1.2  | 1.9  | 2.6  | A      |

| Current Sense Amplifier Gain                         | G <sub>cs</sub>       | 01 C1 G VIA 0.2 K2 01 13 K2 10 GIVD                                                                       | 1.2  | 4    | 2.0  | A/V    |

| Hiccup Time                                          | G <sub>CS</sub>       | $f_{sw} = 300 \text{ kHz}$                                                                                | 10   | 13.6 | 17   |        |

| Number of Cumulative Current Limit                   |                       | 1 <sub>SW</sub> = 300 kH2                                                                                 | 10   |      | 17   | ms     |

| Cycles to Go into Hiccup                             |                       |                                                                                                           |      | 8    |      | Cycles |

| SWITCH NODE CHARACTERISTICS                          |                       |                                                                                                           |      |      |      |        |

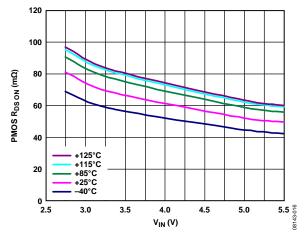

|                                                      |                       | VDD = VINx = 3.3 V                                                                                        |      | 68   |      | m0     |

| High-Side, P-Channel R <sub>DS ON</sub> <sup>1</sup> |                       |                                                                                                           |      |      |      | mΩ     |

| I C'I N.C. ID 1                                      |                       | VDD = VINx = 5.0 V                                                                                        |      | 52   |      | mΩ     |

| Low-Side, N-Channel R <sub>DS ON</sub> <sup>1</sup>  |                       | VDD = VINx = 3.3 V                                                                                        |      | 32   |      | mΩ     |

|                                                      |                       | VDD = VINx = 5.0 V                                                                                        |      | 27   |      | mΩ     |

| SWx Minimum On Time                                  | SW <sub>ON MIN</sub>  | VDD = VINx = 2.75 V to 5.5 V                                                                              |      | 107  |      | ns     |

| SWx Minimum Off Time                                 | SW <sub>OFF MIN</sub> | VDD = VINx = 5.5 V                                                                                        |      | 192  |      | ns     |

|                                                      |                       | VDD = VINx = 2.75 V                                                                                       |      | 255  |      | ns     |

| SWx Maximum Leakage Current                          |                       | VDD = VINx = 2.75 V to 5.5 V; ENx = GND,<br>$T_1 = -40^{\circ}\text{C}$ to +115°C                         |      | 0.1  | 15   | μΑ     |

| ENABLE INPUT                                         |                       |                                                                                                           |      |      |      |        |

| EN1, EN2 Logic Low Level                             | EN <sub>LOW</sub>     | VDD = VINx = 2.75 V to 5.5 V                                                                              |      |      | 0.8  | V      |

| EN1, EN2 Logic High Level                            | EN <sub>HI</sub>      | VDD = VINx = 2.75 V to 5.5 V                                                                              | 2    |      | 0.0  | V      |

| EN1, EN2 Input Leakage Current                       | I <sub>EN_LEAK</sub>  | VDD = VINx = ENx = 2.75 V  to  5.5 V,                                                                     | -    | 0.1  | 1    | μA     |

| Livi, Livi input Leakage carrent                     | 'EN_LEAK              | $T_1 = -40^{\circ}\text{C to} + 115^{\circ}\text{C}$                                                      |      | 0.1  | •    | μπ     |

| THERMAL SHUTDOWN                                     |                       |                                                                                                           |      |      |      |        |

| Thermal Shutdown Threshold                           | T <sub>TMSD</sub>     |                                                                                                           |      | 150  |      | °C     |

| Thermal Shutdown Hysteresis                          | TIVISD                |                                                                                                           |      | 25   |      | °C     |

| SOFT START                                           |                       |                                                                                                           |      |      |      |        |

| SS1, SS2 Pin Current                                 | , ,                   | $VDD = VINx = 2.75 V \text{ to } 5.5 V; V_{SS} = 0 V$                                                     | 4.8  | 6.0  | 7.8  | μΑ     |

|                                                      | $I_{SS1}, I_{SS2}$    | $VDD = VINX = 2.75 \text{ V to } 3.5 \text{ V, } V_{SS} = 0 \text{ V}$<br>VDD = VINX = 2.75  V to  5.5  V | 4.0  |      | 7.0  | V      |

| Soft Start Threshold Voltage                         | $V_{SS\_THRESH}$      |                                                                                                           | 0.5  | 0.65 |      |        |

| Soft Start Pull-Down Current                         |                       | VDD = VINx = 2.75 V to 5.5 V; EN = GND                                                                    | 0.5  |      |      | mA     |

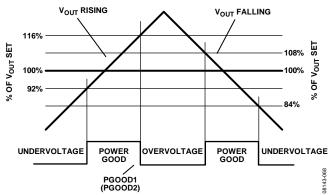

| POWER GOOD                                           |                       | All power good parameters provided for VDD = VINx = 2.75 V to 5.5 V                                       |      |      |      |        |

| Overvoltage PGOODx Rising Threshold <sup>2</sup>     |                       |                                                                                                           |      | 116  |      | %      |

| Overvoltage PGOODx Falling Threshold <sup>2</sup>    |                       |                                                                                                           | 100  | 108  | 114  | %      |

| Undervoltage PGOODx Rising Threshold <sup>2</sup>    |                       |                                                                                                           | 85   | 92   | 97   | %      |

| Undervoltage PGOODx Falling Threshold <sup>2</sup>   |                       |                                                                                                           |      | 84   |      | %      |

| PGOODx Delay                                         |                       |                                                                                                           |      | 50   |      | μs     |

| PGOODX Delay PGOODX Leakage Current                  |                       | $V_{PGOODx} = VDD$                                                                                        |      | 0.1  | 1    | 1 .    |

| =                                                    |                       |                                                                                                           |      |      |      | μA     |

| PGOODx Low Saturation Voltage                        |                       | $I_{PGOODx} = 1 \text{ mA}$                                                                               |      | 50   | 110  | mV     |

$<sup>^{\</sup>rm 1}$  Pin-to-pin measurements.  $^{\rm 2}$  The thresholds are expressed in percentage terms of the nominal output voltage.

### **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Tubic 2.                                                                                                      |                               |

|---------------------------------------------------------------------------------------------------------------|-------------------------------|

| Parameter                                                                                                     | Rating                        |

| VDD to GND                                                                                                    | −0.3 V to +6 V                |

| VIN1, VIN2, VIN3, VIN4, VIN5, VIN6 to<br>PGND1, PGND2, PGND3, PGND4                                           | −0.3 V to +6 V                |

| EN1, EN2, SCFG, FREQ, FB1, FB2, SYNC/<br>CLKOUT, PGOOD1, PGOOD2, V1SET,<br>V2SET, COMP1, COMP2, SS1, SS2 to G | -0.3 V to (VDD + 0.3 V)       |

| FB1, FB2 to GND                                                                                               | -0.3V to +3.6V                |

| SW1, SW2, SW3, SW4 to PGND1, PGN<br>PGND3, PGND4                                                              | D2, -0.3  V to (VDD + 0.3  V) |

| PGND1, PGND2, PGND3, PGND4 to GN                                                                              | ID ±0.3 V                     |

| VIN1, VIN2, VIN3, VIN4, VIN5, VIN6 to VD                                                                      | DD ±0.3 V                     |

| $\theta_{JA}$ , JEDEC 1S2P PCB, Natural Convect                                                               | tion 34°C/W                   |

| Operating Junction Temperature Ran                                                                            | nge                           |

| Storage Temperature Range                                                                                     | −65°C to +150°C               |

| Maximum Soldering Lead<br>Temperature (10 sec)                                                                | 260℃                          |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Absolute maximum ratings apply individually only, not in combination.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

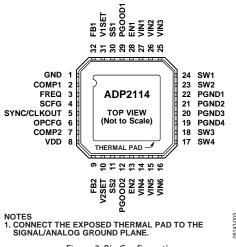

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

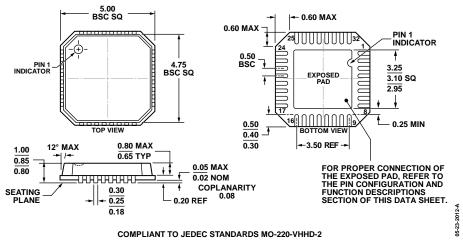

Figure 3. Pin Configuration

**Table 3. Pin Function Descriptions**

| Pin No. | Mnemonic    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GND         | Ground for the Internal Analog and Digital Circuits. Connect GND to the signal/analog ground plane before connecting to the power ground.                                                                                                                                                                                                                                                                                                                                                                            |

| 2       | COMP1       | Error Amplifier Output for Channel 1. Connect a series RC network from COMP1 to GND to compensate for Channel 1. For multiphase operation, tie COMP1 and COMP2 together.                                                                                                                                                                                                                                                                                                                                             |

| 3       | FREQ        | Frequency Select Input. Connect this pin through a resistor to GND to set the appropriate switching frequency (see Table 5).                                                                                                                                                                                                                                                                                                                                                                                         |

| 4       | SCFG        | Synchronization Configuration Input. SCFG configures the SYNC/CLKOUT pin as an input or output. Tie this pin to VDD to configure SYNC/CLKOUT as an output. Tie this pin to GND to configure SYNC/CLKOUT as an input.                                                                                                                                                                                                                                                                                                 |

| 5       | SYNC/CLKOUT | This is a configurable bidirectional pin (configured with the SCFG pin—see the Pin 4 description for details). When SYNC/CLKOUT is an output, a buffered clock of twice the switching frequency with a phase shift of 90° is available on this pin. When configured as an input, this pin accepts an external clock to which the converters are synchronized. The frequency select resistor, mentioned in the description of Pin 3, must be selected close to the expected switching frequency for stable operation. |

| 6       | OPCFG       | Operation Configuration Input. Connect this pin through a resistor to GND to set the system mode of operation according to Table 7. This pin can be used to select a peak current limit for each power channel and enable or disable the pulse skip mode.                                                                                                                                                                                                                                                            |

| 7       | COMP2       | Error Amplifier Output for Channel 2. Connect a series RC network from COMP2 to GND to compensate the Channel 2. Tie COMP1 and COMP2 together for multiphase configuration.                                                                                                                                                                                                                                                                                                                                          |

| 8       | VDD         | Power Supply Input. The power source for the ADP2114 internal circuitry. Connect VDD and VINx with a $10\Omega$ resistor as close as possible to the ADP2114. Bypass VDD to GND with a $1\mu$ F or greater capacitor.                                                                                                                                                                                                                                                                                                |

| 9       | FB2         | Feedback Voltage Input for Channel 2. For the fixed output voltage option, connect FB2 to $V_{OUT2}$ . For the adjustable output voltage option, connect this pin to a resistor divider between $V_{OUT2}$ and GND. The reference voltage for the adjustable output voltage option is 0.6 V. With multiphase configurations, connect FB2 to FB1 and then connect them to $V_{OUT}$ .                                                                                                                                 |

| 10      | V2SET       | Output Voltage Set Pin for Channel 2. Connect this pin through a resistor to GND or tie to VDD to select a fixed output voltage option (0.8 V, 1.2 V, 1.5 V, 1.8 V, 2.5 V, or 3.3 V) or an adjust output voltage for V <sub>OUT2</sub> . See Table 4 for output voltage selection.                                                                                                                                                                                                                                   |

| 11      | SS2         | Soft Start Input for Channel 2. Place a capacitor from SS2 to GND to set the soft start period. A 10 nF capacitor sets a 1 ms soft start period. For multiphase configuration, connect SS2 to SS1.                                                                                                                                                                                                                                                                                                                   |

| 12      | PGOOD2      | Open-Drain Power Good Output for Channel 2. Place a 100 k $\Omega$ pull-up resistor to VDD or any other voltage $\leq$ 5.5 V; PGOOD2 pulls low when Channel 2 is out of regulation.                                                                                                                                                                                                                                                                                                                                  |

| 13      | EN2         | Enable Input for Channel 2. Drive EN2 high to turn on the Channel 2 converter and drive EN2 low to turn off Channel 2. Tie EN2 to VDD for startup with VDD. With multiphase configuration, tie EN2 to EN1.                                                                                                                                                                                                                                                                                                           |

| Pin No. | Mnemonic  | Description                                                                                                                                                                                                                                                                                               |  |  |  |

|---------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 14      | VIN4      | Power Supply Input. The source of the high-side internal power MOSFET of Channel 2.                                                                                                                                                                                                                       |  |  |  |

| 15      | VIN5      | Power Supply Input. The source of the high-side internal power MOSFET of Channel 2.                                                                                                                                                                                                                       |  |  |  |

| 16      | VIN6      | Power Supply Input. The source of the high-side internal power MOSFET of Channel 2.                                                                                                                                                                                                                       |  |  |  |

| 17      | SW4       | Switch Node Output. The drain of the P-channel power switch and N-channel synchronous rectifier of Channel 2. Tie SW3 to SW4 and then connect the output LC filter between SW and the output voltage.                                                                                                     |  |  |  |

| 18      | SW3       | Switch Node Output. The drain of the P-channel power switch and N-channel synchronous rectifier of Channel 2. Tie SW3 to SW4 and then connect the output LC filter between SW and the output voltage.                                                                                                     |  |  |  |

| 19      | PGND4     | Power Ground. Source of the low-side internal power MOSFET of Channel 2.                                                                                                                                                                                                                                  |  |  |  |

| 20      | PGND3     | Power Ground. Source of the low-side internal power MOSFET of Channel 2.                                                                                                                                                                                                                                  |  |  |  |

| 21      | PGND2     | Power Ground. Source of the low-side internal power MOSFET of Channel 1.                                                                                                                                                                                                                                  |  |  |  |

| 22      | PGND1     | Power Ground. Source of the low-side internal power MOSFET of Channel 1.                                                                                                                                                                                                                                  |  |  |  |

| 23      | SW2       | Switch Node Output. The drain of the P-channel power switch and N-channel synchronous rectifier of Channel 1. Tie SW1 to SW2 and connect the output LC filter between SW and the output voltage.                                                                                                          |  |  |  |

| 24      | SW1       | Switch Node Output. The drain of the P-channel power switch and N-channel synchronous rectifier of Channel 1. Tie SW1 to SW2 and connect the output LC filter between SW and the output voltage.                                                                                                          |  |  |  |

| 25      | VIN3      | Power Supply Input. The source of the high-side internal power MOSFET of Channel 1.                                                                                                                                                                                                                       |  |  |  |

| 26      | VIN2      | Power Supply Input. The source of the high-side internal power MOSFET of Channel 1.                                                                                                                                                                                                                       |  |  |  |

| 27      | VIN1      | Power Supply Input. The source of the high-side internal power MOSFET of Channel 1.                                                                                                                                                                                                                       |  |  |  |

| 28      | EN1       | Enable Input for Channel 1. Drive EN1 high to turn on the Channel 1 converter and drive EN1 low to turn off Channel 1. Tie EN1 to VDD for startup with VDD. With multiphase configurations, connect EN1 to EN2.                                                                                           |  |  |  |

| 29      | PGOOD1    | Open-Drain Power Good Output for Channel 1. Place a 100 k $\Omega$ pull-up resistor to VDD or any other voltage $\leq$ 5.5 V; PGOOD1 pulls low when Channel 1 is out of regulation.                                                                                                                       |  |  |  |

| 30      | SS1       | Soft Start Input for Channel 1. Place a capacitor from SS1 to GND to set the soft start period. A 10 nF capacitor sets a 1 ms soft start period. For multiphase configuration, connect SS1 to SS2.                                                                                                        |  |  |  |

| 31      | V1SET     | Output Voltage Set Pin for Channel 1. Connect this pin through a resistor to GND or tie to VDD to select a fixed output voltage option (0.8 V, 1.2 V, 1.5 V, 1.8 V, 2.5 V, or 3.3 V) or an adjustable output voltage for V <sub>OUT1</sub> . See Table 4 for output voltage selection.                    |  |  |  |

| 32      | FB1       | Feedback Voltage Input for Channel 1. For the fixed output voltage option, connect FB1 to $V_{OUT1}$ . For the adjusted output voltage option, connect this pin to a resistor divider between $V_{OUT1}$ and GND. With multiphase configurations, connect FB1 to FB2 and then connect them to $V_{OUT}$ . |  |  |  |

|         | EPAD (EP) | Exposed Thermal Pad. Connect to the signal/analog ground plane.                                                                                                                                                                                                                                           |  |  |  |

### TYPICAL PERFORMANCE CHARACTERISTICS

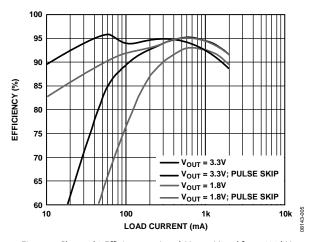

Figure 4. Channel 1 Efficiency vs. Load,  $V_{IN}$  = 5 V and  $f_{sw}$  = 300 kHz;  $V_{OUT}$  = 3.3 V, Inductor Cooper Bussmann DR1050-8R2-R, 8.2  $\mu$ H, 15  $m\Omega$ ;  $V_{OUT}$  = 1.8 V, Inductor TOKO FDV0620-4R7M, 4.7  $\mu$ H, 53  $m\Omega$

Figure 5. Channel 2 Efficiency vs. Load,  $V_{IN}$  = 5 V and  $f_{SW}$  = 600 kHz;  $V_{OUT}$  = 3.3 V, Inductor TOKO FDV0620-4R7M, 4.7 μH, 53 mΩ;  $V_{OUT}$  = 1.8 V, Inductor TOKO FDV0620-2R2M, 2.2 μH, 30 mΩ

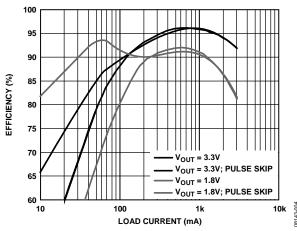

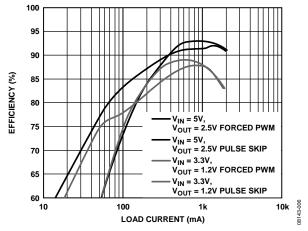

Figure 6. Efficiency vs. Load at  $f_{SW}$  = 1.2 MHz; Inductor TOKO FDV0620-1R0M, 1.0  $\mu$ H, 14  $m\Omega$

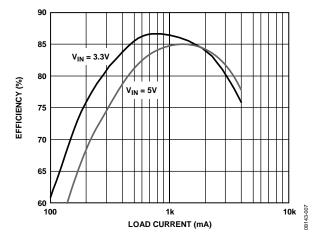

Figure 7. Efficiency Combined Dual-Phase Output,  $V_{OUT}$  = 0.8 V and  $f_{SW}$  = 1.2 MHz; Inductor TOKO FDV0620-1R0M, 1.0  $\mu$ H, 14  $m\Omega$

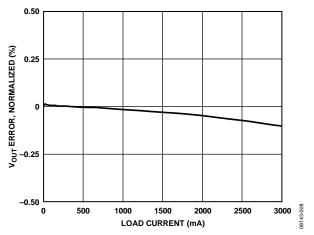

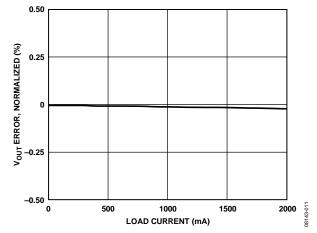

Figure 8. Load Regulation, Channel 1:  $V_{IN} = 5 \text{ V}$ ,  $f_{SW} = 600 \text{ kHz}$ , and  $T_A = 25 ^{\circ}\text{C}$

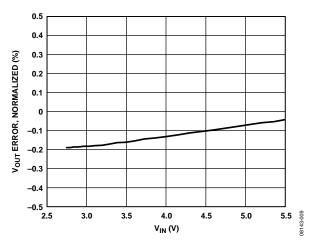

Figure 9. Line Regulation, Channel 1: Load Current = 3 A and  $f_{SW}$  = 600 kHz

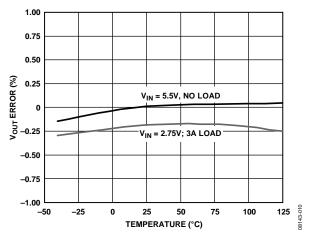

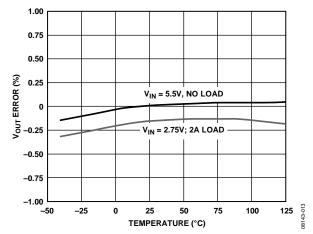

Figure 10. Output Voltage vs. Temperature, Channel 1:  $V_{OUT} = 0.6 V$  and  $f_{SW} = 600 kHz$

Figure 11. Load Regulation, Channel 2:  $V_{IN} = 5 \text{ V}$ ,  $f_{SW} = 300 \text{ kHz}$ , and  $T_A = 25 ^{\circ}\text{C}$

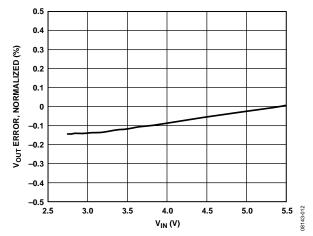

Figure 12. Line Regulation, Channel 2: Load Current = 1 A and  $f_{SW}$  = 600 kHz

Figure 13. Output Voltage vs. Temperature, Channel 2:  $V_{OUT} = 1.5 V$  and  $f_{SW} = 600 \text{ kHz}$

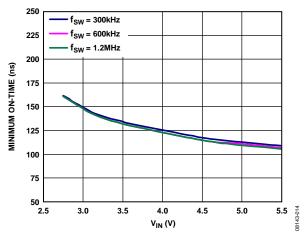

Figure 14. Minimum On-Time, Open Loop, Includes Dead Time

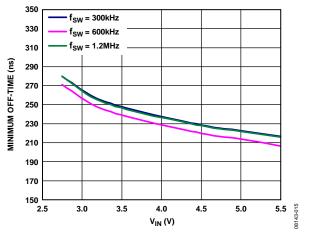

Figure 15. Minimum Off-Time, Open Loop, Includes Dead Time

Figure 16. High-Side PMOS Resistance vs. Input Voltage, Includes Bond Wires

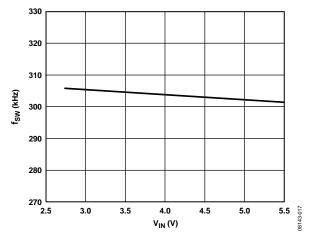

Figure 17. Switching Frequency vs. Input Voltage,  $f_{SW} = 300 \text{ kHz}$

Figure 18. Switching Frequency vs. Input Voltage,  $f_{SW} = 600 \text{ kHz}$

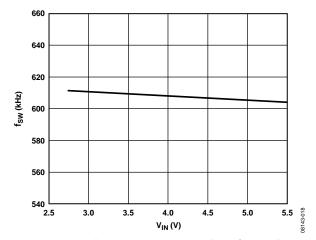

Figure 19. Low-Side NMOS Resistance vs. Input Voltage, Includes Bond Wires

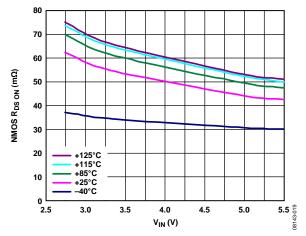

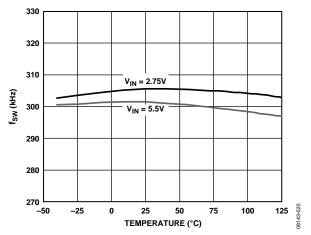

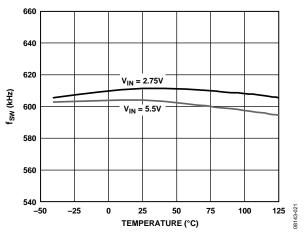

Figure 20. Switching Frequency vs. Temperature,  $f_{SW} = 300 \text{ kHz}$

Figure 21. Switching Frequency vs. Temperature,  $f_{SW} = 600 \text{ kHz}$

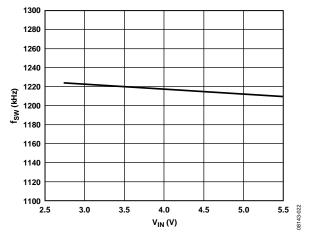

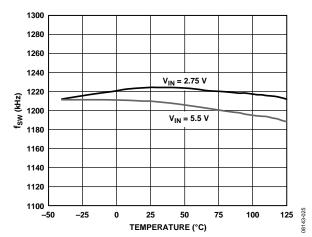

Figure 22. Switching Frequency vs. Input Voltage,  $f_{SW} = 1.2 \text{ MHz}$

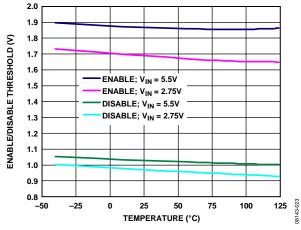

Figure 23. Enable/Disable Threshold vs. Temperature

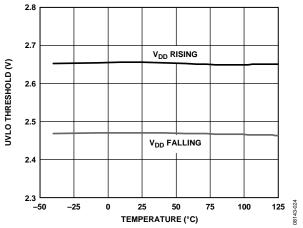

Figure 24. UVLO Threshold vs. Temperature

Figure 25. Switching Frequency vs. Temperature,  $f_{SW} = 1.2 \text{ MHz}$

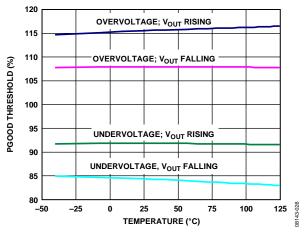

Figure 26. PGOOD Threshold vs. Temperature

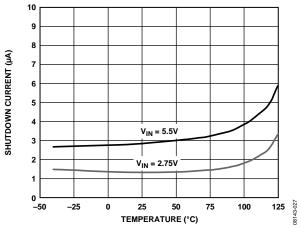

Figure 27. Shutdown Current vs. Temperature

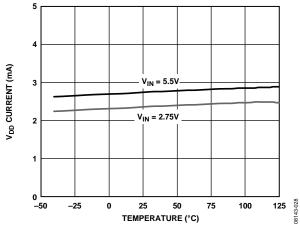

Figure 28. VDD Input Current vs. Temperature (Not Switching)

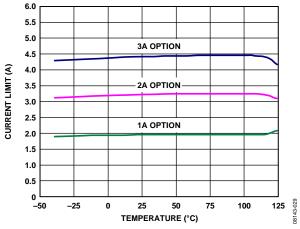

Figure 29. Peak Current Limit vs. Temperature,  $V_{IN} = 5 V$

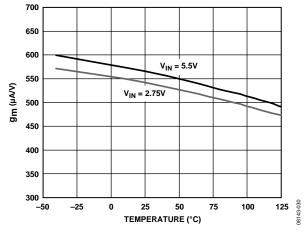

Figure 30.  $g_M$  vs. Temperature

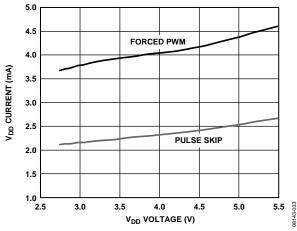

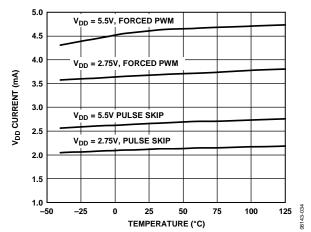

#### **SUPPLY CURRENT**

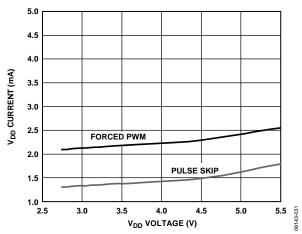

Figure 31.  $V_{DD}$  Supply Current, No Load, Channel 1:  $V_{OUT} = 1.5$  V, Channel 2 Off,  $f_{SW} = 1.2$  MHz

Figure 32.  $V_{\rm DD}$  Supply Current, No Load, Channel 2:  $V_{\rm OUT}$  = 0.8 V, Channel 1 Off,  $f_{\rm SW}$  = 1.2 MHz

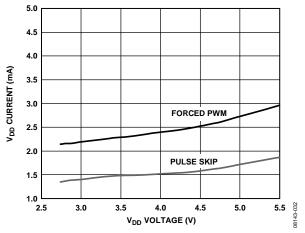

Figure 33.  $V_{DD}$  Supply Current, No Load, Channel 1:  $V_{OUT}$  = 1.5 V, Channel 2:  $V_{OUT}$  = 0.8 V,  $f_{SW}$  = 1.2 MHz

Figure 34.  $V_{\rm DD}$  Supply Current vs. Temperature, Channel 1:  $V_{\rm OUT}$  = 1.5 V, Channel 2:  $V_{\rm OUT}$  = 0.8 V,  $f_{\rm SW}$  = 1.2 MHz

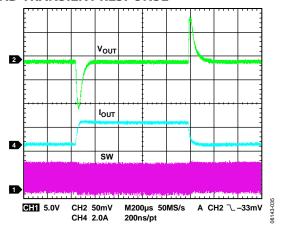

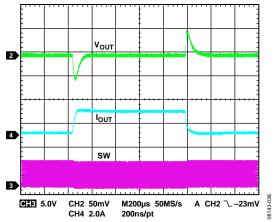

#### LOAD TRANSIENT RESPONSE

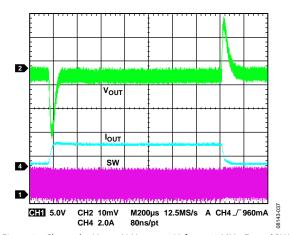

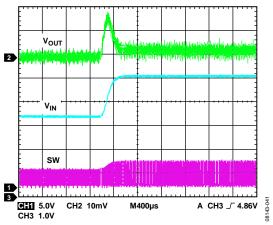

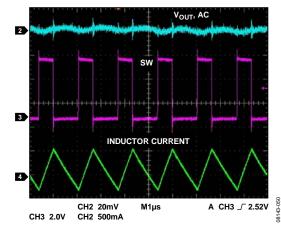

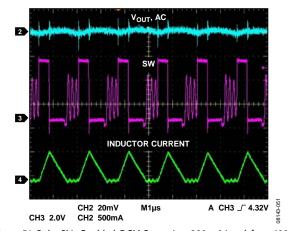

Figure 35. Channel 1:  $V_{\rm IN}$  = 5 V,  $V_{\rm OUT}$  = 3.3V,  $f_{\rm SW}$  = 600 kHz; Forced PWM (See Table 12 for the Circuit Details)

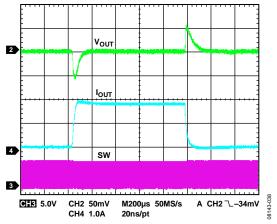

Figure 36. Channel 2:  $V_{IN} = 5 V$ ,  $V_{OUT} = 1.8 V$ ,  $f_{SW} = 600 \text{ kHz}$ ; Forced PWM (See Table 12 for the Circuit Details)

Figure 37. Channel 1:  $V_{\rm IN}=5$  V,  $V_{\rm OUT}=1.2$  V,  $f_{\rm SW}=1.2$  MHz; Forced PWM (See Table 12 for the Circuit Details)

Figure 38. Channel 2:  $V_{IN} = 5 V$ ,  $V_{OUT} = 1.8 V$ ,  $f_{SW} = 600 kHz$ ; Pulse Skip (See Table 12 for the Circuit Details)

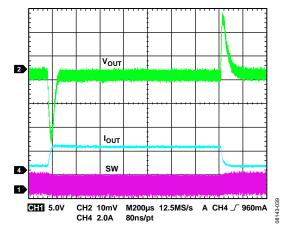

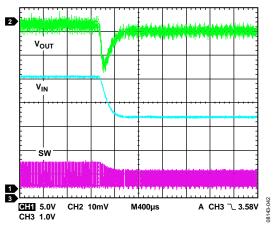

Figure 39. Channel 1:  $V_{\rm IN}$  = 3.3 V,  $V_{\rm OUT}$  = 1.2 V,  $f_{\rm SW}$  = 1.2 MHz; Forced PWM (See Table 12 for the Circuit Details)

Figure 40. Channel 1:  $V_{\rm IN}$  = 3.3 V,  $V_{\rm OUT}$  = 1.2 V,  $f_{\rm SW}$  = 1.2 MHz; Pulse Skip (See Table 12 for the Circuit Details)

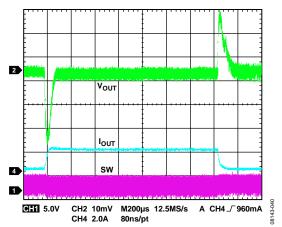

Figure 41. 3.3 V to 5 V Line Transient,  $V_{OUT}$  = 1.5 V, Load = 1 A  $f_{SW}$  = 1.2 MHz, Pulse Skip Enabled

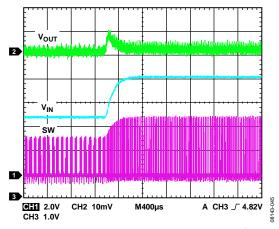

Figure 42. 5 V to 3.3 V Line Transient,  $V_{\rm OUT}$  = 1.5 V, Load = 1 A  $f_{\rm SW}$  = 1.2 MHz, Pulse Skip Enabled

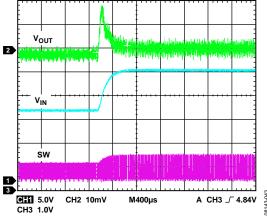

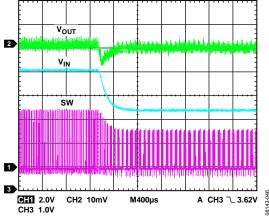

Figure 43. 3.3 V to 5 V Line Transient,  $V_{\rm OUT}$  = 1.5 V, Load = 1 A  $f_{\rm SW}$  = 1.2 MHz, Forced PWM

Figure 44. 5 V to 3.3 V Line Transient,  $V_{OUT} = 1.5$  V, Load = 1 A  $f_{SW} = 1.2$  MHz, Forced PWM

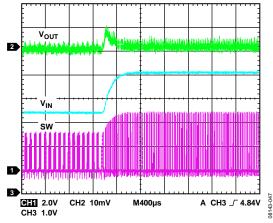

Figure 45. 3.3 V to 5 V Line Transient,  $V_{OUT}$  = 0.6 V, Load = 1 A  $f_{SW}$  = 600 kHz, Pulse Skip Enabled

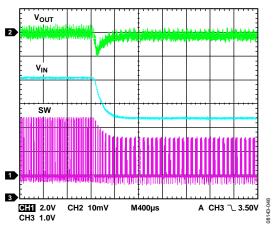

Figure 46. 5 V to 3.3 V Line Transient,  $V_{\rm OUT}$  = 0.6 V, Load = 1 A  $f_{\rm SW}$  = 600 kHz, Pulse Skip Enabled

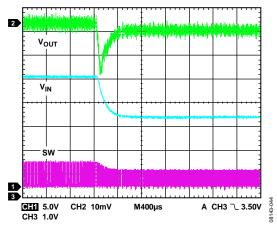

Figure 47. 3.3 V to 5 V Line Transient,  $V_{\rm OUT}$  = 0.6 V, Load = 1 A  $f_{\rm SW}$  = 600 kHz, Forced PWM

Figure 48. 5 V to 3.3 V Line Transient,  $V_{\rm OUT}$  = 0.6 V, Load = 1 A  $f_{\rm SW}$  = 600 kHz, Forced PWM

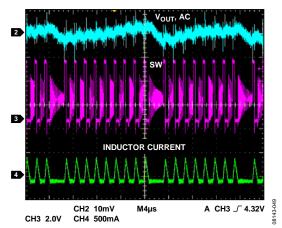

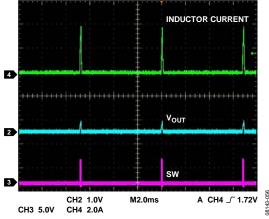

Figure 49. Pulse Skip Mode, 110 mA Load

Figure 50. Forced PWM Mode, CCM Operation, 200 mA Load,  $f_{SW} = 600 \, \mathrm{kHz}$

Figure 51. Pulse Skip Enabled, DCM Operation, 200 mA Load,  $f_{\rm SW}$  = 600 kHz

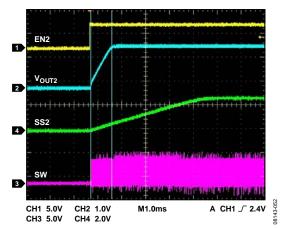

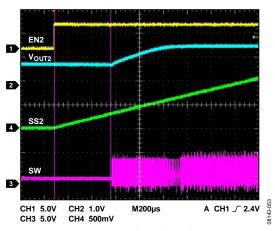

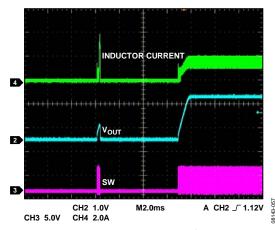

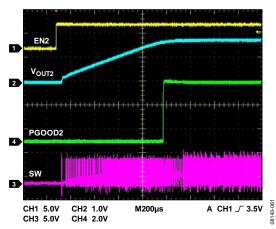

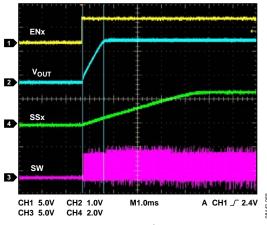

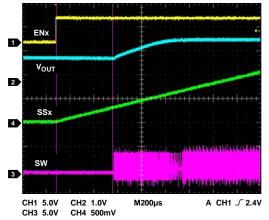

Figure 52. Soft Start, Channel 2  $V_{OUT}$  = 1.8 V,  $C_{SS}$ 2 = 10 nF

Figure 53. Start with Precharged Output

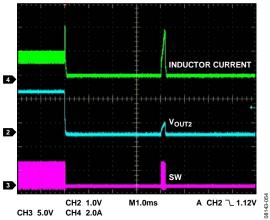

Figure 54. Current Limit Entry, Channel 2  $V_{OUT}$  = 1.8 V, 2 A Configuration,  $f_{SW}$  = 600 kHz

Figure 55. Current Limit Entry (Zoomed In), Channel 2  $V_{OUT}$  = 1.8 V, 2 A Configuration,  $f_{SW}$  = 600 kHz

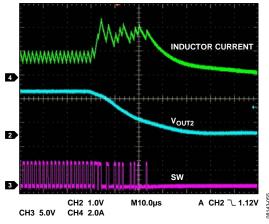

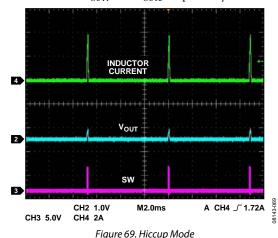

Figure 56. Hiccup Mode,  $f_{SW} = 600 \text{ kHz}$ , 6.8 ms Hiccup Cycle

Figure 57. Exit Hiccup Mode, Channel 2  $V_{OUT}$  = 1.8 V,  $f_{SW}$  = 600 kHz

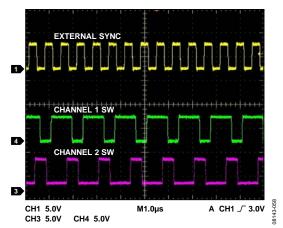

Figure 58. External Synchronization,  $f_{SYNC} = 1.5 \text{ MHz}$ ,  $f_{SW} = 750 \text{ kHz}$

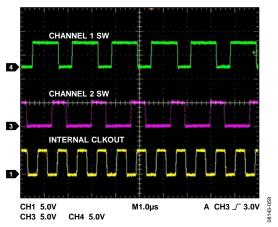

Figure 59. Internal Clock Out,  $f_{SW} = 600 \text{ kHz}$ ,  $f_{CLKOUT} = 1.2 \text{ MHz}$

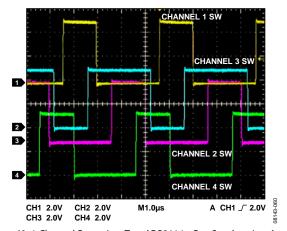

Figure 60. 4-Channel Operation, Two ADP2114s, One Synchronizes Another, 90° Phase-Shifted Switch Nodes

Figure 61. Power Good Signal

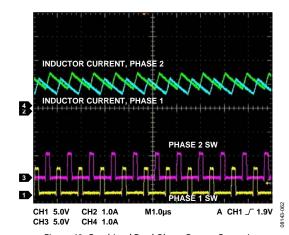

Figure 62. Combined Dual-Phase Output Operation,  $V_{OUT} = 1.2 \text{ V}, f_{SW} = 1.1 \text{ MHz}, 4 \text{ A Load}$

#### **BODE PLOTS**

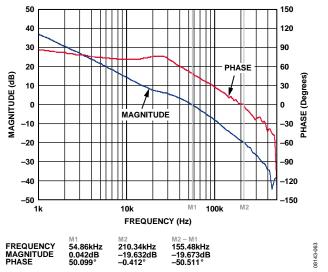

$Figure~63.~V_{IN} = 5~V,~V_{OUT} = 3.3~V,\\ Load = 2~A,~f_{SW} = 600~kHz,\\ Crossover~Frequency~(f_{CO}) = 55~kHz;\\ Phase~Margin~50°~(See~Table~12~for~the~Circuit~Details)$

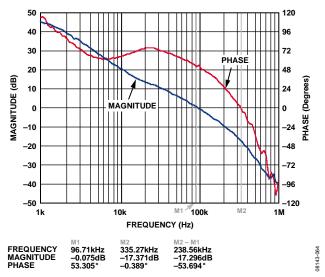

$Figure~64.~V_{IN}=5~V,~V_{OUT}=1.2~V,~Load=2~A,~f_{SW}=1.2~MHz,~Crossover~Frequency~(f_{CO})=97~kHz;~Phase~Margin~53°~(See~Table~12~for~the~Circuit~Details)$

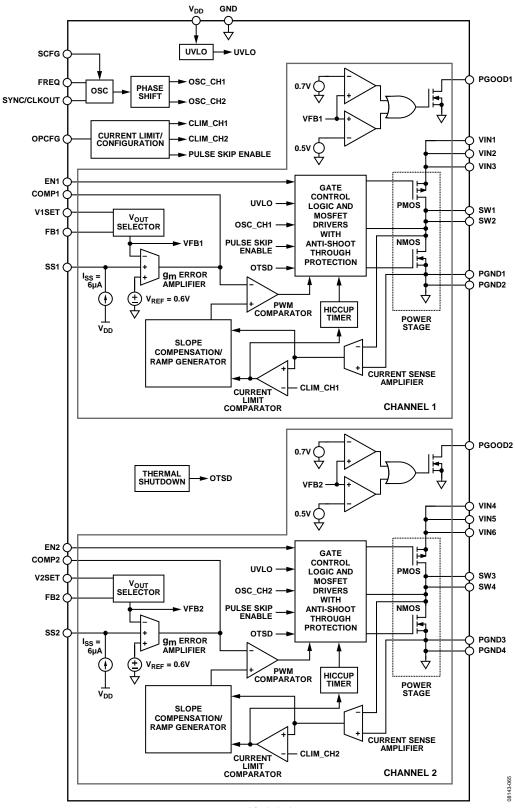

### SIMPLIFIED BLOCK DIAGRAM

Figure 65. Simplified Block Diagram

### THEORY OF OPERATION

#### **ADIsimPower DESIGN TOOL**

The ADP2114 is supported by ADIsimPower design tool set. ADIsimPower is a collection of tools that produce complete power designs optimized for a specific design goal. The tools enable the user to generate a full schematic, bill of materials, and calculate performance in minutes. ADIsimPower can optimize designs for cost, area, efficiency, and parts count while taking into consideration the operating conditions and limitations of the IC and all real external components. For more information about ADIsimPower design tools, refer to www.analog.com/ADIsimPower. The tool set is available from this website, and users can also request an unpopulated board through the tool.

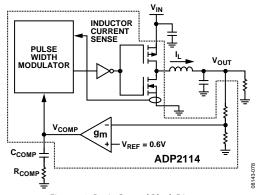

The ADP2114 is a high efficiency, dual, fixed switching frequency, synchronous step-down, dc-to-dc converter with flex mode architecture, which is the Analog Devices, Inc., proprietary version of its peak current mode control architecture. The device operates over an input voltage range of 2.75 V to 5.5 V. Each output channel provides an adjustable output down to 0.6 V and delivers up to 2 A of load current. When both the output channels are tied together, they operate 180° out of phase to deliver up to 4 A of load current. The integrated high-side, P-channel power MOSFET and the low-side, N-channel power MOSFET yield high efficiency at medium to heavy loads. Pulse skip mode is available for improved efficiency at light loads. With its high switching frequency (up to 2 MHz) and its integrated power switches, the ADP2114 has been optimized to deliver high performance in a small size for power management solutions.

The ADP2114 also includes undervoltage lockout (UVLO) with hysteresis, soft start, and power good, as well as protection features such as output short-circuit protection and thermal shutdown. The output voltages, current limits, switching frequency, pulse skip operation, and soft start time are externally programmable with tiny resistors and capacitors.

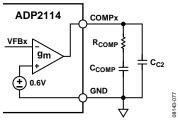

#### **CONTROL ARCHITECTURE**

The ADP2114 consists of two step-down, dc-to-dc converters that deliver regulated output voltages,  $V_{\rm OUT1}$  and  $V_{\rm OUT2}$  (see Figure 1), by modulating the duty cycle at which the internal high-side, P-channel power MOSFET and the low-side, N-channel power MOSFET are switched on and off. In steady-state operation, the output voltage,  $V_{\rm OUT}$ , is sensed on the feedback pin, FB1 (FB2), and attenuated in proportion to the selected output voltage on the V1SET (V2SET) pin.

An error amplifier integrates the error between the feedback voltage and the reference voltage ( $V_{REF} = 0.6 \text{ V}$ ) to generate an error voltage at the COMP1 (COMP2) pin. The valley inductor current is sensed by a current-sense amplifier when the low-side, N-channel MOSFET is on.

An internal oscillator turns off the low-side, N-channel MOSFET and turns on the high-side, P-channel MOSFET at a fixed switching frequency. When the high-side P-channel MOSFET is enabled, the valley inductor current information is added to an emulated ramp signal and compared to the error voltage by the PWM comparator. The output of the PWM comparator modulates the duty cycle by adjusting the trailing edge of the PWM pulse that switches the power devices. Slope compensation is programmed internally into the emulated ramp signal and automatically selected, depending on the  $V_{\rm IN},\,V_{\rm OUT},\,$  and switching frequency. This prevents subharmonic oscillations on the inductor current for greater than 50% duty-cycle operation.

Control logic with the antishoot-through circuit monitor and adjust the low-side and high-side driver outputs to ensure breakbefore-make switching. This monitoring and control prevents crossconduction between the internal high-side, P-channel power MOSFET and the low-side, N-channel power MOSFET.

#### **UNDERVOLTAGE LOCKOUT (UVLO)**

The UVLO threshold is 2.65 V when VDD is increasing and 2.47 V when VDD is decreasing. The 180 mV hysteresis prevents the converter from turning off and on repeatedly during a slow voltage transition on VDD close to the 2.75 V minimum operational level due to changing load conditions.

#### **ENABLE/DISABLE CONTROL**

The EN1 and EN2 pins are used to independently enable or disable Channel 1 and Channel 2, respectively. Drive ENx high to turn on the corresponding channel of ADP2114. Drive ENx low to turn off the corresponding channel of ADP2114, reducing input current below 1  $\mu A$ . To force a channel to start automatically when input power is applied, connect the corresponding ENx to VDD. When shut down, the ADP2114 channels discharge the soft start capacitor, causing a new soft start cycle every time the converters are re-enabled.

#### **SOFT START**

The ADP2114 soft start feature allows the output voltage to ramp up in a controlled manner, eliminating output voltage overshoot during startup. Soft start begins after the undervoltage lockout threshold is exceeded and the enable pin, EN1 (EN2), is pulled high above 2.0 V. External capacitors to ground are required on both the SS1 and SS2 pins. Each regulating channel has its own soft start circuit. When the converter powers up and is enabled, the internal 6  $\mu A$  current source charges the external soft start capacitor, establishing a voltage ramp slope at the SS1 (SS2) pin, as shown in Figure 66. The soft start time period ends when the soft start ramp voltage exceeds the internal reference of 0.6 V.

Figure 66. Soft Start

The capacitance value of the soft start capacitor defines the soft start time,  $t_{ss}$ , based on

$$\frac{V_{REF}}{t_{SS}} = \frac{I_{SS}}{C_{SS}} \tag{1}$$

where:

$V_{REF}$  is the internal reference voltage, 0.6 V.  $I_{SS}$  is the soft start current, 6  $\mu$ A.  $C_{SS}$  is the soft start capacitor value.

If the output voltage  $V_{OUT1}$  ( $V_{OUT2}$ ) is precharged prior to enabling Channel 1 (Channel 2), the control logic prevents inductor current reversal by holding the power MOSFETs off until the soft start voltage ramp at SS1 (SS2) reaches the precharged output voltage on  $V_{FB1}$  ( $V_{FB2}$ ), see Figure 67.

Figure 67. Start with a Precharged Load

#### **POWER GOOD**

The ADP2114 features open-drain, power-good outputs (PGOOD1 and PGOOD2) that indicate when the converter output voltage is within regulation. The power good signal transitions low immediately when the corresponding channel is disabled.

The power good circuitry monitors the output voltage on the FB1 (FB2) pin and compares it to the rising and falling thresholds shown in Table 1. If the output voltage,  $V_{\text{OUT}}1$  ( $V_{\text{OUT}}2$ ), exceeds the typical rising limit of 116% of the target output voltage,  $V_{\text{OUT}}1_{\text{SET}}$  ( $V_{\text{OUT}}2_{\text{SET}}$ ), the PGOOD1 (PGOOD2) pin pulls low. The PGOOD1 (PGOOD2) pin continues to pull low until the output voltage recovers down to 108% (typical) of the target value.

If the output voltage drops below 84% of the target output voltage, the corresponding PGOOD1 (PGOOD2) pin pulls low. The PGOOD1 (PGOOD2) pin continues to pull low until the output voltage rises to within 92% of the target output voltage. The PGOOD1 (PGOOD2) pin then releases and signals the return of the output voltage within the power good window.

The power good thresholds are shown in Figure 68. The PGOOD1 and PGOOD2 outputs also sink current if an overtemperature condition is detected. Use these outputs as logical power good signals by connecting the pull-up resistors from PGOOD1 (PGOOD2) to VDD. If the power good function is not used, the pins can be left floating.

Figure 68. PGOOD1 and PGOOD2 Thresholds

#### **PULSE SKIP MODE**

The ADP2114 has built-in, pulse skip circuitry that turns on during light loads, switching only as necessary to maintain the output voltage within regulation. This allows the converter to maintain high efficiency during light load operation by reducing the switching losses. The pulse skip mode can be selected by configuring the OPCFG pin according to Table 7. In pulse skip mode, when the output voltage dips below regulation, the ADP2114 enters PWM mode for a few oscillator cycles to increase the output voltage back to regulation. During the wait time between bursts, both power switches are off, and the output capacitor supplies all load current. Because the output voltage dips and recovers occasionally, the output voltage ripple in this mode is larger than the ripple in the PWM mode of operation.

If the converter is configured to operate in forced PWM mode (by selecting that configuration on the OPCFG pin), the device operates with a fixed switching frequency, even at light loads.

#### HICCUP MODE CURRENT LIMIT

The ADP2114 features a hiccup mode current limit implementation. When the peak inductor current exceeds the preset current limit for more than eight consecutive clock cycles, the hiccup mode current limit condition occurs. The channel then goes to sleep for 6.8 ms (at a 600 kHz switching frequency), which is enough time for the output to discharge and the average power dissipation to reduce. It then wakes up with a soft start period (see Figure 69). If the current limit condition is triggered again, the channel goes to sleep and wakes up after 6.8 ms. The current limits for the two channels are programmed by configuring the OPCFG pin (see Table 7). For the 2 A/2 A option, the output current limit is set to 3.3 A per output. For the 3 A/1 A option, the current limits are set to 4.5 A and 1.9 A for  $V_{\rm OUT1}$  and  $V_{\rm OUT2}$ , respectively.

#### THERMAL OVERLOAD PROTECTION

The ADP2114 has an internal temperature sensor that monitors the junction temperature. High current going into the switches or a hot printed circuit board (PCB) can cause the junction temperature of the ADP2114 to rise rapidly. When the junction temperature reaches approximately 150°C, the ADP2114 goes into thermal shutdown and the converter is turned off. When the junction temperature drops below 125°C, the ADP2114 resumes normal operation after the soft start sequence.

#### **MAXIMUM DUTY CYCLE OPERATION**

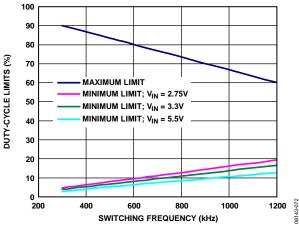

As the input voltage drops and approaches the output voltage, the ADP2114 smoothly transitions to maximum duty cycle operation, maintaining the low-side, N-channel MOSFET switch on for the minimum off time. In maximum duty cycle operation, the output voltage dips below regulation because the output voltage is the product of the input voltage and the maximum duty cycle limitation. The maximum duty cycle limit is a function of the switching frequency and the input voltage, as shown in Figure 72.

#### **SYNCHRONIZATION**

The ADP2114 can be synchronized to an external clock such that the two channels operate at a switching frequency that is half the input synchronization clock. The SYNC/CLKOUT pin can be configured as an input SYNC pin or an output CLKOUT pin through the SCFG pin, as shown in Table 6. Through the input SYNC pin, the ADP2114 can be synchronized to an external clock such that the two channels switch at half the external clock, 180° out of phase. Through the output CLKOUT pin, the ADP2114 provides an output clock that is twice the switching frequency of the channels and 90° out of phase. Therefore, a single ADP2114 configured for the CLKOUT option acts as the master converter and provides an external clock for all other dc-to-dc converters (including other ADP2114s). These other converters are configured as slaves that accept an external clock and synchronize to it. This clock distribution approach synchronizes all dc-to-dc converters in the system and prevents beat harmonics that can lead to EMI issues.

The ADP2114 has been optimized to power high performance signal chain circuits. The slew rate of the switch node is controlled by the size of the driver devices. Fast slewing of the switch node is desirable to minimize transition losses but can lead to serious EMI issues due to parasitic inductance. Therefore, the slew rate of the drivers has been optimized such that the ADP2114 can match the performance of the low dropout regulators in supplying sensitive signal chain circuits while providing excellent power efficiency.

### **CONVERTER CONFIGURATION**

#### **SELECTING THE OUTPUT VOLTAGE**

To set the output voltage,  $V_{OUT1}$  ( $V_{OUT2}$ ), select one of the six fixed voltages, as shown in Table 4, by connecting the V1SET (V2SET) pin to GND through an appropriate value resistor (see Figure 70). V1SET and V2SET set the voltage output levels for Channel 1 and Channel 2, respectively. The feedback pin FB1 (FB2) should be directly connected to  $V_{OUT1}$  ( $V_{OUT2}$ ).

**Table 4. Output Voltage Programming**

| $R_{V1SET}(\Omega) \pm 5\%$ | V <sub>OUT1</sub> (V)       | $R_{V2SET}(\Omega) \pm 5\%$ | V <sub>OUT2</sub> (V)       |

|-----------------------------|-----------------------------|-----------------------------|-----------------------------|

| 0 to GND                    | 0.8                         | 0 to GND                    | 0.8                         |

| 4.7 k to GND                | 1.2                         | 4.7 k to GND                | 1.2                         |

| 8.2 k to GND                | 1.5                         | 8.2 k to GND                | 1.5                         |

| 15 k to GND                 | 1.8                         | 15 k to GND                 | 1.8                         |

| 27 k to GND                 | 2.5                         | 27 k to GND                 | 2.5                         |

| 47 k to GND                 | 3.3                         | 47 k to GND                 | 3.3                         |

| 82 k to GND                 | 0.6 to <1.6<br>(adjustable) | 82 k to GND                 | 0.6 to <1.6<br>(adjustable) |

| 0 to VDD                    | 1.6 to 3.3<br>(adjustable)  | 0 to VDD                    | 1.6 to 3.3<br>(adjustable)  |

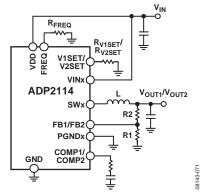

If the required output voltage  $V_{\text{OUT1}}$  ( $V_{\text{OUT2}}$ ) is in the adjustable range, from 0.6 V to less than 1.6 V, connect V1SET (V2SET) through an 82 k $\Omega$  resistor to GND. For the adjustable output voltage range of 1.6 V to 3.3 V, tie V1SET (V2SET) to VDD (see Table 4). The adjustable output voltage of ADP2114 is externally set by a resistive voltage divider from the output voltage to the feedback pin (see Figure 71). The ratio of the resistive voltage divider sets the output voltage, while the absolute value of those resistors sets the divider string current. For lower divider string currents, the small 10 nA (0.1  $\mu$ A maximum) FB bias current should be taken into account when calculating the resistor values. The FB bias current can be ignored for a higher divider string current; however, this degrades efficiency at very light loads.

To limit output voltage accuracy degradation due to FB bias current to less than 0.05% (0.5% maximum), ensure that the divider string current is greater than 20  $\mu$ A. To calculate the desired resistor values, first determine the value of the bottom divider string resistor, R1, by

$$R1 = V_{REF}/I_{STRING} \tag{2}$$

where:

$V_{REF}$  is 0.6 V, the internal reference.

$I_{STRING}$  is the resistor divider string current.

When R1 is determined, calculate the value of the top resistor, R2, by

Figure 70. Configuration for Fixed Outputs

Figure 71. Configuration for Adjustable Outputs

#### **SETTING THE OSCILLATOR FREQUENCY**

The ADP2114 channels can be set to operate in one of the three preset switching frequencies: 300 kHz, 600 kHz, or 1.2 MHz. For 300 kHz operation, connect the FREQ pin to GND. For 600 kHz or 1.2 MHz operation, connect a resistor between the FREQ pin and GND, as shown in Table 5.

**Table 5. Oscillator Frequency Setting**

| $R_{FREQ}(\Omega) \pm 5\%$ | f <sub>sw</sub> (kHz) |

|----------------------------|-----------------------|

| 0 to GND                   | 300                   |

| 8.2 k to GND               | 600                   |

| 27 k to GND                | 1200                  |

Choice of the switching frequency depends on the required dc-to-dc conversion ratio and is limited by the minimum and maximum controllable duty cycle shown on Figure 72. This is due to the requirement of minimum on and minimum off times for current sensing and robust operation. The choice of switching frequency is also determined by the need for small external components. For small, area limited power solutions, use of higher switching frequencies is recommended.

Figure 72. Duty Cycle Working Limits

For single output, multiphase applications that operate at close to 50% duty cycle, it is recommended to use the 1.2 MHz switching frequency to minimize crosstalk between the phases.

#### SYNCHRONIZATION AND CLKOUT

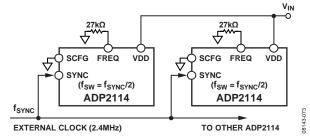

The ADP2114 can be configured to output an internal clock or synchronize to an external clock at the STNC/CLKOUT pin. The SYNC/CLKOUT pin is a bidirectional pin configured by the SCFG pin, as shown in Table 6.

Table 6. SYNC/CLKOUT Configuration Setting

| SCFG | SYNC/CLKOUT |

|------|-------------|

| GND  | Input       |

| VDD  | Output      |

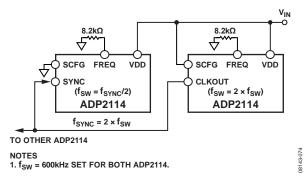

The converter switching frequency,  $f_{SW}$ , is half of the synchronization frequency  $f_{SYNC}/f_{CLKOUT}$  as shown in Equation 4, irrespective of whether SYNC/CLKOUT is configured as an input or output.

$$f_{SYNC}f_{CLKOUT} = 2 \times f_{SW} \tag{4}$$

An external clock can be applied to the SYNC/CLKOUT pin when configured as an input to synchronize multiple ADP2114s to the same external clock. The  $f_{\mbox{\scriptsize SYNC}}$  range is 400 kHz to 4 MHz, which produces  $f_{\mbox{\scriptsize SW}}$  in the 200 kHz to 2 MHz range. See Figure 73 for an illustration.

Figure 73. Synchronization with External Clock ( $f_{SW} = 1.2 \text{ MHz}$  in This Case)

When synchronizing to an external clock, the switching frequency  $f_{\text{SW}}$  must be set close to half of the expected external clock frequency by appropriately terminating the FREQ pin as shown in Table 5.

Figure 74. ADP2114 to SYNC with Another ADP2114 (Note that the SCFG of the master is tied to VDD.)

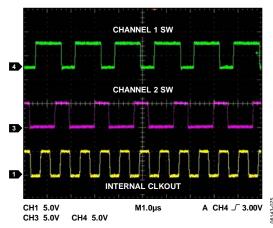

The ADP2114 can also be configured to output a clock signal on the SYNC/CLKOUT pin to synchronize multiple ADP2114s to it (see Figure 74). The CLKOUT signal is 90° phase shifted to the internal clock of the channels so that the master ADP2114 and the slave channels are out of phase (see Figure 75 for additional information).

Figure 75. CLKOUT Waveforms

#### **OPERATION MODE CONFIGURATION**

The dual-channel ADP2114 can be configured to one of the four modes of operation by connecting the OPCFG pin as shown in Table 7. This configuration sets the current limit for each channel and enables or disables the transition to pulse skip mode at light loads.

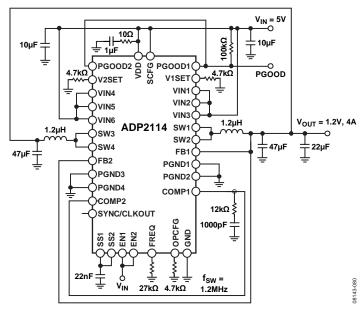

In the dual-phase configuration, the outputs of the two channels are connected together, and they generate a single dc output voltage,  $V_{\rm OUT}$ . For this single combined dual-phase output, only Mode 2 in the OPCFG options can be used. In this mode, the error amplifiers of both phases are used. The feedback pins (FB1 and FB2) are tied together, the compensation pins (COMP1 and COMP2) are tied together, the soft start pins (SS1 and SS2) are tied together, and the enable pins (EN1 and EN2) are tied together.

In addition, if the power-good feature is used, combine PGOOD1 and PGOOD2 and connect them to VDD through a single pull-up resistor.

When the ADP2114 is synchronized to an external clock, the converters always operate in fixed frequency CCM, and they do not enter into pulse skip mode at light loads. In this case, when configuring the OPCFG pin, choose forced PWM mode.

Table 7. Current Limit Operation Mode and Configuration

|      |                             | Maximum Output Current                      | Peak Current Limit                              |                             |

|------|-----------------------------|---------------------------------------------|-------------------------------------------------|-----------------------------|

| Mode | $R_{OPCFG}(\Omega) \pm 5\%$ | I <sub>OUT1</sub> (A)/I <sub>OUT2</sub> (A) | I <sub>LIMIT1</sub> (A)/I <sub>LIMIT2</sub> (A) | Power Savings at Light Load |

| 1    | 0 to GND                    | 2/2                                         | 3.3/3.3                                         | Pulse skip enabled          |

| 2    | 4.7 k to GND                | 2/2                                         | 3.3/3.3                                         | Forced PWM                  |

| 3    | 8.2 k to GND                | 3/1                                         | 4.5/1.9                                         | Pulse skip enabled          |

| 4    | 15 k to GND                 | 3/1                                         | 4.5/1.9                                         | Forced PWM                  |

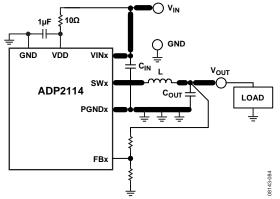

# EXTERNAL COMPONENTS SELECTION INPUT CAPACITOR SELECTION

The input current to a buck converter is pulsating in nature. The current is zero when the high-side switch is off and approximately equal to the load current when it is on. Because this occurs at reasonably high frequencies (300 kHz to 1.2 MHz), the input bypass capacitor ends up supplying most of the high frequency current (ripple current), allowing the input power source to supply only the average (dc) current. The input capacitor needs a sufficient ripple current rating to handle the input ripple as well as an ESR that is low enough to mitigate the input voltage ripple. For the ADP2114, place a 22  $\mu F$ , 6.3 V, X5R ceramic capacitor close to the VINx pin for each channel. X5R or X7R dielectrics are recommended with a voltage rating of 6.3 V or 10 V. Y5V and Z5U dielectrics are not recommended due to their poor temperature and dc bias characteristics.

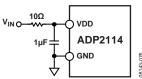

#### **VDD RC FILTER**

It is recommended to apply the input power,  $V_{\rm IN}$ , to the VDD pin through a low-pass RC filter, as shown on Figure 76. Connecting a 10  $\Omega$  resistor in series with  $V_{\rm IN}$  and a 1  $\mu\text{F}$ , 6.3 V, X5R (or X7R) ceramic capacitor between VDD and GND creates a 16 kHz (–3 dB) low-pass filter that effectively attenuates voltage glitches on the input power rail caused by the switching regulator. This provides a clean power supply to the internal, sensitive, analog and digital circuits in the ADP2114, ensuring robust operation.

Figure 76. Low-Pass Filter at VDD

#### **INDUCTOR SELECTION**

The high switching frequency of ADP2114 allows for minimal output voltage ripple even with small inductors. The sizing of the inductor is a trade-off between efficiency and transient response. A small inductor leads to larger inductor current ripple that provides excellent transient response but degrades efficiency. Due to the high switching frequency of ADP2114, shielded ferrite core inductors are recommended for their low core losses and low EMI.

As a guideline, the inductor peak-to-peak current ripple,  $\Delta I_L$ , is typically set to 1/3 of the maximum load current for optimal transient response and efficiency.

$$\Delta I_{L} = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW} \times L} \approx \frac{I_{LOAD(MAX)}}{3}$$

$$\Rightarrow L_{IDEAL} = \frac{3 \times V_{OUT} \times (V_{IN} - V_{OUT})}{f_{SW} \times V_{IN} \times I_{LOAD(MAX)}}$$

(5)

where:

$V_{IN}$  is the input voltage on the VINx terminal.

$V_{OUT}$  is the desired output voltage.

$f_{SW}$  is the converter switching frequency.

The internal slope compensation introduces additional limitations on the optimal inductor value for stable operation because the internal ramp is scaled for each  $V_{\rm OUT}$  setting. The limits for different  $V_{\rm IN}$ ,  $V_{\rm OUT}$ , and  $f_{\rm SW}$  combinations are listed in Table 8.

Table 8. Minimum and Maximum Inductor Values

| Tuble of Millimum and Maximum Inductor varies |                     |                      |            |            |  |

|-----------------------------------------------|---------------------|----------------------|------------|------------|--|

| f <sub>sw</sub> (kHz)                         | V <sub>IN</sub> (V) | V <sub>OUT</sub> (V) | Min L (μH) | Max L (μH) |  |

| 300                                           | 5                   | 3.3                  | 6.8        | 10         |  |

| 300                                           | 5                   | 2.5                  | 5.6        | 15         |  |

| 300                                           | 3.3                 | 2.5                  | 5.6        | 6.8        |  |