# Ultralow Power Step-Down Regulator for Energy Harvesting

Data Sheet ADP5304

#### **FEATURES**

Input supply voltage range: 2.15 V to 6.50 V

Operation down to 2.00 V typical

Ultralow, 260 nA typical quiescent current with no load

Selective output voltage from 1.2 V to 3.6 V (or 0.8 V to 5.0 V)

±2.5% output accuracy over the full temperature range

Output current up to 50 mA in hysteresis mode

VINOK flag to monitor the input voltage

100% duty cycle operation mode

Quick output discharge (QOD) option

Undervoltage lockout (UVLO), overcurrent protection (OCP),

and thermal shutdown (TSD) protection

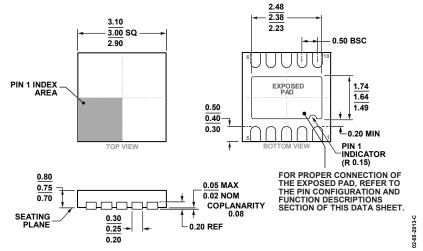

10-lead, 3 mm × 3 mm LFCSP package

-40°C to +125°C operating junction temperature range

#### **APPLICATIONS**

Energy (gas, water) metering

Energy harvesting applications

Portable and battery-powered equipment

Medical applications

Keep-alive power supply

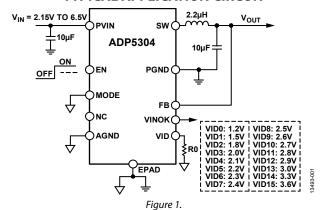

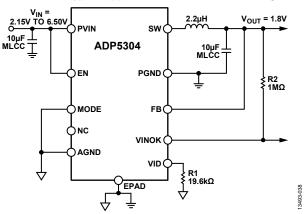

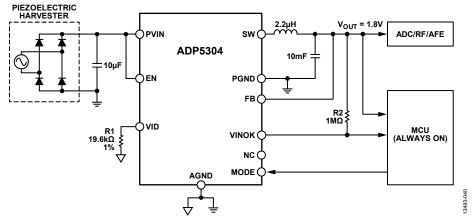

#### TYPICAL APPLICATION CIRCUIT

#### **GENERAL DESCRIPTION**

The ADP5304 is a high efficient, ultralow quiescent current step-down regulator that draws only 260 nA of quiescent current to regulate the output at no load.

The ADP5304 runs from an input voltage range of  $2.15~\rm V$  to  $6.50~\rm V$ , allowing the use of the multiple alkaline, NiMH, and Lithium cells, or the use of a high impedance power source. The output voltage is selectable from  $0.8~\rm V$  to  $5.0~\rm V$  by an external VID resistor to ground. The total solution requires only four tiny external components.

The ADP5304 operates in hysteresis mode via connecting the MODE pin to ground. In hysteresis mode, the regulator achieves excellent efficiency at a power of less than 1 mW and provides up to 50 mA of output load. The device enables very efficient power management to achieve the collection of small amounts of energy from the high impedance battery or the

energy harvester to charge up the conventional capacitor or super capacitor.

The ADP5304 integrates an ultralow power comparator with a factory programmable voltage reference to monitor the voltage of the input power source. The voltage reference, with hysteresis, is the threshold for the stopping and the starting of the switching, allowing the use of the high impedance power source.

Other key features of the ADP5304 include separate enabling and a QOD. Safety features, such as OCP, TSD, and input UVLO are also included.

The ADP5304 is available in 10-lead, 3 mm  $\times$  3 mm LFCSP package rated for the  $-40^{\circ}$ C to  $+125^{\circ}$ C junction temperature range.

Trademarks and registered trademarks are the property of their respective owners.

# **ADP5304\* Product Page Quick Links**

Last Content Update: 11/01/2016

# Comparable Parts <a> □</a>

View a parametric search of comparable parts

## Evaluation Kits <a> □</a>

• ADP5304 Evaluation Board

# Documentation <a>□</a>

#### **Data Sheet**

• ADP5304: Ultralow Power Step-Down Regulator for Energy Harvesting Data Sheet

#### **User Guides**

• UG-882: Evaluating the ADP5304 Ultralow Step-Down Regulator

# Design Resources -

- ADP5304 Material Declaration

- · PCN-PDN Information

- Quality And Reliability

- · Symbols and Footprints

## Discussions <a>□</a>

View all ADP5304 EngineerZone Discussions

# Sample and Buy -

Visit the product page to see pricing options

# Technical Support <a> Image: Page 1</a> <a> Image: Page 2</a> <a> Image: Page 3</a> <a>

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

# **TABLE OF CONTENTS**

| Features                                    |

|---------------------------------------------|

| Applications                                |

| Typical Application Circuit                 |

| General Description                         |

| Revision History                            |

| Detailed Functional Block Diagram           |

| Specifications                              |

| Absolute Maximum Ratings                    |

| Thermal Resistance                          |

| ESD Caution                                 |

| Pin Configuration and Function Descriptions |

| Typical Performance Characteristics         |

| Theory of Operation1                        |

| Buck Regulator Operational Mode1            |

| Adjustable and Fixed Output Voltages1       |

| Undervoltage Lockout (UVLO)1                |

| Enable/Disable1                             |

| VINOK Function1                             |

| Current Limit                  | 12 |

|--------------------------------|----|

| Short-Circuit Protection       | 12 |

| Soft Start                     | 12 |

| Startup with Precharged Output | 12 |

| 100% Duty Operation            | 12 |

| Active Discharge               | 12 |

| Thermal Shutdown               | 12 |

| Applications Information       | 13 |

| External Component Selection   | 13 |

| Selecting the Inductor         | 13 |

| Output Capacitor               | 13 |

| Input Capacitor                | 14 |

| Layout Recommendations         | 14 |

| Typical Application Circuits   | 15 |

| Factory Programmable Options   | 16 |

| Outline Dimensions             | 17 |

| Ordering Guide                 | 17 |

#### **REVISION HISTORY**

10/15—Revision 0: Initial Version

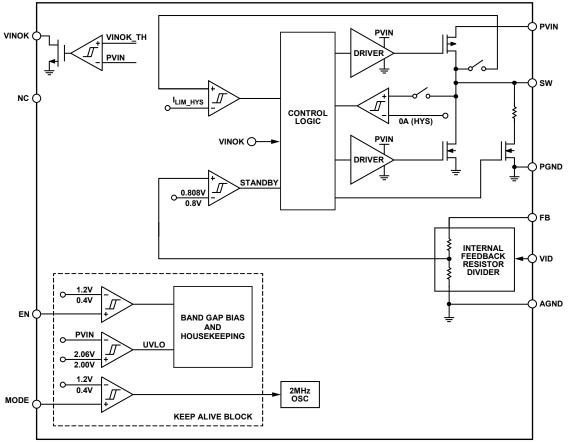

# **DETAILED FUNCTIONAL BLOCK DIAGRAM**

Figure 2.

# **SPECIFICATIONS**

$V_{\rm IN}$  = 3.6 V,  $V_{\rm OUT}$  = 2.5 V,  $T_{\rm J}$  = -40°C to +125°C for minimum and maximum specifications, and  $T_{\rm A}$  = 25°C for typical specifications, unless otherwise noted.

Table 1.

| Parameter                                                                  | Symbol                     | Min   | Тур  | Max   | Unit | Test Conditions/Comments                                                       |

|----------------------------------------------------------------------------|----------------------------|-------|------|-------|------|--------------------------------------------------------------------------------|

| INPUT SUPPLY VOLTAGE RANGE                                                 | V <sub>IN</sub>            | 2.15  |      | 6.50  | V    |                                                                                |

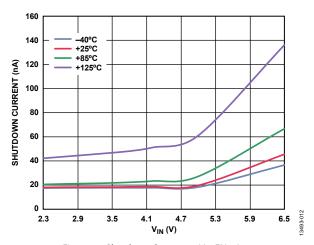

| SHUTDOWN CURRENT                                                           | I <sub>SHUTDOWN</sub>      |       | 18   | 40    | nA   | $V_{EN} = 0 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le +85^{\circ}\text{C}$  |

|                                                                            |                            |       | 18   | 130   | nA   | $V_{EN} = 0 \text{ V}, -40^{\circ}\text{C} \le T_{J} \le +125^{\circ}\text{C}$ |

| QUIESCENT CURRENT                                                          |                            |       |      |       |      |                                                                                |

| Operating Quiescent Current                                                | IQ                         |       | 260  | 360   | nA   | -40°C ≤ T <sub>J</sub> ≤ +85°C                                                 |

|                                                                            |                            |       | 260  | 500   | nA   | -40°C ≤ T <sub>J</sub> ≤ +125°C                                                |

|                                                                            |                            |       | 640  | 1500  | nA   | 100% duty cycle operation, $V_{IN} = 3.0 \text{ V}$ ,                          |

|                                                                            |                            |       |      |       |      | V <sub>OUT</sub> set as 3.3 V                                                  |

| UNDERVOLTAGE LOCKOUT                                                       | UVLO                       |       |      |       |      |                                                                                |

| UVLO Threshold                                                             |                            |       |      |       |      |                                                                                |

| Rising                                                                     | $V_{\text{UVLO\_RISING}}$  |       | 2.06 | 2.14  | V    |                                                                                |

| Falling                                                                    | V <sub>UVLO_FALLING</sub>  | 1.90  | 2.00 |       | V    |                                                                                |

| EN PIN                                                                     |                            |       |      |       |      |                                                                                |

| Input Voltage Threshold                                                    |                            |       |      |       |      |                                                                                |

| High                                                                       | V <sub>IH</sub>            | 1.2   |      |       | V    |                                                                                |

| Low                                                                        | V <sub>IL</sub>            |       |      | 0.4   | V    |                                                                                |

| Input Leakage Current                                                      | I <sub>EN_LEAKAGE</sub>    |       |      | 25    | nA   |                                                                                |

| FB PIN                                                                     |                            |       |      |       |      |                                                                                |

| Output Options by VID Resistor                                             | V <sub>OUT_OPT</sub>       | 0.8   |      | 5.0   | V    | 0.8 V to 5.0 V in different factory option                                     |

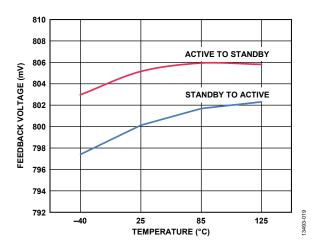

| Fixed VID Code Threshold Accuracy from Active                              | $V_{FB\_FIX}$              | -0.75 |      | +0.75 | %    | T <sub>J</sub> = 25°C                                                          |

| Mode to Standby Mode                                                       |                            | 2.5   |      | . 2.5 | 0/   | 40%C + T + + 135%C                                                             |

| Adicate ble VID Code Three bold According from                             | V                          | -2.5  |      | +2.5  | %    | -40°C ≤ T <sub>J</sub> ≤ +125°C                                                |

| Adjustable VID Code Threshold Accuracy from<br>Active Mode to Standby Mode | V <sub>FB_ADJ</sub>        | -3    |      | +3    | %    | -40°C ≤ T <sub>J</sub> ≤ +125°C                                                |

| Hysteresis of Threshold Accuracy from Active                               | V <sub>FB (HYS)</sub>      |       | 1    |       | %    |                                                                                |

| Mode to Standby Mode                                                       | • FB (FITS)                |       | •    |       | 70   |                                                                                |

| Feedback Bias Current                                                      | I <sub>FB</sub>            |       | 66   | 95    | nA   | Output Option 0, V <sub>OUT</sub> = 2.5 V                                      |

|                                                                            |                            |       | 25   | 45    | nA   | Output Option 1, V <sub>OUT</sub> = 1.3 V                                      |

| SW PIN                                                                     |                            |       |      |       |      |                                                                                |

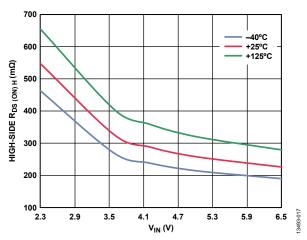

| High-Side Power FET On Resistance                                          | R <sub>DS (ON) H</sub>     |       | 386  | 520   | mΩ   | Pin to pin measurement                                                         |

| Low-Side Power FET On Resistance                                           | R <sub>DS (ON) L</sub>     |       | 299  | 470   | mΩ   | Pin to pin measurement                                                         |

| Peak Current                                                               | I <sub>LIM</sub>           |       | 265  |       | mA   |                                                                                |

| Minimum On Time                                                            | t <sub>MIN_ON</sub>        |       | 40   | 70    | ns   |                                                                                |

| VINOK PIN                                                                  |                            |       |      |       |      |                                                                                |

| VINOK Monitor Threshold Range                                              | V <sub>VINOK</sub> (RISE)  | 2.05  |      | 5.15  | V    | Factory programmable                                                           |

| VINOK Monitor Accuracy Range                                               |                            | -1.5  |      | +1.5  | %    | T <sub>J</sub> = 25°C                                                          |

|                                                                            |                            | -3    |      | +3    | %    | -40°C ≤ T <sub>J</sub> ≤ +125°C                                                |

| VINOK Monitor Threshold Hysteresis                                         | V <sub>VINOK (HYS)</sub>   |       | 1.5  |       | %    |                                                                                |

| VINOK Rising Delay                                                         | t <sub>VINOK_RISE</sub>    |       | 190  |       | μs   |                                                                                |

| VINOK Falling Delay                                                        | t <sub>VINOK_FALL</sub>    |       | 130  |       | μs   |                                                                                |

| Leakage Current for the VINOK Pin                                          | I <sub>VINOK_LEAKAGE</sub> |       | 0.1  | 1     | μΑ   |                                                                                |

| Output Low Voltage for the VINOK Pin                                       | V <sub>VINOK_LOW</sub>     |       | 50   | 100   | mV   | $I_{VINOK} = 100 \mu A$                                                        |

| SOFT START                                                                 |                            |       |      |       |      |                                                                                |

| Default Soft Start Time                                                    | tss                        |       | 350  |       | μs   | Factory trim, 1 bit (350 μs, 2800 μs)                                          |

| Start-Up Delay                                                             | t <sub>START_DELAY</sub>   |       | 2    |       | ms   | Delay from the EN pin being pulled high                                        |

| C <sub>OUT</sub> DISCHARGE SWITCH ON RESISTANCE                            | R <sub>DIS</sub>           |       | 290  |       | Ω    |                                                                                |

| THERMAL SHUTDOWN                                                           |                            |       |      |       |      |                                                                                |

| Threshold                                                                  | T <sub>SHDN</sub>          |       | 142  |       | °C   |                                                                                |

| Hysteresis                                                                 | T <sub>HYS</sub>           |       | 127  |       | °C   |                                                                                |

## **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                            | Rating                 |

|--------------------------------------|------------------------|

| PVIN to PGND                         | −0.3 V to +7 V         |

| SW to PGND                           | −0.3 V to PVIN + 0.3 V |

| FB to AGND                           | −0.3 V to +7 V         |

| VID to AGND                          | −0.3 V to +7 V         |

| EN to AGND                           | −0.3 V to +7 V         |

| VINOK to AGND                        | −0.3 V to +7 V         |

| MODE to AGND                         | −0.3 V to +7 V         |

| NC to AGND                           | −0.3 V to +7 V         |

| PGND to AGND                         | −0.3 V to +0.3 V       |

| Storage Temperate Range              | −65°C to +150°C        |

| Operating Junction Temperature Range | −40°C to +125°C        |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

**Table 3. Thermal Resistance**

| Package Type               | θја | θις  | Unit |

|----------------------------|-----|------|------|

| 10-Lead, 3 mm × 3 mm LFCSP | 57  | 0.86 | °C/W |

## **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

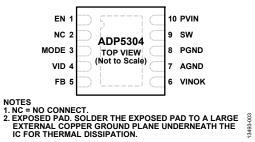

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                               |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------|

| 1       | EN       | Enable Input for the Regulator. A logic low on this pin disables the regulator.                                           |

| 2       | NC       | No Connect. Connect this pin to ground.                                                                                   |

| 3       | MODE     | Operating Mode Pin. Connect this pin to ground; the regulator operates in hysteresis mode.                                |

| 4       | VID      | Voltage Configuration Pin. Connect one resistor from this pin to ground to configure the output voltage of the regulator. |

| 5       | FB       | Feedback Sensing Input for the Regulator.                                                                                 |

| 6       | VINOK    | Input Power-Good Signal. This open-drain output is the power-good signal for the input voltage.                           |

| 7       | AGND     | Analog Ground.                                                                                                            |

| 8       | PGND     | Power Ground.                                                                                                             |

| 9       | SW       | Switching Node Output for the Regulator.                                                                                  |

| 10      | PVIN     | Power Input for the Regulator.                                                                                            |

|         | EPAD     | Exposed Pad. Solder the exposed pad to a large external copper ground plane underneath the IC for thermal dissipation.    |

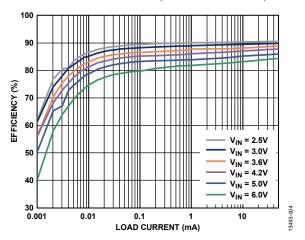

## TYPICAL PERFORMANCE CHARACTERISTICS

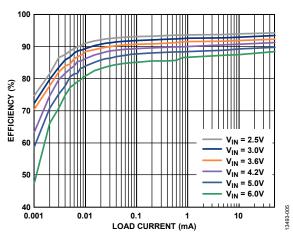

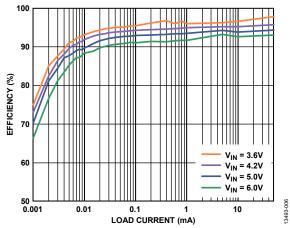

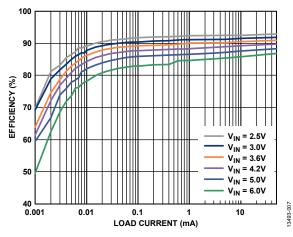

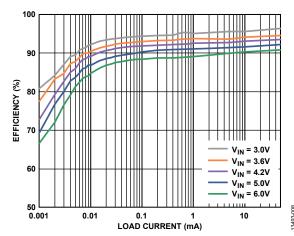

$V_{\text{IN}}$  = 3.6 V,  $V_{\text{OUT}}$  = 2.5 V, L1 = 2.2  $\mu$ H,  $C_{\text{IN}}$  =  $C_{\text{OUT}}$  = 10  $\mu$ F,  $f_{\text{SW}}$  = 2 MHz,  $T_{\text{A}}$  = 25°C, unless otherwise noted.

Figure 4. Hysteresis Efficiency vs. Load Current,  $V_{OUT} = 1.2 \text{ V}$

Figure 5. Hysteresis Efficiency vs. Load Current,  $V_{OUT} = 1.8 \text{ V}$

Figure 6. Hysteresis Efficiency vs. Load Current,  $V_{OUT} = 3.3 V$

Figure 7. Hysteresis Efficiency vs. Load Current,  $V_{OUT} = 1.5 \text{ V}$

Figure 8. Hysteresis Efficiency vs. Load Current,  $V_{OUT} = 2.5 V$

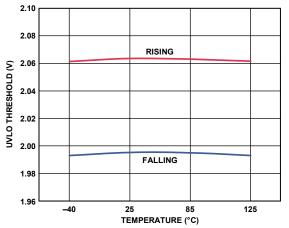

Figure 9. UVLO Threshold, Rising and Falling vs. Temperature

Figure 10. Shutdown Current vs.  $V_{IN}$ , EN = Low

Figure 11. High-Side RDS (ON) H VS. VIN

Figure 12. Feedback Voltage vs. Temperature

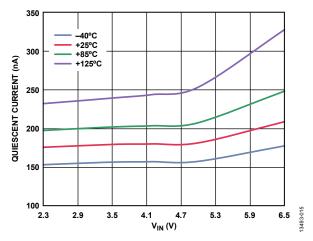

Figure 13. Quiescent Current vs. V<sub>IN</sub>

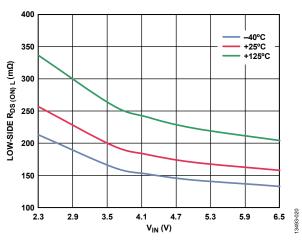

Figure 14. Low-Side R<sub>DS (ON) L</sub> vs. V<sub>IN</sub>

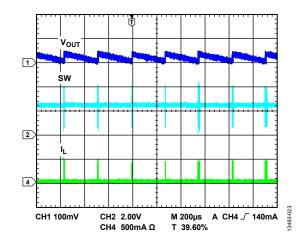

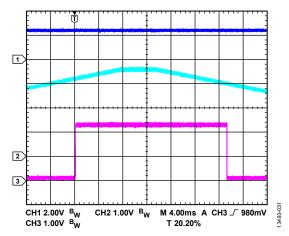

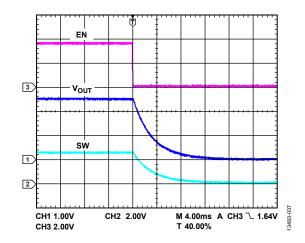

Figure 15. Steady Waveform,  $I_{LOAD} = 1 \text{ mA}$  ( $I_L$  is the Inductor Current)

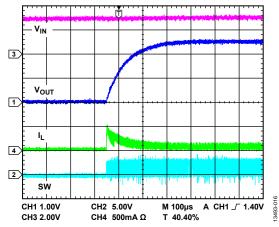

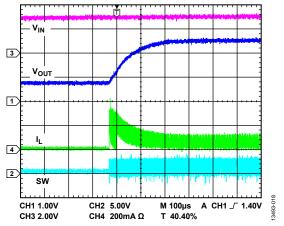

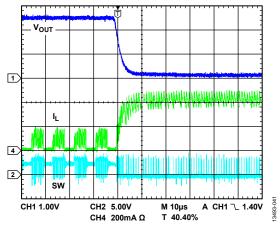

Figure 16. Soft Start,  $I_{LOAD} = 50 \text{ mA}$

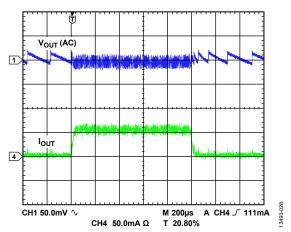

Figure 17. Load Transient,  $I_{LOAD}$  from 0 mA to 50 mA

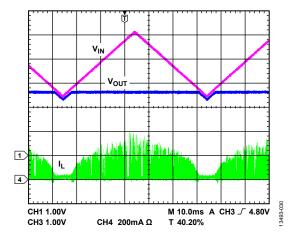

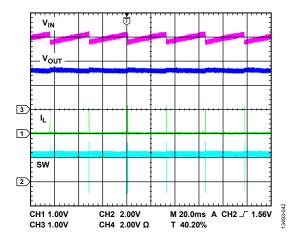

Figure 18. Input Voltage Ramp-Up and Ramp-Down

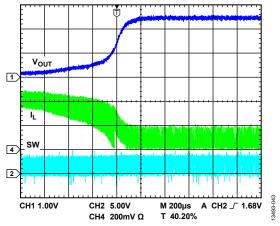

Figure 19. Soft Start with Precharge Function

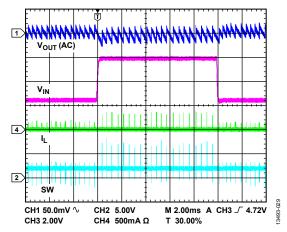

Figure 20. Line Transient,  $I_{LOAD} = 10 \,\mu\text{A}$

Figure 21. VINOK Function at a 3.0 V VINOK Threshold

Figure 22. Output Short Protection

Figure 23. 260  $\mu$ A Current Source Charge Up, 100  $\mu$ F Output Capacitor with 100  $\mu$ A Load Current, and 3.0 V VINOK Threshold

Figure 24. Output Short Recovery

Figure 25. Quick Output Discharge Function

## THEORY OF OPERATION

The ADP5304 is a high efficient, ultralow quiescent current step-down regulator in a 10-lead LFCSP package, designed to meet demanding performance and board space requirements. The device enables direct connection to a wide input voltage range of 2.15 V to 6.50 V, allowing the use of high impedance power sources or energy harvester sources.

#### **BUCK REGULATOR OPERATIONAL MODE**

The ADP5304 buck regulator operates in hysteresis mode and charges the output voltage slightly higher than its nominal output voltage with PWM pulses via the regulation of constant peak inductor current. When the output voltage increases until the output sense signal exceeds the hysteresis upper threshold, the regulator enters the standby mode. In standby mode, the high-side and low-side MOSFET and a majority of the circuitry are disabled to allow a low quiescent current, as well as high efficiency performance. During standby mode, the output capacitor supplies the energy into the load and the output voltage decreases until it falls below the hysteresis comparator lower threshold. Then, the buck regulator wakes up into active mode and generates the PWM pulses to charge the output again.

The buck regulator is forced to operate in hysteresis mode via connecting the MODE pin to ground. The regulator only draws 260 nA of quiescent current to regulate the output under zero load, which allows the regulator to act as keep-alive power supply in battery-powered applications or energy harvesting systems.

#### ADJUSTABLE AND FIXED OUTPUT VOLTAGES

The ADP5304 provides adjustable output voltage settings via the connection of one resistor through the VID pin to AGND. The VID detection circuitry works in the start-up period, and the voltage ID code is sampled and held into the internal register and does not change until the next power recycle. Furthermore, the ADP5304 provides a fixed output voltage programmed via the factory fuse. In this condition, connect the VID pin to the PVIN pin.

For output voltage settings, the feedback resistor divider is built in to the ADP5304, and the feedback pin (FB) must be tied directly to the output. An ultralow power voltage reference and an integrated high impedance (50 M $\Omega$ , typical) feedback divider network contribute to low quiescent current. Table 5 lists the output voltage options by the VID pin configurations. It is recommended to use a 1% resistor.

Table 5. Output Voltage Options by the VID Pin

| VID<br>Configuration             | V <sub>ουτ</sub> ,<br>Factory Option 0 (V) | V <sub>оит</sub> ,<br>Factory Option 1 (V) |

|----------------------------------|--------------------------------------------|--------------------------------------------|

| Short to ground                  | 3.0                                        | 3.1                                        |

| Short to PVIN                    | 2.5                                        | 1.3                                        |

| $R_{VID} = 499 \text{ k}\Omega$  | 3.6                                        | 5.0                                        |

| $R_{VID} = 316 \text{ k}\Omega$  | 3.3                                        | 4.5                                        |

| $R_{VID} = 226 \text{ k}\Omega$  | 2.9                                        | 4.2                                        |

| $R_{VID} = 174 \text{ k}\Omega$  | 2.8                                        | 3.9                                        |

| $R_{VID} = 127 \text{ k}\Omega$  | 2.7                                        | 3.4                                        |

| $R_{VID} = 97.6 \text{ k}\Omega$ | 2.6                                        | 3.2                                        |

| $R_{VID} = 76.8 \text{ k}\Omega$ | 2.4                                        | 1.9                                        |

| $R_{VID} = 56.2 \text{ k}\Omega$ | 2.3                                        | 1.7                                        |

| $R_{VID} = 43 \text{ k}\Omega$   | 2.2                                        | 1.6                                        |

| $R_{VID} = 32.4 \text{ k}\Omega$ | 2.1                                        | 1.4                                        |

| $R_{VID} = 25.5 \text{ k}\Omega$ | 2.0                                        | 1.1                                        |

| $R_{VID} = 19.6 \text{ k}\Omega$ | 1.8                                        | 1.0                                        |

| $R_{VID} = 15 \text{ k}\Omega$   | 1.5                                        | 0.9                                        |

| $R_{VID} = 11.8 \text{ k}\Omega$ | 1.2                                        | 0.8                                        |

#### UNDERVOLTAGE LOCKOUT (UVLO)

The undervoltage lockout circuitry monitors the input voltage level on the PVIN pin. If input voltage falls below 2.00 V (typical), the regulator turns off. After the input voltage rises above 2.06 V (typical), the soft start period initiates, and when the EN pin is high, the regulator enables.

#### **ENABLE/DISABLE**

The ADP5304 includes a separate enable (EN) pin. A logic high on the EN pin starts the regulator. Due to the low quiescent current design, it is typical for the regulator to start switching after a delay of a few milliseconds from the EN pin being pulled high.

A logic low on the EN pin immediately disables the regulator and brings the regulator into extremely low current consumption.

#### **VINOK FUNCTION**

The ADP5304 includes an open-drain VINOK output that can be used to indicate the input voltage status. The VINOK output becomes active high when the input voltage on the PVIN pin is above the reference threshold. When the input voltage falls below the reference threshold, the VINOK pin goes low. Note that a relatively long validation time of 130  $\mu s$  typical exists for the VINOK output status to change due to the ultralow power comparator design.

The ADP5304 VINOK threshold also determines the time when the buck regulator starts and stops switching. When the input voltage is below the threshold, the regulator stops switching in hysteresis mode. After the input source charges the input capacitor voltage above a hysteresis from the threshold, the regulator resumes switching. The regulator operates the input voltage in a hysteresis window around the threshold considered as the maximum power point tracking (MPPT). The high impedance input power source or small input power application employs the ADP5304 to charge the large output capacitor via trickle charging.

Different VINOK thresholds are factory programmable from 2.05 V to 5.15 V in 50 mV steps. To order a device with options other than the default options, contact your local Analog Devices, Inc., sales or distribution representative.

#### **CURRENT LIMIT**

The buck regulators in the ADP5304 have protection circuitry that limits the direction and the amount of current to a certain level that flows through the high-side MOSFET and the low-side MOSFET in cycle by cycle mode. The positive current limit on the high-side MOSFET limits the amount of current that can flow from the input to the output. The negative current limit on the low-side MOSFET prevents the inductor current from reversing direction and flowing out of the load.

## **SHORT-CIRCUIT PROTECTION**

The buck regulators in the ADP5304 include frequency foldback to prevent current runaway on a hard short. When the output voltage at the feedback pin (FB) falls below 0.3 V typical, indicating the possibility of a hard short at the output, the switching frequency in active mode reduces to half of the internal oscillator frequency. The reduction in the switching frequency allows more time for the inductor to discharge, preventing a runaway of output current.

#### **SOFT START**

The ADP5304 has an internal soft start function that ramps the output voltage in a controlled limitation upon startup, thereby limiting the inrush current. This prevents possible input voltage drops when a battery or a high impedance power source is connected to the input of the device. The typical soft start time or the regulator is 350  $\mu$ s.

A different soft start time ( $2800 \mu s$ ) can be programmed for ADP5304 via the factory fuse (see Table 11).

#### STARTUP WITH PRECHARGED OUTPUT

The buck regulators in the ADP5304 include a precharged start-up feature to protect the low-side FETs from damage during startup. If the output voltage is precharged before the regulator is turned on, the regulator prevents reverse inductor current—which discharges the output capacitor—until the internal soft start reference voltage exceeds the precharged voltage on the feedback pin.

#### **100% DUTY OPERATION**

When the input voltage approaches the output voltage, the ADP5304 stops switching and enters 100% duty cycle operation. It connects the output via the inductor and the internal high-side power switch to the input. When the input voltage is charged again and the required duty cycle falls to 95% typical, the buck immediately restarts switching and regulation without allowing overshoot on the output voltage. The ADP5304 draws an ultralow quiescent current of only 640 nA typical during 100% duty cycle operation.

#### **ACTIVE DISCHARGE**

The regulator in the ADP5304 integrates an optional, factory programmable discharge switch from the switching node to ground. This switch turns on when its associated regulator is disabled, which helps discharge the output capacitor quickly. The typical value of the discharge switch is 290  $\Omega$  for the regulator.

By default, the discharge function is not enabled. The active discharge function can be enabled by the factory fuse

#### THERMAL SHUTDOWN

If the ADP5304 junction temperature exceeds 142°C, the thermal shutdown circuit turns the IC off, except for the internal linear regulator. Extreme junction temperatures can be the result of high current operation, poor circuit board design, or high ambient temperature. A 15°C hysteresis is included so that the ADP5304 does not return to operation after thermal shutdown until the junction temperature falls below 127°C. When the device exits thermal shutdown, a soft start is initiated for each enabled channel.

## APPLICATIONS INFORMATION

This section describes the external components selection for the ADP5304. The typical application circuit is shown in Figure 26.

Figure 26. Typical Application Circuit

#### **EXTERNAL COMPONENT SELECTION**

The ADP5304 is optimized for operation with a 2.2  $\mu H$  inductor and 10  $\mu F$  output capacitors for various output voltages using the closed-loop compensation and adaptive slope compensation circuits. The selection of components depends on the efficiency, the load current transient, and other application requirements. The trade-offs among performance parameters, such as efficiency and transient response, are made by varying the choice of external components.

#### **SELECTING THE INDUCTOR**

The high switching frequency of the ADP5304 allows the use of small surface-mount power inductors. The dc resistance (DCR) value of the selected inductor affects efficiency. In addition, it is recommended to select a multilayer inductor rather than a magnetic iron inductor because the high switching frequency increases the core temperature rise and enlarges the core loss.

A minimum requirement of the dc current rating of the inductor is for it to be equal to the maximum load current plus half of the inductor current ripple ( $\Delta I_L$ ), as shown by the following equations:

$$\Delta I_{L} = V_{OUT} + \left(\frac{1 - V_{OUT}/V_{IN}}{L \times f_{SW}}\right)$$

$$I_{PK} = I_{LOAD \, (MAX)} + \left(\frac{\Delta I_{L}}{2}\right)$$

where  $I_{PK}$  is the peak inductor current.

Use the inductor series from the different vendors shown in Table 6.

#### **OUTPUT CAPACITOR**

Output capacitance is required to minimize the voltage overshoot, the voltage undershoot, and the ripple voltage present on the output. Capacitors with low equivalent series resistance (ESR) values produce the lowest output ripple. Furthermore, use capacitors such as X5R and X7R dielectric capacitors. Do not use Y5V and Z5U capacitors, because they are unsuitable choices due to their large capacitance variation over temperature and their dc bias voltage changes. Because ESR is important, select the capacitor using the following equation:

$$ESR_{COUT} \le \frac{V_{RIPPLE}}{\Delta I_{I}}$$

where:

$ESR_{COUT}$  is the ESR of the chosen capacitor.  $V_{RIPPLE}$  is the peak-to-peak output voltage ripple.

Increasing the output capacitor value has no effect on stability and may reduce output ripple and enhance load transient response. ADP5304 can charge up the conventional capacitor or super capacitor. When choosing the output capacitor value, it is important to account for the loss of capacitance due to output voltage dc bias.

Use the capacitor series from the different vendors shown in Table 7.

**Table 6. Recommended Inductors**

| Vendor    | Model            | Inductance (µH) | Dimensions (mm)             | DCR (mΩ) | I <sub>SAT</sub> <sup>1</sup> (A) |

|-----------|------------------|-----------------|-----------------------------|----------|-----------------------------------|

| TDK       | MLP2016V2R2MT0S1 | 2.2             | 2.0 × 1.6 × 0.85            | 280      | 1.0                               |

| Wurth     | 74479889222      | 2.2             | $2.5 \times 2.0 \times 1.2$ | 250      | 1.7                               |

| Coilcraft | LPS3314-222MR    | 2.2             | 3.3 × 3.3 × 1.3             | 100      | 1.5                               |

<sup>&</sup>lt;sup>1</sup> I<sub>SAT</sub> is the dc current at which the inductance drops 30% (typical) from its value without current.

**Table 7. Input and Output Capacitors**

| Vendor | Model             | Capacitance (μF) | Size |

|--------|-------------------|------------------|------|

| Murata | GRM188D71A106MA73 | 10               | 0603 |

| Murata | GRM21BR71A106KE51 | 10               | 0805 |

| Murata | GRM31CR60J107ME39 | 100              | 1206 |

#### **INPUT CAPACITOR**

An input capacitor is required to reduce the input voltage ripple, input ripple current, and source impedance. Place the input capacitor as close as possible to the PVIN pin. A low ESR X7R or X5R capacitor is highly recommended to minimize the input voltage ripple.

Use the following equation to determine the rms input current:

$$I_{\mathit{RMS}} \geq I_{\mathit{LOAD}~(\mathit{MAX}~)} \sqrt{\frac{V_{\mathit{OUT}}\left(V_{\mathit{IN}} - V_{\mathit{OUT}}~\right)}{V_{\mathit{IN}}}}$$

For most applications, a 10  $\mu F$  capacitor is sufficient. The input capacitor can be increased without any limit for better input voltage filtering.

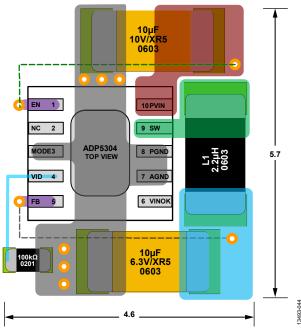

## **LAYOUT RECOMMENDATIONS**

Figure 27 shows the typical printed circuit board (PCB) layout for the ADP5304.

Figure 27. PCB Layout for the ADP5304

# TYPICAL APPLICATION CIRCUITS

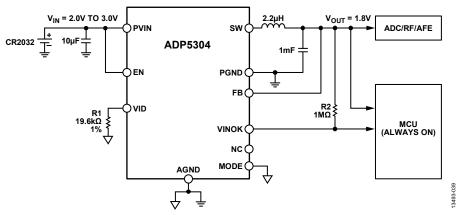

The ADP5304 can be used as a keep-alive, ultralow power step-down regulator to extend the battery life and load pulse current capability with super capacitors (see Figure 28), and as a battery-powered equipment or wireless sensor network

controlled by a microcontroller or a processor (see Figure 29). The VINOK function can achieve the maximum power point tracking.

Figure 28. Typical ADP5304 Application with a Coin Cell Battery (CR2032)

Figure 29. Typical ADP5304 Application with a Piezoelectric Harvester

# **FACTORY PROGRAMMABLE OPTIONS**

To order a device with options other than the default options, contact your local Analog Devices sales or distribution representative.

**Table 8. Output Voltage VID Setting Options**

| Option   | Description                                                                                                                                                                              |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Option 0 | VID resistor to set the output voltage as follows:<br>1.2 V, 1.5 V, 1.8 V, 2.0 V, 2.1 V, 2.2 V, 2.3 V, 2.4 V, 2.5 V,<br>2.6 V, 2.7 V, 2.8 V, 2.9 V, 3.0 V, 3.3 V, 3.6 V, 3.3 V (default) |

| Option 1 | VID resistor to set the output voltage as follows:<br>0.8 V, 0.9 V, 1.0 V, 1.1 V, 1.3 V, 1.4 V, 1.6 V, 1.7 V, 1.9 V,<br>3.1 V, 3.4 V, 3.9 V, 4.2 V, 4.5 V, 5.0 V                         |

**Table 9. VINOK Monitor Threshed Options**

| Option    | VINOK Monitor Threshold (V) |

|-----------|-----------------------------|

| Option 0  | 2.05                        |

| Option 1  | 2.10                        |

| Option 2  | 2.15                        |

| Option 3  | 2.20                        |

|           |                             |

| Option 20 | 3.00 (default)              |

|           |                             |

| Option 62 | 5.10                        |

| Option 63 | 5.15                        |

### **Table 10. Output Discharge Functionality Options**

| Option   | Description                                                     |

|----------|-----------------------------------------------------------------|

| Option 0 | Output discharge function disabled for buck regulator (default) |

| Option 1 | Output discharge function enabled form buck regulator           |

**Table 11. Soft Start Timer Options**

| Option   | Description      |

|----------|------------------|

| Option 0 | 350 μs (default) |

| Option 1 | 2800 μs          |

# **OUTLINE DIMENSIONS**

Figure 30. 10-Lead Lead Frame Chip Scale Package [LFCSP\_WD] 3 mm × 3 mm Body, Very Very Thin, Dual Lead (CP-10-9) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                                                                                 | Package Option |

|--------------------|-------------------|-----------------------------------------------------------------------------------------------------|----------------|

| ADP5304ACPZ-1-R7   | −40°C to +125°C   | 10-Lead Lead Frame Chip Scale Package [LFCSP_WD] Without Output Discharge, VINOK Threshold = 3.00 V | CP-10-9        |

| ADP5304ACPZ-2-R7   | -40°C to +125°C   | 10-Lead Lead Frame Chip Scale Package [LFCSP_WD] Without Output Discharge, VINOK Threshold = 4.00 V | CP-10-9        |

| ADP5304-EVALZ      |                   | Evaluation Board                                                                                    |                |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.