## 150 MBPS Quad-Channel Digital Isolator

### ADuM141ES

### 1.0 Scope

This specification documents the detail requirements for space qualified product manufactured on Analog Devices, Inc.'s QML certified line per MIL-PRF-38535 Level V except as modified herein.

The manufacturing flow described in the STANDARD SPACE LEVEL PRODUCTS PROGRAM brochure is to be considered a part of this specification. http://www.analog.com/aeroinfo

This data specifically details the space grade version of this product. A more detailed operational description and a complete data sheet for commercial product grades can be found at http://www.analog.com/ADuM141

### 2.0 Part Number

The complete part number(s) of this specification follows:

Specific Part Number

**Description**

ADuM141E1L703F

150 MBPS Quad-Channel Digital Isolator

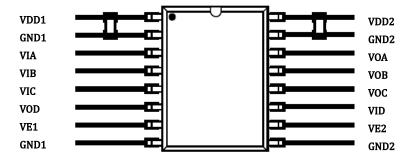

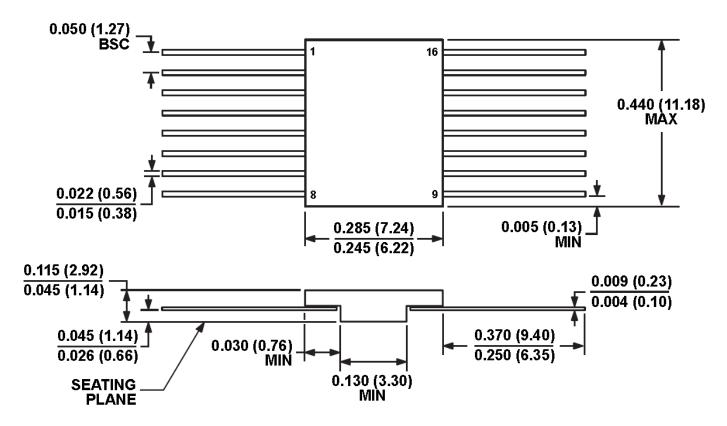

### 3.0 Case Outline

The case outline(s) are as designated in MIL-STD-1835 and as follows:

Outline Letter Descriptive Designator

<u>Terminals</u>

<u>Lead Finish</u>

Package style

Χ

CDFP4-F16

16 lead

Hot Solder Dip

Bottom Brazed Flat Pack

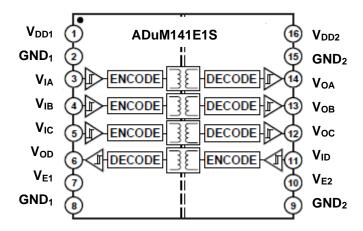

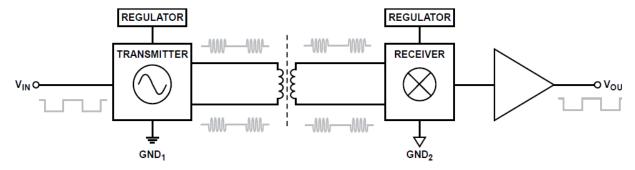

### **FUNCTIONAL BLOCK DIAGRAM**

ASD0016568

Rev. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com Fax: 781.326.8703 © 2020 Analog Devices, Inc. All rights reserved.

|            | Package: X         |                |                                                                        |  |  |  |  |  |  |  |

|------------|--------------------|----------------|------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Pin Number | Terminal<br>Symbol | Pin Type       | Pin Description                                                        |  |  |  |  |  |  |  |

| 1          | VDD1               | Power          | Supply Voltage for Isolator Side 1 <u>1</u> /                          |  |  |  |  |  |  |  |

| 2          | GND1               | Power          | Ground 1. Ground reference for Isolator Side 1. <u>2</u> /             |  |  |  |  |  |  |  |

| 3          | VIA                | Digital Input  | Logic Input A.                                                         |  |  |  |  |  |  |  |

| 4          | VIB                | Digital Input  | Logic Input B                                                          |  |  |  |  |  |  |  |

| 5          | VIC                | Digital Input  | Logic Input C                                                          |  |  |  |  |  |  |  |

| 6          | VOD                | Digital Output | Logic Output D                                                         |  |  |  |  |  |  |  |

| 7          | VE1                | Digital Input  | Output Enable for side 1. Active high logic input                      |  |  |  |  |  |  |  |

| 8          | GND1               | Power          | Ground 1. Ground reference for Isolator Side 1. <u>2</u> /, <u>4</u> / |  |  |  |  |  |  |  |

| 9          | GND2               | Power          | Ground 2. Ground reference for Isolator Side 2. <u>3/</u>              |  |  |  |  |  |  |  |

| 10         | VE2                | Digital Input  | Output Enable for side 2. Active high logic input                      |  |  |  |  |  |  |  |

| 11         | VID                | Digital Input  | Logic Input D.                                                         |  |  |  |  |  |  |  |

| 12         | VOC                | Digital Output | Logic Output C                                                         |  |  |  |  |  |  |  |

| 13         | VOB                | Digital Output | Logic Output B                                                         |  |  |  |  |  |  |  |

| 14         | VOA                | Digital Output | Logic Output A                                                         |  |  |  |  |  |  |  |

| 15         | GND2               | Power          | Ground 2. Ground reference for Isolator Side 2. <u>3</u> /             |  |  |  |  |  |  |  |

| 16         | VDD2               | Power          | Supply Voltage for Isolator Side 2 <u>1</u> /                          |  |  |  |  |  |  |  |

| Lid        |                    | Power          | Metal Lid electrically connected to ground (GND1)                      |  |  |  |  |  |  |  |

Figure 1 – Terminal Connections

<sup>1/</sup> Connect a ceramic bypass capacitor of value 0.01 µF to 0.1 µF between VDD1 (Pin 1) and GND1 (Pin 2), and between VDD2 (Pin 16) and GND2 (Pin 15) 2/ Pin 2 and Pin 8 are internally connected, and connecting both to GND1 is recommended.

3/ Pin 9 and Pin 15 are internally connected, and connecting both to GND2 is recommended.

4/ Internally connected to Metal Lid.

### 4.0 Specifications

### 4.1. Absolute Maximum Ratings 1/

| Supply voltage (V <sub>DD1</sub> , V <sub>DD2</sub> )                                                                      | -0.5V to 7.0V                               |

|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| Input voltage (V <sub>IA</sub> , V <sub>IB</sub> , V <sub>IC</sub> , V <sub>ID</sub> , V <sub>E1</sub> , V <sub>E2</sub> ) | -0.5V to $V_{DDI}$ + 0.5V $\underline{2}$ / |

| Output voltage (V <sub>OA</sub> , V <sub>OB</sub> , V <sub>OC</sub> , V <sub>OD</sub> )                                    | -0.5V to $V_{DDO}$ + 0.5V $\underline{2}$ / |

| Storage temperature range                                                                                                  | -65°C to +150°C                             |

| Output current per pin (I <sub>O1</sub> , I <sub>O2</sub> )                                                                | -10mA to +10mA                              |

| Junction temperature maximum (T <sub>J</sub> )                                                                             | +150°C                                      |

| Lead temperature (soldering, 60 seconds)                                                                                   | +300°C                                      |

| Thermal resistance, junction-to-case ( $\theta$ <sub>JC</sub> )                                                            | 72 °C/W <u>3</u> /                          |

| Thermal resistance, junction-to-ambient ( $\theta_{JA}$ )                                                                  | 162 °C/W <u>3</u> /                         |

| ESD Sensitivity (HBM)                                                                                                      | Class 2                                     |

|                                                                                                                            |                                             |

### 4.2. Recommended Operating Conditions

| Supply voltage (V <sub>DDI</sub> )                    | +1.8 V to +5.0 V |

|-------------------------------------------------------|------------------|

| Ambient operating temperature range (T <sub>A</sub> ) | -55°C to +125°C  |

### 4.3. Nominal Operating Performance Characteristics 4/

**Jitter**

| Peak-to-Peak                  | . 800ps         |

|-------------------------------|-----------------|

| RMS                           | . 190ps         |

| Capacitance (Input-to-Output) | 14pF <u>5</u> / |

| Input Capacitance             | 4pF <u>6</u> /  |

### 4.4. Radiation Features

Maximum total dose available (dose rate = 50 - 300 rads(Si)/s)......50k rads(Si)

Single event phenomenon (SEP):

No single event latchup (SEL) occurs at effective linear energy transfer (LET): ...... ≤ 80MeV-cm2/mg 7/

ASD0016568C | Page 3 of 21

<sup>1/</sup> Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions outside of those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

<sup>2/</sup> VDDI and VDDO refer to the supply voltages on the input and output sides of a given channel, respectively.

<sup>3/</sup> Measurement taken under absolute worst case condition and represent data taken with thermal camera for highest power density location. See MIL-STD-1835 for average OJC number.

<sup>4/</sup> All typical specifications are at TA =  $25^{\circ}$ C,  $3.6 \text{ V} \le \text{VDD1} \le 5. \text{ V}$ ,  $3.3 \text{ V} \le \text{VDD2} \le 5.0 \text{ V}$ , unless otherwise noted. Switching specifications are tested with CL = 15 pF and CMOS signal levels, unless otherwise noted.

<sup>5/</sup> The device is considered a 2-terminal device: Pin 1 through Pin 8 are shorted together and Pin 9 through Pin 16 are shorted together.

<sup>6/</sup> Input capacitance is from any input data pin to ground.

<sup>7/</sup> Limits are characterized at initial qualification and after any design or process changes that may affect the SEP characteristics, but are not production lot tested unless specified by the customer through the purchase order or contract. For more information on single event effect (SEE) test results, customers are requested to contact ADI. SEL test report is available on the external website: <a href="www.analog.com">www.analog.com</a>.

TABLE IA – ELECTRICAL PERFORMANCE CHARACTERISTICS - 5V OPERATION

| Parameter<br>See notes at end of table                   | Symbol                              | Condition<br>Unless otherw          |         | Sub-Group | Limit<br>Min | Limit<br>Max | Units |

|----------------------------------------------------------|-------------------------------------|-------------------------------------|---------|-----------|--------------|--------------|-------|

| SWITCHING CHARACTERISTICS                                | 5                                   |                                     |         |           |              |              |       |

| Data Rate <u>8</u> /                                     | DR                                  | Within PWD Limit                    |         | 9,10,11   |              | 150          | Mbps  |

| <u> </u>                                                 | 2                                   |                                     | D,P,L   | 9         |              | 150          |       |

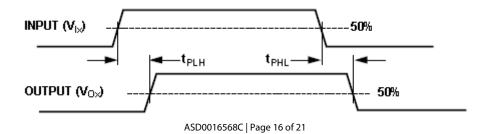

| Propagation Delay                                        | t <sub>PHL</sub> , t <sub>PLH</sub> | 50% input to 50%                    |         | 9         | 4.8          | 13.5         | ns    |

| 1, 1, 3, 1, 1, 1, 1,                                     | <b>,</b> <u>-</u>                   |                                     |         | 10        | 4.8          | 13.5         |       |

|                                                          |                                     |                                     |         | 11        | 4.2          | 13.5         |       |

|                                                          |                                     |                                     | D,P,L   | 9         | 4.8          | 13.5         |       |

| Pulse Width Distortion                                   | PWD                                 | t <sub>PLH</sub> - t <sub>PHL</sub> | •       | 9,10,11   |              | 3            | ns    |

|                                                          |                                     |                                     | D,P,L   | 9         |              | 3            |       |

| Pulse Width                                              | PW                                  | Within PWD limit                    | •       | 9,10,11   | 6.6          |              | ns    |

|                                                          |                                     |                                     | D,P,L   | 9         | 6.6          |              |       |

| Propagation Delay Skew 3/, 4/                            | <b>t</b> <sub>PSK</sub>             |                                     | •       | 9,10,11   |              | 6.1          | ns    |

| Pulse Width Distortion Change vs. Temperature <u>3</u> / | ΔPWD                                |                                     |         | 10,11     | -25          | 25           | ps/°C |

| Channel Matching                                         | t <sub>PSKCD</sub>                  |                                     |         | 9,10,11   |              | 3            | ns    |

| Codirection                                              | ◆i ⊃NCD                             |                                     | D,P,L   | 9         |              | 3            |       |

| Channel Matching                                         | t <sub>PSKOD</sub>                  |                                     | וט,ו ,ב | 9,10,11   |              | 3            | ns    |

| Opposing-Direction                                       | PSKOD                               |                                     | D,P,L   | 9         |              | 3            | 113   |

| Output Rise/Fall Time 2/,                                | t <sub>R</sub> /t <sub>F</sub>      | 10% to 90%                          | 0,1,72  | 9         |              | 4            | ns    |

| 3/                                                       | city ti                             | 1070 (0 3070                        |         | 10        |              | 4.5          | 113   |

| _                                                        |                                     |                                     |         | 11        |              | 3.5          |       |

| SUPPLY CURRENT                                           |                                     |                                     |         | 1         |              | 5.5          |       |

| Dynamic Supply Current                                   | I <sub>DD1(D)</sub>                 | F = 1MBPS                           |         | 4,5,6     |              | 10.3         | mA    |

| , , , , , , , , , , , , , , , , , , , ,                  |                                     |                                     | D,P,L   | 4         |              | 10.3         |       |

|                                                          |                                     | F = 25MBPS                          |         | 4,5,6     |              | 10.9         |       |

|                                                          |                                     |                                     | D,P,L   | 4         |              | 10.9         |       |

|                                                          |                                     | F = 100MBPS                         | •       | 4,5,6     |              | 15.9         |       |

|                                                          |                                     |                                     | D,P,L   | 4         |              | 15.9         |       |

|                                                          |                                     | F = 150MBPS                         |         | 4,5,6     |              | 17           |       |

|                                                          |                                     |                                     | D,P,L   | 4         |              | 17           |       |

|                                                          | I <sub>DD2(D)</sub>                 | F = 1MBPS                           |         | 4,5,6     |              | 6.85         |       |

|                                                          |                                     |                                     | D,P,L   | 4         |              | 6.85         |       |

|                                                          |                                     | F = 25MBPS                          | •       | 4,5,6     |              | 8.5          |       |

|                                                          |                                     |                                     | D,P,L   | 4         |              | 8.5          |       |

|                                                          |                                     | F = 100MBPS                         | •       | 4,5,6     |              | 14           |       |

|                                                          |                                     |                                     | D,P,L   | 4         |              | 14           |       |

|                                                          |                                     | F = 150MBPS                         |         | 4,5,6     |              | 17.5         |       |

|                                                          |                                     |                                     | D,P,L   | 4         |              | 17.5         |       |

| Quiescent Supply Current                                 | I <sub>DD1(Q)</sub>                 | $V_{lx} = 1 \ \underline{5}/$       |         | 1,2,3     |              | 2.46         | mA    |

|                                                          |                                     |                                     | D,P,L   | 1         |              | 2.46         |       |

|                                                          |                                     | $V_{lx} = 0$ <u>5</u> /             |         | 1,2,3     |              | 17           |       |

|                                                          |                                     |                                     | D,P,L   | 1         |              | 17           |       |

| Quiescent Supply                                         | $I_{DD2(Q)}$                        | $V_{1x} = 1 \frac{5}{}$             |         | 1,2,3     |              | 2.62         | mA    |

| Current                                                  |                                     |                                     | D,P,L   | 1         |              | 2.62         |       |

|                                                          |                                     | $V_{lx} = 0$ <u>5</u> /             |         | 1,2,3     |              | 10           |       |

|                                                          |                                     |                                     | D,P,L   | 1         |              | 10           |       |

ASD0016568C | Page 4 of 21

| Parameter<br>See notes at end of table | Symbol              | Condition<br>Unless otherw                                          |                                                     | Sub-Group | Limit<br>Min    | Limit<br>Max  | Units |

|----------------------------------------|---------------------|---------------------------------------------------------------------|-----------------------------------------------------|-----------|-----------------|---------------|-------|

| Logic High Input Threshold             | V <sub>IH</sub>     | <u>7</u> /                                                          |                                                     | 1,2,3     | $0.7 V_{DDx}$   |               | V     |

|                                        |                     |                                                                     | D,P,L                                               | 1         | $0.7 V_{DDx}$   |               |       |

| Logic Low Input Threshold              | $V_{IL}$            | <u>7</u> /                                                          |                                                     | 1,2,3     |                 | $0.3 V_{DDx}$ | V     |

|                                        |                     |                                                                     | D,P,L                                               | 1         |                 | $0.3 V_{DDx}$ |       |

| Logic High Output                      | $V_{OH}$            | $I_{Ox} = -20 \mu A$ , $V_{Ix} = V$                                 | / <sub>IxH</sub> <u>5</u> /, <u>6</u> /, <u>7</u> / | 1,2,3     | $V_{DDx} - 0.1$ |               | V     |

| Voltages                               |                     |                                                                     | D,P,L                                               | 1         | $V_{DDx} - 0.1$ |               |       |

|                                        |                     | $I_{Ox} = -4 \text{ mA, VIx} = 1$                                   | / <sub>IxH</sub> <u>5</u> /, <u>6</u> /, <u>7</u> / | 1,2,3     | $V_{DDx} - 0.4$ |               |       |

|                                        |                     |                                                                     | D,P,L                                               | 1         | $V_{DDx} - 0.4$ |               |       |

| Logic Low Output Voltages              | $V_{OL}$            | $I_{Ox} = 20 \mu A$ , $V_{Ix} = V_{Ix}$                             | ι <u>5</u> /, <u>6</u> /, <u>7</u> /                | 1,2,3     |                 | 0.1           | V     |

|                                        |                     |                                                                     | D,P,L                                               | 1         |                 | 0.1           |       |

|                                        |                     | $I_{Ox} = 4 \text{ mA}, V_{Ix} = V_{IxI}$                           | <u>5</u> /, <u>6</u> /, <u>7</u> /                  | 1,2,3     |                 | 0.4           |       |

|                                        |                     |                                                                     | D,P,L                                               | 1         |                 | 0.4           |       |

| Input Current per Channel              | I <sub>I</sub>      | $V_{lx} = V_{DDx}$ and $V_{lx} =$                                   | 0V <u>5</u> /, <u>6</u> /, <u>7</u> /               | 1,2,3     | -10             | +10           | μΑ    |

|                                        |                     |                                                                     | D,P,L                                               | 1         | -10             | +10           |       |

| Enable Pull-Up Current                 | $I_{PU}$            | $V_{Ex} = 0 \text{ V } \underline{10}/$                             |                                                     | 1,2,3     | -10             |               | μΑ    |

|                                        |                     |                                                                     | D,P,L                                               | 1         | -10             |               |       |

| Enable Pull-Down Current               | $I_{PD}$            | $V_{Ex} = V_{DDx} \ \underline{7}/,\underline{10}/$                 |                                                     | 1,2,3     |                 | 15            | μΑ    |

|                                        |                     |                                                                     | D,P,L                                               | 1         |                 | 15            |       |

| Tristate Output Current per            | loz                 | $0 \text{ V} \leq V_{\text{Ox}} \leq V_{\text{DDx}}  \underline{7}$ |                                                     | 1,2,3     | -10             | 10            | μΑ    |

| Channel                                |                     |                                                                     | D,P,L                                               | 1         | -20             | 20            |       |

| Undervoltage Lockout                   | $V_{\text{DDxUV+}}$ |                                                                     |                                                     | 1,2       |                 | 1.75          | V     |

| Positive VDDX Threshold                |                     |                                                                     |                                                     | 3         |                 | 1.71          |       |

|                                        |                     |                                                                     | D,P,L                                               | 1         |                 | 1.75          |       |

| Undervoltage Lockout                   | $V_{DDxUV}$         |                                                                     | -                                                   | 1,2,3     | 1.35            |               | V     |

| Negative VDDX Threshold                |                     |                                                                     | D,P,L                                               | 1         | 1.35            |               |       |

| Undervoltage Lockout                   | $V_{DDxUVH}$        |                                                                     |                                                     | 1,2,3     |                 | 0.4           | V     |

| VDDX Hysteresis                        |                     |                                                                     | D,P,L                                               | 1         |                 | 0.4           |       |

### TABLE IA NOTES:

- 1/ TA nom = 25°C, TA max = 125°C, and TA min = -55°C unless otherwise noted. Switching specifications are tested with CL = 15 pF, and CMOS signal levels, unless otherwise noted, VDDx nom = 5 V, VDDx max = 5.5V, VDDx min = 4.5V.

- 2/ Parameter is part of device initial characterization which is only repeated after design and process changes or with subsequent wafer lots.

- 3/ Parameter is not tested post irradiation

- 4/ tPSK is the magnitude of the worst-case difference in tPHL or tPLH that is measured between units at the same operating temperature, supply voltages, and output load within the recommended operating conditions.

- 5/ VIx refer to the input voltage.

- 6/ IOx refer to the output current of a given channel (A, B, C, or D).

- 7/ VDDx refers to the power supply on either side of a given channel (A, B, C, or D).

- 8/150 Mbps is the highest data rate that can be guaranteed, although higher data rates are possible

- 9/ Do not exceed VDDxnom where VDD1 = VDD2 = 5V at T = -55°C when all four channels are running in parallel. Device instability may occur.

- 10/  $V_{\text{Ex}}\!$  refers to  $V_{\text{E1}}$  and  $V_{\text{E2}}$

TABLE IB – ELECTRICAL PERFORMANCE CHARACTERISTICS – 3.3V OPERATION

| Parameter<br>See notes at end of table | Symbol                              | Conditions <u>1</u> /<br>Unless otherwise specified |                         | Sub-Group | Limit<br>Min | Limit<br>Max | Units |

|----------------------------------------|-------------------------------------|-----------------------------------------------------|-------------------------|-----------|--------------|--------------|-------|

| SWITCHING CHARACTERISTIC               | S                                   |                                                     |                         |           |              |              |       |

| Data Rate <u>8</u> /                   | DR                                  | Within PWD Limit                                    |                         | 9,10,11   |              | 150          | Mbps  |

|                                        |                                     |                                                     | D,P,L                   | 9         |              | 150          |       |

| Propagation Delay                      | t <sub>PHL</sub> , t <sub>PLH</sub> | 50% input to 50%                                    | 50% input to 50% output |           | 4            | 14           | ns    |

|                                        |                                     |                                                     |                         | 11        | 3.6          | 14           |       |

|                                        |                                     |                                                     | D,P,L                   | 9         | 4            | 14           |       |

ASD0016568C | Page 5 of 21

| Parameter See notes at end of table Un |                                |                                          | Conditions <u>1</u> /<br>Unless otherwise specified |         | Limit<br>Min    | Limit<br>Max         | Units |

|----------------------------------------|--------------------------------|------------------------------------------|-----------------------------------------------------|---------|-----------------|----------------------|-------|

| Pulse Width Distortion                 | PWD                            | t <sub>PLH</sub> - t <sub>PHL</sub>      |                                                     | 9,10,11 |                 | 3                    | ns    |

|                                        |                                |                                          | D,P,L                                               | 9       |                 | 3                    |       |

| Pulse Width                            | PW                             | Within PWD limit                         |                                                     | 9,10,11 | 6.6             |                      | ns    |

|                                        |                                |                                          | D,P,L                                               | 9       | 6.6             |                      |       |

| Propagation Delay Skew                 | t <sub>PSK</sub>               |                                          |                                                     | 9,10,11 |                 | 7.5                  | ns    |

| <u>3</u> /, <u>4</u> /                 |                                |                                          |                                                     |         |                 |                      |       |

| Pulse Width Distortion                 | $\Delta$ PWD                   |                                          |                                                     | 10,11   | -25             | 25                   | ps/°C |

| Change vs. Temperature <u>3</u> /      |                                |                                          |                                                     |         |                 |                      |       |

| Channel Matching                       | <b>t</b> PSKCD                 |                                          |                                                     | 9,10,11 |                 | 3                    | ns    |

| Codirection                            |                                |                                          | D,P,L                                               | 9       |                 | 3                    |       |

| Channel Matching                       | <b>t</b> PSKOD                 |                                          |                                                     | 9,10,11 |                 | 3                    | ns    |

| Opposing-Direction                     |                                |                                          | D,P,L                                               | 9       |                 | 3                    |       |

| Output Rise/Fall Time 2/,              | t <sub>R</sub> /t <sub>F</sub> | 10% to 90%                               |                                                     | 9       |                 | 4                    | ns    |

| <u> </u>                               | ,                              |                                          |                                                     | 10      |                 | 4.5                  |       |

|                                        |                                |                                          |                                                     | 11      |                 | 3.5                  |       |

| SUPPLY CURRENT                         |                                |                                          |                                                     |         |                 |                      |       |

| Dynamic Supply Current                 | I <sub>DD1(D)</sub>            | F = 1MBPS                                |                                                     | 4,5,6   |                 | 10.1                 | mA    |

|                                        |                                |                                          | D,P,L                                               | 4       |                 | 10.1                 |       |

|                                        |                                | F = 25MBPS                               |                                                     | 4,5,6   |                 | 10.5                 |       |

|                                        |                                |                                          | D,P,L                                               | 4       |                 | 10.5                 |       |

|                                        |                                | F = 100MBPS                              |                                                     | 4,5,6   |                 | 14.9                 |       |

|                                        |                                |                                          | D,P,L                                               | 4       |                 | 14.9                 |       |

|                                        |                                | F = 150MBPS                              |                                                     | 4,5,6   |                 | 14.9                 |       |

|                                        |                                |                                          | D,P,L                                               | 4       |                 | 14.9                 |       |

|                                        | I <sub>DD2(D)</sub>            | F = 1MBPS                                |                                                     | 4,5,6   |                 | 6.65                 |       |

|                                        |                                |                                          | D,P,L                                               | 4       |                 | 6.65                 |       |

|                                        |                                | F = 25MBPS                               |                                                     | 4,5,6   |                 | 8                    |       |

|                                        |                                |                                          | D,P,L                                               | 4       |                 | 8                    |       |

|                                        |                                | F = 100MBPS                              |                                                     | 4,5,6   |                 | 12.8                 |       |

|                                        |                                |                                          | D,P,L                                               | 4       |                 | 12.8                 |       |

|                                        |                                | F = 150MBPS                              |                                                     | 4,5,6   |                 | 14.5                 |       |

|                                        |                                |                                          | D,P,L                                               | 4       |                 | 14.5                 |       |

| Quiescent Supply Current               | I <sub>DD1(Q)</sub>            | V <sub>Ix</sub> = 1 <u>5</u> /           |                                                     | 1,2,3   |                 | 2.36                 | mA    |

| ·                                      |                                |                                          | D,P,L                                               | 1       |                 | 2.36                 |       |

|                                        |                                | $V_{lx} = 0 \ \underline{5}/$            |                                                     | 1,2,3   |                 | 16.7                 |       |

|                                        |                                |                                          | D,P,L                                               | 1       |                 | 16.7                 |       |

| Quiescent Supply                       | I <sub>DD2(Q)</sub>            | $V_{1x} = 1 \ \underline{5}/$            |                                                     | 1,2,3   |                 | 2.52                 | mA    |

| Current                                |                                |                                          | D,P,L                                               | 1       |                 | 2.52                 |       |

|                                        |                                | $V_{lx} = 0 \ \underline{5}/$            |                                                     | 1,2,3   |                 | 9.7                  |       |

|                                        |                                |                                          | D,P,L                                               | 1       |                 | 9.7                  |       |

| OC CHARACTERISTICS                     |                                |                                          |                                                     |         |                 |                      |       |

| Logic High Input Threshold             | $V_{IH}$                       | <u>Z</u> /                               |                                                     | 1,2,3   | $0.7 V_{DDx}$   |                      | V     |

|                                        |                                |                                          | D,P,L                                               | 1       | $0.7 V_{DDx}$   |                      |       |

| Logic Low Input Threshold              | $V_{IL}$                       | <u>7</u> /                               |                                                     | 1,2,3   |                 | $0.3 V_{DDx}$        | V     |

|                                        |                                |                                          | D,P,L                                               | 1       |                 | $0.3 V_{\text{DDx}}$ |       |

| Logic High Output                      | $V_{OH}$                       | $I_{Ox} = -20 \mu A$ , $V_{Ix} = V_{Ix}$ | V <sub>іхн</sub> <u>5</u> /, <u>6</u> /, <u>7</u> / | 1,2,3   | $V_{DDx} - 0.1$ |                      | V     |

| /oltages                               |                                |                                          | D,P,L                                               | 1       | $V_{DDx} - 0.1$ |                      |       |

|                                        |                                | $I_{Ox} = -4 \text{ mA, VIx} = 1$        | V <sub>IxH</sub> <u>5</u> /, <u>6</u> /, <u>7</u> / | 1,2,3   | $V_{DDx} - 0.4$ |                      |       |

|                                        |                                |                                          | D,P,L                                               | 1       | $V_{DDx} - 0.4$ |                      |       |

| Logic Low Output Voltages              | Vol                            | $I_{Ox} = 20 \ \mu A, V_{Ix} = V_{Ix}$   | xL <u>5</u> /, <u>6</u> /, <u>7</u> /               | 1,2,3   |                 | 0.1                  | V     |

|                                        |                                |                                          | D,P,L                                               | 1       |                 | 0.1                  |       |

|                                        |                                | $I_{Ox} = 4 \text{ mA}, V_{Ix} = V_{Ix}$ | 5/6/7/                                              | 1,2,3   |                 | 0.4                  |       |

ASD0016568C | Page 6 of 21

| Parameter<br>See notes at end of table | Symbol                     | Condition Unless otherw                                             | _                                     | Sub-Group | Limit<br>Min | Limit<br>Max | Units |

|----------------------------------------|----------------------------|---------------------------------------------------------------------|---------------------------------------|-----------|--------------|--------------|-------|

|                                        |                            |                                                                     | D,P,L                                 | 1         |              | 0.4          |       |

| Input Current per Channel              | lı                         | $V_{lx} = V_{DDx}$ and $V_{lx} =$                                   | 0V <u>5</u> /, <u>6</u> /, <u>7</u> / | 1,2,3     | -10          | +10          | μΑ    |

|                                        |                            |                                                                     | D,P,L                                 | 1         | -10          | +10          |       |

| Enable Pull-Up Current                 | I <sub>PU</sub>            | $V_{Ex} = 0 \text{ V } 9/$                                          |                                       | 1,2,3     | -10          |              | μΑ    |

|                                        |                            |                                                                     | D,P,L                                 | 1         | -10          |              |       |

| Enable Pull-Down Current               | I <sub>PD</sub>            | $V_{Ex} = V_{DDx} \frac{7}{,9}$                                     |                                       | 1,2,3     |              | 15           | μΑ    |

|                                        |                            |                                                                     | D,P,L                                 | 1         |              | 15           |       |

| Tristate Output Current per            | loz                        | $0 \text{ V} \leq V_{\text{Ox}} \leq V_{\text{DDx}}  \underline{7}$ | <i>'</i> .                            | 1,2,3     | -10          | 10           | μΑ    |

| Channel                                |                            |                                                                     | D,P,L                                 | 1         | -20          | 20           |       |

| Undervoltage Lockout                   | $V_{\text{DDxUV}+}$        |                                                                     |                                       | 1,2       |              | 1.75         | V     |

| Positive VDDX Threshold                |                            |                                                                     |                                       | 3         |              | 1.71         |       |

|                                        |                            |                                                                     | D,P,L                                 | 1         |              | 1.75         |       |

| Undervoltage Lockout                   | $V_{\text{DD} \text{xUV}}$ |                                                                     |                                       | 1,2,3     | 1.35         |              | V     |

| Negative VDDX Threshold                |                            |                                                                     | D,P,L                                 | 1         | 1.35         |              |       |

| Undervoltage Lockout                   | $V_{DDxUVH}$               |                                                                     |                                       | 1,2,3     |              | 0.4          | V     |

| VDDX Hysteresis                        |                            |                                                                     | D,P,L                                 | 1         |              | 0.4          |       |

### TABLE IB NOTES:

- 1/ TA nom = 25°C, TA max = 125°C, and TA min = -55°C unless otherwise noted. Switching specifications are tested with CL = 15 pF, and CMOS signal levels, unless otherwise noted. VDDx nom = 3.3 V, VDDx max = 3.6V, VDDx min = 3V

- 2/ Parameter is part of device initial characterization which is only repeated after design and process changes or with subsequent wafer lots.

- 3/ Parameter is not tested post irradiation

- 4/ tPSK is the magnitude of the worst-case difference in tPHL or tPLH that is measured between units at the same operating temperature, supply voltages, and output load within the recommended operating conditions.

- 5/ VIx refer to the input voltage.

- 6/ IOx refer to the output current of a given channel (A, B, C, or D).

- 7/ VDDx refers to the power supply on either side of a given channel (A, B, C, or D).

- 8/150 Mbps is the highest data rate that can be guaranteed, although higher data rates are possible.

- 9/  $V_{\text{Ex}}$  refers to  $V_{\text{E1}}$  and  $V_{\text{E2}}$

TABLE IC - ELECTRICAL PERFORMANCE CHARACTERISTICS - 2.5V OPERATION

| Parameter<br>See notes at end of table | Symbol                              | Conditions <u>1</u> /<br>Unless otherwise specified |        | Sub-Group | Limit<br>Min | Limit<br>Max | Units |

|----------------------------------------|-------------------------------------|-----------------------------------------------------|--------|-----------|--------------|--------------|-------|

| SWITCHING CHARACTERISTICS              | 5                                   |                                                     |        |           |              |              |       |

| Data Rate <u>8</u> /                   | DR                                  | Within PWD Limit                                    |        | 9,10,11   |              | 150          | Mbps  |

|                                        |                                     |                                                     | D,P,L  | 9         |              | 150          |       |

| Propagation Delay                      | t <sub>PHL</sub> , t <sub>PLH</sub> | 50% input to 50%                                    | output | 9         | 4.7          | 14           | ns    |

|                                        |                                     |                                                     |        | 10        | 4.7          | 14           |       |

|                                        |                                     |                                                     |        | 11        | 4            | 14           |       |

|                                        |                                     |                                                     | D,P,L  | 9         | 4.7          | 14           |       |

| Pulse Width Distortion                 | PWD                                 | tplh - tphl                                         |        | 9,10,11   |              | 3            | ns    |

|                                        |                                     |                                                     | D,P,L  | 9         |              | 3            |       |

| Pulse Width                            | PW                                  | Within PWD limit                                    |        | 9,10,11   | 6.6          |              | ns    |

|                                        |                                     |                                                     | D,P,L  | 9         | 6.6          |              |       |

| Propagation Delay Skew                 | t <sub>PSK</sub>                    |                                                     |        | 9,10,11   |              | 6.8          | ns    |

| <u>3</u> /, <u>4</u> /                 |                                     |                                                     |        |           |              |              |       |

| Pulse Width Distortion                 | $\Delta$ PWD                        |                                                     |        | 10,11     | -25          | 25           | ps/°C |

| Change vs. Temperature <u>3</u> /      |                                     |                                                     |        |           |              |              |       |

| Channel Matching                       | <b>t</b> PSKCD                      |                                                     |        | 9,10,11   |              | 3            | ns    |

| Codirection                            |                                     |                                                     | D,P,L  | 9         |              | 3            |       |

| Channel Matching                       | <b>t</b> PSKOD                      |                                                     |        | 9,10,11   |              | 3            | ns    |

| Opposing-Direction                     |                                     |                                                     | D,P,L  | 9         |              | 3            |       |

ASD0016568C | Page 7 of 21

| Parameter<br>See notes at end of table | Symbol                |                                                      | tions <u>1</u> /<br>wise specified | Sub-Group | Limit<br>Min           | Limit<br>Max         | Units |

|----------------------------------------|-----------------------|------------------------------------------------------|------------------------------------|-----------|------------------------|----------------------|-------|

| Output Rise/Fall Time 2/,              | $t_{\rm R}/t_{\rm F}$ | 10% to 90%                                           |                                    | 9         |                        | 4                    | ns    |

| <u>3</u> /                             |                       |                                                      |                                    | 10        |                        | 4.5                  |       |

|                                        |                       |                                                      |                                    | 11        |                        | 3.5                  |       |

| SUPPLY CURRENT                         |                       |                                                      |                                    |           |                        |                      |       |

| Dynamic Supply Current                 | $I_{DD1(D)}$          | F = 1MBPS                                            |                                    | 4, 5, 6   |                        | 10                   | mA    |

|                                        |                       |                                                      | D,P,L                              | 4         |                        | 10                   |       |

|                                        |                       | F = 25MBPS                                           |                                    | 4, 5, 6   |                        | 10.4                 |       |

|                                        |                       |                                                      | D,P,L                              | 4         |                        | 10.4                 |       |

|                                        |                       | F = 100MBPS                                          |                                    | 4, 5, 6   |                        | 14.5                 |       |

|                                        |                       |                                                      | D,P,L                              | 4         |                        | 14.5                 |       |

|                                        |                       | F = 150MBPS                                          |                                    | 4, 5, 6   |                        | 14.5                 |       |

|                                        |                       |                                                      | D,P,L                              | 4         |                        | 14.5                 |       |

|                                        | $I_{DD2(D)}$          | F = 1MBPS                                            |                                    | 4,5,6     |                        | 6.55                 |       |

|                                        |                       |                                                      | D,P,L                              | 4         |                        | 6.55                 |       |

|                                        |                       | F = 25MBPS                                           | •                                  | 4,5,6     |                        | 7.7                  |       |

|                                        |                       |                                                      | D,P,L                              | 4         |                        | 7.7                  |       |

|                                        |                       | F = 100MBPS                                          |                                    | 4,5,6     |                        | 11.5                 |       |

|                                        |                       |                                                      | D,P,L                              | 4         |                        | 11.5                 |       |

|                                        |                       | F = 150MBPS                                          |                                    | 4, 5, 6   |                        | 13                   |       |

|                                        |                       |                                                      | D,P,L                              | 4         |                        | 13                   |       |

| Quiescent Supply Current               | I <sub>DD1(Q)</sub>   | $V_{lx} = 1 \frac{5}{}$                              |                                    | 1,2,3     |                        | 2.32                 | mA    |

| 117                                    |                       | _                                                    | D,P,L                              | 1         |                        | 2.32                 |       |

|                                        |                       | $V_{1x} = 0 \frac{5}{}$                              | 1-,,                               | 1,2,3     |                        | 16.6                 |       |

|                                        |                       |                                                      | D,P,L                              | 1         |                        | 16.6                 |       |

| Quiescent Supply                       | I <sub>DD2(Q)</sub>   | V <sub>Ix</sub> = 1 <u>5</u> /                       | 1-,,                               | 1,2,3     |                        | 2.47                 | mA    |

| Current                                | (-)                   | _                                                    | D,P,L                              | 1         |                        | 2.47                 |       |

|                                        |                       | $V_{lx} = 0 \ \underline{5}/$                        | 1-,,                               | 1,2,3     |                        | 9.67                 |       |

|                                        |                       | _                                                    | D,P,L                              | 1         |                        | 9.67                 |       |

| DC CHARACTERISTICS                     |                       |                                                      |                                    | 1         | 1                      | l.                   |       |

| Logic High Input Threshold             | V <sub>IH</sub>       | 7/                                                   |                                    | 1,2,3     | $0.7 V_{DDx}$          |                      | V     |

|                                        |                       |                                                      | D,P,L                              | 1         | 0.7 V <sub>DDx</sub>   |                      |       |

| Logic Low Input Threshold              | V <sub>IL</sub>       | 7/                                                   | •                                  | 1,2,3     |                        | $0.3 V_{DDx}$        | V     |

|                                        |                       |                                                      | D,P,L                              | 1         |                        | 0.3 V <sub>DDx</sub> |       |

| Logic High Output                      | V <sub>OH</sub>       | $I_{0x} = -20 \mu A, V_{1x} =$                       |                                    | 1,2,3     | $V_{DDx} - 0.1$        |                      | V     |

| Voltages .                             |                       | , ,                                                  | D,P,L                              | 1         | V <sub>DDx</sub> - 0.1 |                      |       |

|                                        |                       | $I_{Ox} = -4 \text{ mA, VIx} =$                      |                                    | 1,2,3     | $V_{DDx} - 0.4$        |                      |       |

|                                        |                       |                                                      | D,P,L                              | 1         | $V_{DDx} - 0.4$        |                      |       |

| Logic Low Output Voltages              | V <sub>OL</sub>       | $I_{Ox} = 20 \mu A, V_{Ix} = V$                      |                                    | 1,2,3     | V DDX O.1              | 0.1                  | V     |

| Logic Low Output Voltages              | ₹ OL                  | Ιοχ 20 μπ, τιχ τ                                     | D,P,L                              | 1         |                        | 0.1                  | •     |

|                                        |                       | $I_{Ox} = 4 \text{ mA, } V_{Ix} = V$                 |                                    | 1,2,3     |                        | 0.4                  |       |

|                                        |                       |                                                      | D,P,L                              | 1,2,3     |                        | 0.4                  |       |

| Input Current per Channel              | l <sub>1</sub>        | $V_{lx} = V_{DDx}$ and $V_{lx} = V_{DDx}$            |                                    | 1,2,3     | -10                    | +10                  | μΑ    |

| input current per chariller            | "                     | VIA — VIDDX GITG VIX -                               | D,P,L                              | 1,2,3     | -10                    | +10                  | μ/ ι  |

| Enable Pull-Up Current                 | I <sub>PU</sub>       | V <sub>Ex</sub> = 0 V <u>9</u> /                     | U,i ,L                             | 1,2,3     | -10                    | 110                  | μΑ    |

| Enable Fall op Cullelle                | IPU                   | - EX = 5 V 2/                                        | D,P,L                              | 1,2,3     | -10                    |                      | μΛ    |

| Enable Pull-Down Current               | I <sub>PD</sub>       | $V_{Ex} = V_{DDx} \ \underline{7/,9}/$               | D,1 ,L                             | 1,2,3     | 10                     | 15                   | μΑ    |

| LIMBICT AII DOWN CANTEIL               | טאו                   | • EX — • DUX <u>11,21</u>                            | D,P,L                              | 1,2,3     |                        | 15                   | μ۱    |

| Tristate Output Current per            | loz                   | $0 \text{ V} \leq V_{\text{Ox}} \leq V_{\text{DDx}}$ |                                    | 1,2,3     | -10                    | 10                   | μΑ    |

| Channel                                | 102                   | U V = VUX = VDDX                                     | <i>D</i> ,P,L                      | 1,2,3     | -10                    | 20                   | μΑ    |

| Undervoltage Lockout                   | $V_{DDxUV+}$          |                                                      | D,F,L                              |           | -20                    | 1.75                 | V     |

| Positive VDDX Threshold                | <b>V</b> DDxUV+       |                                                      |                                    | 1,2<br>3  |                        | 1.75                 | V     |

| I OPITIAE ADDV HILESHOID               |                       |                                                      | D,P,L                              | 1         |                        |                      |       |

|                                        |                       |                                                      | U,F,L                              | I         | 1                      | 1.75                 |       |

ASD0016568C | Page 8 of 21

| Parameter<br>See notes at end of table | Symbol       | Conditions <u>1</u> /<br>Unless otherwise specified | Sub-Group | Limit<br>Min | Limit<br>Max | Units |

|----------------------------------------|--------------|-----------------------------------------------------|-----------|--------------|--------------|-------|

| Undervoltage Lockout                   | $V_{DDxUV}$  |                                                     | 1,2,3     | 1.35         |              | V     |

| Negative VDDX Threshold                |              | D,P,L                                               | 1         | 1.35         |              |       |

| Undervoltage Lockout                   | $V_{DDxUVH}$ |                                                     | 1,2,3     |              | 0.4          | V     |

| VDDX Hysteresis                        |              | D,P,L                                               | 1         |              | 0.4          |       |

#### TABLE IC NOTES:

- 1/TA nom =  $25^{\circ}C$ , TA max =  $125^{\circ}C$ , and TA min =  $-55^{\circ}C$  unless otherwise noted. Switching specifications are tested with CL = 15 pF, and CMOS signal levels, unless otherwise noted. VDDx nom = 2.5 V, VDDx max = 2.75V, VDDx min = 2.25V

- 2/ Parameter is part of device initial characterization which is only repeated after design and process changes or with subsequent wafer lots.

- 3/ Parameter is not tested post irradiation

- 4/ tPSK is the magnitude of the worst-case difference in tPHL or tPLH that is measured between units at the same operating temperature, supply voltages, and output load within the recommended operating conditions.

- 5/ VIx refer to the input voltage.

- 6/ IOx refer to the output current of a given channel (A, B, C, or D).

- 7/ VDDx refers to the power supply on either side of a given channel (A, B, C, or D).

- 8/ 150 Mbps is the highest data rate that can be guaranteed, although higher data rates are possible

- 9/  $V_{\text{Ex}}$  refers to  $V_{\text{E1}}$  and  $V_{\text{E2}}$

TABLE ID - ELECTRICAL PERFORMANCE CHARACTERISTICS -1.8V OPERATION

| Parameter<br>See notes at end of table                      | Symbol                              | Condition Unless otherw             |        | Sub-Group | Limit<br>Min | Limit<br>Max | Units |

|-------------------------------------------------------------|-------------------------------------|-------------------------------------|--------|-----------|--------------|--------------|-------|

| SWITCHING CHARACTERISTICS                                   | 5                                   |                                     |        |           |              |              |       |

| Data Rate <u>8</u> /                                        | DR                                  | Within PWD Limit                    |        | 9,10,11   |              | 150          | Mbps  |

| <u> </u>                                                    |                                     |                                     | D,P,L  | 9         |              | 150          | ·     |

| Propagation Delay                                           | t <sub>PHL</sub> , t <sub>PLH</sub> | 50% input to 50%                    | output | 9         | 4.8          | 15           | ns    |

|                                                             |                                     |                                     |        | 10        | 5.8          | 15           |       |

|                                                             |                                     |                                     |        | 11        | 5.4          | 15           |       |

|                                                             |                                     |                                     | D,P,L  | 9         | 4.8          | 15           |       |

| Pulse Width Distortion                                      | PWD                                 | t <sub>PLH</sub> - t <sub>PHL</sub> |        | 9,10,11   |              | 3            | ns    |

|                                                             |                                     |                                     | D,P,L  | 9         |              | 3            |       |

| Pulse Width                                                 | PW                                  | Within PWD limit                    |        | 9,10,11   | 6.6          |              | ns    |

|                                                             |                                     |                                     | D,P,L  | 9         | 6.6          |              |       |

| Propagation Delay Skew <u>3</u> /, <u>4</u> /               | t <sub>PSK</sub>                    |                                     |        | 9,10,11   |              | 7.0          | ns    |

| Pulse Width Distortion<br>Change vs. Temperature <u>3</u> / | ΔPWD                                |                                     |        | 10,11     | -25          | 25           | ps/°C |

| Channel Matching                                            | t <sub>PSKCD</sub>                  |                                     |        | 9,10,11   |              | 3            | ns    |

| Codirection                                                 |                                     |                                     | D,P,L  | 9         |              | 3            |       |

| Channel Matching                                            | <b>t</b> <sub>PSKOD</sub>           |                                     |        | 9,10,11   |              | 3            | ns    |

| Opposing-Direction                                          |                                     |                                     | D,P,L  | 9         |              | 3            |       |

| Output Rise/Fall Time 2/,                                   | t <sub>R</sub> /t <sub>F</sub>      | 10% to 90%                          | 1      | 9         |              | 4            | ns    |

| <u>.                                    </u>                |                                     |                                     |        | 10        |              | 4.5          |       |

|                                                             |                                     |                                     |        | 11        |              | 3.5          |       |

| SUPPLY CURRENT                                              |                                     |                                     |        |           |              |              |       |

| Dynamic Supply Current                                      | I <sub>DD1(D)</sub>                 | F = 1MBPS                           |        | 4, 5, 6   |              | 9.1          | mA    |

|                                                             |                                     |                                     | D,P,L  | 4         |              | 9.1          |       |

|                                                             |                                     | F = 25MBPS                          |        | 4, 5, 6   |              | 10           |       |

|                                                             |                                     |                                     | D,P,L  | 4         |              | 10           |       |

|                                                             |                                     | F = 100MBPS                         |        | 4, 5, 6   |              | 14           |       |

|                                                             |                                     |                                     | D,P,L  | 4         |              | 14           |       |

|                                                             |                                     | F = 150MBPS                         |        | 4, 5, 6   |              | 14           |       |

|                                                             |                                     |                                     | D,P,L  | 4         |              | 14           |       |

ASD0016568C | Page 9 of 21

| Parameter<br>See notes at end of table | Symbol              |                                                      | tions <u>1</u> /<br>wise specified | Sub-Group | Limit<br>Min         | Limit<br>Max         | Units |

|----------------------------------------|---------------------|------------------------------------------------------|------------------------------------|-----------|----------------------|----------------------|-------|

|                                        | I <sub>DD2(D)</sub> | F = 1MBPS                                            |                                    | 4, 5, 6   |                      | 6.45                 |       |

|                                        |                     |                                                      | D,P,L                              | 4         |                      | 6.45                 |       |

|                                        |                     | F = 25MBPS                                           |                                    | 4, 5, 6   |                      | 7.5                  |       |

|                                        |                     |                                                      | D,P,L                              | 4         |                      | 7.5                  |       |

|                                        |                     | F = 100MBPS                                          |                                    | 4, 5, 6   |                      | 11.2                 |       |

|                                        |                     |                                                      | D,P,L                              | 4         |                      | 11.2                 |       |

|                                        |                     | F = 150MBPS                                          |                                    | 4, 5, 6   |                      | 13                   |       |

|                                        |                     |                                                      | D,P,L                              | 4         |                      | 13                   |       |

| Quiescent Supply Current               | I <sub>DD1(Q)</sub> | $V_{1x} = 1 \ \underline{5}/$                        |                                    | 1,2,3     |                      | 2.28                 | mA    |

|                                        |                     |                                                      | D,P,L                              | 1         |                      | 2.28                 |       |

|                                        |                     | $V_{1x} = 0 \ \underline{5}/$                        |                                    | 1,2,3     |                      | 16.5                 |       |

|                                        |                     |                                                      | D,P,L                              | 1         |                      | 16.5                 |       |

| Quiescent Supply                       | I <sub>DD2(Q)</sub> | $V_{1x} = 1 \ \underline{5}/$                        |                                    | 1,2,3     |                      | 2.45                 | mA    |

| Current                                |                     |                                                      | D,P,L                              | 1         |                      | 2.45                 |       |

|                                        |                     | $V_{1x} = 0 \ \underline{5}/$                        | •                                  | 1,2,3     |                      | 9.6                  |       |

|                                        |                     | _                                                    | D,P,L                              | 1         |                      | 9.6                  |       |

| DC CHARACTERISTICS                     | I.                  |                                                      |                                    | •         |                      | Į.                   |       |

| Logic High Input Threshold             | V <sub>IH</sub>     | <u>7</u> /                                           |                                    | 1,2,3     | $0.7 V_{DDx}$        |                      | V     |

|                                        |                     | _                                                    | D,P,L                              | 1         | 0.7 V <sub>DDx</sub> |                      |       |

| Logic Low Input Threshold              | V <sub>IL</sub>     | <u>7</u> /                                           | 1-,,                               | 1,2,3     |                      | 0.3 V <sub>DDx</sub> | V     |

|                                        | - "-                |                                                      | D,P,L                              | 1         |                      | 0.3 V <sub>DDx</sub> | -     |

| Logic High Output                      | V <sub>OH</sub>     | $I_{Ox} = -20 \mu A, V_{Ix} =$                       |                                    | 1,2,3     | $V_{DDx} - 0.1$      | CIO I DDX            | V     |

| Voltages                               | VOIT                | 20 p/ ( 1)                                           | D,P,L                              | 1         |                      |                      | •     |