Distributed by:

JAMECO

ELECTRONICS

# www.Jameco.com + 1-800-831-4242

The content and copyrights of the attached material are the property of its owner.

Jameco Part Number 1734321

# Micropower, 600kHz PWM DC/DC Converters

#### **FEATURES**

- 100µA Quiescent Current

- Operates with V<sub>IN</sub> as Low as 1.5V

- 600kHz Fixed Frequency Operation

- Starts into Full Load

- Low-Battery Detector Active in Shutdown

- Automatic Burst Mode Operation at Light Load (LT1317)

- Continuous Switching at Light Loads (LT1317B)

- Low V<sub>CFSAT</sub> Switch: 300mV at 500mA

- Pin for Pin Compatible with the LT1307/LT1307B

#### **APPLICATIONS**

- Cellular Telephones

- Cordless Telephones

- Pagers

- GPS Receivers

- Battery Backup

- Portable Electronic Equipment

- Glucose Meters

- Diagnostic Medical Instrumentation

# DESCRIPTION

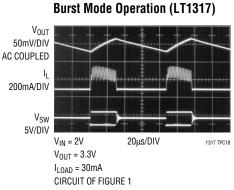

The LT®1317/LT1317B are micropower, fixed frequency step-up DC/DC converters that operate over a wide input voltage range of 1.5V to 12V. The LT1317 features automatic shifting to power saving Burst Mode  $^{\text{TM}}$  operation at light loads. High efficiency is maintained over a broad 300 $\mu$ A to 200mA load range. Peak switch current during Burst Mode operation is kept below 250mA for most operating conditions which results in low output ripple voltage, even at high input voltages. The LT1317B does not shift into Burst Mode operation at light loads, eliminating low frequency output ripple at the expense of light load efficiency.

The LT1317/LT1317B contain an internal low-battery detector with a 200mV reference that stays alive when the device goes into shutdown.

No-load quiescent current of the LT1317 is  $100\mu A$  and shuts down to  $30\mu A$ . The internal NPN power switch handles a 500mA current with a voltage drop of just 300mV.

The LT1317/LT1317B are available in MS8 and SO-8 packages.

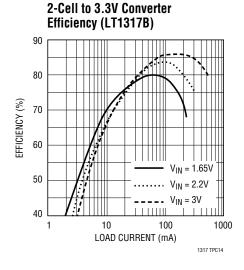

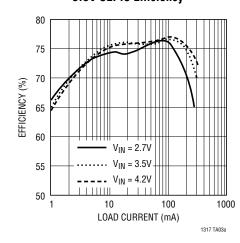

2-Cell to 3.3V Converter Efficiency

**7.** LTC and LT are registered trademarks of Linear Technology Corporation. Burst Mode is a trademark of Linear Technology Corporation.

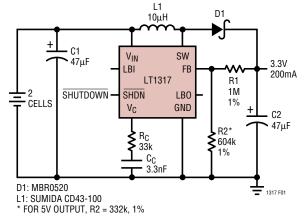

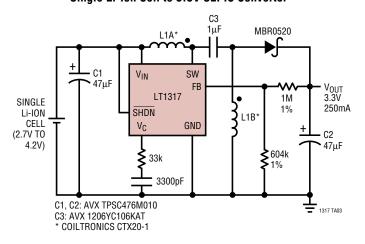

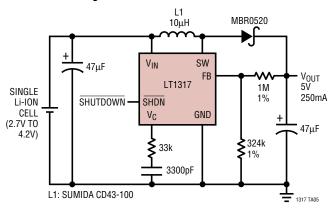

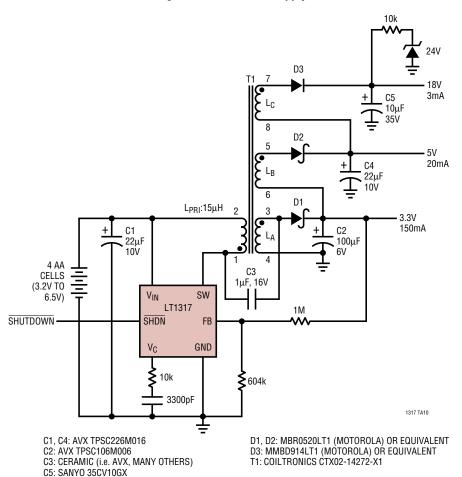

# TYPICAL APPLICATION

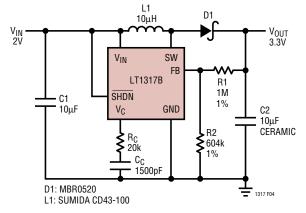

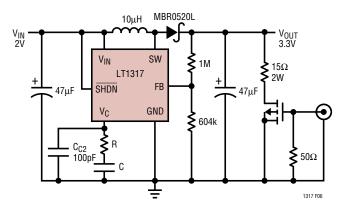

Figure 1. 2-Cell to 3.3V Boost Converter

# 90 2.2V<sub>IN</sub> 3V<sub>IN</sub> 3V<sub>IN</sub> 60 1.65V<sub>IN</sub> 50 LOAD CURRENT (mA)

# **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| V <sub>IN</sub> , LBO Voltage | 12V                     |

|-------------------------------|-------------------------|

| SW Voltage                    |                         |

| FB Voltage                    | $V_{IN} + 0.3V$         |

| V <sub>C</sub> Voltage        | 2V                      |

| LBI Voltage                   | $0V \le V_{LBI} \le 1V$ |

| SHDN Voltage                  | 6V                      |

| Junction Temperature                |         | 125°C                 |

|-------------------------------------|---------|-----------------------|

| Operating Temperature Range         |         |                       |

| Commercial                          | 0°C t   | o 70°C                |

| Industrial                          | 40°C t  | o 85°C                |

| Storage Temperature Range           | 65°C to | 150°C                 |

| Lead Temperature (Soldering, 10 sec | )       | $300^{\circ}\text{C}$ |

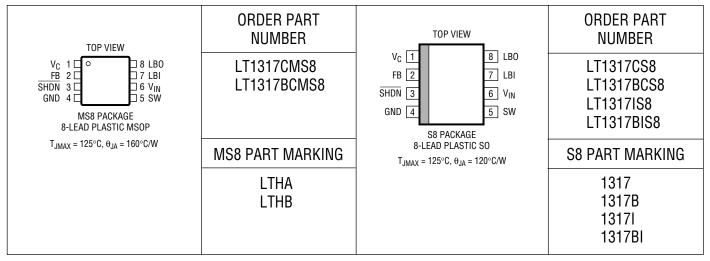

# PACKAGE/ORDER INFORMATION

Consult factory for Military grade parts.

# **ELECTRICAL CHARACTERISTICS**

Commercial Grade  $V_{IN} = 2V$ ,  $V_{\overline{SHDN}} = 2V$ ,  $T_A = 25$ °C, unless otherwise noted.

| SYMBOL           | PARAMETER                                 | CONDITIONS                                                                                           |   | MIN          | TYP          | MAX          | UNITS    |

|------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------|---|--------------|--------------|--------------|----------|

| ΙQ               | Quiescent Current                         | Not Switching, V <sub>SHDN</sub> = 2V (LT1317)<br>V <sub>SHDN</sub> = 0V (LT1317/LT1317B)            | • |              | 100<br>25    | 160<br>40    | μA<br>μA |

|                  |                                           | $V_{\overline{SHDN}} = 2V$ , Switching (LT1317B)<br>$V_{\overline{SHDN}} = 2V$ , Switching (LT1317B) | • |              | 4.8          | 6.5<br>7.5   | mA<br>mA |

| $V_{FB}$         | Feedback Voltage                          |                                                                                                      | • | 1.22<br>1.20 | 1.24<br>1.24 | 1.26<br>1.26 | V        |

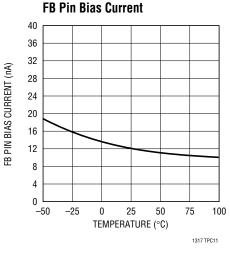

| I <sub>B</sub>   | FB Pin Bias Current (Note 2)              |                                                                                                      | • |              | 12           | 60           | nA       |

|                  | Input Voltage Range                       |                                                                                                      | • | 1.5          |              | 12           | V        |

| g <sub>m</sub>   | Error Amp Transconductance                | $\Delta I = 5\mu A$                                                                                  | • | 70           | 140          | 240          | μmhos    |

| A <sub>V</sub>   | Error Amp Voltage Gain                    |                                                                                                      |   |              | 700          |              | V/V      |

|                  | Maximum Duty Cycle                        |                                                                                                      | • | 80           | 85           |              | %        |

|                  | Switch Current Limit (Note 3)             | V <sub>IN</sub> = 2.5V, Duty Cycle = 30%<br>V <sub>IN</sub> = 2.5V, Duty Cycle = 30%                 | • | 710<br>660   | 800          | 1300<br>1350 | mA<br>mA |

|                  | Burst Mode Operation Switch Current Limit | Duty Cycle = 30% (LT1317)                                                                            |   |              | 275          |              | mA       |

| f <sub>OSC</sub> | Switching Frequency                       |                                                                                                      | • | 520          | 620          | 720          | kHz      |

# **ELECTRICAL CHARACTERISTICS**

Commercial Grade  $V_{IN} = 2V$ ,  $V_{\overline{SHDN}} = 2V$ ,  $T_A = 25^{\circ}C$  unless otherwise noted.

| SYMBOL | PARAMETER                       | CONDITIONS                                                    |   | MIN        | TYP           | MAX        | UNITS    |

|--------|---------------------------------|---------------------------------------------------------------|---|------------|---------------|------------|----------|

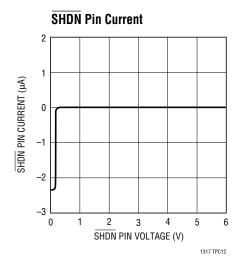

|        | Shutdown Pin Current            | V <sub>SHDN</sub> = V <sub>IN</sub><br>V <sub>SHDN</sub> = 0V | • |            | 0.015<br>-2.3 | 0.06<br>-6 | μA<br>μA |

|        | LBI Threshold Voltage           | CHEN                                                          | • | 190<br>180 | 200<br>200    | 210<br>220 | mV<br>mV |

|        | LBO Output Low                  | I <sub>SINK</sub> = 10μA                                      | • |            | 0.15          | 0.25       | V        |

|        | LBO Leakage Current             | V <sub>LBI</sub> = 250mV, V <sub>LBO</sub> = 5V               | • |            | 0.02          | 0.1        | μΑ       |

|        | LBI Input Bias Current (Note 4) | V <sub>LBI</sub> = 150mV                                      | • |            | 5             | 40         | nA       |

|        | Low-Battery Detector Gain       | 1MΩ Load                                                      |   |            | 2000          |            | V/V      |

|        | Switch Leakage Current          | V <sub>SW</sub> = 5V                                          | • |            | 0.01          | 3          | μΑ       |

|        | Switch V <sub>CE</sub> Sat      | I <sub>SW</sub> = 500mA                                       | • |            | 300           | 350<br>400 | mV<br>mV |

|        | Reference Line Regulation       | $1.8V \le V_{IN} \le 12V$                                     | • |            | 0.08          | 0.15       | %/V      |

|        | SHDN Input Voltage High         |                                                               | • | 1.4        |               | 6          | V        |

|        | SHDN Input Voltage Low          |                                                               | • |            |               | 0.4        | V        |

$\mbox{Industrial Grade} \qquad \mbox{$V_{IN}=2V$, $V_{\overline{SHDN}}=2V$, $-40^{\circ}C \leq T_A \leq 85^{\circ}C$ unless otherwise noted.}$

| SYMBOL           | PARAMETER                       | CONDITIONS                                                                                                                               |   | MIN  | TYP | MAX              | UNITS          |

|------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---|------|-----|------------------|----------------|

| IQ               | Quiescent Current               | Not Switching, V <sub>SHDN</sub> = 2V (LT1317)<br>V <sub>SHDN</sub> = 0V (LT1317/LT1317B)<br>V <sub>SHDN</sub> = 2V, Switching (LT1317B) | • |      |     | 160<br>40<br>7.5 | μΑ<br>μΑ<br>mA |

| $V_{FB}$         | Feedback Voltage                |                                                                                                                                          | • | 1.20 |     | 1.26             | V              |

| I <sub>B</sub>   | FB Pin Bias Current (Note 2)    |                                                                                                                                          | • |      |     | 80               | nA             |

|                  | Input Voltage Range             |                                                                                                                                          | • | 1.7  |     | 12               | V              |

| g <sub>m</sub>   | Error Amp Transconductance      | ΔΙ = 5μΑ                                                                                                                                 | • | 70   | 140 | 240              | μmhos          |

|                  | Maximum Duty Cycle              |                                                                                                                                          | • | 80   |     |                  | %              |

|                  | Switch Current Limit (Note 3)   | V <sub>IN</sub> = 2.5V, Duty Cycle = 30%                                                                                                 | • | 550  |     | 1350             | mA             |

| f <sub>OSC</sub> | Switching Frequency             |                                                                                                                                          | • | 500  |     | 750              | kHz            |

|                  | Shutdown Pin Current            | V <sub>SHDN</sub> = V <sub>IN</sub><br>V <sub>SHDN</sub> = 0V                                                                            | • |      |     | 0.1<br>-7        | μA<br>μA       |

|                  | LBI Threshold Voltage           |                                                                                                                                          | • | 180  |     | 220              | mV             |

|                  | LBO Output Low                  | I <sub>SINK</sub> = 10μA                                                                                                                 | • |      |     | 0.25             | V              |

|                  | LBO Leakage Current             | V <sub>LBI</sub> = 250mV, V <sub>LBO</sub> = 5V                                                                                          | • |      |     | 0.1              | μА             |

|                  | LBI Input Bias Current (Note 4) | V <sub>LBI</sub> = 150mV                                                                                                                 | • |      |     | 60               | nA             |

|                  | Switch Leakage Current          | V <sub>SW</sub> = 5V                                                                                                                     | • |      |     | 3                | μА             |

|                  | Switch V <sub>CE</sub> Sat      | I <sub>SW</sub> = 500mA                                                                                                                  | • |      |     | 400              | mV             |

|                  | Reference Line Regulation       | $1.8V \le V_{IN} \le 12V$                                                                                                                | • |      |     | 0.15             | %/V            |

|                  | SHDN Input Voltage High         |                                                                                                                                          | • | 1.4  |     | 6                | V              |

|                  | SHDN Input Voltage Low          |                                                                                                                                          | • |      |     | 0.4              | V              |

The  $\bullet$  denotes specifications which apply over the full operating temperature range.

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

Note 2: Bias current flows into FB pin.

**Note 3:** Switch current limit guaranteed by design and/or correlation to static tests. Duty cycle affects current limit due to ramp generator.

Note 4: Bias current flows out of LBI pin.

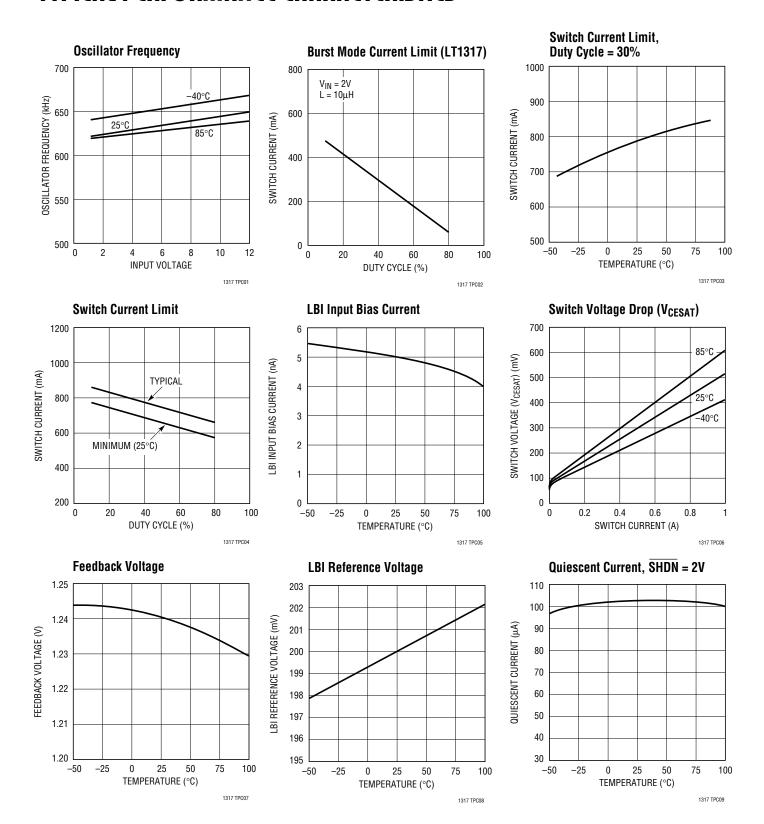

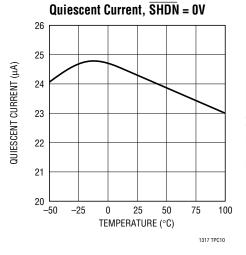

# TYPICAL PERFORMANCE CHARACTERISTICS

# TYPICAL PERFORMANCE CHARACTERISTICS

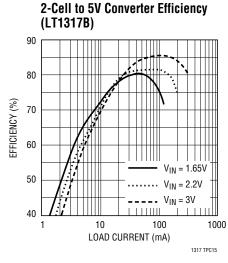

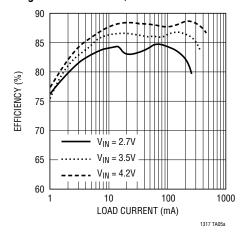

5V Output Efficiency, Circuit of Figure 1 (LT1317)

90

80

70

V<sub>IN</sub> = 1.65V

V<sub>IN</sub> = 2.2V

50

LOAD CURRENT (mA)

#### TYPICAL PERFORMANCE CHARACTERISTICS

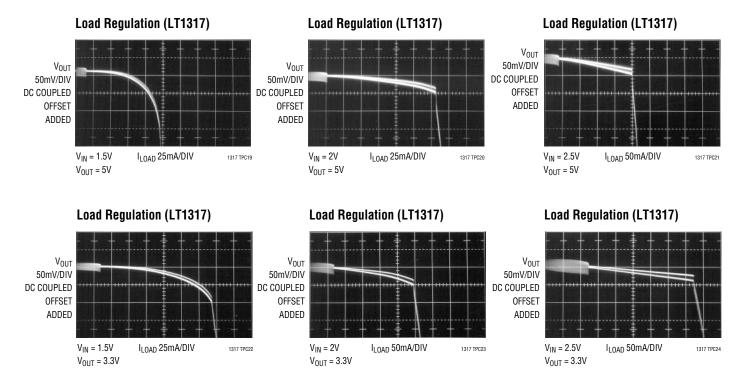

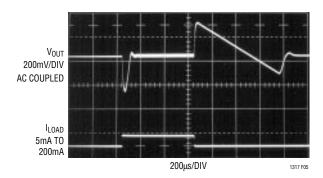

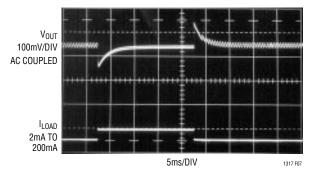

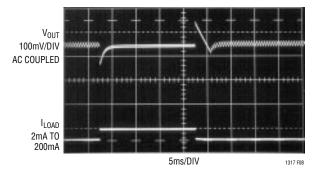

**Note:** For load regulation pictures, double lines are due to output capacitor ESR.

# PIN FUNCTIONS

$V_C$  (Pin 1): Compensation Pin for Error Amplifier. Connect a series RC network from this pin to ground. Typical values for compensation are a 33k/3.3nF combination. A 100pF capacitor from the  $V_C$  pin to ground is optional and improves noise immunity. Minimize trace area at  $V_C$ .

**FB** (Pin 2): Feedback Pin. Reference voltage is 1.24V. Connect resistor divider tap here. Minimize trace area at FB. Set  $V_{OUT}$  according to:  $V_{OUT} = 1.24V(1 + R1/R2)$ .

**SHDN** (**Pin 3**): Shutdown. Pull this pin low for shutdown mode (only the low-battery detector remains active). Leave this pin floating or tie to a voltage between 1.4V and 6V to enable the device. SHDN pin is logic level and need only meet the logic specification (1.4V for high, 0.4V for low).

**GND (Pin 4):** Ground. Connect directly to local ground plane.

**SW** (**Pin 5**): Switch Pin. Connect inductor/diode here. Minimize trace area at this pin to keep EMI down.

$\mathbf{V_{IN}}$  (Pin 6): Supply Pin. Must be bypassed close to the pin.

**LBI (Pin 7):** Low-Battery Detector Input. 200mV reference. Voltage on LBI must stay between ground and 700mV. Low-battery detector remains active in shutdown mode.

**LBO (Pin 8):** Low-Battery Detector Output. Open collector, can sink  $10\mu A$ . A  $1M\Omega$  pull-up is recommended.

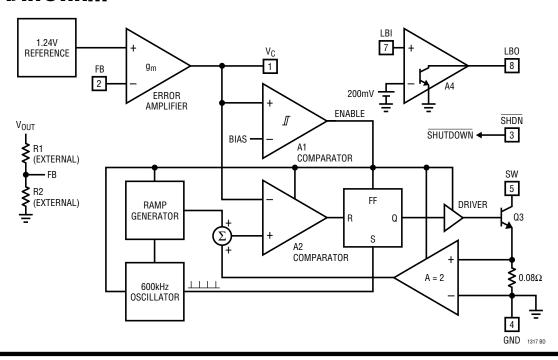

# **BLOCK DIAGRAM**

### APPLICATIONS INFORMATION

#### **OPERATION**

The LT1317 combines a current mode, fixed frequency PWM architecture with Burst Mode micropower operation to maintain high efficiency at light loads. Operation can best be understood by referring to the Block Diagram.

The error amplifier compares voltage at the FB pin with the internal 1.24V bandgap reference and generates an error signal  $V_C$ . When  $V_C$  decreases below the bias voltage on hysteretic comparator A1, A1's output goes low, turning off all circuitry except the 1.24V reference, error amplifier and low-battery detector. Total current consumption in this state is 100µA. As output loading causes the FB voltage to decrease, V<sub>C</sub> increases causing A1's output to go high, in turn enabling the rest of the IC. Switch current is limited to approximately 250mA initially after A1's output goes high. If the load is light, the output voltage (and FB voltage) will increase until A1's output goes low, turning off the rest of the LT1317. Low frequency ripple voltage appears at the output. The ripple frequency is dependent on load current and output capacitance. This Burst Mode operation keeps the output regulated and reduces average current into the IC, resulting in high efficiency even at load currents of 300µA or less.

If the output load increases sufficiently, A1's output remains high, resulting in continuous operation. When the LT1317 is running continuously, peak switch current is controlled by  $V_{C}$  to regulate the output voltage. The switch is turned on at the beginning of each switch cycle. When the summation of a signal representing switch current and a ramp generator (introduced to avoid subharmonic oscillations at duty factors greater than 50%) exceeds the  $V_{C}$  signal, comparator A2 changes state, resetting the flip-flop and turning off the switch. Output voltage increases as switch current is increased. The output, attenuated by a resistor divider, appears at the FB pin, closing the overall loop. Frequency compensation is provided by an external series RC network and an optional capacitor connected between the  $V_{C}$  pin and ground.

Low-battery detector A4's open collector output (LBO) pulls low when the LBI pin voltage drops below 200mV. There is no hysteresis in A4, allowing it to be used as an amplifier in some applications. The low-battery detector remains active in shutdown. To enable the converter, SHDN must be left floating or tied to a voltage between 1.4V and 6V.

The LT1317B differs from the LT1317 in that the bias point on A1 is set lower than on the LT1317 so that minimum switch current can drop below 50mA. Because A1's bias point is set lower, there is no Burst Mode operation at light loads and the device continues switching at constant frequency. This results in the absence of low frequency output voltage ripple at the expense of light load efficiency.

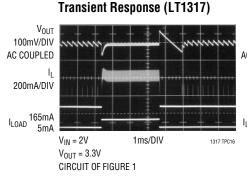

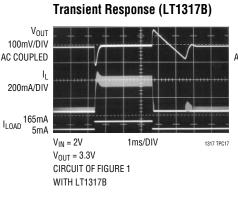

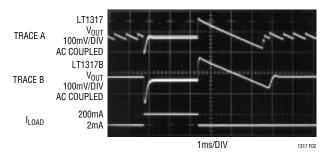

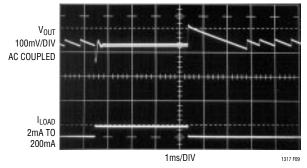

The difference between the two devices is clearly illustrated in Figure 2. The top two traces in Figure 2 show an LT1317/LT1317B circuit, using the components indicated in Figure 1, set to a 3.3V output. Input voltage is 2V. Load current is stepped from 2mA to 200mA for both circuits. Low frequency Burst Mode operation voltage ripple is observed on Trace A, while none is observed on Trace B.

Figure 2. LT1317 Exhibits Ripple at 2mA Load During Burst Mode Operation, the LT1317B Does Not

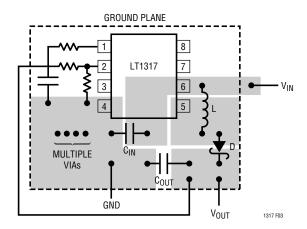

#### **LAYOUT HINTS**

The LT1317 switches current at high speed, mandating careful attention to layout for proper performance. *You will not get advertised performance with careless layouts.* Figure 3 shows recommended component placement. Follow this closely in your PC layout. Note the direct path of the switching loops. Input capacitor  $C_{IN}$  *must* be placed close (<5mm) to the IC package. As little as 10mm of wire or PC trace from  $C_{IN}$  to  $V_{IN}$  will cause problems such as inability to regulate or oscillation.

Figure 3. Recommended Component Placement. Traces Carrying High Current Are Direct. Trace Area at FB Pin and  $V_{\rm C}$  Pin is Kept Low. Lead Length to Battery Should be Kept Short.

#### COMPONENT SELECTION

#### **Inductors**

Inductors appropriate for use with the LT1317 must possess three attributes. First, they must have low core loss at 600kHz. Most ferrite core units have acceptable losses at this switching frequency. Inexpensive iron powder cores should be viewed suspiciously, as core losses can cause significant efficiency penalties at 600kHz. Second, the inductor must be able to handle peak switch current of the LT1317 without saturating. This places a lower limit on the physical size of the unit. Molded chokes or chip inductors usually do not have enough core to support the LT1317 maximum peak switch current and are unsuitable for the application. Lastly, the inductor should have low DCR (copper wire resistance) to prevent efficiency-killing I<sup>2</sup>R losses. Linear Technology has identified several inductors suitable for use with the LT1317. This is not an exclusive list. There are many magnetics vendors whose components are suitable for use. A few vendor's components are listed in Table 1.

Table 1. Inductors Suitable for Use with the LT1317

| PART        | VALUE | MAX<br>DCR | MFR         | HEIGHT<br>(mm) | COMMENT                                       |

|-------------|-------|------------|-------------|----------------|-----------------------------------------------|

| LQH3C100    | 10μΗ  | 0.57       | Murata-Erie | 2.0            | Smallest Size,<br>Limited Current<br>Handling |

| D01608-103  | 10μΗ  | 0.16       | Coilcraft   | 3.0            |                                               |

| CD43-100    | 10μΗ  | 0.18       | Sumida      | 3.2            |                                               |

| CD54-100    | 10μΗ  | 0.10       | Sumida      | 4.5            | Best Efficiency                               |

| CTX32CT-100 | 10μΗ  | 0.50       | Coiltronics | 2.2            | 1210 Footprint                                |

#### **Capacitor Selection**

Low ESR (Equivalent Series Resistance) capacitors should be used at the output of the LT1317. For most applications a solid tantalum in a C or D case size works well. Acceptable capacitance values range from  $10\mu F$  to  $330\mu F$  with ESR falling between  $0.1\Omega$  and  $0.5\Omega$ . If component size is an issue, tantalum capacitors in smaller case sizes can be used but they have high ESR and output voltage ripple may reach unacceptable levels.

Ceramic capacitors are an alternative because of their combination of small size and low ESR. A  $10\mu$ F ceramic capacitor will work for some applications but the extremely low ESR of these capacitors may cause loop stability problems. Compensation components will need

to be adjusted to ensure a stable system for the entire input voltage range. Figure 4 shows a 2V to 3.3V converter with new values for  $R_{C}$  and  $C_{C}$ . Figure 5 details transient response for this circuit. Also, ceramic caps are prone to temperature effects and the designer must check loop stability over the operating temperature range (see section on Frequency Compensation).

Input bypass capacitor ESR is less critical and smaller units may be used. If the input voltage source is physically near the  $V_{IN}$  pin (<5mm), a  $10\mu F$  ceramic or a  $10\mu F$  A case tantalum is adequate.

#### **Diodes**

Most of the application circuits on this data sheet specify the Motorola MBR0520L surface mount Schottky diode. In lower current applications, a 1N4148 can be used, although efficiency will suffer due to the higher forward drop. This effect is particularly noticeable at low output voltages. For higher voltage output applications, such as LCD bias generators, the extra drop is a small percentage of the output voltage so the efficiency penalty is small. The low cost of the 1N4148 makes it attractive wherever it can be used. In through hole applications the 1N5818 is the all around best choice.

Figure 4. 2V to 3.3V Converter with a 10 $\mu$ F Ceramic Output Capacitor.  $R_C$  and  $C_C$  Have Been Adjusted to Give Optimum Transient Response.

Figure 5. Transient Response for the Circuit of Figure 4.

#### FREQUENCY COMPENSATION

The LT1317 has an external compensation pin  $(V_C)$  which allows the frequency response to be optimized for the circuit configuration. In most cases, the values used in Figure 1 will work. Some circuits may need additional compensation and a simple trial and error method for determining the necessary component values is given.

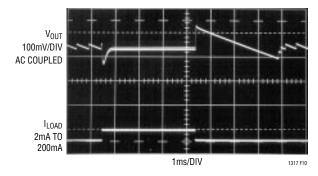

Figure 6 shows the test setup. A load step is applied and the resulting output voltage waveform is observed. Figures 7 through 10 detail the response for various values of R and C in the compensation network. The circuit of Figure 7 starts with a large C and small R giving a highly overdamped system. This system will always be stable but the output voltage displays a long settling time of >5ms. Figure 8's circuit has reduced C giving a shorter settling time but still overdamped. Figure 9 shows the results when C is reduced to the point where the system becomes underdamped. The output voltage responds quickly ( $\approx 200 \mu s$  to  $300 \mu s$ ) but some ringing exists. Figure 10 has

Figure 6. Frequency Response Test Setup

optimum R and C values giving the best possible settling time with adequate phase margin.

An additional 100pF capacitor ( $C_{C2}$ ) is connected to the  $V_C$  pin and is necessary if the LT1317 is operated near current limit. Also,  $C_{C2}$  should be present when higher ESR output capacitors are used.

Figure 7. With C = 56nF and R = 33k, the System is Highly Overdamped.

Figure 8. Reducing C to 22nF Speeds Up the Response. (R = 33k)

Figure 9. Using 680pF for C Results in an Underdamped System with Ringing. (R = 33k)

Figure 10. 3.3nF and 33k Gives the Shortest Settling Time with No Ringing.

#### LOW-BATTERY DETECTOR

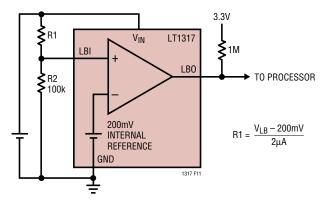

The LT1317's low-battery detector is a simple PNP input gain stage with an open collector NPN output. The negative input of the gain stage is tied internally to a 200mV  $\pm 5\%$  reference. The positive input is the LBI pin. Arrangement as a low-battery detector is straightforward.

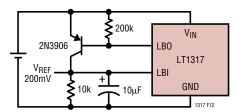

Figure 11 details hookup. R1 and R2 need only be low enough in value so that the bias current of the LBI pin doesn't cause large errors. For R2, 100k is adequate. The 200mV reference can also be accessed as shown in Figure 12. The low-battery detector remains active in shutdown.

Figure 11. Setting Low-Battery Detector Trip Point

Figure 12. Accessing 200mV Reference

# TYPICAL APPLICATIONS

#### Single Li-Ion Cell to 3.3V SEPIC Converter

#### 3.3V SEPIC Efficiency

# TYPICAL APPLICATIONS

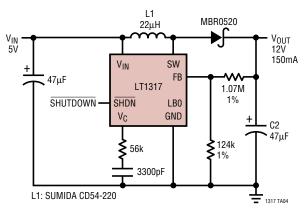

5V to 12V Boost Converter

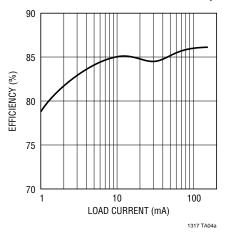

#### **5V to 12V Boost Converter Efficiency**

Single Li-Ion to 5V DC/DC Converter

Single Li-Ion to 5V DC/DC Converter Efficiency

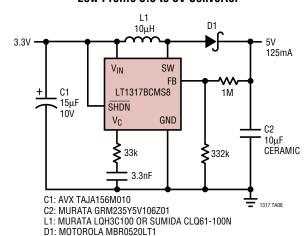

Low Profile 3.3 to 5V Converter

**TECHNOLO**

12

# TYPICAL APPLICATIONS

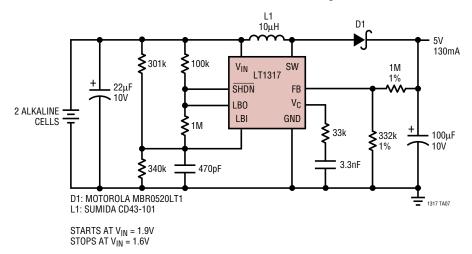

#### 2-Cell to 5V DC/DC Converter with Undervoltage Lockout

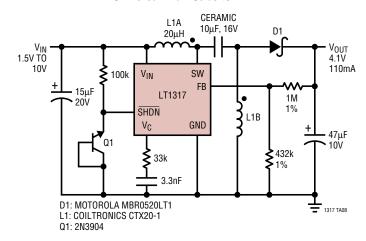

#### Universal Wall Cube to 4.1V

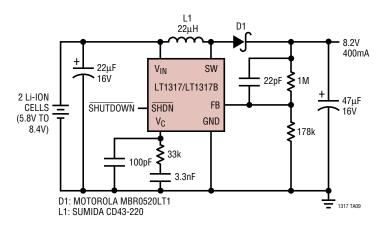

#### 2 Li-Ion to 8.2V DC/DC Converter

# TYPICAL APPLICATIONS

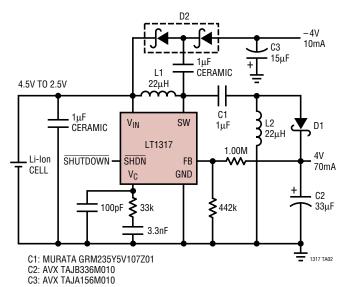

Single Li-Ion Cell to 4V/70mA, -4V/10mA

D1: MBR0520 D2: BAT54S (DUAL DIODE) L1, L2: MURATA LQH3C220K04

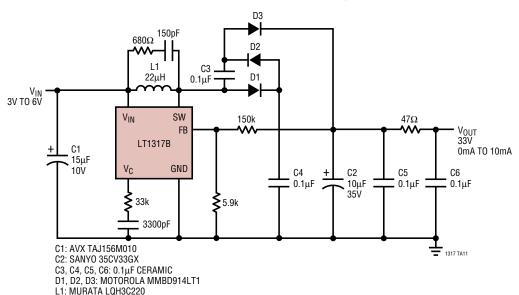

#### **Low Noise 33V Varactor Bias Supply**

**TUNEAD**

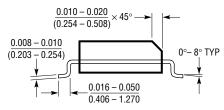

# PACKAGE DESCRIPTION Dimensions in inches (millimeters) unless otherwise noted.

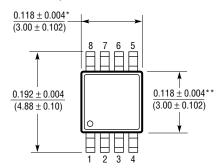

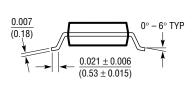

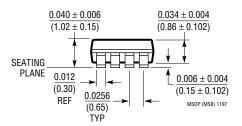

#### **MS8 Package** 8-Lead Plastic MSOP

(LTC DWG # 05-08-1660)

- \* DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

- \*\* DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

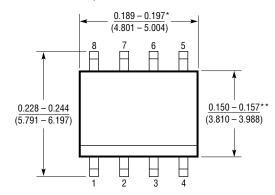

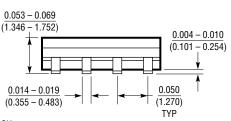

#### S8 Package 8-Lead Plastic Small Outline (Narrow 0.150)

(LTC DWG # 05-08-1610)

- \*DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

- \*\*DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

SO8 0996

# TYPICAL APPLICATION

#### **Digital Camera Power Supply**

# **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                           | COMMENTS                                                     |

|-------------|-------------------------------------------------------|--------------------------------------------------------------|

| LTC®1163    | Triple High Side Driver for 2-Cell Inputs             | 1.8V Minimum Input, Drives N-Channel MOSFETs                 |

| LTC1174     | Micropower Step-Down DC/DC Converter                  | 94% Efficiency, 130μA I <sub>Q</sub> , 9V to 5V at 300mA     |

| LT1302      | High Output Current Micropower DC/DC Converter        | 5V/600mA from 2V, 2A Internal Switch, 200μA I <sub>Q</sub>   |

| LT1304      | 2-Cell Micropower DC/DC Converter                     | Low-Battery Detector Active in Shutdown                      |

| LT1307      | Single Cell Micropower 600kHz PWM DC/DC Converter     | 3.3V at 75mA from 1 Cell, MSOP Package                       |

| LTC1440/1/2 | Ultralow Power Single/Dual Comparators with Reference | 2.8μA I <sub>Q</sub> , Adjustable Hysteresis                 |

| LTC1516     | 2-Cell to 5V Regulated Charge Pump                    | 12μA I <sub>Q</sub> , No Inductors, 5V at 50mA from 3V Input |

| LT1521      | Micropower Low Dropout Linear Regulator               | 500mV Dropout, 300mA Current, 12μA I <sub>Q</sub>            |