## 55V Buck-Boost Multi-Chemistry Battery Charger

#### **FEATURES**

- Wide Voltage Range: 4.5V to 55V Input, Up to 55V Output (60V Absolute Maximums)

- Synchronous Buck-Boost DC/DC Controller

- Li-lon and Lead-Acid Charge Algorithms

- ±0.5% Float Voltage Accuracy

- ±5% Charge Current Accuracy

- Instant-On for Heavily Discharged Batteries

- Ideal Diode Controller Provides Low Loss PowerPath When Input Power is Limited

- Input Voltage Regulation for High Impedance Input Supplies and Solar Panel Peak Power Operation

- Onboard Timer for Protection and Termination

- Bad Battery Detection with Auto-Reset

- NTC Input for Temperature Qualified Charging

- Binary Coded Open-Collector Status Pins

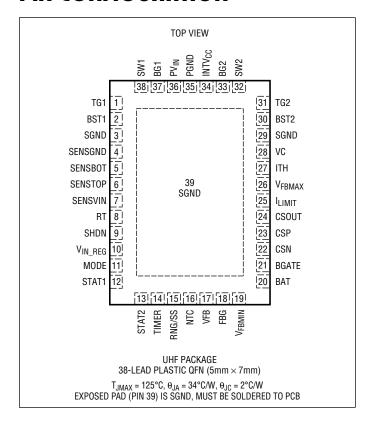

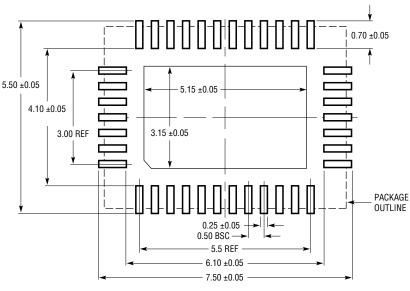

- Low Profile (0.75mm) 38-Pin 5mm × 7mm QFN Package

#### **APPLICATIONS**

- Portable Industrial and Medical Equipment

- Solar-Powered Systems

- Military Communications Equipment

- 12V to 24V Embedded Automotive Systems

#### DESCRIPTION

The LTC®4020 is a high voltage power manager providing PowerPath™ instant-on operation and high efficiency battery charging over a wide voltage range. An onboard buck-boost DC/DC controller operates with battery and/or system voltages above, below, or equal to the input voltage.

The LTC4020 seamlessly manages power distribution between battery and converter outputs in response to load variations, battery charge requirements and input power supply limitations.

The LTC4020 battery charger can provide a constant-current/constant-voltage charge algorithm (CC/CV), constant-current charging (CC), or charging with an optimized 4-step, 3-stage lead-acid battery charge profile. Maximum converter and battery charge currents are resistor programmable.

The IC's instant-on operation ensures system load power even with a fully discharged battery. Additional safety features include preconditioning for heavily discharged batteries and an integrated timer for termination and protection.

(T, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and PowerPath is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents, including 7583113 and 8405362.

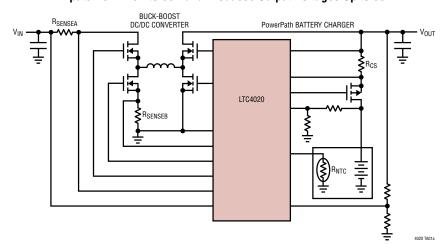

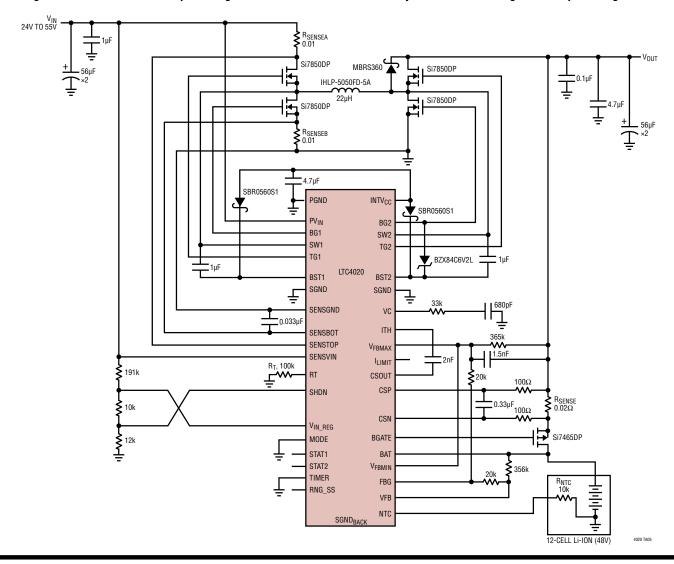

#### TYPICAL APPLICATION

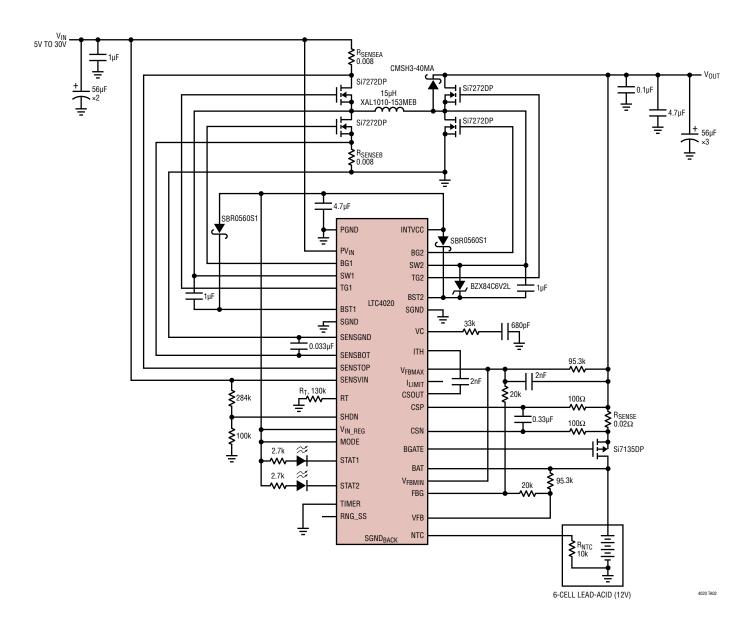

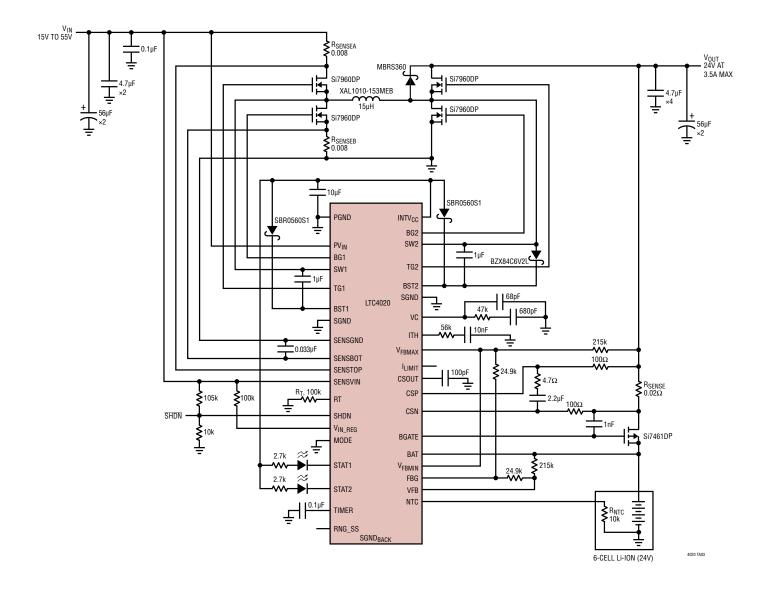

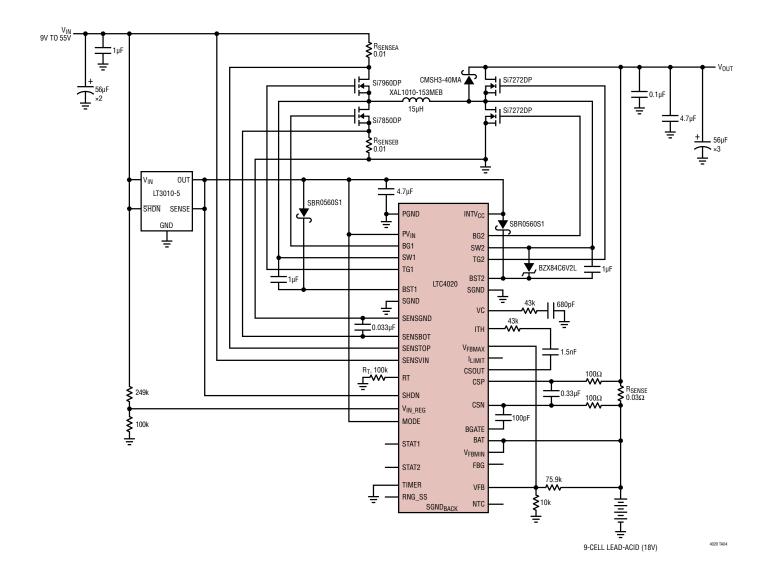

Buck-Boost DC/DC Converter Controller with PowerPath Battery Charger Accepts Inputs from 4.5V to 55V and Produces Output Voltages Up to 55V

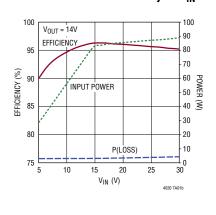

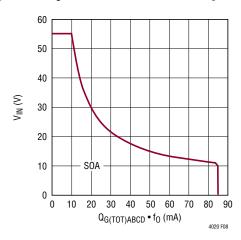

## 5V to 30V 6-Cell Lead-Acid Supply/Charger Maximum Power Efficiency vs $V_{\rm IN}$

#### **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| ,                                                                                          |                |

|--------------------------------------------------------------------------------------------|----------------|

| PV <sub>IN</sub> , SENSVIN                                                                 | 0.3 to 60V     |

| BST1, BST2                                                                                 | 0.3 to 66V     |

| SW1, SW2                                                                                   | 2 to 60V       |

| SENSVIN – PV <sub>IN</sub>                                                                 | 0.3 to 60V     |

| BST1 – SW1, BST2 – SW2                                                                     | 0.3 to 6V      |

| SENSVIN – SENSTOP, SENSBOT –                                                               |                |

| SENSGND                                                                                    | 0.3 to 0.3V    |

| CSP, CSN                                                                                   | 0.3 to 60V     |

| CSP – CSN                                                                                  |                |

| STAT1, STAT2, SHDN                                                                         |                |

| V <sub>FBMAX</sub> , V <sub>INREG</sub> , V <sub>FB</sub> , V <sub>FBMIN</sub> , BAT, FBG. | 0.3 to 60V     |

| MODE                                                                                       | 0.3 to 6V      |

| Status Pin Currents:                                                                       |                |

| STAT1, STAT2                                                                               | 5mA            |

| Operating Junction Temperature                                                             |                |

| Range (Note 2)                                                                             |                |

| Storage Temperature Range                                                                  | -65°C to 150°C |

|                                                                                            |                |

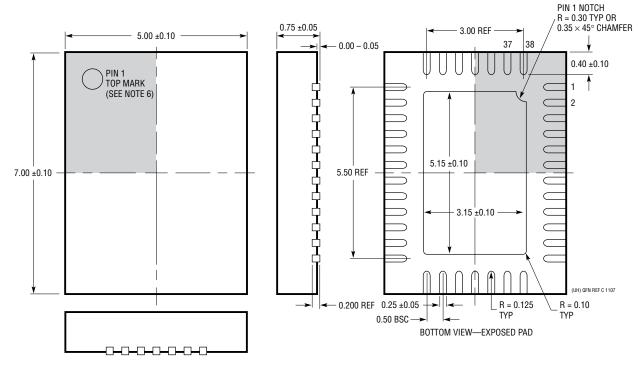

#### PIN CONFIGURATION

#### ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|-------------------|---------------|---------------------------------|-------------------|

| LTC4020EUHF#PBF  | LTC4020EUHF#TRPBF | 4020          | 38-Lead (5mm × 7mm) Plastic QFN | -40°C to 125°C    |

| LTC4020IUHF#PBF  | LTC4020IUHF#TRPBF | 4020          | 38-Lead (5mm × 7mm) Plastic QFN | -40°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ (Note 2). $V_{IN} = SENSVIN = CSP = CSN = BAT = 20V$ , SHDN = 2V, $C_{(TG1, BG1, TG2, BG2)} = 1000pF$ , $V_{RNG/SS} = 2V$ .

| SYMBOL              | PARAMETER                                                                      | CONDITIONS                                      | CONDITIONS |     | TYP        | MAX | UNITS |  |  |

|---------------------|--------------------------------------------------------------------------------|-------------------------------------------------|------------|-----|------------|-----|-------|--|--|

| Buck-Boost          | Buck-Boost Switching Converter                                                 |                                                 |            |     |            |     |       |  |  |

| $\overline{V_{IN}}$ | Operating Voltage Range                                                        | PV <sub>IN</sub> ; SENSVIN                      | •          | 4.5 |            | 55  | V     |  |  |

| UVLO                | V <sub>IN</sub> Supply UVLO (Rising)<br>V <sub>IN</sub> Supply UVLO Hysteresis | DC/DC Functions Enabled V <sub>IN</sub> Falling | •          | 3.6 | 4.0<br>0.4 | 4.4 | V     |  |  |

|                     | SENSVIN Supply UVLO (Rising)<br>SENSVIN UVLO Hysteresis                        | INTV <sub>CC</sub> Enabled<br>SENSVIN Falling   |            |     | 3.4<br>0.3 |     | V     |  |  |

|                     | BST Supplies UVLO (Rising)<br>BST Supplies UVLO Hysteresis                     | BST1 – SW1; BST2 – SW2;<br>SW1, SW2 = 0V        | •          | 3.0 | 3.3<br>0.4 | 3.8 | V     |  |  |

|                     | 20. 00pp00 0. 20 Hyotoroolo                                                    | J, 32                                           |            |     | <b></b>    |     |       |  |  |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2).  $V_{IN} = SENSVIN = CSP = CSN = BAT = 20V$ , SHDN = 2V,  $C_{(TG1, BG1, TG2, BG2)} = 1000pF$ ,  $V_{RNG/SS} = 2V$ .

| SYMBOL               | PARAMETER                                                 | CONDITIONS                                                                                   |   | MIN   | TYP               | MAX   | UNITS             |

|----------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------|---|-------|-------------------|-------|-------------------|

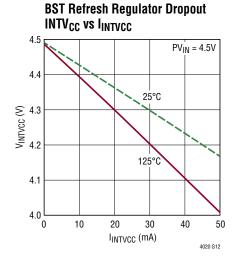

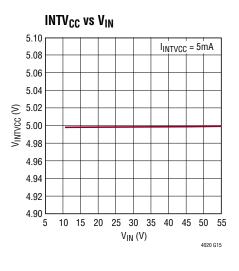

| INTV <sub>CC</sub>   | Boost Refresh Supply Voltage                              | I <sub>LOAD</sub> = 5mA                                                                      | • | 4.85  | 5.0               | 5.15  | V                 |

|                      | Boost Refresh Supply Dropout                              | PV <sub>IN</sub> = 4.5V; I <sub>INTVCC</sub> = 5mA                                           |   |       | 4.46              |       | V                 |

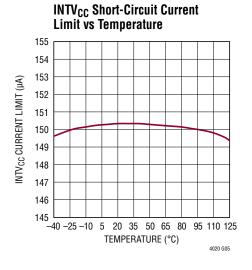

|                      | Boost Refresh Supply Short-Circuit Current<br>Limit       | V <sub>INTVCC</sub> = 0V                                                                     | • | 85    | 150               |       | mA                |

| I <sub>PVIN</sub>    | PV <sub>IN</sub> Operating Current                        | Note 3; ITH = 0V                                                                             | • |       | 1.6               | 3     | mA                |

|                      | Shutdown Current                                          | V <sub>SHDN</sub> = 0                                                                        | • |       | 3                 | 6     | μA                |

| I <sub>SENSVIN</sub> | SENSEVIN Operating Current                                |                                                                                              | • |       | 0.25              | 0.5   | mA                |

|                      | Shutdown Current                                          | V <sub>SHDN</sub> = 0                                                                        | • |       | 25                | 60    | μA                |

| I <sub>SENSTOP</sub> | SENSETOP Operating Current                                |                                                                                              |   |       | 10                |       | μA                |

|                      | Shutdown Current                                          | V <sub>SHDN</sub> = 0                                                                        |   |       | 0.1               |       | μA                |

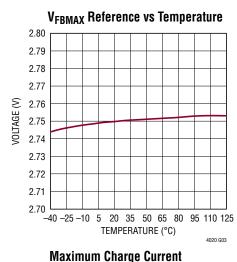

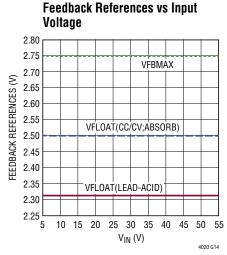

| V <sub>FBMAX</sub>   | DC/DC Converter Reference                                 | Charging Terminated                                                                          | • | 2.7   | 2.75              | 2.8   | V                 |

| SHDN                 | IC Enable Threshold (Rising)<br>Threshold Hysteresis      |                                                                                              | • | 1.175 | 1.225<br>100      | 1.275 | V<br>mV           |

|                      | SHDN Pin Bias Current                                     |                                                                                              |   |       | 10                |       | nA                |

| V <sub>SENS</sub>    | DC/DC Converter Inductor Current Limit<br>(Average Value) | V <sub>SENSVIN</sub> - V <sub>SENSTOP</sub> ;<br>V <sub>SENSGND</sub> - V <sub>SENSBOT</sub> | • | 45    | 50                | 60    | mV                |

|                      | Reverse Current Inhibit<br>(Average Value)                | V <sub>ITH</sub> Falling (TG2 Disabled)<br>V <sub>ITH</sub> Rising (TG2 Enabled)             | • | 0     | 2<br>6            |       | mV<br>mV          |

| I <sub>LIMIT</sub>   | Inductor Current Limit Programming                        | V <sub>ILIMIT</sub> = 0.5V; V <sub>ILIMIT</sub> /V <sub>SENS(MAX)</sub>                      |   |       | 20                |       | V/V               |

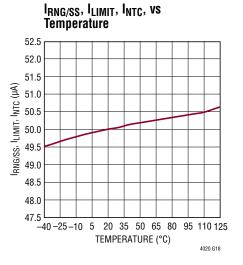

|                      | I <sub>LIMIT</sub> Pin Bias Current                       |                                                                                              | • | 47.5  | 50                | 52.5  | μA                |

| ITH                  | Error Amp Current Limit                                   | $V_{FBMAX} = 0$ , $V_{ITH} = 1.3V$                                                           |   |       | 8                 |       | μA                |

|                      | Error Amp Transconductance                                | V <sub>FBMAX</sub> = 2.75V; V <sub>ITH</sub> = 1.3V                                          |   |       | 85                |       | umho              |

| VC                   | High Side Current Sense Transconductance                  | $(V_{SENSVIN} - V_{SENSETOP})$ to $I_{VC}$<br>$V_C = 1.8V$                                   |   |       | 200               |       | umho              |

|                      | Low Side Current Sense Transconductance                   | $(V_{SENSGND} - V_{SENSEBOT})$ to $I_{VC}$<br>$V_C = 1.8V$                                   |   |       | 200               |       | umho              |

| DC <sub>MAX</sub>    | Maximum Duty Cycle                                        | BG2: t <sub>ON</sub> • f <sub>O</sub>                                                        | • | 70    | 80                |       | %                 |

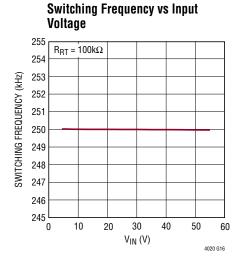

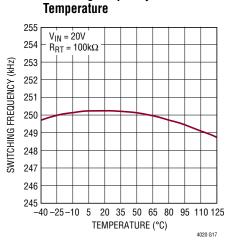

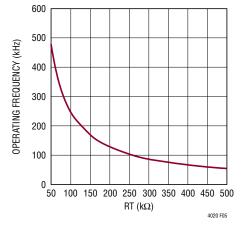

| $f_0$                | Switching Frequency                                       | R <sub>RT</sub> = 100k<br>R <sub>RT</sub> = 50k<br>R <sub>RT</sub> = 250k                    | • | 235   | 250<br>500<br>100 | 265   | kHz<br>kHz<br>kHz |

| $\overline{t_{ON}}$  | Minimum On Time                                           | BG2                                                                                          | • |       | 150               | 250   | ns                |

| t <sub>OFF</sub>     | Minimum Off Time                                          | TG1                                                                                          | • |       | 300               | 500   | ns                |

| $t_{TR}$             | Gate Drive Transition Time                                | TG1, BG1, TG2, BG2                                                                           |   |       | 5                 |       | ns                |

| t <sub>NOL</sub>     | Gate Drive Non-Overlap time                               | (TG1 – SW1) to BG1,<br>(TG2 – SW2) to BG2                                                    |   |       | 75                | ,     | ns                |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2).  $V_{IN} = SENSVIN = CSP = CSN = BAT = 20V$ , SHDN = 2V,  $C_{(TG1, BG1, TG2, BG2)} = 1000pF$ ,  $V_{RNG/SS} = 2V$ .

| SYMBOL                 | PARAMETER CONDITIONS                                                                                                         |                                                                                                                               | MIN         | TYP                                 | MAX                             | UNITS                               |                        |

|------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------|---------------------------------|-------------------------------------|------------------------|

| <b>Battery Cha</b>     | rger                                                                                                                         |                                                                                                                               |             |                                     |                                 |                                     |                        |

| $V_{BAT}$              | Charger Output Voltage Range                                                                                                 |                                                                                                                               | •           |                                     |                                 | 55                                  | V                      |

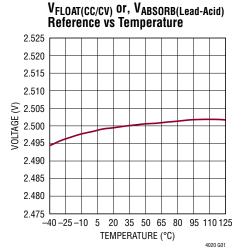

| $V_{FB}$               | Float Reference                                                                                                              | CC/CV Charging (MODE = 0V)                                                                                                    | •           | 2.4875<br>2.475                     | 2.5                             | 2.5125<br>2.525                     | V                      |

|                        | Auto Recharge Voltage<br>Precondition Threshold (Rising)<br>Precondition Hysteresis                                          | % of Float Reference<br>% of Float Reference                                                                                  | •           | 96.5<br>68                          | 97.5<br>70<br>85                | 98.5<br>72                          | %<br>%<br>mV           |

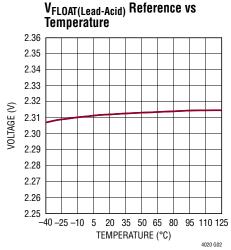

|                        | Absorption Reference Float Reference Bulk Charge Threshold (Falling) Precondition Threshold (Rising) Precondition Hysteresis | Lead-Acid Charging (MODE = INTV <sub>CC</sub> ) % of Absorption Reference % of Absorption Reference % of Absorption Reference | •           | 2.4875<br>2.475<br>91.5<br>86<br>68 | 2.5<br>92.5<br>87.5<br>70<br>85 | 2.5125<br>2.525<br>93.5<br>89<br>72 | V<br>V<br>%<br>%<br>mV |

|                        | Voltage Reference                                                                                                            | CC Charging (MODE = - NC -)                                                                                                   | •           | 2.4875<br>2.475                     | 2.5                             | 2.5125<br>2.525                     | V<br>V                 |

| V <sub>IN_REG</sub>    | Input Regulation Reference                                                                                                   | % of Float (CC/CV), Safety (CC), or<br>Absorption (LA) Reference                                                              | •           | 98                                  | 100                             | 102                                 | %                      |

| V <sub>FBMIN</sub>     | Instant-On Reference                                                                                                         | % of Float (CC/CV) or Absorption (LA)<br>Reference                                                                            | •           | 84                                  | 85                              | 86                                  | %                      |

|                        | C/10 Detection Enable (Rising)<br>Hysteresis (Falling)                                                                       |                                                                                                                               |             |                                     | 2.175<br>20                     |                                     | mV<br>mV               |

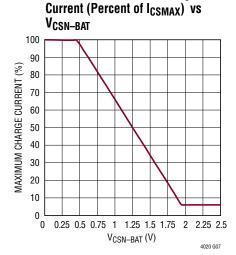

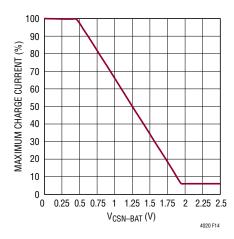

|                        | Instant-On Charge Current Reduction<br>Threshold                                                                             | V <sub>CSN</sub> – V <sub>BAT</sub> ; Note 4                                                                                  |             |                                     | 0.45                            |                                     | V                      |

|                        | C/10 Detection Enable<br>C/10 Detection Hysteresis                                                                           | V <sub>CSN</sub> – V <sub>BAT</sub> Falling<br>V <sub>CSN</sub> – V <sub>BAT</sub> Rising                                     | 1.05<br>200 |                                     |                                 | V<br>mV                             |                        |

|                        | Charge Current Reduction Gain                                                                                                | $\Delta V_{CS(MAX)}/\Delta (V_{CSN} - V_{BAT});$ Note 4                                                                       |             |                                     | -33                             |                                     | mV/V                   |

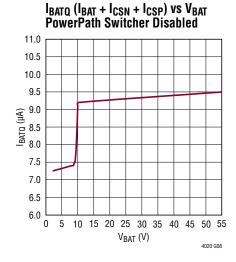

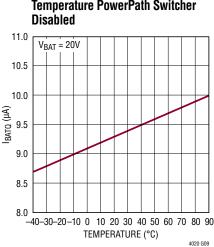

| I <sub>BATQ</sub>      | Battery Bias Currents with PowerPath<br>Switcher Disabled                                                                    | I <sub>CSP</sub> + I <sub>CSN</sub> + I <sub>BAT</sub>                                                                        | •           |                                     | 9                               | 18                                  | μA                     |

| CSN, CSP               | Charger Current Sense Pin Operating Bias<br>Currents                                                                         | I <sub>CSP</sub> = I <sub>CSN</sub> ; Charging Enabled                                                                        |             | 40                                  |                                 | μА                                  |                        |

|                        | Charger Current Sense Limit Voltage                                                                                          | V <sub>CSP</sub> - V <sub>CSN</sub>                                                                                           | •           | 47.5                                | 50                              | 52.5                                | mV                     |

|                        | Charger Current Sense Termination Voltage (C/10)                                                                             | V <sub>CSP</sub> – V <sub>CSN</sub> ; MODE = 0V                                                                               | •           | 3                                   | 5                               | 7                                   | mV                     |

|                        | Charger Current Sense Precondition Voltage                                                                                   | $V_{CSP} - V_{CSN}$ ; $V_{FB} = 1.5$                                                                                          | •           | 1.5                                 | 3                               | 4.5                                 | mV                     |

|                        | Sense Input UVLO<br>UVLO Hysteresis                                                                                          | V <sub>CSP</sub> Rising (Charging Enabled)<br>V <sub>CSP</sub> Falling (Charging Disabled)                                    | •           | 1.6                                 | 1.75<br>100                     | 1.9                                 | V<br>mV                |

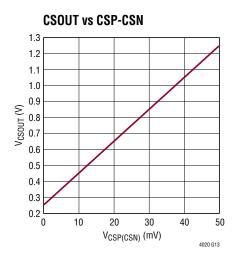

| CSOUT                  | Offset                                                                                                                       | V <sub>CSP</sub> = V <sub>CSN</sub>                                                                                           | •           | 0.225                               | 0.25                            | 0.290                               | V                      |

|                        | Gain                                                                                                                         | $\Delta V_{CSOUT} / \Delta (V_{CSP} - V_{CSN})$                                                                               | •           | 19                                  | 20                              | 21                                  | V/V                    |

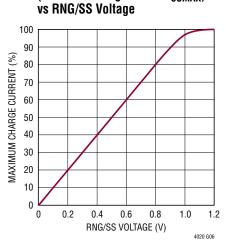

| RNG/SS                 | Current Limit Programming                                                                                                    | $V_{RNG/SS} = 0.5V; V_{RNG/SS}/V_{CS(MAX)}$                                                                                   | •           | 18                                  | 20                              | 22                                  | V/V                    |

| NTC                    | NTC Range Limit (High)<br>NTC Range Limit (Low)<br>NTC Range Hysteresis                                                      | V <sub>NTC</sub> Rising<br>V <sub>NTC</sub> Falling<br>% of V <sub>NTC(H,L)</sub>                                             | •           | 1.30 1.35 1.40                      |                                 | V<br>V<br>%                         |                        |

| I <sub>NTC</sub>       | NTC Pin Bias Current                                                                                                         | V <sub>NTC</sub> = 0.8V                                                                                                       | •           | 47.5                                | 50                              | 52.5                                | μA                     |

| •                      | NTC Disable Current                                                                                                          | INTC Pin Current (Falling)                                                                                                    | )           |                                     | 3.5                             |                                     | <u>.</u><br>μΑ         |

|                        | NTC Disable Current Hysteresis                                                                                               | , , , ,                                                                                                                       |             |                                     | 2                               |                                     | μA                     |

| $\overline{V_{BGATE}}$ | Gate Clamp Voltage                                                                                                           | V <sub>CSN</sub> – V <sub>BGATE</sub> ; V <sub>CSN</sub> = 20V                                                                | •           | 7                                   | 9.5                             | 12                                  | V                      |

| Dartie                 | C/10 Detection Enable (Falling) C/10 Detection Enable Hysteresis                                                             | V <sub>CSN</sub> < 7V                                                                                                         |             |                                     | 0.425<br>0.125                  |                                     | V                      |

|                        | _ 1                                                                                                                          | 1                                                                                                                             | - 1         |                                     |                                 |                                     | 4020f                  |

4

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2).  $V_{IN} = SENSVIN = CSP = CSN = BAT = 20V$ , SHDN = 2V,  $C_{(TG1, BG1, TG2, BG2)} = 1000pF$ ,  $V_{RNG/SS} = 2V$ .

| SYMBOL                  | PARAMETER                        | CONDITIONS                                                                                               | , | MIN | TYP          | MAX        | UNITS |  |

|-------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------|---|-----|--------------|------------|-------|--|

| BGATE Pull-Down Current |                                  | Charging Enabled; V <sub>BGATE</sub> = V <sub>CSN</sub>                                                  |   |     | 15           |            | μА    |  |

|                         | BGATE Pull-Up Current            | Charging Disabled; V <sub>CSN</sub> – V <sub>BGATE</sub> = 2V                                            |   |     | 15           |            | μА    |  |

|                         | BGATE Standby Pull-Down Current  | V <sub>SHDN</sub> = 0V; V <sub>BGATE</sub> = V <sub>CSN</sub>                                            |   |     | 120          |            | μА    |  |

|                         | Ideal Diode Pull-Down Current    | Charging Disabled; $V_{BAT} - V_{CSN} = 0.5V$ ; $V_{BGATE} = V_{CSN}$                                    |   |     | 500          |            | μА    |  |

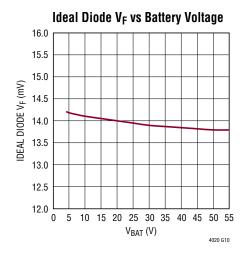

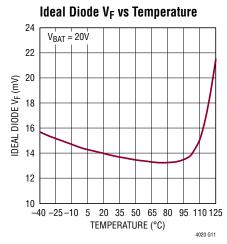

|                         | Ideal Diode Forward Voltage      | $V_{BAT} - V_{CSN}$ ; $V_{CSN}$ Measured Through $100\Omega$ Series Resistor                             | • | 5   | 14           | 20         | mV    |  |

| TIMER                   | Timer High Threshold             |                                                                                                          |   |     | 1.5          |            | V     |  |

|                         | Timer Low Threshold              |                                                                                                          |   |     | 1.0          |            | V     |  |

|                         | C/10 Mode Threshold (Rising)     |                                                                                                          | • | 0.4 | 0.5          | 0.6        | V     |  |

|                         | C/10 Mode Hysteresis             |                                                                                                          |   |     | 225          |            | mV    |  |

|                         | Timer Source/Sink Current        | V <sub>TIMER</sub> = 1.25V                                                                               | • | 8.5 | 10           | 11.5       | μА    |  |

| V <sub>STAT(L)</sub>    | Status Pins Enabled Voltage      | I <sub>STAT1</sub> = 1mA; I <sub>STAT2</sub> = 1mA<br>I <sub>STAT1</sub> = 5mA; I <sub>STAT2</sub> = 5mA | • |     | 0.15<br>0.75 | 0.4<br>2.5 | V     |  |

| I <sub>VFBMIN</sub>     | Instant-On Feedback Bias Current |                                                                                                          |   |     | 10           |            | nA    |  |

| I <sub>VFB</sub>        | Feedback Pin Bias Current        |                                                                                                          |   |     | 10           |            | nA    |  |

| I <sub>VIN_REG</sub>    | Input Regulation Bias Current    |                                                                                                          |   |     | 10           |            | nA    |  |

| I <sub>FB_GND</sub>     | Pin current (Disabled)           | V <sub>SHDN</sub> = 0V; V <sub>FB_GND</sub> = 55V                                                        |   |     | 10           |            | nA    |  |

| R <sub>NTC</sub>        | NTC Minimum Disable Resistance   |                                                                                                          | • | 250 | 400          |            | kΩ    |  |

| R <sub>FBG</sub>        | FBG Resistance to SGND           | I <sub>FBG</sub> = 1mA                                                                                   | • |     | 20           | 50         |       |  |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC4020 is tested under pulsed load conditions such that  $T_J \approx T_A$ . The LTC4020E is guaranteed to meet specifications from 0°C to 85°C junction temperature. Specifications over the –40°C to 125°C operating junction temperature range are assured by design, characterization, and correlation with statistical process controls. The LTC4020I is guaranteed over the full –40°C to 125°C operating junction temperature range. The junction temperature  $(T_J)$  is calculated from the ambient temperature  $(T_A)$  and power dissipation (PD) according

to the formula  $T_J = T_A + (PD \bullet \theta J_A)$ . Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal resistance and other environmental factors. This IC includes overtemperature protection that is intended to protect the device during momentary overload. Junction temperature will exceed 125°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

Note 3: ICC does not include switching currents.  $V_{BST1}$  =  $V_{BST2}$  =  $V_{INTVCC}$  and  $V_{SW1}$  =  $V_{SW2}$  = 0V for testing.

Note 4: See Typical Performance Characteristics

## TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = 25$ °C, unless otherwise noted.

**Shutdown Current vs Temperature** (IPVIN + ISENSVIN + ISENSTOP) 50 STANDBY MODE CURRENT (µA) 40 35 30 25 20 , -40-30-20-10 0 10 20 30 40 50 60 70 80 90 TEMPERATURE (°C) 4020 G04

(Percent of Programmed I<sub>CSMAX</sub>)

**Instant-On: Maximum Charge**

I<sub>BATQ</sub> (I<sub>BAT</sub> + I<sub>CSN</sub> + I<sub>CSP</sub>) vs Temperature PowerPath Switcher

## TYPICAL PERFORMANCE CHARACTERISTICS

T<sub>A</sub> = 25°C, unless otherwise noted.

Switching Frequency vs

**TG1 (Pin 1):**  $V_{IN}$  side (step-down) primary switch FET gate driver output.

**BST1 (Pin 2):** Boosted supply rail for  $V_{IN}$  side (step-down) switch FETs. Connect 1 $\mu$ F capacitor from this pin to SW1. Connect 1A Schottky diode anode to this pin, cathode to INTV<sub>CC</sub> pin.

**SENSGND (Pin 4):** Kelvin connection for PGND used for SENSBOT current sense reference.

**SENSBOT (Pin 5):** Ground Referred Current Sense Amplifier Input. Inductor current is monitored via a PGND referenced current sense resistor ( $R_{SENSEB}$ ), typically in series with the source of the  $V_{IN}$  side synchronous switch FET. Kelvin connect this pin to the associated sense resistor. Inductor current is limited to a maximum average value ( $I_{LMAX}$ ), and corresponds to 50mV across this sense resistor during normal operation.

$R_{SENSEB} = 0.05/I_{LMAX}$

Set  $R_{\text{SENSEB}} = R_{\text{SENSEA}}$ , as described in SENSTOP pin description.

**SENSTOP** (Pin 6):  $V_{IN}$  Referred Current Sense Amplifier Input. Inductor current is monitored via a  $V_{IN}$  referenced current sense resistor ( $R_{SENSEA}$ ), typically in series with the drain of the  $V_{IN}$  side primary switch FET. Kelvin connect this pin to the associated sense resistor. Inductor current is limited to a maximum average value ( $I_{LMAX}$ ), and corresponds to 50mV across this sense resistor during normal operation.

$R_{SENSEA} = 0.05/I_{LMAX}$

Set  $R_{\text{SENSEA}} = R_{\text{SENSEB}}$ , as described in SENSBOT pin description.

**SENSVIN (Pin 7):** Kelvin connection for input supply  $(V_{IN})$  used for SENSTOP current sense reference. Input power supply pin for most internal low current functions. Typical pin bias current is 0.25 mA.

**RT (Pin 8):** System Oscillator Frequency Control Pin. Connect resistor ( $R_{RT}$ ) from this pin to ground. Resistor value can range from  $50k\Omega$  (500khz) to  $500k\Omega$  (50khz).  $R_{RT} = 100k\Omega$  yields 250kHz operating frequency. See Applications Information.

**SHDN (Pin 9):** Precision Threshold Shutdown Pin. Enable threshold is 1.225V (rising), with 100mV of input hysteresis. When in shutdown, all charging functions are disabled and input supply current is reduced to 27.5 $\mu$ A. Typical SHDN pin input bias current is 10nA.

V<sub>IN REG</sub> (Pin 10): Input Voltage Regulation Reference. Battery charge current is reduced when the voltage on this pin falls below 2.5V. Connecting a resistor divider from  $V_{\text{IN}}$  to this pin enables programming of minimum operational V<sub>IN</sub> voltage for the battery charging function. This is used to program the peak power voltage for a solar panel, or to help maintain a minimum voltage on a poorly regulated input supply. This pin should not be used to program minimum operational V<sub>IN</sub> voltage with low impedance supplies. Should the input supply begin to collapse, the LTC4020 reduces the DC/DC converter input power such that programmed minimum V<sub>IN</sub> operational voltage is maintained. If the voltage regulation feature is not used, connect the  $V_{IN\ REG}$  pin to  $V_{IN}$  or  $INTV_{CC}.$  Typical V<sub>IN REG</sub> pin input bias current is 10nA. See Applications Information.

**MODE (Pin 11):** Charger Mode Control Pin. Short this pin to ground to enable a constant-current/constant-voltage (CC/CV) charging algorithm. Connect this pin to pin INTV<sub>CC</sub> to enable a 4-step, 3-stage lead-acid charging algorithm. Float this pin to force a constant-current (CC) charging function. See Applications Information section.

**STAT1 (Pin 12):** Open-collector status output, typically pulled up through a resistor to a supply voltage. This status pin can be pulled up to voltages as high as 55V when the pin is disabled, and can sink currents up to 1mA when logic low (<0.4V). Pull down currents as high as 5mA (absolute maximum) are supported for higher current applications, such as lighting LEDs.

If the LTC4020 is configured for a CC/CV charging algorithm, the STAT1 pin is pulled low while battery charge currents exceed 10% of the programmed maximum (C/10). The STAT1 pin is also pulled low during NTC faults. The STAT1 pin becomes high impedance when a charge cycle is terminated or when charge current is below the C/10 threshold.

If the LTC4020 is configured for a CC charging algorithm, the STAT1 pin is pulled low during the entire charging

cycle. The STAT1 pin becomes high impedance when the charge cycle is terminated.

If the LTC4020 is configured for a lead-acid charging algorithm, the STAT1 pin is used as a charge cycle stage indicator pin, and pulled low during the bulk and absorption charging stages. The pin is high impedance during the float charging period and during NTC or bad battery faults.

See Applications Information section.

**STAT2** (Pin 13): Open-collector status output, typically pulled up through a resistor to a supply voltage. This status pin can be pulled up to voltages as high as 55V when disabled, and can sink currents up to 1mA when enabled (<0.4V). Pull down currents as high as 5mA (absolute maximum) are supported for higher current applications, such as lighting LEDs.

If the LTC4020 is configured for a CC/CV charging algorithms, the STAT2 pin is pulled low during NTC faults or after a bad battery fault occurs.

If the LTC4020 is configured for a CC charging algorithms, the STAT2 pin is pulled low during NTC faults.

If the LTC4020 is configured for a lead-acid charging algorithm, the STAT2 pin is used as a charge cycle stage indicator pin, and pulled low during the bulk and float charging stages. The pin is high impedance during the absorption charging stage and during NTC or bad battery faults.

See Applications Information section.

**TIMER (Pin 14):** End-Of-Cycle Timer Programming Pin. If a timer based charging algorithm is desired, connect a capacitor ( $C_{TIMER}$ ) from this pin to ground. If no timer functions are desired, connect this pin to ground.

End-of-cycle time (in hours) is programmed with the value of  $C_{\text{TIMER}}$  following the equation:

$$T_{EOC} = C_{TIMER} \cdot 2.9 \times 10^{7}$$

;

During CC/CV or lead-acid charging algorithms, a bad battery fault is generated if the battery voltage does not reach the precondition threshold voltage within 1/8 of  $T_{EOC}$ , or:

$$T_{PRE} = C_{TIMER} \cdot 3.65 \times 10^6$$

.

A 0.1 $\mu$ F capacitor is typically used for CC/CV charging, which generates a 2.9 hour timer  $T_{EOC}$ , and a precondition limit time of 22 minutes. A 0.15 $\mu$ F or 0.22 $\mu$ F capacitor is typically used for a lead-acid charger, which generates a 4.4 or 6.4 hour absorption stage safety timeout respectively. See Applications Information section.

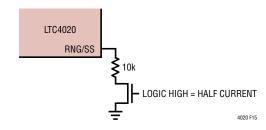

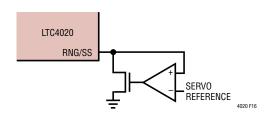

**RNG/SS (Pin 15):** Battery Charge Current Programming Pin. This pin allows dynamic adjustment of maximum charge current, and can be used to employ a soft-start function.

Setting the voltage on the RNG/SS pin reduces maximum charge current from the value programmed. The inductor current limit is reduced to the fraction of programmed current (as per the sense resistor, RCS) corresponding to the voltage set on the pin (in volts). This pin has an effective range from 0 to 1V.

For example, with 0.5V RNG/SS on the pin, the maximum inductor current will be reduced to 50% of the programmed value set by the sense resistor values.

$50\mu A$  is sourced from the RNG/SS pin, so maximum charge current can be programmed by connecting a single resistor (R<sub>RNG/SS</sub>) from RNG/SS to ground, such that the voltage dropped across the resistor is equivalent to the desired pin voltage:

$$V_{RNG/SS} = 50 \mu A \cdot R_{RNG/SS}$$

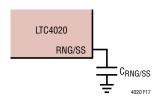

Soft-start functionality can be implemented by connecting a capacitor ( $C_{RNG/SS}$ ) from RNG/SS to ground, such that the time required to charge the capacitor is the desired soft-start interval ( $T_{SS1}$ ). The voltage that corresponds to full programmed inductor current on the RNG/SS pin is 1V, so the relation for this capacitor reduces to:

$$C_{RNG/SS} = 50 \mu A \cdot T_{SS1}$$

The RNG/SS pin is pulled low during periods when charging is disabled, including NTC faults, bad battery faults, and normal charge cycle termination. This allows for a graceful start after faults and when initiating new charge cycles, should soft-start functionality be implemented.

Both a soft-start capacitor and a programming resistor can be implemented in parallel.

RNG/SS voltage can also be manipulated using an active device, such as employing a pull-down transistor to disable charge current or to dynamically servo maximum charging current. Because this pin is internally pulled to ground during fault conditions, active devices with low-impedance pull up capability cannot be used.

See Applications Information section.

**NTC (Pin 16):** Battery Temperature Monitor Pin. Connect a  $10k\Omega$ ,  $\beta = 3380$  NTC thermistor from this pin to ground.

The NTC pin is the input to the negative temperature coefficient temperature monitoring circuit. This pin sources  $50\mu A$ , and monitors the voltage created across the  $10k\Omega$  thermistor. When the voltage on this pin is above 1.35V (0°C) or below 0.3V (40°C), charging is disabled and an NTC fault is signaled at the STAT1 and STAT2 status pins. If the internal timer is being used, the timer is paused, suspending the charging cycle until the NTC fault condition is relieved. There is approximately  $5^{\circ}C$  of temperature hysteresis associated with each of the temperature thresholds. The NTC function remains enabled while thermistor resistance to ground is less than  $250k\Omega$ . If this function is not desired, leave the NTC pin unconnected or connect a 10k resistor from the NTC pin to ground.

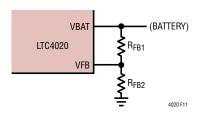

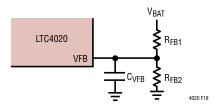

**VFB (Pin 17):** Battery Voltage Feedback Pin. Battery voltages are programmed through a feedback resistor divider placed from the BAT pin to FBG.

During CC/CV charging, the battery voltage references are:

Float Voltage  $(V_{FLOAT}) = 2.5V$

Trickle Charge Voltage  $(V_{TRK}) = 1.75V$

Auto-Restart Voltage (V<sub>RESTART</sub>) = 2.4375

During lead-acid charging, the battery voltage references are:

Absorption Voltage  $(V_{ABSOR}) = 2.5V$

Float Charge Voltage  $(V_{FLT}) = 2.3125V$

Trickle Charge Voltage  $(V_{TRK}) = 1.75V$

Bulk Recharge Voltage ( $V_{BULK}$ ) = 2.1875V

With  $R_{FB1}$  connected from BAT to VFB and  $R_{FB2}$  connected from VFB to FBG, the ratio of  $(R_{FB1}/R_{FB2})$  for the desired

programmed battery float voltage (CC/CV charging) or absorption voltage (lead-acid charging) follows the relation:

$$R_{FB1}/R_{FB2} = (V_{FLOAT/ABSORB})/2.5 - 2.5$$

(V)

**FBG (Pin 18):** Voltage Feedback Divider Return. This pin contains a low impedance path to signal ground, used as the ground reference for voltage monitoring feedback resistor dividers. When  $V_{\text{IN}}$  is not present or the LTC4020 is in shutdown, this pin becomes high impedance, eliminating current drain from the battery associated with the feedback resistor dividers.

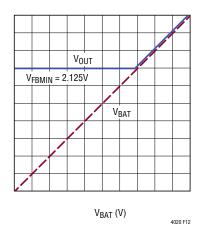

$V_{FBMIN}$  (Pin 19): Minimum voltage feedback pin for instanton operation. Minimum DC/DC converter output voltage ( $V_{OUTMIN}$ ) is programmed using this pin for instant-on functionality.  $V_{OUTMIN}$  is programmed through a feedback resistor divider placed from the CSP pin to FBG.

If the battery voltage is below the voltage level programmed using this pin, the LTC4020 controls the external PowerPath FET as a linear pass element, allowing the DC/DC converter output to achieve the minimum programmed voltage. Maximum battery charge current is reduced as the voltage across the PowerPath FET increases to control power dissipation.

The internal  $V_{FBMIN}$  voltage reference is 2.125V. With a resistor ( $R_{MIN1}$ ) connected from CSP to  $V_{FBMIN}$ , and a resistor ( $R_{MIN2}$ ) connected from  $V_{FBMIN}$  to FBG, the ratio of these resistors for the desired minimum converter output voltage follows the relation:

$$R_{MIN1}/R_{MIN2} = (V_{OUT(MIN)}/2.125) - 2.125$$

Using the same resistor values for battery voltage programming, or  $R_{FB1} = R_{MIN1}$  and  $R_{FB2} = R_{MIN2}$ , yields an instant-on voltage that is 85% of  $V_{FLOAT}$  (CC/CV charging) or  $V_{ABSORB}$  (lead-acid charging):

**BAT (Pin 20):** Battery Voltage Monitor Pin. This pin serves as the positive reference for the LTC4020 ideal diode function.

If a system load occurs that is large enough to collapse the DC/DC converter output while charging is terminated or disabled, and the battery is disconnected (PowerPath FET is high impedance), the ideal diode function engages the PowerPath. This function powers the system load from

4020

the battery, and modulates the PowerPath FET gate such that the system output voltage is maintained with 14mV across the PowerPath FET, provided the voltage drop due to  $R_{DS(ON)} < 14$ mV. This allows large loads to be accommodated without excessive power dissipation in the body diode of the PowerPath FET.

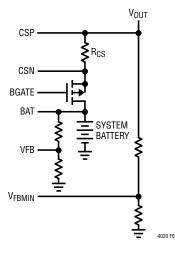

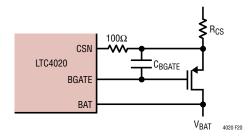

BGATE (Pin 21): PowerPath FET Gate Driver Output.

This pin is controls the multiple functions of the Power-Path FET.

This pin is pulled low during a normal charging cycle, minimizing the FET series impedance between the DC/DC converter output and the battery.

The BGATE pin is also forced low when the DC/DC converter is disabled, maintaining a low impedance connection to power the system from the battery.

When BGATE is pulled low, CSP BGATE is limited internally to 9.5V, so if CSP > 9.5V, BGATE is maintained by an internal clamp at CSP - BGATE = 9.5V. The BGATE pin must be near ground or at the clamp voltage for C/10 detection to occur.

If the battery voltage is lower than the instant-on threshold (see  $V_{FBMIN}$ ), BGATE servos the PowerPath FET impedance such that a voltage drop between the CSN pin and the BAT pin is created while battery charging continues. If the  $V_{CSN}-V_{BAT}$  voltage exceeds 0.4V, maximum charge current is reduced to decrease power dissipation in the PowerPath FET.

When the DC/DC converter is enabled, but the battery charge cycle has terminated, BGATE is pulled high to disconnect the battery from the converter output. The battery is also disconnected in the same manner during NTC faults. The ideal diode function is active during these periods, however, so if a system load occurs that is larger than what the DC/DC converter can accommodate, the battery can supply the required current, and the BGATE pin will be servo controlled to force a voltage drop of only 14mV across the PowerPath FET. The ideal diode function is disabled during bad battery faults.

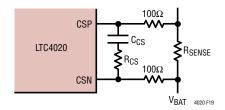

If a PowerPath FET is not being used, such as with a leadacid charging application, connect a 0.1nF capacitor from BGATE to CSN. **CSN (Pin 22):** Battery Charger Current Sense Negative Input. Connect this pin to the negative terminal of the battery charge current sense resistor (RCS) through a  $100\Omega$  resistor. Connect a filter capacitor between this pin and the CSP pin for ripple reduction. See Applications Information section.

The value of the sense resistor is related to the maximum battery charge current  $(I_{CSMAX})$ :

$$R_{CS} = 0.05/I_{CSMAX}$$

This pin also serves as the negative reference for the LTC4020 ideal diode function (see BAT).

**CSP** (Pin 23): Battery Charger Current Sense Positive Input. Connect this pin to the positive terminal of the battery charge current sense resistor ( $R_{CS}$ ) through a  $100\Omega$  resistor. Connect a filter capacitor between this pin and the CSN pin for ripple reduction. See Applications Information section.

The value of the sense resistor is related to the maximum battery charge current ( $I_{CSMAX}$ ) such that:

$$R_{CS} = 0.05/I_{CSMAX}$$

**CSOUT (Pin 24):** Current Sense Amplifier Output and Charge Current Monitor. Connect 100pF capacitor to ground.

Pin output impedance is  $100k\Omega$ , so any loading for monitors must be high impedance. The sense output voltage follows the relation:

$$V_{CSOUT} = 0.25 + 20 \bullet (V_{CSP} - V_{CSN})$$

CSOUT is only active while battery charger functions are operating. CSOUT pin voltage is pulled to 0V after charge cycle termination or during fault conditions.

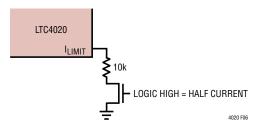

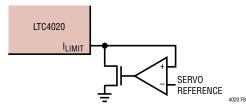

**I<sub>LIMIT</sub>** (**Pin 25**): Switched Inductor Maximum Current Programming Pin. This pin allows dynamic adjustment of DC/DC converter maximum average inductor current, and can be used to employ a soft-start function.

Setting the voltage on the  $I_{LIMIT}$  pin reduces maximum average inductor current from the value programmed. The inductor current limit is reduced to the fraction of programmed current (as per the sense resistors) corresponding to the voltage set on the pin (in volts). This pin has an effective range from 0 to 1V.

For example, with 0.5V on the pin, the maximum inductor current will be reduced to 50% of the programmed value set by the sense resistor values.

$50\mu A$  is sourced from this pin, so maximum charge current can be programmed by connecting a single resistor (R<sub>ILIMIT</sub>) from I<sub>LIMIT</sub> to ground, such that the voltage dropped across the resistor is equivalent to the desired pin voltage:

Soft-start functionality can be implemented by connecting a capacitor ( $C_{\text{ILIMIT}}$ ) from  $I_{\text{LIMIT}}$  to ground, such that the time required to charge the capacitor is the desired soft-start interval ( $T_{\text{SS2}}$ ). The voltage that corresponds to full inductor current on the  $I_{\text{LIMIT}}$  pin is 1V, so the relation for this capacitor reduces to:

$$C_{ILIMIT} = 50 \mu A \cdot T_{SS2}$$

I<sub>LIMIT</sub> voltage can also be manipulated using an active device, such as employing a pull-down transistor to disable DC/DC converter current or to dynamically servo maximum current. Because this pin is internally pulled to ground during portions of the converter power-up cycle, active devices with low impedance pull-up capability cannot be used.

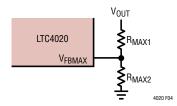

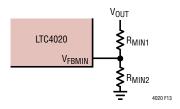

**V<sub>FBMAX</sub>** (**Pin 26**): DC/DC Converter Output Feedback Pin. Maximum DC/DC converter output voltage (V<sub>OUTMAX</sub>) is programmed using this pin. When a battery charge cycle is terminated or disabled, and the battery is disconnected (PowerPath FET is high impedance), the converter output will servo to this maximum voltage.

The internal  $V_{FBMAX}$  voltage reference is 2.75V. With a resistor ( $R_{MAX1}$ ) connected from CSP to  $V_{FBMAX}$  and a resistor ( $R_{MAX2}$ ) connected from  $V_{FBMAX}$  to FBG, the ratio of  $R_{MAX1}/R_{MAX2}$  for the desired maximum DC/DC converter output voltage follows the relation:

$$R_{MAX1}/R_{MAX2} = (V_{OUTMAX}/2.75) - 2.75$$

Using the same resistor values for battery voltage programming, or  $R_{FB1} = R_{MAX1}$  and  $R_{FB2} = R_{MAX2}$ , yields an instant-on voltage that is 110% of  $V_{FLOAT}$  (CC/CV charging) or  $V_{ABSORB}$  (lead-acid charging):

**ITH (Pin 27):** DC/DC Converter Voltage Loop Compensation Pin. See Applications Information section for compensation component selection details.

**VC (Pin 28):** DC/DC Converter Current Loop Compensation Pin. See Applications Information section for compensation component selection details.

**BST2 (Pin 30):** Boosted supply rail for  $V_{OUT}$  side (stepup) switch FETs. Connect a 1µF capacitor from this pin to SW2. Connect a 1A Schottky diode anode to this pin, cathode to INTV<sub>CC</sub> pin.

**TG2 (Pin 31):**  $V_{OUT}$  side (step-up) synchronous switch FET gate driver output.

**SW2** (**Pin 32**): Switched node for step-up switches. Connect the switched inductor to this pin. Connect the primary switch FET drain and synchronous switch FET source to this pin.

**BG2 (Pin 33):** V<sub>OUT</sub> side (step-up) primary switch FET gate driver output.

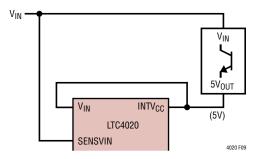

INTVCC (Pin 34): Boosted Driver Refresh Supply. This supply is regulated to 5V and is current limited to 150mA. Connect a 2.2µF ceramic capacitor from this pin to PGND. Boosted supply refresh diode cathodes are connected to this pin. Using this pin to power external 5V circuitry is not recommended.

**PGND (Pin 35):** Switch high current return path for step-up primary and step-down synchronous switches.

**PVIN (Pin 36):** High Current Input Supply Pin. Connect  $10\mu\text{F}$  decoupling capacitor from this pin to PGND. The PV<sub>IN</sub> pin provides input supply current for the INTV<sub>CC</sub> internal 5V linear regulator.

**BG1 (Pin 37):**  $V_{IN}$  side (step-down) synchronous switch FET gate driver output.

**SW1 (Pin 38):** Switched node for step-down switches. Connect the switched inductor to this pin. Connect the primary switch FET source and synchronous switch FET drain to this pin.

**SGND (Pins 3, 29, Exposed Pad 39):** Signal Ground Reference. Connect to the output decoupling capacitor negative terminal and battery negative terminal. The exposed pad (39) must be soldered to PCB ground (SGND) for electrical connection and rated thermal performance.

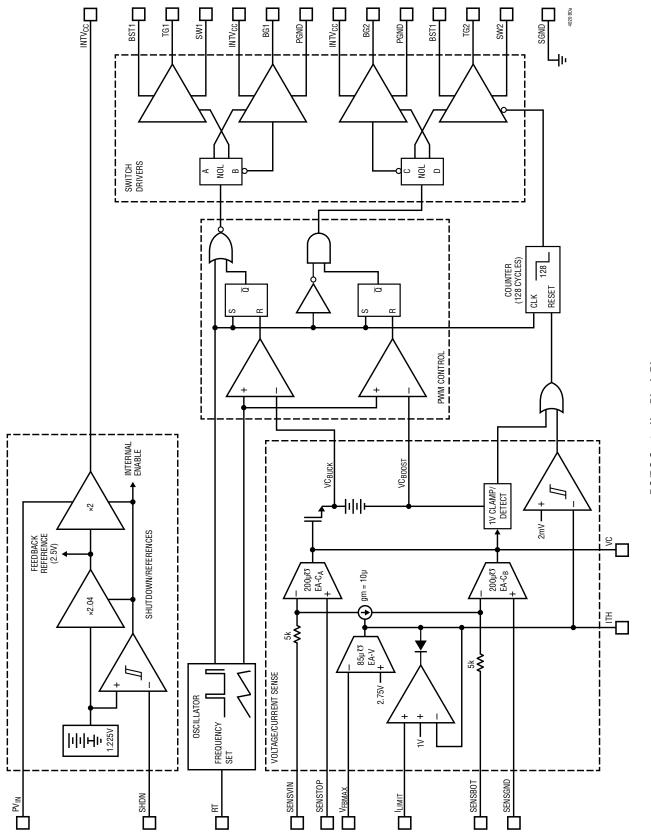

## **BLOCK DIAGRAM**

DC/DC Controller Block Diagram

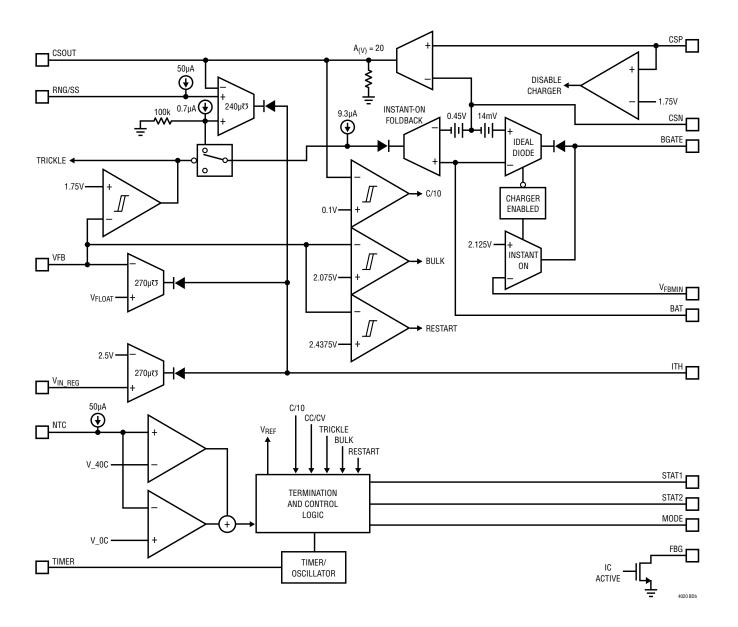

### **BLOCK DIAGRAM**

**Battery Charger Block Diagram**

#### **Functional Overview**

The LTC4020 is an advanced high voltage power manager and multi-chemistry battery charger designed to efficiently transfer power from a variety of sources to a system power supply rail and a battery.

The LTC4020 contains a step-up/step-down DC/DC controller that allows operation with battery and system voltages that are above, below, or equal to the input voltage ( $V_{IN}$ ). A precision threshold shutdown feature allows incorporation of input voltage UVLO functionality using a simple resistor divider. When in low current shutdown mode, the IC input supply bias is reduced to only 27.5 $\mu$ A.

The LTC4020 charger is programmable to produce optimized charging profiles for a variety of battery chemistries. The LTC4020 can provide a constant-current/constant-voltage charge characteristic with either C/10 or timed termination for use with lithium based battery systems, a constant-current characteristic with timed termination, or an optimized 4-step, 3-stage lead-acid charge profile.

Maximum battery charge current is programmable using a sense resistor, and a charge current range adjust pin allows dynamic adjustment of maximum charge current. A switcher core current limit adjust pin also allows dynamic limiting of power available to the system by virtue of limiting maximum current in the DC/DC converter inductor.

The LTC4020 preconditions heavily discharged batteries by reducing charge current to one-fifteenth of the programmed maximum. Once the battery voltage climbs above an internally set threshold, the IC automatically increases maximum charging current to the full programmed value. A bad battery detection function signals a fault and suspends charging should a battery not respond to preconditioning.

Battery temperature is monitored using a thermistor measurement system. This feature monitors battery temperature during the charging cycle, suspending the charge cycle and signaling a fault condition if the battery temperature moves outside a safe charging range of 0°C to 40°C. The charge cycle automatically resumes when the temperature returns to that safe charging range.

Instant-on PowerPath architecture ensures that an application is powered immediately after an external voltage is applied, even with a completely dead battery, by prioritizing power to the application. Since the controller output ( $V_{OUT}$ ) and the battery (BAT) are sometimes decoupled, the LTC4020 includes an ideal diode controller, which guarantees that ample power is always available to  $V_{OUT}$  if there is insufficient power available from the DC/DC converter. Should there be no input power available ( $V_{IN}$ ), the LTC4020 makes a low impedance connection from the battery to  $V_{OUT}$  though the PowerPath FET. Battery life is maximized during periods of input supply disconnect by reducing the LTC4020 battery standby current to less than  $10\mu A$ .

The LTC4020 contains two digital open-collector outputs that provide charger status and signal fault conditions. These binary coded pins signal battery charging, standby or shutdown modes, battery temperature faults, and bad battery faults.

## DC/DC Converter Operation (See Block Diagrams)

The LTC4020 uses a proprietary average current mode DC/DC converter architecture.

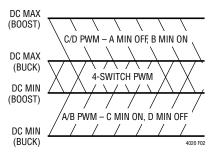

As shown in Figure 1, when  $V_{IN}$  is higher than  $V_{OUT}$  during step-down (buck) operation, switches A (driven by pin TG1) and B (driven by pin BG1) perform the PWM required for accommodating power conversion. Ideally, switch D (driven by pin TG2) would conduct continuously and switch C (driven by pin BG2) would stay off, making PWM switching action much like that in a synchronous buck topology. Switch D uses a bootstrapped driver, however, so switch C conducts for a minimum on time of 150nS each cycle to refresh the driver and switch D is disabled to accommodate this refresh time. A 75ns non-overlap period, separates the conduction of the two switches, preventing shoot-through currents.

When  $V_{IN}$  is lower than  $V_{OUT}$  during step-up (boost) operation, switches C and D perform the PWM required for accommodating power conversion. Ideally, switch A would conduct continuously and switch B would stay off, making

PWM switching action much like that in a synchronous boost topology. Since switch A also uses a bootstrapped drive, however, the B switch conducts for 100nS during this refresh period. A 75ns non-overlap period, separates the conduction of the two switches, preventing shoot-through currents.

If  $V_{IN}$  is close to  $V_{OUT}$ , the controller operates in 4-switch (buck-boost) mode, where both switch pairs PWM simultaneously to accommodate conversion requirements.

The LTC4020 senses the DC/DC converter output voltage using a resistor divider feedback network that drives the  $V_{FBMAX}$  pin. The difference between the voltage on the  $V_{FBMAX}$  pin and an internal 2.75V reference is converted into an error current by the voltage loop transconductance amplifier (EA-V). This error current is integrated by a compensation network to produce a voltage on pin ITH. The ITH compensation network is designed to optimize the response of the converter to changes in load current while the converter is in regulation. At regulation, the ITH pin will servo to a value that corresponds to the average inductor current of the DC/DC converter.

Inductor current is monitored through two like value sense resistors, placed in series with each of the  $V_{\text{IN}}$  side converter switches, A and B. The sum of these sensed currents yields a reasonably accurate continuous representation of inductor current.

The voltage produced on the ITH pin is translated into an offset at the input of the two current sense amplifiers. The difference between this offset voltage and the sum of the voltages is sensed on the SENSTOP and SENSBOT pins, then is converted to error currents by the current sense transconductance amplifiers (EA- $C_A$  and EA- $C_B$ ). These error currents are summed and integrated by a compensation network to produce a voltage on the pin VC. This compensation network is designed to optimize the response of the converter duty cycle to required changes in inductor current.

The VC pin voltage is compared to an internally generated ramp, and the output of this comparison controls the duty cycle of the charger's switches.

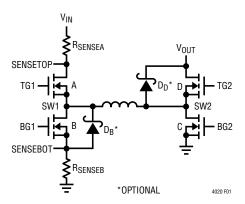

Figure 1 shows a simplified diagram of the four power switches and their connections to the IC, inductor,  $V_{IN}$ ,  $V_{OUT}$ , ground, and current sense elements.

Figure 1. Converter Switch Diagram

Figure 2. Operating Regions vs Duty Cycle (DC)

Reverse current protection is accomplished through disabling the  $V_{OUT}$  side synchronous switch (D) during initial power-up, when the converter is in step-up duty cycle limit, and when ITH falls to a voltage that corresponds to <1/25 of programmed  $I_{LMAX}$ . Once these conditions subside, the D switch remains disabled for an additional 128 clock cycles.

LINEAR

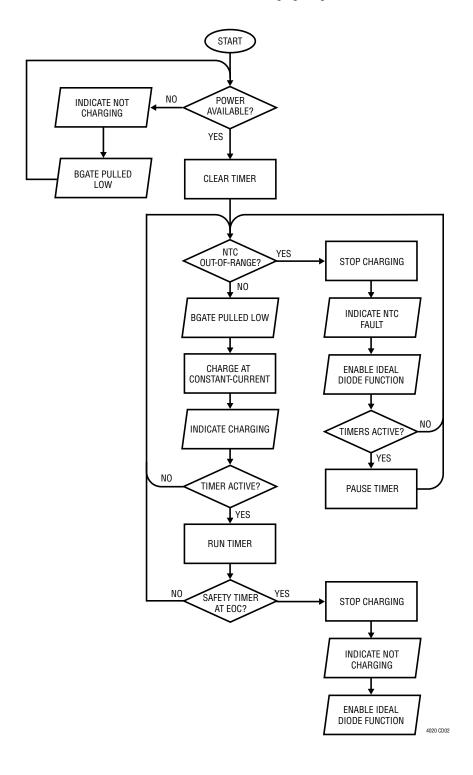

## Battery Charger Operation (See Block Diagrams)

During the majority of a normal battery charge cycle, the LTC4020 makes a low impedance connection between the battery and the DC/DC converter output through the PowerPath FET, as in Figure 3. This PFET is controlled by the LTC4020 through modulation of the BGATE pin, which is connected to the FET gate. When charging is disabled, the FET is disabled, disconnecting the battery from the converter output by pulling the gate of the PowerPath FET high via the BGATE pin. The converter output is regulated by V<sub>FBMAX</sub> while the FET is disabled. When normal charger operation resumes, the gate is pulled low. As the BGATE pin is a slow-moving node, C/10 detection is disabled until the BGATE pin approaches its normal operating voltage, which prevents premature C/10 detection during reconnection of the battery. The slow movement of BGATE can also cause the converter output to regulate to V<sub>FBMAX</sub> for a short time during start-up until the FET is enabled. This FET is also linearly controlled during low battery conditions to enable the instant-on function, where the converter output can be separated from a heavily discharged battery to power the rest of the system before the battery voltage responds to charging. C/10 detection is also disabled when the charger is operating in instant-on mode. This FET is also automatically configured as a 14mV ideal diode, which provides a low loss path from the battery to the output when system loads require power from the battery while the battery is disconnected from the converter output.

Figure 3. Battery Charger PowerPath Diagram

The battery charger takes control of the DC/DC converter operation by modulating the ITH pin voltage in response to sensed battery charge current, battery voltage, and input voltage. The converter thus provides exactly the amount of power required to satisfy both the system load and battery charger requirements.

Battery charge current is monitored via an external sense resistor connected to the pins CSP and CSN. The voltage across this resistor is amplified internally by a factor of 20, which is output onto pin CSOUT. This output voltage rides on top of a constant 250mV offset. The CSOUT pin voltage drives an internal transconductance amplifier that servos the DC/DC converter's ITH pin voltage in response to the current requirements of a charging battery. CSOUT voltage is also used internally as a charge current monitor to detect <C/10 current thresholds.

Battery voltage is monitored via the VFB pin. This voltage drives a transconductance amplifier that servos the DC/DC converter ITH pin voltage in response to voltage developed on a charging battery. The transition from constant-current (CC) to constant-voltage (CV) charging modes is also detected using this transconductance amplifier. The VFB voltage is used for all battery voltage monitor thresholds, each being defined as a percentage of the internal 2.5V reference voltage.

Input voltage regulation is implemented via the  $V_{IN\_REG}$  pin for use with poorly regulated or high impedance supplies. This pin drives a transconductance amplifier that reduces the ITH pin voltage in response to voltage sensed on the  $V_{IN\_REG}$  pin falling through 2.5V. This transconductance amplifier remains active even while battery charging is disabled, so the input regulation feature continues to operate regardless of the state of a charge cycle.

The LTC4020 contains an internal charge cycle timer that is used for time based control of a charge cycle. This function is enabled by connecting a capacitor to the TIMER pin. Grounding this pin disables all timer functions. The timer is used to terminate a successful CC or CC/CV charge cycle after a programmed end-of-cycle ( $T_{EOC}$ ) time. This timer is also used to transition a lead-acid charger to float charging if charge current does not fall adequately during the absorption phase of the charge cycle within the programmed  $T_{EOC}$  time.

40201

Use of the timer function also enables bad battery detection during CC/CV or lead-acid charging. This fault condition is achieved if the battery does not respond to preconditioning ( $V_{FB} < 1.75V$ ), such that the charger remains in (or enters) precondition mode after one-eighth of the programmed  $T_{EOC}$  time. A bad battery fault halts the charging cycle, and the fault condition is reported on the status pins.

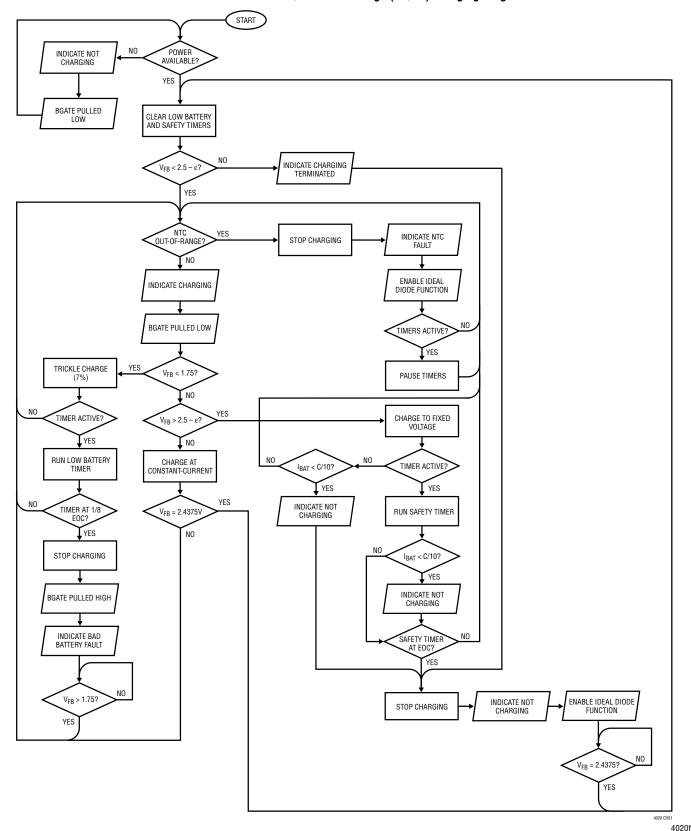

#### CC/CV Charging Overview (MODE = 0V)

To program the LTC4020 for CC/CV charging, connect the MODE pin to ground. This mode is commonly used for Li-Ion, Li-Polymer, and LiFePO<sub>4</sub> battery charging.

If the voltage on the VFB pin is below 1.75V, the LTC4020 engages precondition mode, which provides low level charge currents to gently increase voltage on heavily discharged batteries. During preconditioning, the maximum charge current is reduced to one-fifteenth of the programmed value as set by  $R_{CS}$ , the battery charge current programming resistor. Full charge current capability is restored once the voltage on VFB rises above 1.75V. Full charge current capability remains until the VFB pin approaches the 2.5V float voltage. This is the constant-current (CC) portion of the charge cycle.

When the voltage on the VFB pin approaches the 2.5V float voltage, the charger transitions into constant-voltage (CV) mode, and charge current is reduced from the maximum programmed value. If timer termination is used, the safety timer period starts when CV mode is initiated, and the charge cycle will terminate when the timer achieves end-of-cycle ( $T_{EOC}$ ). This timer is typically programmed to achieve  $T_{EOC}$  in three hours, but can be configured for any amount of time by setting an appropriate timing capacitor value ( $T_{TIMFR}$ ).

During CV mode, the required charge current is steadily reduced as the battery voltage is maintained such that the voltage on the VFB pin remains close to 2.5V. If the charger is configured for C/10 termination, when the battery charge current falls below one-tenth of the programmed maximum current (<C/10), the charge cycle will terminate and the charger indicates not charging on the status pins.

When timer termination is used, the charger continues to operate with charging current less than one-tenth of the

programmed maximum current. The STAT1 status pin, however, responds to the <C/10 current level regardless of termination scheme, so the IC will indicate a not charging status when the charging current is below the C/10 current level. The charge cycle will continue, however, and the charger will source <C/10 current into the battery. Programmed float voltage is maintained while the charger tops-off the battery with low currents until the programmed  $T_{EOC}$  time has elapsed, at which time the charge cycle will terminate, charge current flow into the battery will be disabled, and the battery will be disconnected from the converter output.

After termination, if the battery discharges such that the voltage on the VFB pin drops to 2.4375V, or 97.5% of the programmed float voltage, a new charge cycle is automatically initiated.

|              | TYPICAL CC/CV CHARGE CYCLE VOLTAGES (PER CELL) |       |  |  |

|--------------|------------------------------------------------|-------|--|--|

|              | Li-lon LiFePO <sub>4</sub>                     |       |  |  |

| Precondition | 2.94V                                          | 2.52V |  |  |

| Float        | 4.2V                                           | 3.6V  |  |  |

| Recharge     | 4.095V                                         | 3.51V |  |  |

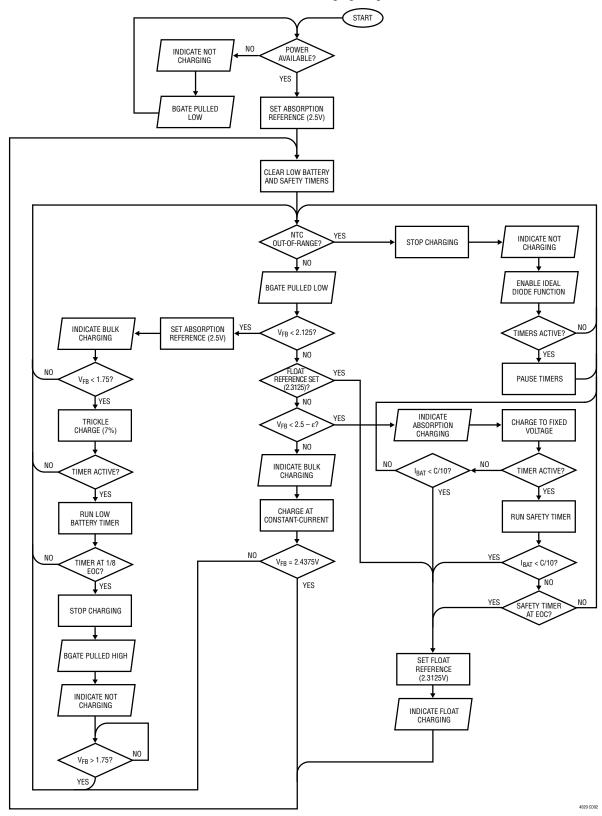

#### Lead-Acid Charging Overview (MODE = INT\_VCC)

To program the LTC4020 for lead-acid charging, connect the MODE pin to the  $INTV_{CC}$  pin. The LTC4020 supports a 4-step, 3-stage lead-acid charging profile.

The first step of the charging profile provides low level charge current to gently increase voltage on heavily discharged batteries. If the voltage on VFB is below 1.75V, which corresponds to just over 10V for a 6-cell (12V) battery, the maximum charge current is reduced to one-fifteenth of the programmed value as set by RCS. Once the VFB voltage rises above 1.75V, full charge current capability is restored, and the bulk charging stage begins.

The bulk charging stage of the charge profile, which is the first stage of 3-stage battery charging, is a constant-current charging stage, with the maximum programmed charge current forced into the battery. This continues until the battery voltage rises such that the VFB pin approaches the 2.5V absorption reference voltage.

LINEAR TECHNOLOGY

As the bulk charging stage completes and the voltage on the VFB pin rises to approach 2.5V, the charger transitions into the absorption stage, which is the 2nd stage of 3-stage battery charging. During the absorption stage, the required charge current is steadily reduced as the battery voltage approaches the absorption voltage. This is a constant-voltage charging stage, as the battery voltage is maintained such that the VFB pin remains close to the 2.5V absorption reference voltage. It is during this stage that the battery stored charge increases to 100% capacity. The 2.5V absorption reference typically corresponds to 14.4V for a 6-cell battery.

When the absorption stage charge current is reduced to one-tenth of the programmed maximum current, the charger will initiate the third stage in the charge profile, the float charging stage. The safety timer can be used with a lead-acid charger to limit the duration of the absorption stage of the charging profile. The timer is initiated at the start of the absorption stage, and forces the charger into float if the charge current does not fall to the required one-tenth of the programmed maximum current during the absorption stage before the timer reaches  $T_{EOC}$ . A  $0.15\mu F$  or  $0.22\mu F$  capacitor on the TIMER pin is typically used, which generates a 4.4 or 6.4 hour absorption stage safety timeout respectively.

Once the float charging stage is initiated, the battery reference voltage is reduced to 92.5% of the absorption voltage, or 2.3125V. The battery voltage is maintained at a voltage corresponding to this reference voltage, and maximum charge current is reduced to one-fifteenth of the programmed maximum. This level corresponds to 13.3V for a 6-cell battery.

Once float charging is achieved, the LTC4020 charger remains active and will attempt to maintain the float voltage on the battery indefinitely. During float charging, if a load on the battery exceeds the maintenance charge current of one-fifteenth of the programmed maximum, the battery voltage will begin to discharge. If a load discharges the battery such that the voltage on VFB falls to 2.1875V, corresponding to 12.6V for a 6-cell battery, the LTC4020 restarts the full 3-stage charging cycle by reinitiating the bulk charging stage. Bulk charging is engaged by resetting the internal VFB reference to the 2.5V absorption voltage

reference and increasing the charge current capability to the programmed maximum.

|              | TYPICAL LEAD-ACID CHARGE CYCLE VOLTAGES (12V System) |

|--------------|------------------------------------------------------|

| Precondition | 10.1V                                                |

| Absorption   | 14.4V                                                |

| Float        | 13.3V                                                |

| Bulk Restart | 12.6V                                                |

#### CC Charging Overview (MODE = NC)

To program the LTC4020 for CC charging, leave the MODE pin unconnected. This mode can be used for charging NiCd and NiMH batteries, supercap charging, or in any other application where a timed current source is desired. CC mode can also be used when the voltage dependent precondition mode is not desired.

In CC mode, the LTC4020 will maintain full programmed charge current capability for the duration of the timer period. The trickle charge function is disabled, although maximum charge current will be reduced during lower deck operation if there is excessive voltage (>0.3V) imposed across the PowerPath FET. The charger will terminate the charge cycle and the PowerPath FET will become high-impedance once timer EOC is reached.

While the charge cycle is designed to be voltage independent, a maximum  $V_{BAT}$  voltage can be programmed corresponding to VFB = 2.5V, allowing constant-voltage functionality at that level if desired.

Once the timer reaches  $T_{EOC}$  and the charge cycle terminates, input power or SHDN must be cycled to initiate another charge cycle. If the timer function is disabled (TIMER = 0V), the current source function remains active indefinitely.

Note: For nickel-chemistry batteries (e.g. NiCd or NiMH), the possibility of overcharging must be considered. A typical method is to charge with low currents for a long period of time. NiCd and NiMH batteries can absorb a C/300 charge rate indefinitely. Shorter duration charging is possible using a timed current source charge algorithm. It is recommended to ensure a depleted battery before charging, then subsequently charge the battery to no more than 125% capacity. For example, a depleted 2000mAh NiMH battery is charged with 2.5A for one hour.

#### DC/DC CONVERTER SECTION

#### **Output Voltage Programming**

The LTC4020 DC/DC converter maximum output voltage, or voltage safety limit, is set by an external feedback resistive divider, providing feedback to the  $V_{FBMAX}$  pin. This divider sets the output voltage that the converter will servo to when the PowerPath FET is high impedance, which occurs after charge cycle termination or during a charge cycle fault.

Figure 4. V<sub>OUT</sub> Safety Limit Programming

The resultant feedback signal is compared with the internal 2.75V voltage reference by the converter error amplifier. The output voltage is given by the equation:

$$V_{OUT} = 2.75 \text{V} \cdot \left(1 + \frac{R_{MAX1}}{R_{MAX2}}\right)$$

where  $R_{MAX1}$  and  $R_{MAX2}$  are defined as in Figure 4.

The values for  $R_{MAX1}$  and  $R_{MAX2}$  are typically the same as those used for the divider that programs battery voltage (to the VFB pin; see Battery Charger section), to yield a DC/DC converter maximum regulation voltage, or safety limit, that is 10% higher than the battery charge voltage.

## $R_{SENSEA},\,R_{SENSEB}\!\!:$ DC/DC Converter Current Programming

The LTC4020 performs inductor current sensing via two resistors connected in series with the  $V_{IN}$  side switches (see Figure 1). The high side sense resistor ( $R_{SENSEA}$ ) is connected between  $V_{IN}$  and the drain of the top side switch FET (A). Both nodes on the sense resistor must be Kelvin connected to the IC via the pins SENSVIN and SENSTOP. Likewise, the low side sense resistor ( $R_{SENSEB}$ ) is connected between the source of the bottom side switch FET (B) and PGND. Both nodes on the sense resistor must be Kelvin connected to the IC, via the pins SENSBOT and SENSGND.

Both of these sense resistors must be of equal value, and that value programs the switched inductor maximum average current in the DC/DC converter inductor ( $I_{LMAX}$ ) such that:

$$R_{SENSEA} = R_{SENSEB} = \frac{0.05}{I_{LMAX}}$$

When the converter is stepping down, or operating in buck mode, the inductor current will be roughly equivalent to the converter output current. Input supply current ( $I_{IN}$ ) will be less than the inductor current ( $I_{I}$ ), such that:

$$I_L \sim I_{IN} \bullet \left( \frac{V_{IN}}{V_{OUT}} \right)$$