# HOLT

# HI-8450, HI-8451, HI-8454, HI-8455 Single / Quad ARINC 429 Line Receivers with

March 2018

# Integrated DO-160G Level 3 Lightning Protection

# **GENERAL DESCRIPTION**

Holt's family of ARINC 429 line receivers include internal lightning protection circuitry which ensures compliance with RTCA/DO-160G, Section 22 Level 3 Pin Injection Test Waveform Set A (3 & 4), Set B (3 & 5A) and Set Z (3 & 5B) without the use of any external components. Pin surge levels for Level 3 are summarized below. The HI-8450 and HI-8451 are single ARINC 429 line receivers available in compact 8-pin SOIC packages. The HI-8454 and HI-8455 contain 4 independent ARINC 429 line receivers.

| Waveform<br>3 | Waveform<br>4 | Waveform<br>5A | Waveform<br>5B |

|---------------|---------------|----------------|----------------|

| VOC/ISC       | VOC/ISC       | VOC/ISC        | VOC/ISC        |

| 600V/24A      | 300V/60A      | 300V/300A      | 300V/300A      |

The devices are designed to operate from either a 5V or 3.3V supply. Each receiver channel translates incoming ARINC 429 data bus signals to a pair of TTL / CMOS outputs.

The TESTA and TESTB inputs bypass the analog inputs for testing purposes. They force the receiver outputs to the specified ZERO, ONE or NULL state. The ARINC inputs are ignored when the devices are in test mode.

The HI-8451 and HI-8454 produce low outputs when the TESTA and TESTB inputs are held high, whereas the HI-8450 produces high impedance outputs when the TESTA and TESTB inputs are held high. The HI-8455 does not have TEST inputs and these pins may be considered no-connect (NC).

The parts are available in Industrial  $-40^{\circ}$ C to  $+85^{\circ}$ C, or Extended,  $-55^{\circ}$ C to  $+125^{\circ}$ C temperature ranges. Optional burn-in is available on the extended temperature range.

# FEATURES

- Internal lightning protection circuitry ensures compliance with RTCA/DO-160G, Section 22 Level 3 Pin Injection Test Waveform Set A (3 & 4), Set B (3 & 5A) and Set Z (3 & 5B)

- Direct connection to ARINC 429 bus with no external components

- 3.3V or 5.0V single supply operation

- Test inputs bypass analog inputs and force digital outputs to a one, zero, or null state (not available on HI-8455)

- · Industrial and Extended temperature ranges

- Burn-in available

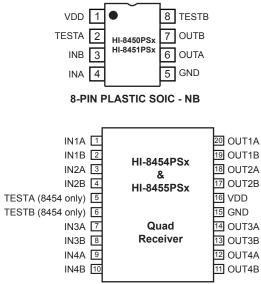

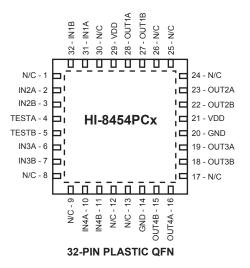

# **PIN CONFIGURATION (TOP VIEW)**

20-PIN PLASTIC TSSOP PACKAGE

#### Table 1. Function Table

| ARINC<br>INPUTS<br>INA - INB | TESTA | TESTB | OUTA                | OUTB                |

|------------------------------|-------|-------|---------------------|---------------------|

| -2.5 to +2.5V                | 0     | 0     | 0                   | 0                   |

| < -6.5V                      | 0     | 0     | 0                   | 1                   |

| > +6.5V                      | 0     | 0     | 1                   | 0                   |

| x                            | 0     | 1     | 0                   | 1                   |

| x                            | 1     | 0     | 1                   | 0                   |

| x                            | 1     | 1     | 0 (1)               | 0 (1)               |

| x                            | 1     | 1     | HI-Z <sup>(2)</sup> | HI-Z <sup>(2)</sup> |

Note (1): HI-8451 and HI-8454 only.

Note (2): HI-8450 only.

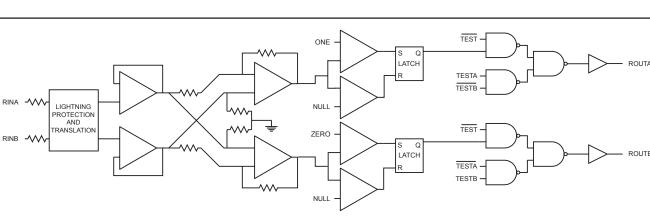

## FUNCTIONAL DESCRIPTION

Figure 1 shows the general architecture of an ARINC 429 receiver. The receiver operates off the VDD supply only. The inputs RINA and RINB may be connected directly to the ARINC 429 bus. Internal lightning protection circuitry ensures compliance with RTCA/DO-160G, Section 22 Level 3 Pin Injection Test Waveform Set A (3 & 4), Set B (3 & 5A) and Set Z (3 & 5B) without the use of any external components.

After level translation, the inputs are buffered and become inputs to a differential amplifier. The amplitude of the differential signal is compared to levels derived from a divider between VDD and Ground. The nominal settings correspond to a One/Zero amplitude of 6.0V and a Null amplitude of 3.3V.

The status of the ARINC receiver input is latched. A Null input resets the latches and a One or Zero input sets the latches.

The logic at the output is controlled by the test signal which is generated by the logical OR of the TESTA and TESTB pins (not available on HI-8455). If TESTA and TESTB are both One, the outputs are pulled low (HI-8451 and HI-8454 only). This allows the digital outputs of a transmitter to be connected to the test inputs through control logic for system self-test purposes. In the case of HI-8450, if TESTA and TESTB are both One, the outputs are high impedance (HI-Z).

# **BLOCK DIAGRAMS**

Figure 1. Line Receiver Block Diagram

Figure 2. HI-8454 Block Diagram

HOLT INTEGRATED CIRCUITS 2

# **PIN DESCRIPTIONS**

| Symbol | Function     | Description                           |

|--------|--------------|---------------------------------------|

| IN1A   | ARINC INPUT  | Receiver 1 positive input             |

| IN1B   | ARINC INPUT  | Receiver 1 negative input             |

| IN2A   | ARINC INPUT  | Receiver 2 positive input             |

| IN2B   | ARINC INPUT  | Receiver 2 negative input             |

| TESTA  | LOGIC INPUT  | Test input (not available on HI-8455) |

| TESTB  | LOGIC INPUT  | Test input (not available on HI-8455) |

| IN3A   | ARINC INPUT  | Receiver 3 positive input             |

| IN3B   | ARINC INPUT  | Receiver 3 negative input             |

| IN4A   | ARINC INPUT  | Receiver 4 positive input             |

| IN4B   | ARINC INPUT  | Receiver 4 negative input             |

| OUT4B  | LOGIC OUTPUT | Receiver 4 "ZERO" output              |

| OUT4A  | LOGIC OUTPUT | Receiver 4 "ONE" output               |

| OUT3B  | LOGIC OUTPUT | Receiver 3 "ZERO" output              |

| OUT3A  | LOGIC OUTPUT | Receiver 3 "ONE" output               |

| GND    | POWER        | Ground supply voltage                 |

| VDD    | POWER        | +3.3V or +5V supply voltage           |

| OUT2B  | LOGIC OUTPUT | Receiver 2 "ZERO" output              |

| OUT2A  | LOGIC OUTPUT | Receiver 2 "ONE" output               |

| OUT1B  | LOGIC OUTPUT | Receiver 1 "ZERO" output              |

| OUT1A  | LOGIC OUTPUT | Receiver 1 "ONE" output               |

# **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (V <sub>DD</sub> ) |       | -0.3V to +7V    |

|-----------------------------------|-------|-----------------|

| Logic input voltage range         |       | -0.3V to +5.5V  |

|                                   |       | -120V to + 120V |

| ARINC input voltage               | AC    | 120Vrms @ 400Hz |

| Solder Temperature (reflow        | 260°C |                 |

| Storage Temperature               |       | -65°C to +150°C |

| ESD-HBM (JS-001-2012)             |       |                 |

| Logic and supply pins             |       | 2,000V          |

| ARINC 429 bus input pins          |       | 1,000V          |

| RTCA/DO-160G, Section 22 pin injection |            |  |  |  |  |

|----------------------------------------|------------|--|--|--|--|

| Waveform                               | Voc/Isc    |  |  |  |  |

| 3                                      | 1,000V/40A |  |  |  |  |

| 4                                      | 500V/100A  |  |  |  |  |

| 5A                                     | 500V/500A  |  |  |  |  |

| 5B                                     | 500V/500A  |  |  |  |  |

# RECOMMENDED OPERATING CONDITIONS

| Supply Voltages      |      |        |        |

|----------------------|------|--------|--------|

| V <sub>DD</sub>      | 3.0V | to     | +5.5V  |

| Temperature Range    |      |        |        |

| Industrial Screening | 40°  | C to   | +85°C  |

| Hi-Temp Screening    | 55°C | ; to - | +125°C |

NOTE: Stresses above absolute maximum ratings or outside recommended operating conditions may cause permanent damage to the device. These are stress ratings only. Operation at the limits is not recommended.

# **ELECTRICAL CHARACTERISTICS**

#### Table 3. DC Electrical Characteristics

$V_{_{DD}}$  = +5.0V ± 10% or +3.3V ± 10%, GND = 0V, T<sub>A</sub> = Operating Temperature Range (unless otherwise stated)

| Parameters        |                                        | Symbol           | Test Conditions            | Min | Тур | Мах  | Units |

|-------------------|----------------------------------------|------------------|----------------------------|-----|-----|------|-------|

| ARINC INPUTS      |                                        |                  |                            |     |     |      |       |

| Input Voltage     | ONE or ZERO                            | V <sub>DIN</sub> | Differential Input voltage | 6.5 | 10  | 13   | V     |

|                   | NULL                                   | V <sub>NIN</sub> | Differential Input voltage |     |     | 2.5  | V     |

|                   | Common mode                            | V <sub>COM</sub> | With respect to GND        |     |     | ±5.0 | V     |

| Input Resistance  | INA to INB                             | $R_{DIFF}$       | Supplies floating          | 30  |     |      | kΩ    |

|                   | Input to GND or $\rm V_{\rm \tiny DD}$ | R <sub>SUP</sub> | Supplies floating          | 15  |     |      | kΩ    |

| Input Hysteresis  |                                        | V <sub>HYS</sub> |                            | 0.5 | 1.0 |      | V     |

| Input Capacitance | ARINC differential                     | C <sub>AD</sub>  |                            |     | 5   | 10   | pF    |

|                   | ARINC single ended<br>to GND           | C <sub>AS</sub>  |                            |     |     | 10   | pF    |

# HI-8450, HI-8451, HI-8454, HI-8455

| Parameters                     |        | Symbol           | Test Conditions                                  | Min                  | Тур | Мах                                   | Units |

|--------------------------------|--------|------------------|--------------------------------------------------|----------------------|-----|---------------------------------------|-------|

| TEST INPUTS                    |        |                  |                                                  |                      |     | · · · · · · · · · · · · · · · · · · · |       |

| Logic Input Voltage            | High   | V <sub>IH</sub>  |                                                  | 80%V <sub>DD</sub>   |     |                                       | V     |

|                                | Low    | V <sub>IL</sub>  |                                                  |                      |     | $20\%V_{dd}$                          | V     |

| Logic Input Current            | Sink   | I <sub>IH</sub>  | $V_{IH} = V_{DD}$                                |                      |     | 200                                   | μA    |

|                                | Source | I <sub>IL</sub>  | $V_{IL} = 0V$                                    | -1.0                 |     |                                       | μA    |

| OUTPUTS                        |        |                  |                                                  |                      |     |                                       |       |

|                                | Llink  | V <sub>OH</sub>  | I <sub>OH</sub> = -5.0mA, V <sub>DD</sub> = 5.0V | 2.4                  |     |                                       | V     |

| Logic Output Voltage           | High   |                  | I <sub>OH</sub> = -4.0mA, V <sub>DD</sub> = 3.3V | 2.4                  |     |                                       | V     |

|                                | Law    | N                | I <sub>OH</sub> = 5.0mA, V <sub>DD</sub> = 5.0V  |                      |     | 0.4                                   | V     |

|                                | Low    | V <sub>ol</sub>  | I <sub>OH</sub> = 4.0mA, V <sub>DD</sub> = 3.3V  |                      |     | 0.5                                   |       |

| Logic Output Voltage<br>(CMOS) | High   | V <sub>OHC</sub> | I <sub>он</sub> = -100µА                         | V <sub>DD</sub> -0.2 |     |                                       | V     |

|                                | Low    | V <sub>olc</sub> | Ι <sub>οL</sub> = 100μΑ                          |                      |     | GND+0.2                               | V     |

| SUPPLY CURRENT                 |        |                  |                                                  |                      |     |                                       |       |

| V <sub>DD</sub> Current        |        |                  | V <sub>DD</sub> = 5.0V                           |                      | 14  | 20                                    | mA    |

| (HI-8454, HI-8455)             |        | I <sub>DD</sub>  | V <sub>DD</sub> = 3.3V                           |                      | 9   | 15                                    | mA    |

| V <sub>DD</sub> Current        |        |                  | V <sub>DD</sub> = 5.0V                           |                      | 12  | 18                                    | mA    |

| (HI-8450, HI-8451)             |        | I <sub>DD</sub>  | V <sub>DD</sub> = 3.3V                           |                      | 8   | 14                                    | mA    |

#### Table 4. AC Electrical Characteristics

$V_{_{DD}}$  = +5.0V ± 10% or +3.3V ± 10%, GND = 0V, T<sub>A</sub> = Operating Temperature Range (unless otherwise stated)

| Parameters             |                           | Symbol           | Test Conditions       | Min | Тур | Мах | Units |  |  |

|------------------------|---------------------------|------------------|-----------------------|-----|-----|-----|-------|--|--|

| SWITCHING CHARACTERIST | SWITCHING CHARACTERISTICS |                  |                       |     |     |     |       |  |  |

| Propagation Delay      | IN to OUT                 | t <sub>LH</sub>  | C <sub>L</sub> = 50pF |     | 150 | 300 | ns    |  |  |

|                        |                           | t <sub>HL</sub>  | $C_{L} = 50 pF$       |     | 150 | 300 | ns    |  |  |

| Output Rise Time       |                           | t <sub>R</sub>   | 10% to 90%            |     | 15  | 50  | ns    |  |  |

| Output Fall Time       |                           | t <sub>F</sub>   | 90% to 10%            |     | 15  | 50  | ns    |  |  |

| Propagation Delay      | TEST to OUT               | t <sub>тон</sub> |                       |     | 50  |     | ns    |  |  |

|                        |                           | t <sub>TOL</sub> |                       |     | 50  |     | ns    |  |  |

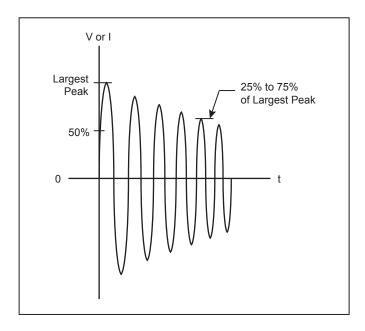

#### LIGHTNING INDUCED TRANSIENT VOLTAGE WAVEFORMS

#### Waveform 3.

Figure 3. DO-160G Lightning Induced Transient Voltage Waveform 3. Voc = 600V, Isc = 24A, Frequency = 1MHz ± 20%.

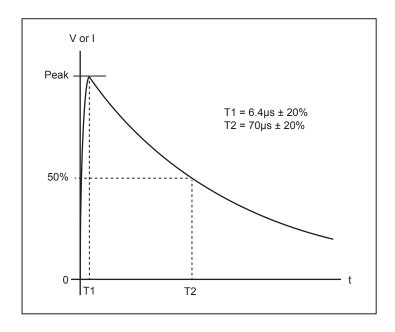

#### Waveform 4.

Figure 4. DO-160G Lightning Induced Transient Voltage Waveform 4. Voc = 300V, Isc = 60A.

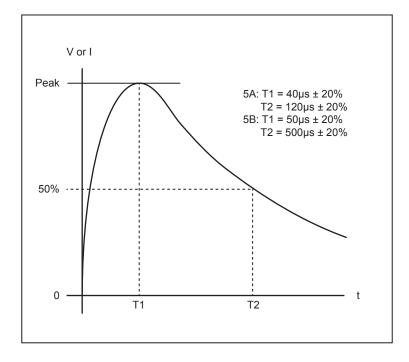

#### Waveform 5.

Figure 5. DO-160G Lightning Induced Transient Voltage Waveforms 5A and 5B. Voc = 300V, Isc = 300A.

## ADDITIONAL PIN CONFIGURATIONS

#### **ORDERING INFORMATION**

#### HI - 845xxx x x (Plastic)

| L | -[ | PART NUMBER | LEAD FINISH                              |

|---|----|-------------|------------------------------------------|

|   |    | Blank       | Tin / Lead (Sn / Pb) Solder              |

|   |    | F           | 100% Matte Tin (Pb-free, RoHS compliant) |

| PART NUMBER | TEMPERATURE RANGE | FLOW | BURN IN |

|-------------|-------------------|------|---------|

| I           | -40°C to +85°C    | I    | No      |

| Т           | -55°C to +125°C   | Т    | No      |

| М           | -55°C to +125°C   | М    | Yes     |

| <br>PART NUMBER | PACKAGE DESCRIPTION                  |

|-----------------|--------------------------------------|

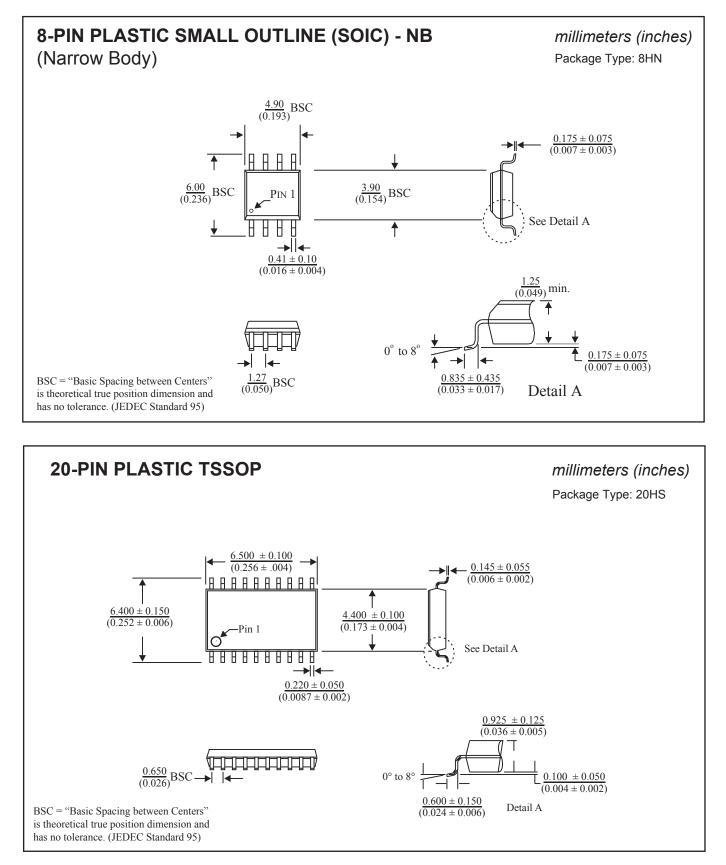

| 8450PS          | 8 PIN PLASTIC NARROW BODY SOIC (8HN) |

| 8451PS          | 8 PIN PLASTIC NARROW BODY SOIC (8HN) |

| 8454PS          | 20 PIN PLASTIC TSSOP (20HS)          |

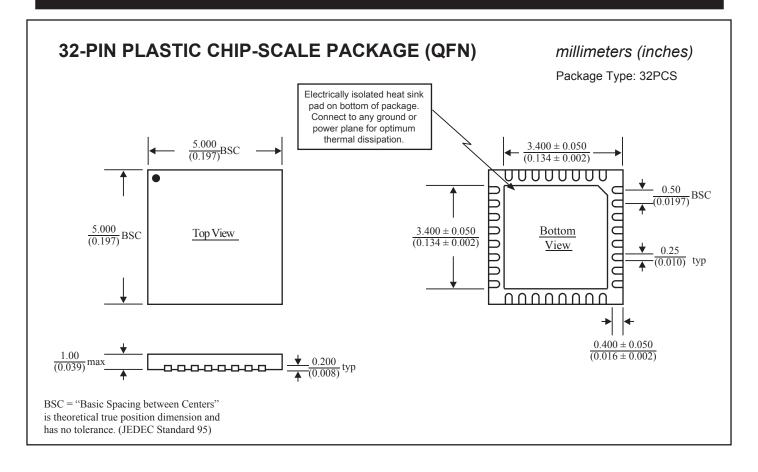

| 8454PC          | 32 PIN PLASTIC QFN (32PCS)           |

| 8455PS          | 20 PIN PLASTIC TSSOP (20HS)          |

## **REVISION HISTORY**

| Revision |          | Date     | Description of Change                                          |

|----------|----------|----------|----------------------------------------------------------------|

| DS8450,  | Rev. New | 01/14/14 | Initial Release                                                |

|          | Rev. A   | 12/05/16 | Remove Power Dissipation spec from "Absolute Maximum Ratings". |

|          | Rev. B   | 03/12/18 | Add ARINC AC Input Voltage to Absolute Maximum Ratings table.  |

#### PACKAGE DIMENSIONS