## **Errata Sheet**

Rel. 1.3, 2018-06-11

Device TC23x

Marking/Step ES-AC, AC

Package see Data Sheet

No. 063/18

This Errata Sheet describes the deviations from the current user documentation.

Table 1 Current Documentation<sup>1)</sup>

| TC21x/TC22x/TC23x                                          | V1.1             | 2014-12          |

|------------------------------------------------------------|------------------|------------------|

| User's Manual                                              |                  |                  |

| TC233/TC234/TC237 AC-Step<br>Data Sheet                    | V1.0             | 2017-03          |

| TriCore TC1.6P & TC1.6E Core Architecture, Instruction Set | V1.0D10, V1.0D15 | 2012-02, 2013-07 |

<sup>1)</sup> Newer versions replace older versions, unless specifically noted otherwise.

Make sure you always use the corresponding documentation for this device (User's Manual, Data Sheet, Documentation Addendum (if applicable), TriCore Architecture Manual, Errata Sheet) available in category 'Documents' at www.infineon.com/AURIX and www.myInfineon.com.

#### Conventions used in this document

Each erratum identifier follows the pattern **Module\_Arch.TypeNumber**:

- Module: subsystem, peripheral, or function affected by the erratum

- · Arch: microcontroller architecture where the erratum was initially detected

- AI: Architecture Independent

- TC: TriCore

- Type: category of deviation

- [none]: Functional Deviation

- P: Parametric Deviation

- H: Application Hint

- D: Documentation Update

- Number: ascending sequential number within the three previous fields. As

this sequence is used over several derivatives, including already solved

deviations, gaps inside this enumeration can occur.

#### **Notes**

- 1. This Errata Sheet applies to all temperature and frequency versions and to all memory size variants, unless explicitly noted otherwise. For a derivative synopsis, see the latest Data Sheet/User's Manual.

- This Errata Sheet covers several device versions. If an issue is related to a particular module, and this module is not specified for a specific device version, this issue does not apply to this device version.

- E.g. issues with identifier "ETH" only apply to devices with a specific extended feature set.

- Devices marked with EES or ES are engineering samples which may not be completely tested in all functional and electrical characteristics, therefore they should be used for evaluation only.

- The specific test conditions for EES and ES are documented in a separate Status Sheet.

- 3. This device is equipped with TriCore "TC1.6E" core(s). Some of the errata have workarounds which are possibly supported by the tool vendors. Some corresponding compiler switches need possibly to be set. Please see the respective documentation of your compiler.

- For effects of issues related to the on-chip debug system, see also the documentation of the debug tool vendor.

TC23x, ES-AC, AC 2/201 Rel. 1.3, 2018-06-11

Table 2 History List

| Table 2 | History L  | JEST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Version | Date       | Remark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.0     | 2016-10-21 | <ul> <li>New/updated text modules see columns "Change" in tables 46 of errata sheet V1.0.</li> <li>The following text modules have been removed, as no device variant exists of this design step (AC) that includes EMEM, ETH, FFT modules:         <ul> <li>EMEM_TC.H002 (EMEM will raise ECC errors when not properly initialized)</li> <li>ETH_AI.003 (Overflow Status bits of Missed Frame and Buffer Overflow counters get cleared without a Read operation)</li> <li>ETH_AI.H001 (Sequence for Switching between MII and RMII Modes)</li> <li>ETH_TC.004 (DMA Access to Reserved/Protected Resources: FPI Error Response not correctly evaluated)</li> <li>ETH_TC.H002 (Minimum operation frequency for Ethernet MAC)</li> <li>ETH_TC.H003 (Interrupt Generation by Wake-up or Magic Packet Frames)</li> <li>FFT_TC.001 (FFT Access with disabled FFT Module)</li> <li>FFT_TC.003 (No Error reported upon Write to FFT Registers in User Mode)</li> </ul> </li> <li>The following text module has been removed, as no ADAS variant exists of this design step (AC)</li> <li>SCU_TC.H012 (Overlay Feature for ADAS Variants)</li> </ul> |

Table 2 History List (cont'd)

| I able 2 | - 1113tory L | ist (cont d)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Version  | Date         | Remark                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.1      | 2017-03-31   | <ul> <li>New/updated text modules see columns "Change" in tables 46 of errata sheet V1.1.</li> <li>Removed reference to "GTM-IP 210 Errata Sheet" in Table 1 - all GTM errata relevant for this design step are considered in this TC23x errata sheet</li> <li>The following text modules have been included in Table 3 (Errata fixed in this step):         <ul> <li>ADC_TC.P007 (Additional Parameter for Data Sheet: Wakeup Time t<sub>WU</sub>): see specification of t<sub>WU</sub> in TC23x AC-Step Data Sheet</li> <li>I0_TC.P003 (Calculating the 1.3 V Current Consumption for TC23x): see corresponding section in TC23x AC-Step Data Sheet</li> <li>PADS_TC.P007 (Connection of Ball U17 in LFBGA-292 Package): see chapter "Package and Pinning Definitions" in TC23x AC-Step Data Sheet</li> </ul> </li> </ul> |

| 1.2      | 2017-11-03   | • Update: new/updated text modules see columns<br>"Change" in tables 46 of errata sheet V1.2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.3      | 2018-06-11   | <ul> <li>New/updated text modules see columns "Change" in tables 46</li> <li>Replaced:         <ul> <li>DMA_TC.029 (DMA Double Buffering Overflow),</li> <li>DMA_TC.047 (DMA Double Buffering Buffer Switch),</li> <li>DMA_TC.057 (Double Buffering Overflow Causes Other Channel Corruption)</li> <li>&gt;&gt; replaced by DMA_TC.061 (DMA Double Buffering Operations)</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                             |

Table 2 History List (cont'd)

| Version         | Date | Remark                                                                            |

|-----------------|------|-----------------------------------------------------------------------------------|

| 1.3<br>(cont'd) |      | • Removed: - GTM_TC.010 (Effects of GTM Resets) - TC23xTC21x do not have GTM SRAM |

Table 3 Errata fixed in this step

| Errata          | Short Description                                                         | Change                      |

|-----------------|---------------------------------------------------------------------------|-----------------------------|

| ADC_TC.P007     | Additional Parameter for Data Sheet: Wakeup Time t <sub>WU</sub>          | Fixed                       |

| CCU_TC.002      | Clock Monitors - Target Monitoring Frequency Selection                    | Fixed                       |

| CCU_TC.003      | Maximum Amplitude for Frequency Modulation                                | Fixed                       |

| FLASH_TC.044    | Repetitive Erase Suspend Requests on Data Flash                           | Fixed                       |

| I0_TC.P003      | Calculating the 1.3 V Current Consumption for TC23x                       | Fixed                       |

| MTU_TC.016      | Wrong Address(es) Tracked in Registers ETRRx of TC1.6E CPU0 PSPR and DSPR | Fixed                       |

| MultiCAN_AI.047 | Transmit Frame Corruption after Protocol Exception (CAN FD only)          | Fixed                       |

| MultiCAN_TC.043 | CAN FD: Idle Condition                                                    | Fixed<br>(node 0,1<br>only) |

| MultiCAN_TC.044 | CAN FD: Missing Hardsync                                                  | Fixed<br>(node 0,1<br>only) |

Table 3 Errata fixed in this step (cont'd)

| Errata       | Short Description                                              | Change |

|--------------|----------------------------------------------------------------|--------|

| PADS_TC.P007 | Connection of Ball U17 in LFBGA-292<br>Package                 | Fixed  |

| RESET_TC.007 | Unexpected SMU Reset during SSW execution if no HARR requested | Fixed  |

| SMU_TC.005   | Unexpected/Incorrect Reset caused by SMU Alarms                | Fixed  |

Note: Changes to the previous errata sheet version are particularly marked in column "Change" in the following tables.

**Table 4** Functional Deviations

| Functional Deviation | Short Description                                                 | Cha<br>nge | Pa<br>ge |

|----------------------|-------------------------------------------------------------------|------------|----------|

| ADC_AI.016           | No Channel Interrupt in Fast Compare Mode with GLOBRES            |            | 24       |

| ADC_TC.068           | Effect of VAGND Cross Coupling on Conversion Result               |            | 24       |

| ASCLIN_TC.004        | SLSO in SPI mode still active after module disable                |            | 27       |

| ASCLIN_TC.005        | Unjustified collision detection error in half-<br>duplex SPI mode |            | 27       |

| ASCLIN_TC.006        | Unjustified response timeout in LIN slave mode                    |            | 28       |

| ASCLIN_TC.007        | Break Detected in LIN Frames in Soft Suspend mode                 |            | 28       |

| ASCLIN_TC.008        | Response timeout in LIN Mode in case of header only               |            | 28       |

| ASCLIN_TC.009        | RFL flag set in Buffer Mode when Receive FIFO Inlet is disabled   |            | 29       |

Table 4 Functional Deviations (cont'd)

| Functional    | Short Description                                                                          | Cha | Pa |

|---------------|--------------------------------------------------------------------------------------------|-----|----|

| Deviation     |                                                                                            | nge | ge |

| ASCLIN_TC.010 | Flush of TXFIFO leads to frame transmission                                                |     | 29 |

| BROM_TC.008   | Sporadic Power-on Reset after Wake-up from Standby Mode                                    |     | 30 |

| CPU_TC.123    | Data Corruption possible when CPU GPR accesses made via SRI slave with CPU running         |     | 30 |

| CPU_TC.127    | Pending Interrupt Priority Number PIPN in Register ICR                                     |     | 31 |

| DAP_TC.002    | DAP client_blockread has Performance issue in Specific Operation Modes                     |     | 31 |

| DAP_TC.003    | DAP CRC32 definition and algorithm                                                         |     | 32 |

| DAP_TC.004    | DAP client_blockwrite telegram with CRC6 and CRC32 protection options                      |     | 33 |

| DAP_TC.005    | DAP client_read: dirty bit feature of Cerberus' Triggered Transfer Mode                    |     | 34 |

| DAP_TC.006    | CRC6 error in telegram following a get_CRCdown telegram prevents reset of CRC32 calculator |     | 34 |

| DAP_TC.007    | Incomplete client_blockread telegram in DXCM mode when using the "read CRCup" option       |     | 35 |

| DAP_TC.009    | CRC6 error in client_blockwrite telegram                                                   | New | 35 |

| DMA_TC.015    | DMA Double Buffering: No Timestamp<br>Support                                              |     | 36 |

| DMA_TC.016    | Byte and Half-word Write Accesses to specific Registers not supported                      |     | 36 |

| DMA_TC.017    | Pattern Detection Double Interrupt Trigger when INTCT = 11 <sub>B</sub>                    |     | 37 |

Table 4 Functional Deviations (cont'd)

| Functional Deviation | Short Description                                                                        | Cha<br>nge | Pa       |

|----------------------|------------------------------------------------------------------------------------------|------------|----------|

| DMA_TC.018           | FPI timeout can cause pipelined register reads to break                                  | iige       | ge<br>38 |

| DMA_TC.019           | CBS Accesses with Large SPB:SRI Clock Ratios Configured                                  |            | 38       |

| DMA_TC.020           | DMA Conditional Linked List: Circular Buffer Enabled                                     |            | 38       |

| DMA_TC.021           | Combined Software/Hardware Controlled Mode Spurious Errors                               |            | 39       |

| DMA_TC.022           | Conditional Linked List: Bus Error                                                       |            | 39       |

| DMA_TC.024           | Suspend Request coincident with Channel Activation                                       |            | 40       |

| DMA_TC.025           | Conditional Linked List: new non-CLL mode TCS load can corrupt SDCRC RAM write           |            | 41       |

| DMA_TC.026           | Linked List: Failed TCS load can trigger wrap interrupt                                  |            | 41       |

| DMA_TC.028           | Transaction Request Lost (TRL) Interrupt Service Request Behaviour                       | Upd<br>ate | 41       |

| DMA_TC.031           | CHCSR.ICH can be incorrectly set after pattern match                                     |            | 42       |

| DMA_TC.034           | DMA Timestamp and Destination Circular Buffer                                            | Upd<br>ate | 42       |

| DMA_TC.035           | Last DMA Transaction in a Linked List triggers a DMA Daisy Chain                         |            | 44       |

| DMA_TC.036           | Linked List: SADR/DADR can be overwritten when loading a non-LL TCS                      |            | 44       |

| DMA_TC.037           | Conditional Linked List: Bit TSR.CH not cleared for a CLL transaction upon pattern match |            | 45       |

Table 4 Functional Deviations (cont'd)

| Functional Deviation | Short Description                                                                                                             | Cha<br>nge | Pa<br>ge  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------|------------|-----------|

| DMA_TC.038           | Linked List: SIT interrupt when SIT bit set in newly loaded TCS                                                               |            | 45        |

| DMA_TC.039           | Read Data CRC                                                                                                                 |            | 46        |

| DMA_TC.040           | DMA Linked Lists: Intermittent Clearing of<br>Hardware Transaction Request Enable<br>with mixed mode Transaction Control Sets |            | 46        |

| DMA_TC.041           | DMA Circular Buffer Wrap Interrupt                                                                                            |            | 47        |

| DMA_TC.042           | DMA Interrupt from Channel reported before Completion of DMA Transaction                                                      |            | 48        |

| DMA_TC.043           | DMA Write Move Data Corruption for non<br>32-byte Aligned Cacheable Source<br>Address                                         |            | 48        |

| DMA_TC.044           | Clock Switch after SPB Error Reported results in Spurious SRI Error                                                           |            | 49        |

| DMA_TC.045           | DMA Reconfigures DMA Channels Lockup                                                                                          |            | 49        |

| DMA_TC.046           | Shadow Operation Read Only Mode                                                                                               |            | 50        |

| DMA_TC.049           | <b>Bus Error Reported During LL TCS Load</b>                                                                                  |            | <b>50</b> |

| DMA_TC.050           | Clearing CHCSR.FROZEN during Double Buffering                                                                                 |            | 51        |

| DMA_TC.052           | SER and DER During Linked List<br>Operations                                                                                  | Upd<br>ate | 51        |

| DMA_TC.053           | TS16_ERR Type of Error Reporting Unreliable                                                                                   |            | <b>52</b> |

| DMA_TC.054           | DMA Channel Halt Acknowledge Unreliable                                                                                       |            | 52        |

| DMA_TC.055           | ICU to DMA Interface in Sleep Mode                                                                                            |            | <b>53</b> |

| DMA_TC.056           | TSR and SUSENR Access Protection Unreliable                                                                                   |            | 53        |

| DMA_TC.058           | Linked List Load Transaction Control Set (TCS) Integrity Error                                                                |            | 55        |

Table 4 Functional Deviations (cont'd)

| Functional     | Short Description                                                                                                                                              | Cha | Pa        |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|

| Deviation      |                                                                                                                                                                | nge | ge        |

| DMA_TC.061     | DMA Double Buffering Operations                                                                                                                                | New | 56        |

| DMA_TC.062     | Termination of DMA Transaction for Pattern Match                                                                                                               | New | 58        |

| DMA_TC.063     | DMA Timestamp Destination Address                                                                                                                              | New | <b>59</b> |

| DMA_TC.064     | DMA Daisy Chain Request                                                                                                                                        | New | 59        |

| DMA_TC.065     | DMA Move Concurrent Bus Accesses                                                                                                                               | New | 60        |

| DTS_TC.001     | Temperature Sensor Formula                                                                                                                                     |     | 60        |

| FlexRay_Al.087 | After reception of a valid sync frame followed by a valid non-sync frame in the same static slot the received sync frame may be ignored                        |     | 61        |

| FlexRay_Al.088 | A sequence of received WUS may generate redundant SIR.WUPA/B events                                                                                            |     | 61        |

| FlexRay_Al.089 | Rate correction set to zero in case of SyncCalcResult=MISSING_TERM                                                                                             |     | 62        |

| FlexRay_Al.090 | Flag SFS.MRCS is set erroneously although at least one valid sync frame pair is received                                                                       |     | 63        |

| FlexRay_Al.091 | Incorrect rate and/or offset correction value if second Secondary Time Reference Point (STRP) coincides with the action point after detection of a valid frame |     | 64        |

| FlexRay_Al.092 | Initial rate correction value of an integrating node is zero if pMicroInitialOffsetA,B = 0x00                                                                  |     | 64        |

| FlexRay_Al.093 | Acceptance of startup frames received after reception of more than gSyncNodeMax sync frames                                                                    |     | 65        |

| FlexRay_Al.094 | Sync frame overflow flag EIR.SFO may be set if slot counter is greater than 1024                                                                               |     | 66        |

Table 4 Functional Deviations (cont'd)

| Functional     | Short Description                                                                                                                 | Cha | Pa |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|----|

| Deviation      |                                                                                                                                   | nge | ge |

| FlexRay_Al.095 | Register RCV displays wrong value                                                                                                 |     | 66 |

| FlexRay_Al.096 | Noise following a dynamic frame that delays idle detection may fail to stop slot                                                  |     | 67 |

| FlexRay_Al.097 | Loop back mode operates only at 10 MBit/s                                                                                         |     | 68 |

| FlexRay_Al.099 | Erroneous cycle offset during startup after abort of startup or normal operation                                                  |     | 68 |

| FlexRay_Al.100 | First WUS following received valid WUP may be ignored                                                                             |     | 69 |

| FlexRay_Al.101 | READY command accepted in READY state                                                                                             |     | 70 |

| FlexRay_Al.102 | Slot Status vPOC!SlotMode is reset immediately when entering HALT state                                                           |     | 71 |

| FlexRay_Al.103 | Received messages not stored in Message RAM when in Loop Back Mode                                                                |     | 71 |

| FlexRay_Al.104 | Missing startup frame in cycle 0 at coldstart after FREEZE or READY command                                                       |     | 72 |

| FlexRay_Al.105 | RAM select signals of IBF1/IBF2 and OBF1/OBF2 in RAM test mode                                                                    |     | 73 |

| FlexRay_Al.106 | Data transfer overrun for message<br>transfers Message RAM to Output Buffer<br>(OBF) or from Input Buffer (IBF) to<br>Message RAM |     | 74 |

| GTM_AI.132     | GTM_TOP level: AEI write to BRIDGE_MODE register can result in blocking of AEI configuration interface                            |     | 77 |

Table 4 Functional Deviations (cont'd)

| Functional Deviation | Short Description                                                                                                                                         | Cha<br>nge | Pa<br>ge |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|

| GTM_AI.141           | TIM: Incorrect data captured to GPR registers and routed via ARU when EGPRi_SEL,GPRi_SEL= 100 in TIM channel mode TIEM, TPWM, TIPM, TPIM, TGPS            |            | 78       |

| GTM_AI.142           | TIM: Incorrect data captured to GPR registers and routed via ARU when EGPRi_SEL,GPRi_SEL= 100 in TIM channel mode TBCM                                    |            | 79       |

| GTM_AI.143           | GTM_TOP level: AEI pipelined write to GTM_BRIDGE_MODE register directly after setting aei_reset='0' can result in blocking of AEI configuration interface |            | 80       |

| GTM_AI.144           | TIM: TIM interrupts as trigger source from TIM to TOM/ATOM not functional                                                                                 |            | 80       |

| GTM_AI.153           | TIM: Incorrect data captured to CNTS register when TIM channel operates in mode TPWM or TPIM and CNTS_SEL = 1 and selected CMU_CLK ≠ sys_clk              |            | 81       |

| GTM_AI.154           | TOM: Incorrect duty cycle in PCM mode (bit reversed mode)                                                                                                 |            | 82       |

| GTM_AI.157           | CMU: Incorrect AEI status by writing 1 to bit 24 of register CMU_CLK_6/7_CTRL                                                                             |            | 82       |

| GTM_AI.163           | TIM: timeout signaled when TDU unit is reenabled                                                                                                          |            | 83       |

| GTM_AI.164           | TIM: capturing of data into TIM[i]_CH[x]_CNTS with setting CNTS_SEL=1 not functional in TPWM and TPIM mode                                                |            | 84       |

| GTM_AI.181           | TIM: Incorrect signal level bit ECNT[0] in mode TIEM, TPWM, TIPM, TPIM, TGPS                                                                              |            | 84       |

Table 4 Functional Deviations (cont'd)

| Functional | Short Description                                                                                                                                 | Cha | Pa |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|----|

| Deviation  |                                                                                                                                                   | nge | ge |

| GTM_AI.202 | (A)TOM: no CCU1 interrupt in case of CM1=0 or 1 and RST_CCU0=1                                                                                    |     | 85 |

| GTM_AI.205 | TIM: unexpected CNTS register update in TPWM OSM mode                                                                                             |     | 86 |

| GTM_AI.209 | TOM/ATOM: no update of CM0/CM1/CLK_SRC via trigger signal from preceding instance if selected CMU_CLKx is not SYS_CLK                             |     | 86 |

| GTM_AI.270 | (A)TOM: output signal is postponed one period for the values CM0=1 and CM1>CM0 if CN0 is reset by the trigger of a preceding channel (RST_CCU0=1) |     | 87 |

| GTM_AI.298 | TOM/ATOM: wrong output behaviour in SOMP oneshot mode when oneshot pulse is triggered by TIM_EXT_CAPTURE(x)29                                     |     | 88 |

| GTM_AI.299 | TOM/ATOM: wrong output behaviour in SOMP oneshot mode when oneshot pulse is triggered by trig_[x-1]                                               |     | 89 |

| GTM_TC.009 | TBU signals not wired to debug logic                                                                                                              |     | 89 |

| GTM_TC.012 | Read Access Control by Register ODA                                                                                                               |     | 90 |

| IOM_TC.002 | Missed or spurious IOM events when pulse length exceeds Event Window counter range                                                                |     | 91 |

| IOM_TC.003 | Unexpected Event upon Kernel Reset                                                                                                                |     | 91 |

| IOM_TC.004 | Write to IOM register space when IOM_CLC.RMC > 1                                                                                                  |     | 92 |

| MTU_TC.005 | Access to MCx_ECCD and MCx_ETRRi while MBIST disabled                                                                                             |     | 92 |

| MTU_TC.007 | Error Overflow Indication ECCD.EOV                                                                                                                |     | 94 |

| MTU_TC.011 | MBIST Bitmap not working for w0 - r1                                                                                                              |     | 94 |

Table 4 Functional Deviations (cont'd)

| Functional          | Short Description                                                                                        | Cha | Pa  |

|---------------------|----------------------------------------------------------------------------------------------------------|-----|-----|

| Deviation           |                                                                                                          | nge | ge  |

| MTU_TC.012          | Security of CPU Cache Memories During Runtime is Limited                                                 |     | 95  |

| MultiCAN_TC.043     | CAN FD: Idle Condition                                                                                   |     | 96  |

| MultiCAN_TC.044     | CAN FD: Missing Hardsync                                                                                 |     | 96  |

| OCDS_TC.038         | Disconnecting a debugger without device reset ("hot detach") may require reading of OCS registers        |     | 98  |

| OCDS_TC.042         | OTGS capture registers can miss single clock cycle triggers                                              |     | 99  |

| OCDS_TC.043         | Read-Modify-Write Bus Transactions to Cerberus Registers                                                 |     | 99  |

| PLL_ERAY_TC.0<br>01 | PLL_ERAY Initialization after Cold Power-<br>up or Wake-up from Standby mode                             |     | 100 |

| PLL_TC.005          | PLL Initialization after Cold Power-up or Wake-up from Standby mode                                      |     | 100 |

| PMC_TC.002          | Switch Capacitor Regulator Mode,<br>Frequency Spreading - Documentation<br>Update to Register EVRSDCTRL1 |     | 101 |

| PMC_TC.003          | Usecase limitation of LDO mode with on chip pass device for SAL devices                                  |     | 103 |

| QSPI_TC.006         | Baud rate error detection in slave mode (error indication in current frame)                              |     | 104 |

| RESET_TC.005        | Indication of Power Fail Events in SCU_RSTSTAT                                                           |     | 104 |

| SMU_TC.006          | OCDS Trigger Bus OTGB during<br>Application Reset                                                        |     | 105 |

| SMU_TC.007          | Size and Position of Field ACNT in Register SMU_AFCNT                                                    |     | 105 |

| SMU_TC.008          | Behavior of Action Counter ACNT                                                                          |     | 106 |

Table 4 Functional Deviations (cont'd)

| Functional | Short Description                                   | Cha | Pa  |

|------------|-----------------------------------------------------|-----|-----|

| Deviation  |                                                     | nge | ge  |

| SMU_TC.010 | Transfer to SMU_AD register not triggered correctly |     | 107 |

| SRI_TC.003 | XBAR_PRIOL/H Register Layout and Reset Values       |     | 107 |

Table 5 Deviations from Electrical- and Timing Specification

| AC/DC/ADC      | Short Description                                                                 | Cha | Pa  |

|----------------|-----------------------------------------------------------------------------------|-----|-----|

| Deviation      |                                                                                   | nge | ge  |

| ADC_TC.P010    | Increased Gain Error ( $EA_{GAIN}$ ) for $T_J < 0$ °C                             |     | 110 |

| IDD_TC.H001    | IPC Limits used in Production Test for IDD Max Power Pattern                      |     | 110 |

| PADS_TC.H004   | PN-Junction Characteristics for Pad Type S                                        |     | 111 |

| RTH_TC.H001    | Thermal characteristics of the package - Footnote update for LF-BGA-292-6 package | New | 111 |

| VDDPPA_TC.H001 | Voltage to ensure defined pad states - Footnote update                            | New | 111 |

Table 6 Application Hints

| Hint           | Short Description                                                           | Cha<br>nge | Pa<br>ge |

|----------------|-----------------------------------------------------------------------------|------------|----------|

| ADC_AI.H003    | Injected conversion may be performed with sample time of aborted conversion |            | 113      |

| ADC_TC.H011    | Bit DCMSB in register GLOBCFG                                               |            | 114      |

| ADC_TC.H014    | VADC Start-up Calibration                                                   |            | 114      |

| ADC_TC.H015    | Conversion Time with Broken Wire Detection                                  |            | 115      |

| ADC_TC.H020    | Minimum/Maximum Detection Compares 12 Bits Only                             |            | 116      |

| ADC_TC.H022    | Sample Time Control - Formula                                               |            | 117      |

| ADC_TC.H024    | Documentation: Filter control only in registers GxRCR7/GxRCR15              |            | 118      |

| ASCLIN_TC.H001 | Bit field FRAMECON.IDLE in LIN slave mode                                   |            | 118      |

| ASCLIN_TC.H003 | Behavior of LIN Autobaud Detection<br>Error Flag                            |            | 118      |

| ASCLIN_TC.H004 | Changing the Transmit FIFO Inlet Width / Receive FIFO Outlet Width          |            | 119      |

| ASCLIN_TC.H005 | Collision detection error reported twice in LIN slave mode                  |            | 120      |

| BCU_TC.H001    | HSM Transaction Information not captured                                    |            | 121      |

| BROM_TC.H003   | Information related to Register FLASH0_PROCOND                              |            | 121      |

| CCU6_AI.H001   | Update of Register MCMOUT                                                   |            | 122      |

| CCU6_AI.H002   | Description of Bit RWHE in Register ISR                                     |            | 122      |

| CCU6_AI.H003   | Bit TRPCTR.TRPM2 in Manual Mode - Documentation Update                      |            | 123      |

| CCU_TC.H001    | Clock Monitor Check Limit Values                                            |            | 123      |

Table 6 Application Hints (cont'd)

| Hint        | Short Description                                                                                                     | Cha<br>nge | Pa<br>ge |

|-------------|-----------------------------------------------------------------------------------------------------------------------|------------|----------|

| CCU_TC.H002 | Oscillator Gain Selection via OSCCON.GAINSEL                                                                          |            | 124      |

| CCU_TC.H005 | References to f <sub>PLL2</sub> , f <sub>PLL2_ERAY</sub> and K3<br>Divider in User's Manual                           |            | 124      |

| CCU_TC.H006 | Clock Monitor Support - Documentation<br>Update                                                                       |            | 125      |

| CCU_TC.H007 | Oscillator Watchdog Trigger Conditions for ALM3[0]                                                                    |            | 125      |

| CPU_TC.H006 | Store Buffering in TC1.6/P/E Processors                                                                               |            | 126      |

| CPU_TC.H008 | Instruction Memory Range Limitations                                                                                  |            | 128      |

| CPU_TC.H009 | Details on CPU Clock Control                                                                                          |            | 129      |

| CPU_TC.H012 | Behavior of bit-wise operations on certain peripheral register bits which need to be written back with the same value |            | 129      |

| CPU_TC.H014 | ACCEN* Protection for Write Access to Safety Protection Registers - Documentation Update                              |            | 131      |

| CPU_TC.H015 | Register Access Modes for Safety Protection Registers - Documentation Update                                          | New        | 131      |

| DAP_TC.H002 | DAP client_blockread in Combination with TGIP and all Parcels with CRC6                                               |            | 131      |

| DAP_TC.H003 | Not acknowledged DAP telegrams in noisy environments                                                                  |            | 132      |

| DMA_TC.H002 | Bit CHCSRz.BUFFER can be toggled when not in Double Buffer Mode                                                       |            | 133      |

| DMA_TC.H004 | Transaction Request Lost upon software trigger with pattern match                                                     |            | 133      |

Table 6 Application Hints (cont'd)

| Hint            | Short Description                                                                | Cha<br>nge | Pa<br>ge |

|-----------------|----------------------------------------------------------------------------------|------------|----------|

| DMA_TC.H005     | Linked List Transfer leading to loading of non-Linked List TCS causes corruption |            | 133      |

| DMA_TC.H006     | Clearing of HTRE when DMA channel is configured for Single Mode                  |            | 134      |

| DMA_TC.H007     | Selecting the Priority for DMA Channels                                          |            | 135      |

| DMA_TC.H008     | Transaction Request State                                                        |            | 136      |

| DMA_TC.H009     | Resetting Bits ICH and IPM in register CHCSRz                                    |            | 136      |

| DMA_TC.H010     | Calculation of DMA Address Checksum for DMA read moves to Cacheable Addresses    |            | 137      |

| DMA_TC.H011     | DMA_ADICRz.SHCT - Reserved Values                                                |            | 137      |

| DMA_TC.H012     | TCS Update in Halt State                                                         |            | 138      |

| DMA_TC.H013     | MExSR.WS and MExSR.RS Status Bits                                                | New        | 138      |

| DMA_TC.H016     | DMARAM ECC Error Disable                                                         | New        | 139      |

| DMA_TC.H017     | DMA Channel Request Control - Documentation Update                               | New        | 139      |

| DTS_TC.H001     | Update of Bit DTSSTAT.BUSY                                                       |            | 139      |

| ENDINIT_TC.H001 | Endinit Protection for Registers KRST0, KRST1, KRSTCLR                           |            | 140      |

| FLASH_TC.H007   | Advice for using Suspend and Resume                                              |            | 140      |

| FLASH_TC.H008   | Understanding Flash<br>Retention/Endurance Figures in the Data<br>Sheet          |            | 142      |

| FlexRay_Al.H004 | Only the first message can be received in External Loop Back mode                |            | 143      |

| FlexRay_Al.H005 | Initialization of internal RAMs requires one eray_bclk cycle more                |            | 143      |

| FlexRay_Al.H006 | Transmission in ATM/Loopback mode                                                |            | 144      |

Table 6 Application Hints (cont'd)

| Hint            | Short Description                                                        | Cha<br>nge | Ра  |

|-----------------|--------------------------------------------------------------------------|------------|-----|

|                 |                                                                          |            | ge  |

| FlexRay_Al.H007 | Reporting of coding errors via TEST1.CERA/B                              |            | 144 |

| FlexRay_Al.H009 | Return from test mode operation                                          |            | 144 |

| FlexRay_TC.H002 | Initialization of E-Ray RAMs                                             |            | 145 |

| FPI_TC.H002     | Write Access to Register ACCEN1                                          |            | 147 |

| GPT12_TC.H001   | Timer T5 Run Bit T5R - Documentation Correction                          |            | 147 |

| GTM_TC.H004     | Correction to Bit Fields GTM_TIMi_IN_SRC.VAL_x                           |            | 148 |

| GTM_TC.H005     | External Capture in TIM Pulse Integration Mode (TPIM)                    |            | 148 |

| GTM_TC.H007     | GTM to CAN Timer Triggers                                                |            | 149 |

| GTM_TC.H009     | TIM0 Channel x Input Selection - Mapping for QFP-80 and QFP-100 Packages |            | 150 |

| GTM_TC.H011     | First CM0 updates in case of SR0=1 and (A)TOM used as Triggered Channel  |            | 153 |

| GTM_TC.H014     | Synchronous Bridge Mode Restrictions                                     |            | 153 |

| GTM_TC.H015     | Register TIMi_CHx_CTRL - Correction to Register Image                    |            | 154 |

| INT_TC.H004     | Corrections to the Interrupt Router Documentation                        |            | 154 |

| IOM_TC.H001     | How to clear the IOM_LAMEWCm register                                    |            | 155 |

| IOM_TC.H002     | IOM Clock Control                                                        |            | 155 |

| IOM_TC.H003     | Configuration of LAMCFG.IVW and LAMEWS.THR                               |            | 157 |

| IOM_TC.H004     | Behavior of LAMEWCn.CNT when LAMEWSn.THR is 0                            |            | 159 |

| IOM_TC.H006     | ACCEN* Protection for Write Access to IOM Registers                      |            | 159 |

Table 6 Application Hints (cont'd)

| Hint             | Short Description                                                             | Cha<br>nge | Pa<br>ge |

|------------------|-------------------------------------------------------------------------------|------------|----------|

| IOM_TC.H007      | Write Access to FPCESR                                                        |            | 159      |

| LMU_TC.H002      | On-the-fly BBB:SRI clock ratio switching                                      |            | 160      |

| LMU_TC.H003      | Function of Bit MEMCON.PMIC (Protection Bit for Memory Integrity Control Bit) |            | 160      |

| MTU_TC.H003      | AURIX™ Memory Tests using the MTU                                             |            | 161      |

| MTU_TC.H004      | Handling the Error Tracking Registers ETRR                                    |            | 162      |

| MTU_TC.H005      | Handling SRAM Alarms                                                          |            | 163      |

| MTU_TC.H006      | Alarm Propagation to SMU via Error Flags in MCx_ECCD                          |            | 164      |

| MTU_TC.H008      | Memory Controllers for DSPR                                                   |            | 165      |

| MTU_TC.H009      | Reset Value for Register ECCD                                                 |            | 166      |

| MTU_TC.H010      | Register MCONTROL - Bit Field Res4                                            |            | 167      |

| MTU_TC.H011      | Access Protection for Memory Control Registers                                |            | 167      |

| MTU_TC.H012      | Kernel Reset triggers Reset of MBIST<br>Registers                             |            | 167      |

| MTU_TC.H014      | Access to SRAM while MTU operations are underway                              | New        | 168      |

| MultiCAN_AI.H005 | TxD Pulse upon short disable request                                          |            | 169      |

| MultiCAN_AI.H006 | Time stamp influenced by resynchronization                                    |            | 169      |

| MultiCAN_AI.H007 | Alert Interrupt Behavior in case of Bus-<br>Off                               |            | 170      |

| MultiCAN_TC.H003 | Message may be discarded before transmission in STT mode                      |            | 170      |

| MultiCAN_TC.H004 | Double remote request                                                         |            | 171      |

Table 6 Application Hints (cont'd)

| Hint                 | Short Description                                                                        | Cha<br>nge | Pa<br>ge |

|----------------------|------------------------------------------------------------------------------------------|------------|----------|

| MultiCAN_TC.H007     | Oscillating CAN Bus may Disable the CAN Interface                                        |            | 171      |

| MultiCAN_TC.H008     | Changes due to CAN FD protocol ISO 11898-1:2015                                          |            | 172      |

| MultiCAN_TC.H009     | Limitation on Secondary Sample Point (SSP) Position (ISO CAN FD nodes only)              | Upd<br>ate | 176      |

| MultiCAN_TC.H010     | Limitation on maximum SJW Range for CAN FD Data Phase (ISO CAN FD nodes only)            | New        | 177      |

| OCDS_TC.H010         | JTAG requires two initial clock cycles after PORST                                       |            | 178      |

| OCDS_TC.H012         | Minimum Hold Time for Inputs OCDS_TGIx                                                   |            | 178      |

| PLL_ERAY_TC.H0<br>02 | Correction in Figure "PLL_ERAY Block Diagram"                                            |            | 179      |

| PMC_TC.H001          | Check for permanent Overvoltage during Power-up                                          |            | 179      |

| PMC_TC.H004          | Selecting the WUT Clock Divider                                                          |            | 179      |

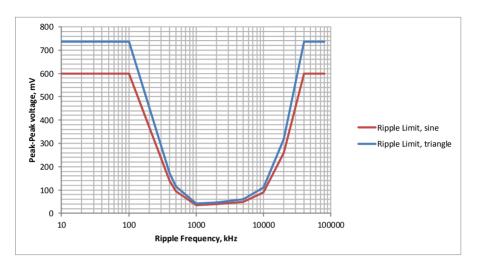

| PMS_TC.H002          | Sensitivity to supply voltage ripple at VDDP3 during start-up                            | New        | 180      |

| PORTS_TC.H006        | Using P33.8 while SMU is disabled                                                        |            | 182      |

| QSPI_TC.H005         | Stopping Transmission in Continuous Mode                                                 |            | 183      |

| QSPI_TC.H006         | Corrections to Figures "QSPI - Frequency Domains" and "Phase Duration Control, Overview" |            | 184      |

| QSPI_TC.H007         | RXFIFO Overflow Bit Behavior in Slave Mode                                               |            | 184      |

| RESET_TC.H002        | Unexpected SMU Reset Indication in SCU_RSTSTAT                                           |            | 185      |

Table 6 Application Hints (cont'd)

| Hint          | Short Description                                                                                         | Cha<br>nge | Pa<br>ge |

|---------------|-----------------------------------------------------------------------------------------------------------|------------|----------|

| RESET_TC.H003 | Usage of the Prolongation Feature for ESR0 as Reset Indicator Output                                      |            | 186      |

| RESET_TC.H004 | Effect of Power-on and System Reset on DSPR                                                               |            | 186      |

| SCU_TC.H009   | LBIST Influence on Pad Behavior                                                                           |            | 187      |

| SCU_TC.H010   | LBIST Signature Depends on Debug<br>Interface Configuration                                               |            | 187      |

| SCU_TC.H013   | Correction to Register References in Chapter "Watchdog Timers"                                            |            | 188      |

| SCU_TC.H014   | Reset Value of Bit Field IOCR.PC1 -<br>Control for Pin ESR1                                               |            | 189      |

| SENT_TC.H003  | First Write Access to Registers FDR and TPD after ENDINIT Status Change                                   |            | 189      |

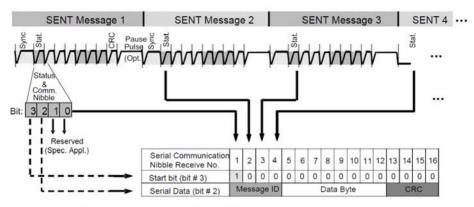

| SENT_TC.H004  | Short Serial Message - Figure Correction                                                                  |            | 190      |

| SENT_TC.H005  | Interface Connections of the SENT Module - Documentation Correction                                       |            | 191      |

| SMU_TC.H001   | Write all bit fields of SMU_PCTL with one write access                                                    |            | 192      |

| SMU_TC.H005   | Correction to Figure "SMU Register Map"                                                                   |            | 192      |

| SMU_TC.H006   | Description of Bit EFRST in Register SMU_AGC                                                              |            | 192      |

| SMU_TC.H007   | SPB Bus Control Unit (SBCU) Alarm Signalling to SMU                                                       |            | 193      |

| SMU_TC.H009   | Alarm Table Corrections                                                                                   |            | 193      |

| SMU_TC.H010   | Clearing individual SMU flags: use only 32-bit writes                                                     |            | 199      |

| SRI_TC.H001   | Using LDMST and SWAPMSK.W instructions on SRI mapped Peripheral Registers (range 0xF800 0000-0xFFFF FFFF) |            | 199      |

## Table 6 Application Hints (cont'd)

| Hint        | Short Description                                    | Cha | Pa  |

|-------------|------------------------------------------------------|-----|-----|

|             |                                                      | nge | ge  |

| STM_TC.H001 | Effect of kernel reset on interrupt outputs STMIR0/1 |     | 200 |

| STM_TC.H002 | Access Protection for STM Control<br>Registers       |     | 201 |

## 2 Functional Deviations

### ADC Al.016 No Channel Interrupt in Fast Compare Mode with GLOBRES

In fast compare mode, the compare value is taken from bitfield RESULT of the selected result register and the result of the comparison is stored in the respective bit FCR.

A channel event can be generated when the input becomes higher or lower than the compare value.

In case the global result register GLOBRES is selected, the comparison is executed correctly, the target bit is stored correctly, source events and result events are generated, but a channel event is not generated.

#### Workaround

If channel events are required, choose a local result register GxRESy for the operation of the fast compare channel.

## ADC\_TC.068 Effect of VAGND Cross Coupling on Conversion Result

Due the implementation of the clock dividers as fractional dividers, a statistical phase shift of one  $f_{VADC}$  clock can occur between the operation of different converter groups. If the last  $f_{VADC}$  clock of the sample phase of a converter group Gx coincides with the first  $f_{VADC}$  clock of a conversion step of (one or more) other converter groups Gy, the Total Unadjusted Error (TUE) of the conversion result of Gx is increased due to cross coupling via VAGND.

For TC26x, TC23x, TC22x, and TC21x, the TUE is increased up to ± 25 LSB<sub>12</sub>

#### Workarounds - Introduction

Workaround 1..3 may be used with any device step.

Workaround 4 can only be used with TC21x, TC22x, TC23x ≥ step AB.

TC23x, ES-AC, AC 24/201 Rel. 1.3, 2018-06-11

#### Workaround 1

Synchronize the trigger events of different converter groups as follows:

- Operate the arbiters and the analog parts of the VADC at the same clock frequency, i.e. select the divider factors DIVA and DIVD in register GLOBCFG such that f<sub>ADCD</sub> = f<sub>ADCI</sub> for all converter groups:

- Note: As  $f_{ADCD} = f_{VADC}/4$  with the maximum divider (DIVD = 3), this implies that  $f_{VADC} = f_{SPB}$  must be limited to 80 MHz to achieve  $f_{ADCD} = f_{ADCI}$  with the error limits specified for  $f_{ADCI} = 20$  MHz in the Data Sheet.

- Enlarge the length of an arbitration round to a minimum of 16 arbitration slots (i.e. bit field GxARBCFG.ARBRND ≥ 2 for any x).

- Select the conversion time (including sample time) of the longest conversion

of any group Gx to be shorter than two arbitration rounds. This ensures that

all converters are idle when the arbiters have determined the next

conversion request.

- Synchronize the digital and the analog clock by switching off/on the Module Disable Request bit, i.e. set CLC.DISR = 1<sub>R</sub> and then CLC.DISR = 0<sub>R</sub>.

- Initiate the start-up calibration by setting bit GLOBCFG.SUCAL = 1<sub>B</sub> (mandatory after switching off/on VADC clocks via CLC.DISR).

#### Workaround 2

Ensure that conversions never overlap for any two converter groups Gx and Gy. This may be achieved under software control, or by exclusively using the VADC background request source.

For this workaround, no restrictions apply on clock and arbitration round settings.

#### Workaround 3

Use the converters within a synchronization group in master/slave configuration, such that they are synchronized for parallel sampling, triggered by one common master. In this case, the cross coupling effect will not occur as long as only one synchronization group is performing conversions.

For devices that support more than one synchronization group, operate the synchronization groups in an interleaving manner.

For this workaround, no restrictions apply on clock and arbitration round settings.

#### Workaround 4

To avoid the cross coupling effect, this device step (see "Workarounds - Introduction" above) supports selection of signal CCU6061\_TRIG1 to synchronize the start of the converter groups to a raster of  $5/f_{SPB}$  (i.e. 50 ns @f\_SPB = 100 MHz). The resulting jitter (delay from trigger to start of conversion) is thus limited to max.  $5/f_{SPB}$ .

For this workaround, either CCU60\_T13 or CCU61\_T13 is configured (reserved) to provide the synchronization signal. The selection is performed via bit field TRIG1SEL in register CCU60\_MOSEL:

- TRIG1SEL = 000<sub>B</sub>: signal CCU60\_COUT63 from CCU60\_T13 is selected

- TRIG1SEL = 001<sub>B</sub>: signal CCU61\_COUT63 from CCU61\_T13 is selected

The synchronization signal is enabled inside the VADC module by setting bit GLOBCFG.DCMSB =  $1_B$ . The default function of this bit (DCMSB =  $0_B$ : one clock cycle for MSB conversion step) is hardwired and thus stays unaffected.

The following examples describe the initialization of CCU60 or CCU61, respectively, to provide a 20 MHz synchronization signal  $@f_{SPB} = 100$  MHz:

### **Example for CCU60 initialization**

## **Example for CCU61 initialization**

```

CCU61\_CLC = 0x0; // enable CCU61 kernel

```

Note: In case an application only uses kernel CCU61, ensure that kernel CCU60 is also clocked until register CCU60\_MOSEL is configured.

#### ASCLIN TC.004 SLSO in SPI mode still active after module disable

It is expected that in SPI mode, after module disable, the Slave Select Output signal SLSO should be in idle state according to configuration of Slave Polarity in Synchronous mode (IOCR.SPOL).

However, in this design step, when the module is disabled, the Slave Select Output signal SLSO is always 0 (low) independent of IOCR.SPOL, i.e., it is still active even when IOCR.SPOL =  $1_p$ .

#### Workaround

Before disabling the ASCLIN module, set SLSO to the desired level in the corresponding Port control registers.

## <u>ASCLIN\_TC.005</u> Unjustified collision detection error in half-duplex SPI mode

In Half Duplex SPI mode, when collision detection is enabled and the number of stop bits in SPI frame is configured as any value from 1 to 7 in FRAMECON.STOP, a Collision Error (FLAGS.CE) is triggered during the trailing phase (i.e., during stop bits), although RX and TX signal are identical.

TC23x, ES-AC, AC 27/201 Rel. 1.3, 2018-06-11

#### Workaround

In half-duplex SPI mode, set FRAMECON.STOP = 0 if trailing phase is irrelevant, or ignore/disable collision error if FRAMECON.STOP > 0.

## ASCLIN TC.006 Unjustified response timeout in LIN slave mode

When ASCLIN is configured as LIN slave and Response timeout is configured as DATCON.RM =  $1_{\rm B}$ , Response timeout is triggered even when an incomplete LIN Header frame is received. The timeout counter runs further after Header timeout detection without reset and triggers Response Timeout when it reaches the Response Timeout Threshold value defined by DATCON.RESPONSE.

#### Workaround

Ignore the Response Timeout which comes directly after a Header Timeout has occurred and before the next break is detected.

### ASCLIN\_TC.007 Break Detected in LIN Frames in Soft Suspend mode

When ASCLIN has entered Soft Suspend mode (OCS.SUS = 0x2), it still detects a Break Field in LIN frames and triggers an interrupt if enabled (FLAGSENABLE.BDE =  $1_B$ ).

#### Workaround

Ignore a detected break event when the module has been soft-suspended (e.g. set FLAGSENABLE.BDE =  $0_B$  when using soft suspend mode).

## <u>ASCLIN\_TC.008</u> Response timeout in LIN Mode in case of header only

In LIN (Master/Slave) mode, when Header Only (DATCON.HO =  $\mathbf{1}_{\rm B}$ ) is configured, Response timeout could occur even though no Response frame is expected.

TC23x, ES-AC, AC 28/201 Rel. 1.3, 2018-06-11

#### Workaround

To avoid the unwanted interrupt, disable the interrupt on Response Timeout by FLAGSENABLE.RTE =  $0_B$  whenever Header Only (DATCON.HO =  $1_B$ ) is configured.

## <u>ASCLIN\_TC.009</u> RFL flag set in Buffer Mode when Receive FIFO Inlet is disabled

When RXFIFO is configured in Buffer Mode (RXFIFOCON.BUF =  $1_{\rm B}$ ) and Receive FIFO Inlet is disabled (RXFIFOCON.ENI =  $0_{\rm B}$ ), the receive FIFO level flag is set (FLAGS.RFL =  $1_{\rm B}$ ) even though RXFIFO is not filled with new incoming data.

#### Workaround

To avoid the unwanted Receive FIFO Level interrupt, disable it by setting FLAGSENABLE.RFLE =  $0_B$  whenever Receive FIFO Inlet is disabled (RXFIFOCON.ENI =  $0_B$ ),

### ASCLIN\_TC.010 Flush of TXFIFO leads to frame transmission

When the TXFIFO is flushed (TXFIFIOCON.FLUSH =  $1_B$ ), it triggers transmission of a frame in the following corner case:

- · Starting condition:

- TXFIFO is not empty and TXFIFOCON.ENO = 0<sub>B</sub>

- Triggering condition:

- Write to TXFIFOCON with both TXFIFOCON.FLUSH = 1<sub>B</sub> and TXFIFOCON.ENO = 1<sub>B</sub>

#### Workaround

Do not flush TXFIFO and change bit TXFIFOCON.ENO from  $0_B$  to  $1_B$  in one single write to TXFIFOCON if TXFIFO is not empty.

## <u>BROM\_TC.008</u> Sporadic Power-on Reset after Wake-up from Standby Mode

On a wake-up from Standby mode, the Standby RAM redundancy installation procedure is executed. In case there is a sporadic Power-on reset in a time window between  $600 \, \mu s$  - 1 ms after Standby mode wake-up, it can happen that the application data stored in specific Standby RAM cells are overwritten.

Note: This effect can occur only on devices where non-zero data are stored in CPU0 DSPR at locations D000 2000<sub>H</sub> to D000 203F<sub>H</sub> by the Startup Software (SSW) after cold power-on (see section "Preparation before to enter Stand-by mode" in the BootROM chapter of the User's Manual). Only CPU0 DSPR Standby RAM is affected, EMEM in ADAS or ED devices is not affected.

#### Workarounds

- Calculate CRC over critical Standby RAM data and store result before Standby mode entry. On a consequent wake-up, CRC of the critical data shall be carried out. The CRC is a general recommended measure for improved robustness of Standby RAM handling. Or / and

- Keep a copy of the critical data at a second location in Standby RAM. On wake-up, compare data from both locations to ascertain their integrity.

## <u>CPU\_TC.123</u> Data Corruption possible when CPU GPR accesses made via SRI slave with CPU running

Data corruption may occur when another master accesses a TriCore CPU's General Purpose Registers (GPRs) via its SRI slave port whilst the CPU is running (i.e. not Idle, Halted or Suspended). The TriCore GPRs are A0-A15 and D0-D15. The scenarios in which data corruption may occur are different for the TC1.6P and TC1.6E processors as described below.

TC1.6P - Data corruption may occur when one of the CPU GPRs is **written** via the SRI slave port whilst the CPU is running. Both AGPR and DGPR writes may be affected.

TC1.6E - Data corruption may occur when one of the CPU Address GPRs (A0-A15) is **read** via the SRI slave port whilst the CPU is running. However, data corruption can only occur when the slave AGPR read interacts with the execution of a specific form of store instruction. The store instructions affected by this issue are ST.A and ST.DA, where the address register to be stored is modified by the addressing mode of the store instruction. For example:

However, such store instructions are architecturally undefined and should not be being used. In the case of this errata all data written to memory by this store instruction may be corrupted.

#### Workaround

Writes to a CPU's GPRs via its SRI slave port must never be performed whilst the CPU is running. If it is necessary for an external master to write to a CPU's GPR then that CPU must first be placed in Idle, Halt or Suspend mode.

If it is necessary for an external master to read a TC1.6E CPU's AGPR whilst that CPU is running then store instructions of the form above (where any source register is modified by the addressing mode of the store instruction) are not allowed.

## CPU TC.127 Pending Interrupt Priority Number PIPN in Register ICR

In the TriCore Architecture Manual, it is described for the Pending Interrupt Priority Number ICR.PIPN that it is reset to 0x0 in case there is no request pending.

However, the AURIX<sup>™</sup> hardware implementation behaves differently, as the value of PIPN is not changed after the interrupt is serviced in case there is no further request pending.

## <u>DAP TC.002</u> DAP client\_blockread has Performance issue in Specific Operation Modes

For achieving the highest block read bandwidth, the following word is already read chip internally while a word is transmitted on DAP. This read ahead is

TC23x, ES-AC, AC 31/201 Rel. 1.3, 2018-06-11

under certain conditions disabled in the case that the "All parcels with CRC6" bit is set in the telegram. In this case the distance between the reply parcels becomes significantly longer, due to the missing read ahead. This effect occurs also in Wide Mode.

The data values in the parcels are always correct, it is just a performance issue.

#### Workaround

Don't use the "All parcels with CRC6" option, use "Read CRCup" instead.

This mode is anyway better in terms of performance for larger blocks (no CRC6 overhead for each parcel) and data protection (32 bit CRC). For a few words, the impact of this performance issue might be tolerable. For the first word a read ahead is not possible anyway.

#### DAP TC.003 DAP CRC32 definition and algorithm

The DAP CRC32 algorithm is different from the IEEE 802.3 Ethernet CRC.

#### Workaround

Use the following (VHDL) algorithm for each incoming data bit. The CRC32 value is initialized with all ones.

In Wide Mode the function is called for both DAP data bits in each DAP0 clock cycle.

```

crc(7) := bit_new xor crc_now(6) xor crc_now(31);

crc(8) := bit_new xor crc_now(7) xor crc_now(31);

crc(10) := bit_new xor crc_now(9) xor crc_now(31);

crc(11) := bit_new xor crc_now(10) xor crc_now(31);

crc(12) := bit_new xor crc_now(11) xor crc_now(31);

crc(16) := bit_new xor crc_now(15) xor crc_now(31);

crc(22) := bit_new xor crc_now(21) xor crc_now(31);

crc(23) := bit_new xor crc_now(22) xor crc_now(31);

crc(26) := bit_new xor crc_now(25) xor crc_now(31);

return crc;

end calc_crc32_f;

```

## <u>DAP\_TC.004</u> DAP client\_blockwrite telegram with CRC6 and CRC32 protection options

Note: This problem is only relevant for tool development, not for application development.

When issuing a DAP client\_blockwrite telegram from the tool to the device several CRC protection options are available, namely CRC6 and CRC32.

## **Expected Behavior**

- For CRC6 the expected behavior is:

- (1) A CRC6 will be appended to the reply of only the last parcel of the telegram.

- (2) An optional CRC6 can be appended to the devices "single startbit response" by setting DAPISC.RC6.

- For CRC32 the expected behavior is:

- (3) The telegram can optionally send the CRCdown value as the last parcel.

## **Actual Implementation**

- For the actual implementation the CRC6 slightly differs as follows:

- (1) The CRC6 of the last parcel will be erroneous if DAPISC.RC6 is set or if the CRCdown option is enabled.

- (2) If DAPISC.RC6 = 1<sub>B</sub>, an unintentional CRC6 will be appended to the device response of parcels which are not the last parcel.

- For the actual implementation the CRC32 option slightly differs as follows:

- (3) If also the CRC6option is set, the CRCdown option will not return the correct CRCdown value.

#### Workaround for (3)

Workaround for (3) is not to use the CRCdown feature of the client\_blockwrite telegram, but to use the dedicated get\_CRCdown telegram.

## <u>DAP TC.005</u> DAP client\_read: dirty bit feature of Cerberus' Triggered Transfer Mode

Note: This problem is only relevant for tool development, not for application development.

The DAP telegram client\_read reads a certain number of bits from an IOclient (e.g. Cerberus). The parameter k can be selected to be zero, which is supposed to activate reading of 32 bits plus dirty bit.

However, in the current implementation, the dirty bit feature does not work correctly.

It is recommended not to use this dirty bit feature, meaning the number k should not evaluate to "0".

## <u>DAP\_TC.006</u> CRC6 error in telegram following a get\_CRCdown telegram prevents reset of CRC32 calculator

Note: This problem is only relevant for tool development, not for application development.

If a CRC6 error occurs in the telegram following a get\_CRCdown telegram the AURIX™ internal CRC32 calculator does not get reset, as is the expected behavior for get\_CRCdown.

TC23x, ES-AC, AC 34/201 Rel. 1.3, 2018-06-11

This effect can lead to unexpected CRC32 values for the next get\_CRCdown telegram. This corresponds to the perception of the tool that there has been a CRC32 error, even if the data was transmitted correctly.

#### Workaround 1

Accept extra traffic for a required retransmission: In this case the tool could see a CRC32 error which is not based on a wrong transmission, but on the missing reset of the AURIX™ internal CRC32 calculator. This would trigger the retransmission of correctly sent data.

#### Workaround 2

Check for no-reply after a get\_CRCdown telegram: If the tool does not receive an answer for the telegram following a get\_CRCdown, it needs to resend the get\_CRCdown telegram and ignore the data.

## <u>DAP\_TC.007</u> Incomplete client\_blockread telegram in DXCM mode when using the "read CRCup" option

In DXCM (DAP over CAN Messages) mode, the last parcel containing the CRC32 might be skipped in a client\_blockread telegram using the "read CRCup" option.

#### Workaround

Do not use CRCup option with client\_blockread telegrams in DXCM mode. Instead the CRCup can be read by a dedicated getCRCup telegram.

## <u>DAP\_TC.009</u> CRC6 error in client\_blockwrite telegram

Note: This problem is only relevant for tool development, not for application development.

If a CRC6 error happens in a client\_blockwrite telegram, the DAP module will not execute the write and the tool will run into timeout according to the DAP protocol.

TC23x, ES-AC, AC 35/201 Rel. 1.3, 2018-06-11

But in this case a following client\_blockwrite (with start address) will be ignored by the DAP module.

#### Workaround

If the tool is running into a timeout after a client\_blockwrite telegram it should transmit a dummy client\_blockread telegram (e.g. len=0, arbitrary address) which will clean up the DAP client blockwrite function.

### DMA TC.015 DMA Double Buffering: No Timestamp Support

When a DMA channel is configured for DMA Double Buffering, and flow control (or appendage of time stamp) is selected, i.e.  $DMA\_ADICRz$ . STAMP =  $1_B$ , the Move Engine may lock up.

#### Workaround

When a DMA channel is configured for DMA Double Buffering then flow control (or appendage of time stamp) should not be selected, i.e. bit  $DMA\_ADICRz.STAMP$  must be =  $0_B$ .

# <u>DMA TC.016</u> Byte and Half-word Write Accesses to specific Registers not supported

Note: This erratum might affect the SFR C Header Definitions. In such cases, SFR usage in the software shall be analyzed within the applications for their correct handling.

Byte and half-word write accesses via the SPB (System Peripheral Bus) to the Regfile and Request Control logic are not supported.

This affects the following registers:

- DMA\_OTSS (OCDS Trigger Set Select)

- DMA\_ERRINTR (Error Interrupt)

- DMA\_PRR0 (Pattern Read Register 0)

- DMA PRR1 (Pattern Read Register 1)

- DMA\_MODEy (Hardware Resource Mode)

- DMA HRRz (Hardware Resource Partition)

- DMA\_SUSENRz (Channel Suspend Enable)

- DMA TSRz (Transaction State)

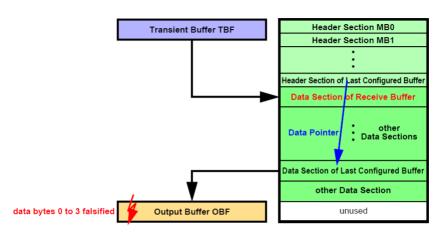

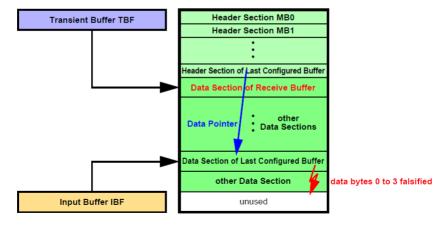

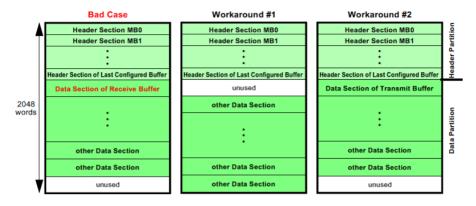

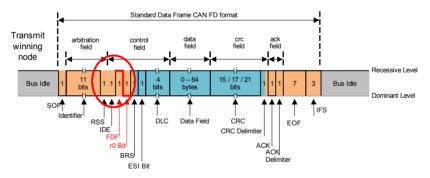

## Workaround