# FemtoClock® Crystal-to-3.3V LVPECL **Clock Generator**

ICS843031

PRODUCT DISCONTINUATION NOTICE - LAST TIME BUY EXPIRES NOVEMBER 2, 2016

**DATA SHEET**

# GENERAL DESCRIPTION

The 843031 is a 1 Gigabit Ethernet Clock Generator. The 843031 can synthesize 1 Gigabit Ethernet, SONET, or Serial ATA reference clock frequencies with the appropriate choice of crystal and output divider. The 843031 has excellent phase jitter performance and is packaged in a small 8-pin TSSOP, making it ideal for use in systems with limited board space.

# **F**EATURES

- One differential 3.3V LVPECL output

- Crystal oscillator interface designed for 18pF parallel resonant crystals

- Output frequency range: 290MHz 350MHz

- VCO frequency range: 580MHz 700MHz

- RMS phase jitter @312.5MHz (1.875MHz 20MHz): 0.475ps (typical)

RMS phase jitter @318.75MHz (1.875MHz - 20MHz): 0.475ps (typical)

- · 3.3V operating supply

- 0°C to 70°C ambient operating temperature

- Available in lead-free (RoHS 6) package

- For functional replacement part use 843031i-01

## FREQUENCY TABLE

| Inputs                  | M/N Ratio (Multiplier) | Output Frequency |

|-------------------------|------------------------|------------------|

| Crystal Frequency (MHz) |                        | (MHz)            |

| 25.92                   | 12                     | 311.04           |

| 26.04166                | 12                     | 312.5            |

| 26.5625                 | 12                     | 318.75           |

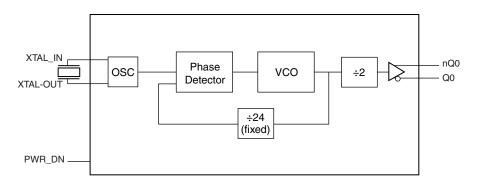

# **BLOCK DIAGRAM**

# PIN ASSIGNMENT

TABLE 1. PIN DESCRIPTIONS

| Number | Name                 | Туре   |        | Description                                                                                            |

|--------|----------------------|--------|--------|--------------------------------------------------------------------------------------------------------|

| 1, 6   | V <sub>cc</sub>      | Power  |        | Core supply pin.                                                                                       |

| 2, 3   | XTAL_OUT,<br>XTAL_IN | Input  |        | Crystal oscillator interface. XTAL_IN is the input, XTAL_OUT is the output.                            |

| 4      | V <sub>EE</sub>      | Power  |        | Negative supply pin.                                                                                   |

| 5      | PWR_DN               | Input  | Pullup | Output state control input. High impedance when LOW (oscillator stops). LVCMOS/LVTTL interface levels. |

| 7, 8   | nQ0, Q0              | Output |        | Differential clock outputs. LVPECL interface levels.                                                   |

NOTE: Pullup refers to internal input resistors. See Table 2, Pin Characterristics, for typical values.

TABLE 2. PIN CHARACTERISTICS

| Symbol              | Parameter             | Test Conditions | Minimum | Typical | Maximum | Units |

|---------------------|-----------------------|-----------------|---------|---------|---------|-------|

| C <sub>IN</sub>     | Input Capacitance     |                 |         | 4       |         | pF    |

| R <sub>PULLUP</sub> | Input Pullup Resistor |                 |         | 51      |         | kΩ    |

### **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage,  $V_{CC}$ 4.6V

-0.5V to  $V_{CC} + 0.5V$ Inputs, V<sub>1</sub>

$\begin{array}{c} \text{Outputs, I}_{\text{O}} \\ \text{Continuous Current} \end{array}$ 50mA Surge Current 100mA

Package Thermal Impedance,  $\theta_{\text{JA}}$  101.7°C/W (0 mps) -65°C to 150°C Storage Temperature,  $T_{STG}$

NOTE: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in the DC Characteristics or AC Characteristics is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

Table 3A. Power Supply DC Characteristics,  $V_{cc} = 3.3V \pm 5\%$ , Ta=0°C to 70°C

| Symbol          | Parameter            | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------------|----------------------|-----------------|---------|---------|---------|-------|

| V <sub>cc</sub> | Core Supply Voltage  |                 | 3.135   | 3.3     | 3.465   | V     |

|                 | Dower Cumply Current | PWR_DN = 1      |         |         | 105     | mA    |

| LEE .           | Power Supply Current | PWR_DN = 0      |         |         | <1      | mA    |

Table 3B. LVCMOS/LVTTL DC Characteristics,  $V_{CC} = 3.3V \pm 5\%$ , Ta=0°C to 70°C

| Symbol          | Parameter          |        | Test Conditions                | Minimum | Typical | Maximum               | Units |

|-----------------|--------------------|--------|--------------------------------|---------|---------|-----------------------|-------|

| V <sub>IH</sub> | Input High Voltage |        |                                | 2       |         | V <sub>cc</sub> + 0.3 | V     |

| V <sub>IL</sub> | Input Low Voltage  |        |                                | -0.3    |         | 0.8                   | V     |

| I <sub>IH</sub> | Input High Current | PWR_DN | $V_{CC} = V_{IN} = 3.465V$     |         |         | 5                     | μA    |

| I               | Input Low Current  | PWR_DN | $V_{CC} = 3.465V, V_{IN} = 0V$ | -150    |         |                       | μA    |

Table 3C. LVPECL DC Characteristics,  $V_{CC} = 3.3V \pm 5\%$ , Ta=0°C to 70°C

| Symbol             | Parameter                         | Test Conditions | Minimum               | Typical | Maximum               | Units |

|--------------------|-----------------------------------|-----------------|-----------------------|---------|-----------------------|-------|

| V <sub>OH</sub>    | Output High Voltage; NOTE 1       |                 | V <sub>cc</sub> - 1.4 |         | V <sub>cc</sub> - 0.9 | ٧     |

| V <sub>OL</sub>    | Output Low Voltage; NOTE 1        |                 | V <sub>cc</sub> - 2.0 |         | V <sub>cc</sub> - 1.7 | V     |

| V <sub>SWING</sub> | Peak-to-Peak Output Voltage Swing |                 | 0.6                   |         | 1.0                   | V     |

NOTE 1: Outputs terminated with  $50\Omega$  to  $\mathrm{V}_{\mathrm{CC}}$  - 2V.

TABLE 4. CRYSTAL CHARACTERISTICS

| Parameter                          | Test Conditions | Minimum     | Typical | Maximum | Units |

|------------------------------------|-----------------|-------------|---------|---------|-------|

| Mode of Oscillation                |                 | Fundamental |         |         |       |

| Frequency                          |                 | 12          |         | 40      | MHz   |

| Equivalent Series Resistance (ESR) |                 |             |         | 50      | Ω     |

| Shunt Capacitance                  |                 |             |         | 7       | pF    |

| Drive Level                        |                 |             |         | 1       | mW    |

Table 5. AC Characteristics,  $V_{\text{CC}}$  = 3.3V±5%, Ta=0°C to 70°C

| Symbol            | Parameter                            | Test Conditions                                    | Minimum | Typical | Maximum | Units |

|-------------------|--------------------------------------|----------------------------------------------------|---------|---------|---------|-------|

| f <sub>out</sub>  | Output Frequency                     |                                                    | 290     |         | 350     | MHz   |

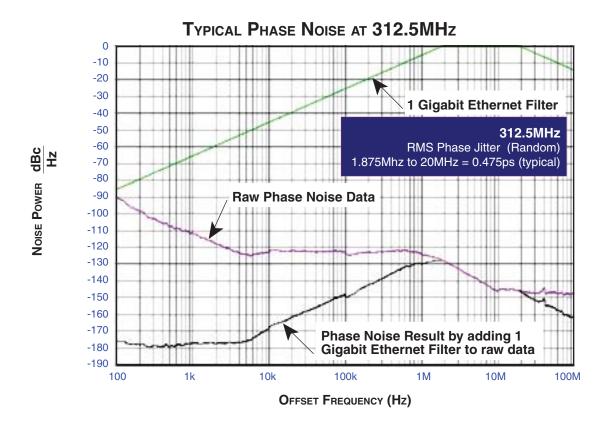

| +ii+( <i>C</i> X) | RMS Phase Jitter (Random);<br>NOTE 1 | 312.5MHz, Integration Range:<br>1.875MHz to 20MHz  |         | 0.475   |         | ps    |

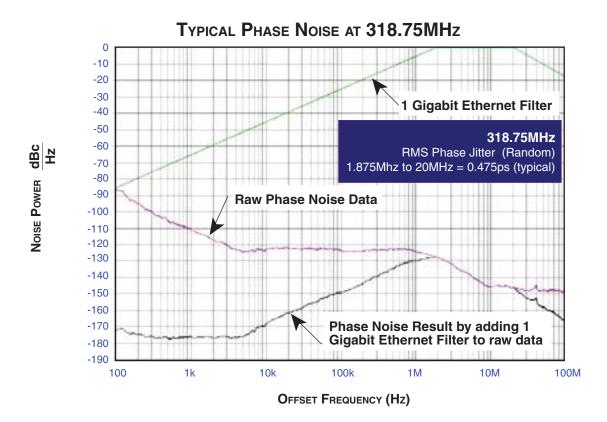

| tjit(Ø)           |                                      | 318.75MHz, Integration Range:<br>1.875MHz to 20MHz |         | 0.475   |         | ps    |

| $t_R / t_F$       | Output Rise/Fall Time                | 20% to 80%                                         | 200     |         | 600     | ps    |

| odc               | Output Duty Cycle                    |                                                    | 46      |         | 54      | %     |

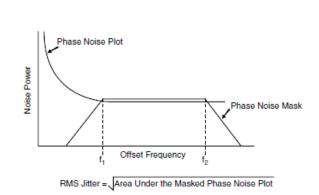

NOTE 1: Please refer to the Phase Noise Plot.

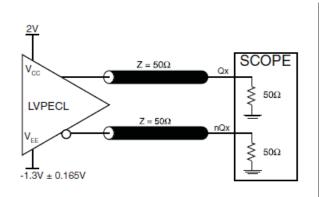

# PARAMETER MEASUREMENT INFORMATION

# 3.3V OUTPUT LOAD AC TEST CIRCUIT

# RMS PHASE JITTER

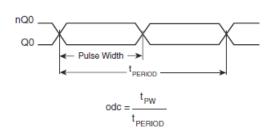

# OUTPUT DUTY CYCLE/PULSE WIDTH/PERIOD

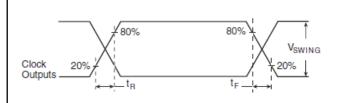

# OUTPUT RISE/FALL TIME

# **APPLICATION INFORMATION**

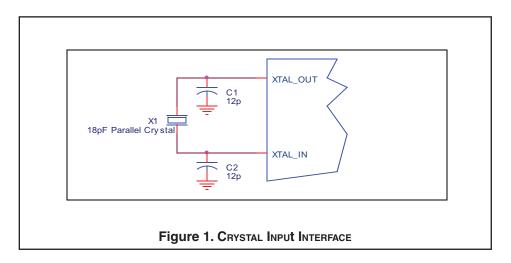

### CRYSTAL INPUT INTERFACE

The 843031 has been characterized with 18pF parallel resonant crystals. The capacitor values, C1 and C2, shown in *Figure 1* below were determined using a 26.04167MHz, 18pF

parallel resonant crystal and were chosen to minimize the ppm error. The optimum C1 and C2 values can be slightly adjusted for different board layouts.

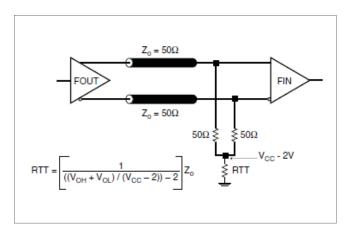

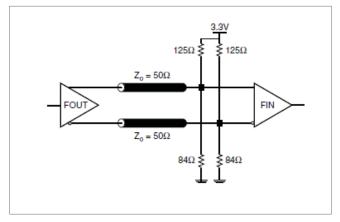

# **TERMINATION FOR 3.3V LVPECL OUTPUT**

The clock layout topology shown below is a typical termination for LVPECL outputs. The two different layouts mentioned are recommended only as guidelines.

FOUT and nFOUT are low impedance follower outputs that generate ECL/LVPECL compatible outputs. Therefore, terminating resistors (DC current path to ground) or current sources must be used for functionality. These outputs are designed to

drive  $50\Omega$  transmission lines.Matched impedance techniques should be used to maximize operating frequency and minimize signal distortion. *Figures 2A and 2B* show two different layouts which are recommended only as guidelines. Other suitable clock layouts may exist and it would be recommended that the board designers simulate to guarantee compatibility across all printed circuit and clock component process variations.

FIGURE 2A. LVPECL OUTPUT TERMINATION

FIGURE 2B. LVPECL OUTPUT TERMINATION

# Power Considerations

This section provides information on power dissipation and junction temperature for the ICS843051. Equations and example calculations are also provided.

### 1. Power Dissipation.

The total power dissipation for the ICS843051 is the sum of the core power plus the power dissipated in the load(s). The following is the power dissipation for  $V_{CC} = 3.3V + 5\% = 3.465V$ , which gives worst case results.

NOTE: Please refer to Section 3 for details on calculating power dissipated in the load.

- Power (core)<sub>MAX</sub> = V<sub>CC\_MAX</sub> \* I<sub>EE\_TYP</sub> = 3.465V \* 105mA = 363.83mW

- Power (outputs)<sub>MAX</sub> = 30mW/Loaded Output pair

Total Power  $_{MAX}$  (3.465V, with all outputs switching) = 363.8mW + 30mW = 393.8mW

### 2. Junction Temperature.

Junction temperature, Tj, is the temperature at the junction of the bond wire and bond pad and directly affects the reliability of the device. The maximum recommended junction temperature for the devices is 125°C.

The equation for Tj is as follows: Tj =  $\theta_{JA}$  \* Pd\_total + TA

Tj = Junction Temperature

$\theta_{JA} = Junction-to-Ambient Thermal Resistance$

Pd\_total = Total Device Power Dissipation (example calculation is in section 1 above)

T<sub>A</sub> = Ambient Temperature

In order to calculate junction temperature, the appropriate junction-to-ambient thermal resistance  $\theta$ <sup>JA</sup> must be used. Assuming a moderate air flow of 1 meter per second and a multi-layer board, the appropriate value is  $90.5^{\circ}$ C/W per Table 6 below.

Therefore, Tj for an ambient temperature of 70°C with all outputs switching is:

$70^{\circ}\text{C} + 0.394\text{W} * 90.5^{\circ}\text{C/W} = 105.65^{\circ}\text{C}$ . This is well below the limit of  $125^{\circ}\text{C}$ .

This calculation is only an example. Tj will obviously vary depending on the number of loaded outputs, supply voltage, air flow, and the type of board (single layer or multi-layer).

Table 6. Thermal Resistance  $\theta$  Ja for 8-pin TSSOP, Forced Convection

# θ<sub>JA</sub> by Velocity (Meters per Second) 0 1 2.5 Multi-Layer PCB, JEDEC Standard Test Boards 101.7°C/W 90.5°C/W 89.8°C/W

### 3. Calculations and Equations.

The purpose of this section is to derive the power dissipated into the load.

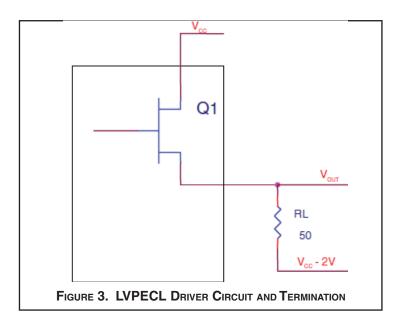

LVPECL output driver circuit and termination are shown in Figure 4.

To calculate worst case power dissipation into the load, use the following equations which assume a  $50\Omega$  load, and a termination voltage of  $V_{cc}$ - 2V.

• For logic high,

$$V_{OUT} = V_{OH\_MAX} = V_{CC\_MAX} - 0.9V$$

$$(V_{CCO\_MAX} - V_{OH\_MAX}) = 0.9V$$

• For logic low,

$$V_{OUT} = V_{OL\_MAX} = V_{CC\_MAX} - 1.7V$$

$$(V_{CCO\_MAX} - V_{OL\_MAX}) = 1.7V$$

Pd\_H is power dissipation when the output drives high. Pd\_L is the power dissipation when the output drives low.

$$Pd_{-}H = [(V_{OH\_MAX} - (V_{CC\_MAX} - 2V))/R_{L}] * (V_{CC\_MAX} - V_{OH\_MAX}) = [(2V - (V_{CC\_MAX} - V_{OH\_MAX}))/R_{L}] * (V_{CC\_MAX} - V_{OH\_MAX}) = [(2V - 0.9V)/50\Omega] * 0.9V = 19.8mW$$

$$Pd\_L = [(V_{OL\_MAX} - (V_{CC\_MAX} - 2V))/R_L] * (V_{CC\_MAX} - V_{OL\_MAX}) = [(2V - (V_{CC\_MAX} - V_{OL\_MAX}))/R_L] * (V_{CC\_MAX} - V_{OL\_MAX}) = [(2V - 1.7V)/50\Omega] * 1.7V = 10.2mW$$

Total Power Dissipation per output pair = Pd\_H + Pd\_L = 30mW

# **RELIABILITY INFORMATION**

Table 7.  $\boldsymbol{\theta}_{\text{JA}} \text{vs. Air Flow Table for 8 Lead TSSOP}$

$\theta_{\text{JA}}$  by Velocity (Meters per Second)

0

1

2.5

Multi-Layer PCB, JEDEC Standard Test Boards

101.7°C/W

90.5°C/W

89.8°C/W

# **TRANSISTOR COUNT**

The transistor count for 843031 is: 2360

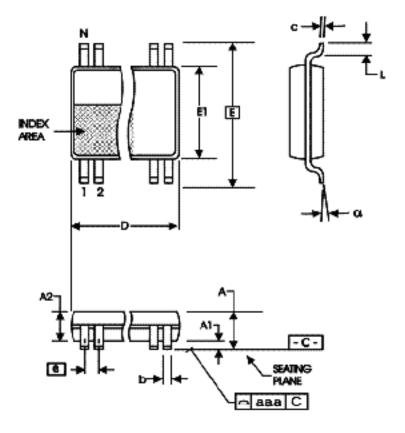

# PACKAGE OUTLINE - G SUFFIX FOR 8 LEAD TSSOP

TABLE 8. PACKAGE DIMENSIONS

| SYMBOL | Millim  | neters  |

|--------|---------|---------|

| STWBOL | Minimum | Maximum |

| N      | 8       | 3       |

| А      |         | 1.20    |

| A1     | 0.05    | 0.15    |

| A2     | 0.80    | 1.05    |

| b      | 0.19    | 0.30    |

| С      | 0.09    | 0.20    |

| D      | 2.90    | 3.10    |

| E      | 6.40 E  | BASIC   |

| E1     | 4.30    | 4.50    |

| е      | 0.65 E  | BASIC   |

| L      | 0.45    | 0.75    |

| α      | 0°      | 8°      |

| aaa    |         | 0.10    |

Reference Document: JEDEC Publication 95, MO-153

TABLE 9. ORDERING INFORMATION

| Part/Order Number | Marking | Package                  | Shipping Packaging | Temperature |

|-------------------|---------|--------------------------|--------------------|-------------|

| 843031AGLF        | 031AL   | 8 lead "Lead-Free" TSSOP | tube               | 0°C to 70°C |

| 843031AGLFT       | 031AL   | 8 lead "Lead-Free" TSSOP | tape & reel        | 0°C to 70°C |

NOTE: Parts that are ordered with an "LF" suffix to the part number are the Pb-Free configuration and are RoHS compliant.

While the information presented herein has been checked for both accuracy and reliability, Integrated Device Technology, Incorporated (IDT) assumes no responsibility for either its use or for infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications such as those requiring extended temperature range, high reliability, or other extraordinary environmental requirements are not recommended without additional processing by IDT. IDT reserves the right to change any circuitry or specifications without notice. IDT does not authorize or warrant any IDT product for use in life support devices or critical medical instruments.

|     | REVISION HISTORY SHEET |         |                                                                                                                                                                                          |           |  |  |

|-----|------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|

| Rev | Table                  | Page    | Description of Change                                                                                                                                                                    | Date      |  |  |

| А   | Т9                     | 1<br>12 | Features Section - deleted duplicate phase jitter bullet. Ordering Information Table - deleted ICS prefix from part order number. Added LF marking. Updated header/footer with IDT logo. | 10/5/2011 |  |  |

| А   | T9                     | 12      | Ordering Information - removed leaded devices. Updated contact information.                                                                                                              | 10/14/15  |  |  |

| А   |                        | 1       | Product Discontinuation Notice - Last time buy expires November 2, 2016. PDN# CQ-15-05.                                                                                                  | 11/5/15   |  |  |

**Corporate Headquarters**

6024 Silver Creek Valley Road San Jose, California 95138 Sales

800-345-7015 or +408-284-8200 Fax: 408-284-2775 www.IDT.com Technical Support email: clocks@idt.com

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described herein at any time and at IDT's sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are registered trademarks of IDT. Other trademarks and service marks used herein, including protected names, logos and designs, are the property of IDT or their respective third party owners.