# Low Skew, ÷1, ÷2 LVCMOS/LVTTL Clock Generator

**DATA SHEET**

# **General Description**

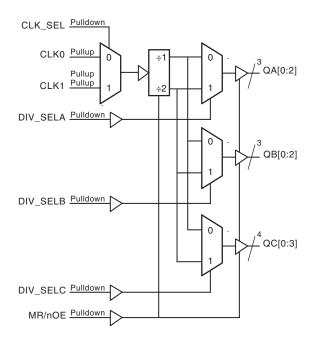

The ICS87946I-147 is a low skew, ÷1, ÷2 LVCMOS/LVTTL Clock Generator and a member of the HiPerClockS™ family of High Performance Clock Solutions from IDT. The ICS87946I-147 has two selectable single ended clock inputs. The single ended

clock inputs accept LVCMOS or LVTTL input levels. The low impedance LVCMOS/LVTTL outputs are designed to drive  $50\Omega$  series or parallel terminated transmission lines. The effective fanout can be increased from 10 to 20 by utilizing the ability of the outputs to drive two series terminated lines.

The divide select inputs, DIV\_SELx, control the output frequency of each bank. The outputs can be utilized in the  $\div 1$ ,  $\div 2$  or a combination of  $\div 1$  and  $\div 2$  modes. The master reset input, MR/nOE, resets the internal frequency dividers and also controls the active and high impedance states of all outputs.

The ICS87946I-147 is characterized at full 3.3V for input  $V_{DD_i}$  and mixed 3.3V and 2.5V for output operating supply mode. Guaranteed bank, output and part-to-part skew characteristics make the ICS87946I-147 ideal for those clock distribution applications demanding well defined performance and repeatability.

#### **Features**

- Ten single ended LVCMOS/LVTTL outputs,

7Ω typical output impedance

- Selectable LVCMOS/LVTTL CLK0 and CLK1 inputs

- CLK0 and CLK1 can accept the following input levels: LVCMOS and LVTTL

- Maximum input frequency: 250MHz

- Bank skew: 30ps (maximum)

- Output skew: 175ps (maximum)

- Part-to-part skew: 850ps (maximum)

- Multiple frequency skew: 200ps (maximum)

- 3.3V core, 3.3V or 2.5V output supply modes

- -40°C to 85°C ambient operating temperature

- Available in both standard (RoHS 5) and lead-free (RoHS 6) packages

# **Block Diagram**

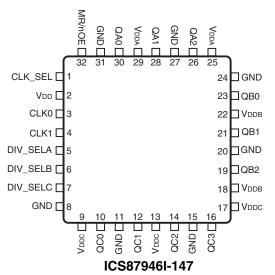

# **Pin Assignment**

32-Lead LQFP 7mm x 7mm x 1.4mm package body Y Package Top View

**Table 1. Pin Descriptions**

| Number                       | Name                  | Т      | уре      | Description                                                                                                                                                                                                                                               |

|------------------------------|-----------------------|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                            | CLK_SEL               | Input  | Pulldown | Clock select input. When HIGH, selects CLK1. When LOW, selects CLK0. LVCMOS / LVTTL interface levels.                                                                                                                                                     |

| 2                            | $V_{DD}$              | Power  |          | Positive supply pin.                                                                                                                                                                                                                                      |

| 3, 4                         | CLK0, CLK1            | Input  | Pullup   | Single-ended clock inputs. LVCMOS/LVTTL interface levels.                                                                                                                                                                                                 |

| 5                            | DIV_SELA              | Input  | Pulldown | Controls frequency division for Bank A outputs. See Table 3 LVCMOS/LVTTL interface levels.                                                                                                                                                                |

| 6                            | DIV_SELB              | Input  | Pulldown | Controls frequency division for Bank B outputs. See Table 3. LVCMOS/LVTTL interface levels.                                                                                                                                                               |

| 7                            | DIV_SELC              | Input  | Pulldown | Controls frequency division for Bank C outputs. See Table 3. LVCMOS/LVTTL interface levels.                                                                                                                                                               |

| 8, 11, 15, 20,<br>24, 27, 31 | GND                   | Power  |          | Power supply ground.                                                                                                                                                                                                                                      |

| 9, 13, 17                    | $V_{\mathrm{DDC}}$    | Power  |          | Output supply pins for Bank C outputs.                                                                                                                                                                                                                    |

| 10, 12,<br>14, 16            | QC0, QC1,<br>QC2, QC3 | Output |          | Single-ended Bank C clock outputs. LVCMOS/LVTTL interface levels. $7\Omega$ typical output impedance.                                                                                                                                                     |

| 18, 22                       | $V_{DDB}$             | Power  |          | Output supply pins for Bank B outputs.                                                                                                                                                                                                                    |

| 19,<br>21, 23                | QB2,<br>QB1, QB0      | Output |          | Single-ended Bank B clock outputs. LVCMOS/LVTTL interface levels. $7\Omega$ typical output impedance.                                                                                                                                                     |

| 25, 29                       | $V_{DDA}$             | Power  |          | Output supply pins for Bank A outputs.                                                                                                                                                                                                                    |

| 26,<br>28, 30                | QA2,<br>QA1, QA0      | Output |          | Single-ended Bank A clock outputs. LVCMOS/LVTTL interface levels. $7\Omega$ typical output impedance.                                                                                                                                                     |

| 32                           | MR/nOE                | Input  | Pulldown | Active HIGH Master Reset. Active LOW Output Enable. When logic HIGH, the internal dividers are reset and the outputs are (High-Impedance). When logic LOW, the internal dividers and the outputs are enabled. See Table 3. LVCMOS/LVTTL interface levels. |

NOTE: Pullup and Pulldown refer to internal input resistors. See Table 2, Pin Characteristics, for typical values.

## **Table 2. Pin Characteristics**

| Symbol                | Parameter                     | Test Conditions                               | Minimum | Typical | Maximum | Units |

|-----------------------|-------------------------------|-----------------------------------------------|---------|---------|---------|-------|

| C <sub>IN</sub>       | Input Capacitance             |                                               |         |         | 4       | pF    |

| C <sub>PD</sub>       | Power Dissipation Capacitance | $V_{DD} = V_{DDA} = V_{DDB} = V_{DDC} = 3.6V$ |         | 25      |         | pF    |

| R <sub>PULLUP</sub>   | Input Pullup Resistor         |                                               |         | 51      |         | kΩ    |

| R <sub>PULLDOWN</sub> | Input Pulldown Resistor       |                                               |         | 51      |         | kΩ    |

| R <sub>OUT</sub>      | Output Impedance              |                                               |         | 7       |         | Ω     |

#### **Function Tables**

**Table 3. Clock Input Function Table**

| Inputs |          |          |          | Outputs            |                    |                    |

|--------|----------|----------|----------|--------------------|--------------------|--------------------|

| MR/nOE | DIV_SELA | DIV_SELB | DIV_SELC | QA0:QA2            | QB0:QB2            | QC0:QC3            |

| 1      | Х        | Х        | Х        | High-Impedance     | High-Impedance     | High-Impedance     |

| 0      | 0        | Х        | Х        | f <sub>IN</sub> /1 | Active             | Active             |

| 0      | 1        | Х        | Х        | f <sub>IN</sub> /2 | Active             | Active             |

| 0      | Х        | 0        | Х        | Active             | f <sub>IN</sub> /1 | Active             |

| 0      | Х        | 1        | Х        | Active             | f <sub>IN</sub> /2 | Active             |

| 0      | Х        | Х        | 0        | Active             | Active             | f <sub>IN</sub> /1 |

| 0      | Х        | Х        | 1        | Active             | Active             | f <sub>IN</sub> /2 |

# **Absolute Maximum Ratings**

NOTE: Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in the *DC Characteristics* or *AC Characteristics* is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

| Item                                     | Rating                           |  |

|------------------------------------------|----------------------------------|--|

| Supply Voltage, V <sub>DD</sub>          | 4.6V                             |  |

| Inputs, V <sub>I</sub>                   | -0.5V to V <sub>DD</sub> + 0.5V  |  |

| Outputs, V <sub>O</sub>                  | -0.5V to V <sub>DDX</sub> + 0.5V |  |

| Package Thermal Impedance, $\theta_{JA}$ | 47.9°C/W (0 lfpm)                |  |

| Storage Temperature, T <sub>STG</sub>    | -65°C to 150°C                   |  |

#### **DC Electrical Characteristics**

Table 4A. Power Supply DC Characteristics,  $V_{DD} = V_{DDA} = V_{DDB} = V_{DDC} = 3.3V \pm 0.3V$ ,  $T_A = -40^{\circ}C$  to  $85^{\circ}C$

| Symbol                                                 | Parameter               | Test Conditions | Minimum | Typical | Maximum | Units |

|--------------------------------------------------------|-------------------------|-----------------|---------|---------|---------|-------|

| $V_{DD}$                                               | Positive Supply Voltage |                 | 3.0     | 3.3     | 3.6     | V     |

| $V_{DDA}, V_{DDB}, V_{DDC}$                            | Output Supply Voltage   |                 | 3.0     | 3.3     | 3.6     | V     |

| I <sub>DD</sub>                                        | Power Supply Current    |                 |         |         | 55      | mA    |

| I <sub>DDA</sub> , I <sub>DDB</sub> , I <sub>DDC</sub> | Output Supply Current   |                 |         |         | 23      | mA    |

$\textbf{Table 4B. Power Supply DC Characteristics, } V_{DD} = 3.3V \pm 5\%, \ V_{DDA} = V_{DDB} = V_{DDC} = 2.5V \pm 5\%, \ T_{A} = -40^{\circ}C \ to \ 85^{\circ}C$

| Symbol                                                 | Parameter               | Test Conditions | Minimum | Typical | Maximum | Units |

|--------------------------------------------------------|-------------------------|-----------------|---------|---------|---------|-------|

| $V_{DD}$                                               | Positive Supply Voltage |                 | 3.135   | 3.3     | 3.465   | V     |

| $V_{DDA}, V_{DDB}, V_{DDC}$                            | Output Supply Voltage   |                 | 2.375   | 2.5     | 2.625   | V     |

| I <sub>DD</sub>                                        | Power Supply Current    |                 |         |         | 55      | mA    |

| I <sub>DDA</sub> , I <sub>DDB</sub> , I <sub>DDC</sub> | Output Supply Current   |                 |         |         | 22      | mA    |

Table 4C. LVCMOS/LVTTL DC Characteristics,  $V_{DD} = V_{DDA} = V_{DDB} = V_{DDC} = 3.3V \pm 0.3V$ ,  $T_A = -40^{\circ}C$  to  $85^{\circ}C$

| Symbol           | Parameter                  |                                                     | Test Conditions                              | Minimum | Typical | Maximum               | Units |

|------------------|----------------------------|-----------------------------------------------------|----------------------------------------------|---------|---------|-----------------------|-------|

| V <sub>IH</sub>  | Input High                 | Voltage                                             |                                              | 2       |         | V <sub>DD</sub> + 0.3 | V     |

| Input Low        |                            | MR/nOE,<br>DIV_SELA, DIV_SELB,<br>DIV_SELC, CLK_SEL |                                              | -0.3    |         | 0.8                   | V     |

|                  | Voltage                    | CLK0, CLK1                                          |                                              | -0.3    |         | 1.3                   | V     |

| I <sub>IH</sub>  | Input<br>High              | MR/nOE,<br>DIV_SELA, DIV_SELB,<br>DIV_SELC, CLK_SEL | $V_{DD} = V_{IN} = 3.6V$                     |         |         | 150                   | μΑ    |

|                  | Current                    | CLK0, CLK1                                          | $V_{DD} = V_{IN} = 3.6V$                     |         |         | 5                     | μΑ    |

| I <sub>IL</sub>  | Input<br>Low<br>Current    | MR/nOE,<br>DIV_SELA, DIV_SELB,<br>DIV_SELC, CLK_SEL | V <sub>DD</sub> = 3.6V, V <sub>IN</sub> = 0V | -5      |         |                       | μА    |

|                  | Current                    | CLK0, CLK1                                          | $V_{DD} = 3.6V, V_{IN} = 0V$                 | -150    |         |                       | μΑ    |

| V <sub>OH</sub>  | Output Hig                 | gh Voltage; NOTE 1                                  | $V_{DDA} = V_{DDB} = V_{DDC} = 3.6V$         | 2.6     |         |                       | V     |

| V <sub>OL</sub>  | Output Low Voltage; NOTE 1 |                                                     | $V_{DDA} = V_{DDB} = V_{DDC} = 3.63V$        |         |         | 0.5                   | V     |

| I <sub>OZL</sub> | Output Hi-Z Current Low    |                                                     | $V_{DDA} = V_{DDB} = V_{DDC} = 3.63V$        | -5      |         |                       | μΑ    |

| I <sub>OZH</sub> | Output Hi-                 | Z Current High                                      | $V_{DDA} = V_{DDB} = V_{DDC} = 3.63V$        |         |         | 5                     | μΑ    |

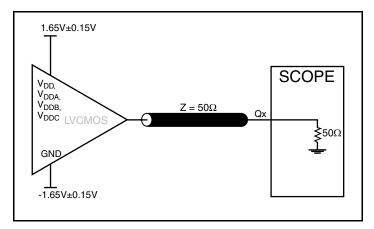

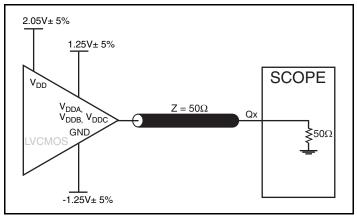

NOTE 1: Outputs terminated with  $50\Omega$  to  $V_{DDx}/2$ . See Parameter Measurement Information section. Load Test Circuit diagrams.

$\textbf{Table 4D. LVCMOS/LVTTL DC Characteristics, } V_{DD} = 3.3V \pm 5\%, \ V_{DDA} = V_{DDB} = V_{DDC} = 2.5V \pm 5\%, \ T_{A} = -40^{\circ}C \ to \ 85^{\circ}C$

| Symbol           | Parameter                      |                                                     | Test Conditions                                | Minimum | Typical | Maximum               | Units |

|------------------|--------------------------------|-----------------------------------------------------|------------------------------------------------|---------|---------|-----------------------|-------|

| V <sub>IH</sub>  | Input High                     | Voltage                                             |                                                | 2       |         | V <sub>DD</sub> + 0.3 | V     |

| V <sub>IL</sub>  | Input<br>Low                   | MR/nOE,<br>DIV_SELA, DIV_SELB,<br>DIV_SELC, CLK_SEL |                                                | -0.3    |         | 0.8                   | V     |

|                  | Voltage                        | CLK0, CLK1                                          |                                                | -0.3    |         | 1.3                   | V     |

| I <sub>IH</sub>  | Input<br>High                  | MR/nOE,<br>DIV_SELA, DIV_SELB,<br>DIV_SELC, CLK_SEL | $V_{DD} = V_{IN} = 3.465V$                     |         |         | 150                   | μΑ    |

|                  | Current                        | CLK0, CLK1                                          | $V_{DD} = V_{IN} = 3.465V$                     |         |         | 5                     | μΑ    |

| I <sub>IL</sub>  | Input<br>Low                   | MR/nOE,<br>DIV_SELA, DIV_SELB,<br>DIV_SELC, CLK_SEL | V <sub>DD</sub> = 3.465V, V <sub>IN</sub> = 0V | -5      |         |                       | μΑ    |

|                  | Current                        | CLK0, CLK1                                          | V <sub>DD</sub> = 3.465V, V <sub>IN</sub> = 0V | -150    |         |                       | μΑ    |

| V <sub>OH</sub>  | Output High Voltage;<br>NOTE 1 |                                                     | $V_{DDA} = V_{DDB} = V_{DDC} = 2.625V$         | 1.8     |         |                       | V     |

| V <sub>OL</sub>  | Output Low Voltage; NOTE 1     |                                                     | $V_{DDA} = V_{DDB} = V_{DDC} = 2.625V$         |         |         | 0.5                   | V     |

| I <sub>OZL</sub> | Output Hi-Z Current Low        |                                                     | $V_{DDA} = V_{DDB} = V_{DDC} = 2.625V$         | -5      |         |                       | μΑ    |

| I <sub>OZH</sub> | Output Hi-                     | Z Current High                                      | $V_{DDA} = V_{DDB} = V_{DDC} = 2.625V$         |         |         | 5                     | μΑ    |

NOTE 1: Outputs terminated with  $50\Omega$  to  $V_{DDx}/2$ . See Parameter Measurement Information section. Load Test Circuit diagrams.

#### **AC Electrical Characteristics**

Table 5A. AC Characteristics,  $V_{DD} = V_{DDA} = V_{DDB} = V_{DDC} = 3.3V \pm 0.3V$ ,  $T_A = -40^{\circ}C$  to  $85^{\circ}C$

| Symbol                          | Parameter                             | Test Conditions                                | Minimum                    | Typical                | Maximum                    | Units |

|---------------------------------|---------------------------------------|------------------------------------------------|----------------------------|------------------------|----------------------------|-------|

| f <sub>MAX</sub>                | Output Frequency                      |                                                |                            |                        | 250                        | MHz   |

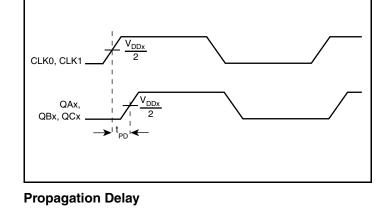

| t <sub>PD</sub>                 | Propagation Delay;<br>NOTE 1          | <i>f</i> ≤ 250MHz                              | 2                          |                        | 5                          | ns    |

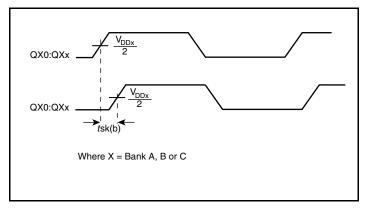

| tsk(b)                          | Bank Skew, NOTE 2, 7                  | Measured on rising edge at V <sub>DDX</sub> /2 |                            |                        | 30                         | ps    |

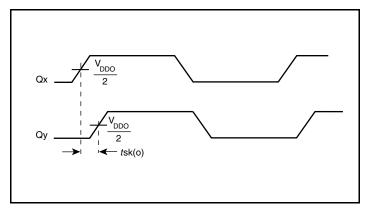

| tsk(o)                          | Output Skew; NOTE 3, 7                | Measured on rising edge at V <sub>DDX</sub> /2 |                            |                        | 175                        | ps    |

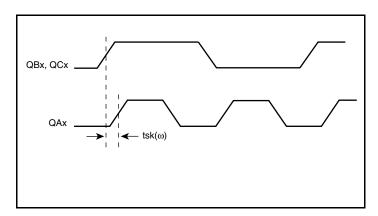

| tsk(w)                          | Multiple Frequency Skew;<br>NOTE 4, 7 | Measured on rising edge at V <sub>DDX</sub> /2 |                            |                        | 275                        | ps    |

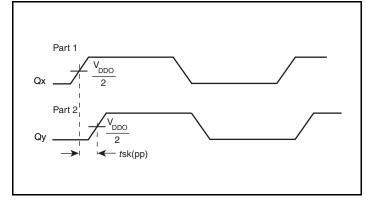

| tsk(pp)                         | Part-to-Part Skew;<br>NOTE 5, 7       | Measured on rising edge at V <sub>DDX</sub> /2 |                            |                        | 850                        | ps    |

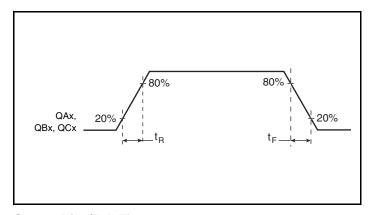

| t <sub>R</sub> / t <sub>F</sub> | Output Rise/Fall Time;<br>NOTE 6      | 20% to 80%                                     | 400                        |                        | 950                        | ps    |

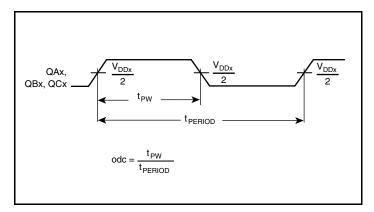

| t <sub>PW</sub>                 | Output Pulse Width                    |                                                | t <sub>PERIOD</sub> /2 - 1 | t <sub>PERIOD</sub> /2 | t <sub>PERIOD</sub> /2 + 1 | %     |

| t <sub>EN</sub>                 | Output Enable Time;<br>NOTE 6         | f= 10MHz                                       |                            |                        | 3                          | ns    |

| t <sub>DIS</sub>                | Output Disable Time;<br>NOTE 6        | f= 10MHz                                       |                            |                        | 3                          | ns    |

NOTE: Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specifications after thermal equilibrium has been reached under these conditions.

- NOTE 1: Measured from  $V_{DD}/2$  of the input to  $V_{DDX}/2$  of the output.

- NOTE 2: Defined as skew within a bank of outputs at the same supply voltage and with equal load conditions.

- NOTE 3: Defined as skew across banks of outputs at the same supply voltage and with equal load conditions. Measured at V<sub>DDX</sub>/2.

- NOTE 4: Defined as skew across banks of outputs operating at different frequencies with the same supply voltage and equal load conditions.

- NOTE 5: Defined as skew between outputs on different devices operating at the same supply voltage and with equal load conditions. Using the same type of inputs on each device, the outputs are measured at  $V_{DDX}/2$ .

- NOTE 6: These parameters are guaranteed by characterization. Not tested in production.

- NOTE 7: This parameter is defined in accordance with JEDEC Standard 65.

Table 5B. AC Characteristics,  $V_{DD}$  = 3.3V  $\pm$  5%,  $V_{DDA}$  =  $V_{DDB}$  =  $V_{DDC}$  = 2.5V  $\pm$  5%,  $T_A$  = -40°C to 85°C

| Symbol                          | Parameter                             | Test Conditions                                | Minimum                    | Typical                | Maximum                    | Units |

|---------------------------------|---------------------------------------|------------------------------------------------|----------------------------|------------------------|----------------------------|-------|

| f <sub>MAX</sub>                | Output Frequency                      |                                                |                            |                        | 250                        | MHz   |

| t <sub>PD</sub>                 | Propagation Delay;<br>NOTE 1          | <i>f</i> ≤ 250MHz                              | 2                          |                        | 5                          | ns    |

| tsk(b)                          | Bank Skew, NOTE 2, 7                  | Measured on rising edge at V <sub>DDX</sub> /2 |                            |                        | 35                         | ps    |

| tsk(o)                          | Output Skew; NOTE 3, 7                | Measured on rising edge at V <sub>DDX</sub> /2 |                            |                        | 175                        | ps    |

| tsk(w)                          | Multiple Frequency Skew;<br>NOTE 4, 7 | Measured on rising edge at V <sub>DDX</sub> /2 |                            |                        | 200                        | ps    |

| tsk(pp)                         | Part-to-Part Skew;<br>NOTE 5, 7       | Measured on rising edge at V <sub>DDX</sub> /2 |                            |                        | 875                        | ps    |

| t <sub>R</sub> / t <sub>F</sub> | Output Rise/Fall Time;<br>NOTE 6      | 20% to 80%                                     | 400                        |                        | 950                        | ps    |

| t <sub>PW</sub>                 | Output Pulse Width                    |                                                | t <sub>PERIOD</sub> /2 - 1 | t <sub>PERIOD</sub> /2 | t <sub>PERIOD</sub> /2 + 1 | %     |

| t <sub>EN</sub>                 | Output Enable Time;<br>NOTE 6         | f= 10MHz                                       |                            |                        | 3                          | ns    |

| t <sub>DIS</sub>                | Output Disable Time;<br>NOTE 6        | f= 10MHz                                       |                            |                        | 3                          | ns    |

NOTE: Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specifications after thermal equilibrium has been reached under these conditions.

- NOTE 1: Measured from  $V_{DD}/2$  of the input to  $V_{DDX}/2$  of the output.

- NOTE 2: Defined as skew within a bank of outputs at the same supply voltage and with equal load conditions.

- NOTE 3: Defined as skew across banks of outputs at the same supply voltage and with equal load conditions. Measured at V<sub>DDX</sub>/2.

- NOTE 4: Defined as skew across banks of outputs operating at different frequencies with the same supply voltage and equal load conditions.

- NOTE 5: Defined as skew between outputs on different devices operating at the same supply voltage and with equal load conditions. Using the same type of inputs on each device, the outputs are measured at  $V_{DDX}/2$ .

- NOTE 6: These parameters are guaranteed by characterization. Not tested in production.

- NOTE 7: This parameter is defined in accordance with JEDEC Standard 65.

## **Parameter Measurement Information**

3.3V Core/3.3V Output Load AC Test Circuit

3.3V Core/2.5V Output Load AC Test Circuit

**Output Skew**

**Part-to-Part Skew**

**Bank Skew**

**Multiple Frequency Skew**

# **Parameter Measurement Information, continued**

t<sub>PW</sub> & t<sub>PERIOD</sub>

**Output Rise/Fall Time**

# **Application Information**

#### **Recommendations for Unused Input and Output Pins**

#### Inputs:

#### **LVCMOS Control Pins**

All control pins have internal pulldowns; additional resistance is not required but can be added for additional protection. A  $1k\Omega$  resistor can be used.

#### **CLK Inputs**

For applications not requiring the use of a clock input, it can be left floating. Though not required, but for additional protection, a  $1 k\Omega$  resistor can be tied from the CLK input to ground.

#### **Outputs:**

#### **LVCMOS Outputs**

All unused LVCMOS output can be left floating. There should be no trace attached.

# **Reliability Information**

Table 6.  $\theta_{JA}$  vs. Air Flow Table for a 32 Lead LQFP

|                                                                                                              | $\theta_{\text{JA}}$ vs. Air Flow |          |          |  |  |

|--------------------------------------------------------------------------------------------------------------|-----------------------------------|----------|----------|--|--|

| Linear Feet per Minute                                                                                       | 0                                 | 200      | 500      |  |  |

| Single-Layer PCB, JEDEC Standard Test Boards                                                                 | 67.8°C/W                          | 55.9°C/W | 50.1°C/W |  |  |

| Multi-Layer PCB, JEDEC Standard Test Boards 47.9°C/W 42.1°C/W 39.4°C/W                                       |                                   |          |          |  |  |

| NOTE: Most modern PCB designs use multi-layered boards. The data in the second row pertains to most designs. |                                   |          |          |  |  |

#### **Transistor Count**

The transistor count for ICS87946I-147 is: 1204 Pin compatible to the MPC9446 and MPC946

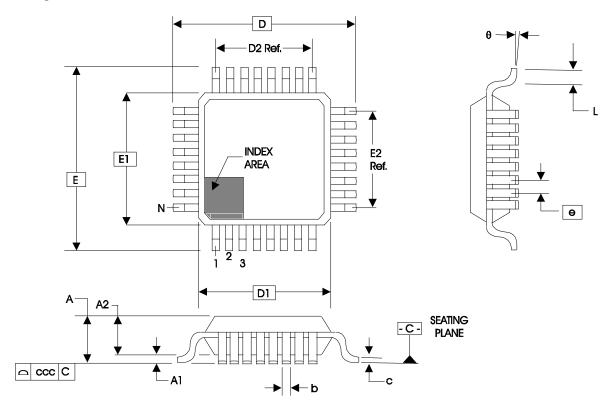

# Package Outline and Package DimensionS

Package Outline - Y Suffix for 32 Lead LQFP

Table 7. Package Dimensions for 32 Lead LQFP

| JEDEC Variation: BBC - HD All Dimensions in Millimeters |         |            |         |  |  |  |  |

|---------------------------------------------------------|---------|------------|---------|--|--|--|--|

| Symbol                                                  | Minimum | Nominal    | Maximum |  |  |  |  |

| N                                                       |         | 32         |         |  |  |  |  |

| Α                                                       |         |            | 1.60    |  |  |  |  |

| A1                                                      | 0.05    | 0.10       | 0.15    |  |  |  |  |

| A2                                                      | 1.35    | 1.40       | 1.45    |  |  |  |  |

| b                                                       | 0.30    | 0.37       | 0.45    |  |  |  |  |

| С                                                       | 0.09    |            | 0.20    |  |  |  |  |

| D&E                                                     |         | 9.00 Basic |         |  |  |  |  |

| D1 & E1                                                 |         | 7.00 Basic |         |  |  |  |  |

| D2 & E2                                                 |         | 5.60 Ref.  |         |  |  |  |  |

| е                                                       |         | 0.80 Basic |         |  |  |  |  |

| L                                                       | 0.45    | 0.60       | 0.75    |  |  |  |  |

| θ                                                       | 0°      | 0° 7°      |         |  |  |  |  |

| ccc                                                     |         |            | 0.10    |  |  |  |  |

Reference Document: JEDEC Publication 95, MS-026

# **Ordering Information**

#### **Table 8. Ordering Information**

| Part/Order Number | Marking       | Package                  | Shipping Packaging | Temperature   |

|-------------------|---------------|--------------------------|--------------------|---------------|

| 87946AYI-147      | ICS87946AI147 | 32 Lead LQFP             | Tray               | -40°C to 85°C |

| 87946AYI-147T     | ICS87946AI147 | 32 Lead LQFP             | 1000 Tape & Reel   | -40°C to 85°C |

| 87946AYI-147LF    | ICS7946AI147L | "Lead-Free" 32 Lead LQFP | Tray               | -40°C to 85°C |

| 87946AYI-147LFT   | ICS7946AI147L | "Lead-Free" 32 Lead LQFP | 1000 Tape & Reel   | -40°C to 85°C |

NOTE: Parts that are ordered with an "LF" suffix to the part number are the Pb-Free configuration and are RoHS compliant.

While the information presented herein has been checked for both accuracy and reliability, Integrated Device Technology (IDT) assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial and industrial applications. Any other applications, such as those requiring high reliability or other extraordinary environmental requirements are not recommended without additional processing by IDT. IDT reserves the right to change any circuitry or specifications without notice. IDT does not authorize or warrant any IDT product for use in life support devices or critical medical instruments.

# **Revision History Sheet**

| Rev | Table     | Page  | Description of Change                                                                   | Date    |

|-----|-----------|-------|-----------------------------------------------------------------------------------------|---------|

| Α   |           | 1     | Features section added <i>Lead-Free</i> bullet.                                         |         |

|     | T2        | 2     | Pin Description Table - corrected description for $V_{DDA}$ , $V_{DDB}$ and $V_{DDC}$ . |         |

|     |           | 8     | Parameter Measurement Information Section - added part-to-part skew, bank               |         |

|     |           | 4.0   | skew, and multiple frequency skew diagrams.                                             | 7/22/08 |

|     |           | 10    | Application Section - added Recommendations for Unused Input and Output                 |         |

|     |           |       | Pins.                                                                                   |         |

|     | Т8        | 12    | Ordering Information Table - added lead-free marking.                                   |         |

|     |           |       | Updated format throughout the datasheet.                                                |         |

| Α   |           |       | AC Tables - added thermal note.                                                         |         |

|     | T5A - T5B | 6 - 7 | Ordering Information Table - corrected the Part/Order Numbers and corrected             | 8/7/09  |

|     | T8        | 12    | the non-LF marking.                                                                     | 0/7/09  |

|     |           |       | Updated Header/Footer of the datasheet.                                                 |         |

|     |           |       |                                                                                         |         |

|     |           |       |                                                                                         |         |

6024 Silver Creek Valley Road San Jose, California 95138 **Sales** 800-345-7015 (inside USA) +408-284-8200 (outside USA) Fax: 408-284-2775 www.IDT.com/go/contactIDT Technical Support netcom@idt.com +480-763-2056

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described herein at any time and at IDT's sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are registered trademarks of IDT. Other trademarks and service marks used herein, including protected names, logos and designs, are the property of IDT or their respective third party owners.