# DATASHEET

## TEN CHANNEL HD AUDIO CODEC

# 92HD73E

## **Description**

The 92HD73E codec is a low power optimized, high fidelity, 10-channel audio codec compatible with Intel's High Definition (HD) Audio Interface. The 92HD73E codec provides stereo 24-bit resolution with sample rates up to 192kHz. Dual SPDIF provides connectivity to consumer electronic equipment that is WLP compliant. The 92HD73E provides high quality, HD Audio capability to multimedia notebook and desktop PC applications.

### **Features**

- 10 Channels (5 stereo DACs and 2 stereo ADCs) with 24-bit resolution

- Supports full-duplex 7.1 audio and simultaneous VoIP

- Microsoft WLP premium logo compliant

- Optimized and flexible power management with pop/click mitigation

- SPDIF

- 48QFP package supports 2 independent S/PDIF Output converters for WLP compliant HDMI/SPDIF support

- 40QFN package supports a single SPDIF Out

- Both packages support SPDIF Input

## HDA signaling

- 48QFP package support for 1.5V and 3.3V with runtime selection

- 40QFN package supports 3.3V only

- 3 adjustable VREF Out pins for microphone bias

- · High performance analog mixer

- 9 stereo analog ports with presence detect capability

- Digital and Analog PC Beep to all outputs

- 3 Integrated headphone amps

- Sample rates up to 192kHz

- Additional Features on 48QFP package

- Two-pin volume up/down control

- · Digital microphone input (mono, stereo, or quad array)

- 4th adjustable VREF Out

- Additional 5 GPIOs

#### Package Options

- 48-pin QFP RoHS package

- 48-pin QFP RoHS package, Industrial Temp

- 40-pin QFN RoHS package

## **Software Support**

- Intuitive IDT HD Sound graphical user interface that allows configurability and preference settings

- 12 band fully parametric equalizer

- Constant, system-level effects tuned to optimize a particular platform can be combined with user-mode "presets" tailored for specific acoustical environments and applications

- System-level effects automatically disabled when external audio connections made

- Dynamics Processing

- · Enables improved voice articulation

- Compressor/limiter allows higher average volume level without resonances or damage to speakers.

- IDT Vista APO wrapper

- Enables multiple APOs to be used with the IDT Driver

- Microphone Beam Forming, Acoustic Echo Cancellation, and Noise Suppression

- Dynamic Stream Switching

- Improved multi-streaming user experience with less support calls

- Broad 3<sup>rd</sup> party branded software including Creative, Dolby, DTS, and SRS

V 1.3 08/11

## **TABLE OF CONTENTS**

| 1. DESCRIPTION                                      | 4   |

|-----------------------------------------------------|-----|

| 1.1. Overview                                       | 4   |

| 1.2. Orderable Part Numbers                         | 4   |

| 1.3. Detailed Description                           |     |

| 2. CHARACTERISTICS                                  | 22  |

| 2.1. Electrical Specifications                      |     |

| 2.2. 92HD73E Analog Performance Characteristics     |     |

| 3. PORT CONFIGURATIONS                              |     |

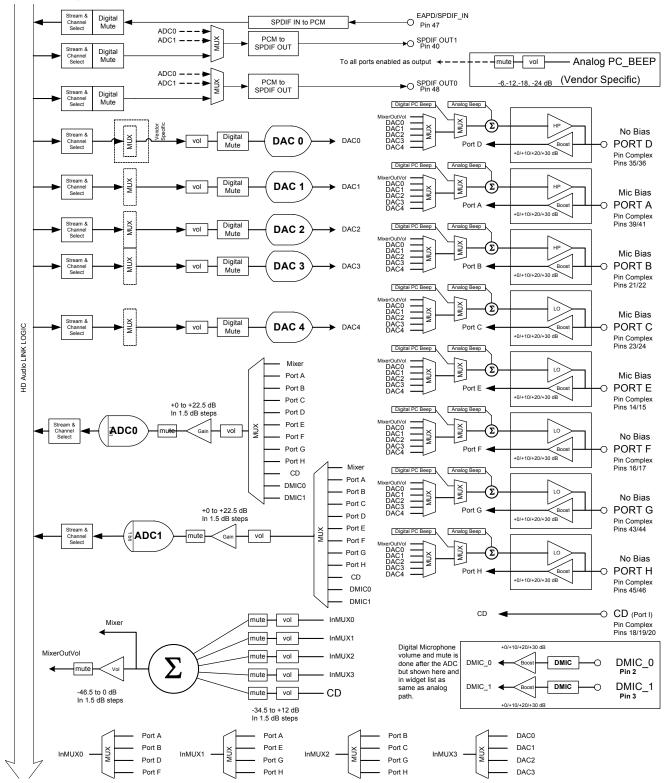

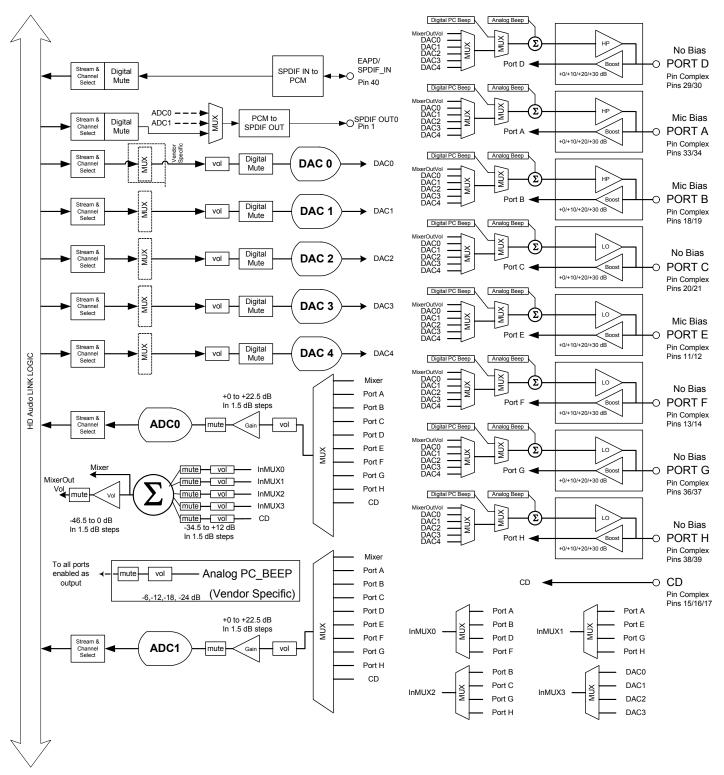

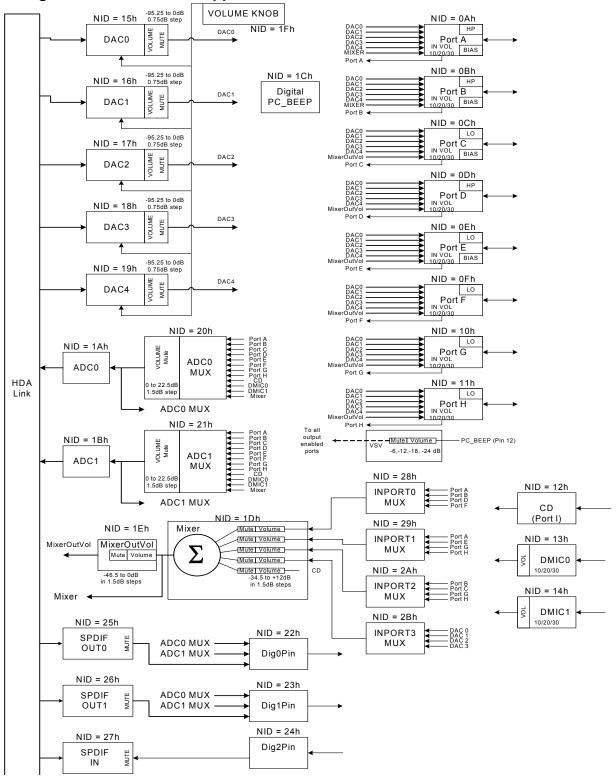

| 4. FUNCTIONAL BLOCK DIAGRAMS                        | 28  |

| 4.1. 48QFP                                          |     |

| 4.2. 40QFN                                          |     |

| 4.3. Widget Information and Supported Command Verbs |     |

| 4.4. Widget List                                    |     |

| 4.5. Pin Configuration Default Register Settings    |     |

| 5. WIDGET INFORMATION                               |     |

| 5.1. Root Node (NID = 00))                          |     |

| 5.2. AFG Node (NID = 01                             |     |

| 5.3. Port A Node (NID = 0A)                         |     |

| 5.4. PortB Node (NID = 0B)                          |     |

| 5.5. Port C Node (NID = 0C)                         |     |

| 5.6. Port D Node (NID = 0D)                         |     |

| 5.7. PortE Node (NID = 0E)                          | 81  |

| 5.8. PortF Node (NID = 0F)                          |     |

| 5.9. PortG Node (NID = 10)                          | 93  |

| 5.10. PortH Node (NID = 11)                         | 101 |

| 5.11. Portl Node (NID = 12)                         | 108 |

| 5.12. DMic0 Node (NID = 13)                         |     |

| 5.13. DMic1 Node (NID = 14)                         | 117 |

| 5.14. DAC0 Node (NID = 15)                          |     |

| 5.15. DAC1 Node (NID = 16)                          |     |

| 5.16. DAC2 Node (NID = 17)                          |     |

| 5.17. DAC3 Node (NID = 18)                          |     |

| 5.18. DAC4 Node (NID = 19)                          |     |

| 5.19. ADC0 Node (NID = 1A)                          |     |

| 5.20. ADC1 Node (NID = 1B)                          |     |

| 5.21. DigBeep Node (NID = 1C)                       |     |

| 5.22. Mixer Node (NID = 1D)                         |     |

| 5.23. MixerOutVol Node (NID = 1E)                   |     |

| 5.24. VolumeKnob Node (NID = 1F)                    |     |

| 5.25. ADC0Mux Node (NID = 20)                       |     |

| 5.26. ADC1Mux Node (NID = 21)                       |     |

| 5.27. Dig0Pin Node (NID = 22)                       |     |

| 5.28. Dig1Pin Node (NID = 23)                       |     |

| 5.29. Dig2Pin Node (NID = 24)                       |     |

| 5.30. SPDIFOut0 Node (NID = 25)                     |     |

| 5.31. SPDIFOut1 Node (NID = 26)                     |     |

| ,                                                   |     |

| 5.33. InPort0Mux Node (NID = 28)                    |     |

| 5.35. InPort2Mux Node (NID = 29)                    |     |

| 5.36. InPort3Mux Node (NID = 2A)                    |     |

| 6. DISCLAIMER                                       |     |

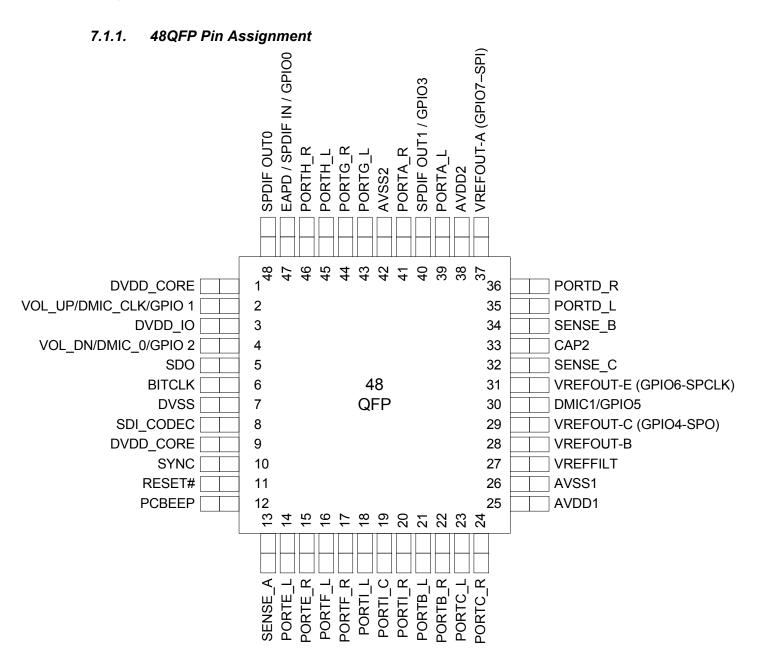

| 7. PINOUTS                                          |     |

|                                                     |     |

| 7.1. 48QFP                                          |     |

| 8. PACKAGE OUTLINE AND PACKAGE DIMENSIONS           |     |

|                                                     |     |

| 8.1. 48QFP Package                                  | ∠34 |

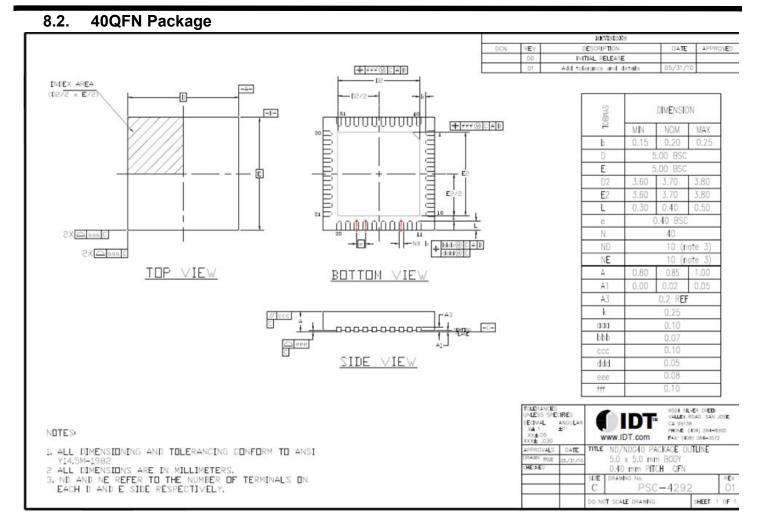

| 8.2. 40QFN Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 235                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

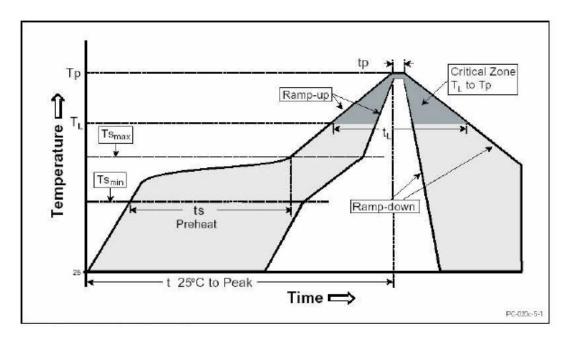

| 8.3. Standard Reflow Profile Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                        |

| 8.4. Pb Free Process - Package Classification Reflow Temperatures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                        |

| 9. DOCUMENT REVISION HISTORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                        |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                        |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                        |

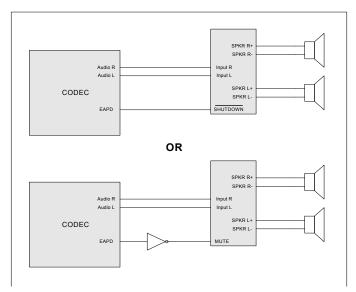

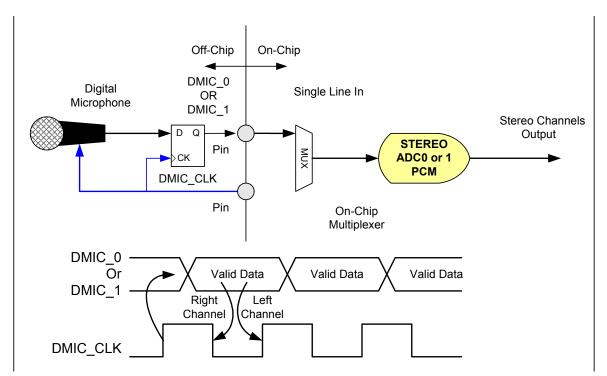

| Figure 1. Multi-channel capture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11                                                                                     |

| Figure 2. Multi-channel timing diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                        |

| Figure 3. EAPD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                        |

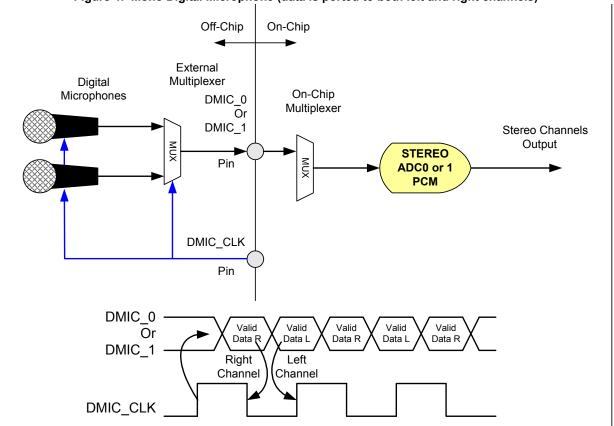

| Figure 4: Mono Digital Microphone (data is ported to both left and right channels)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                        |

| Figure 5: Stereo Digital Microphone Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                        |

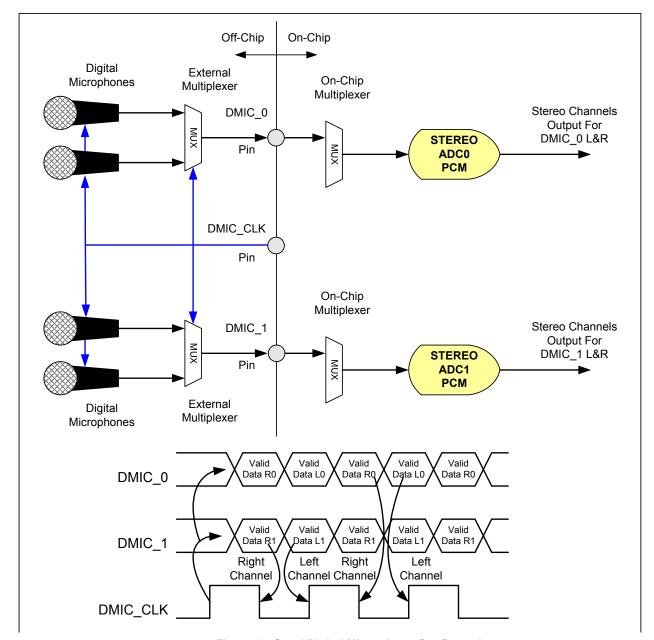

| Figure 6: Quad Digital Microphone Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                        |

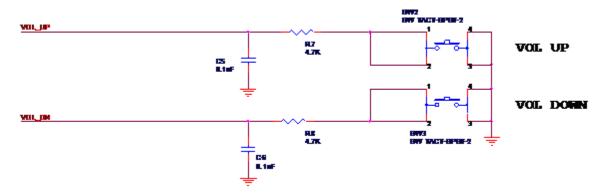

| Figure 7: External Volume Control Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21                                                                                     |

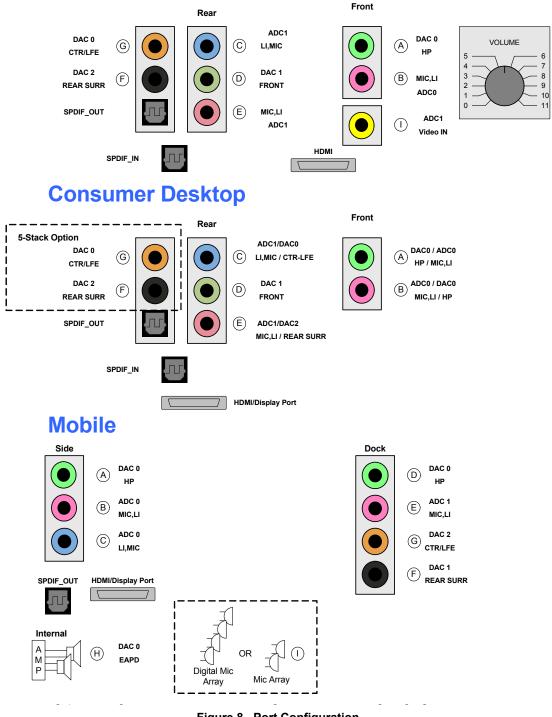

| Figure 8. Port Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27                                                                                     |

| Figure 9. 48QFP Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 28                                                                                     |

| Figure 10. 40QFN Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29                                                                                     |

| Figure 11. Widget Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 30                                                                                     |

| Figure 12. 48QFP Pin Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                        |

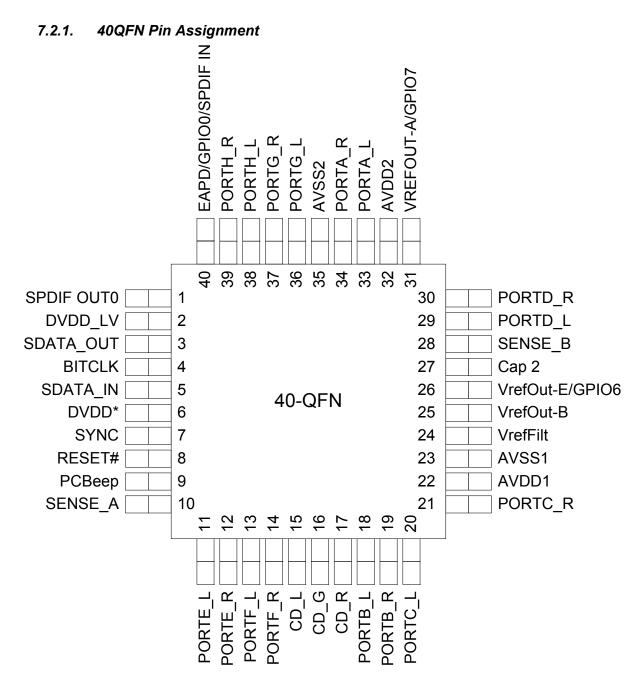

| Figure 13. 40QFN Pin Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                        |

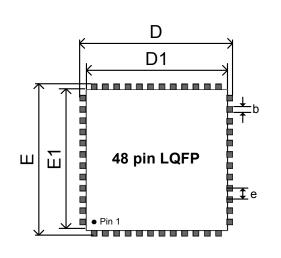

| Figure 14. 48QFP Package Drawing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                        |

| Figure 15, 400EN Package Drawing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 235                                                                                    |

| Figure 15. 40QFN Package Drawing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                        |

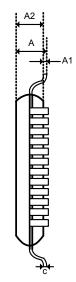

| Figure 16. Solder Reflow Profile                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 236                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 236                                                                                    |

| Figure 16. Solder Reflow Profile  LIST OF TABLES  Table 1. Port Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <u>.</u>                                                                               |

| Figure 16. Solder Reflow Profile  LIST OF TABLES  Table 1. Port Functionality Table 2. Analog I/O Port Behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5<br>6                                                                                 |

| Figure 16. Solder Reflow Profile  LIST OF TABLES  Table 1. Port Functionality Table 2. Analog I/O Port Behavior Table 4. SPDIF OUT 0 (Pin 48) Behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                        |

| Figure 16. Solder Reflow Profile  LIST OF TABLES  Table 1. Port Functionality Table 2. Analog I/O Port Behavior Table 4. SPDIF OUT 0 (Pin 48) Behavior Table 5. SPDIF OUT 1 (Pin 40) Behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                        |

| Figure 16. Solder Reflow Profile  LIST OF TABLES  Table 1. Port Functionality Table 2. Analog I/O Port Behavior Table 4. SPDIF OUT 0 (Pin 48) Behavior Table 5. SPDIF OUT 1 (Pin 40) Behavior Table 6. Input Multiplexers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                        |

| Figure 16. Solder Reflow Profile  LIST OF TABLES  Table 1. Port Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                        |

| Table 1. Port Functionality Table 2. Analog I/O Port Behavior Table 4. SPDIF OUT 0 (Pin 48) Behavior Table 5. SPDIF OUT 1 (Pin 40) Behavior Table 6. Input Multiplexers Table 7. Function state vs. AFG power state Table 10. EAPD Behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                        |

| Figure 16. Solder Reflow Profile  LIST OF TABLES  Table 1. Port Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                        |

| Table 1. Port Functionality Table 2. Analog I/O Port Behavior Table 4. SPDIF OUT 0 (Pin 48) Behavior Table 5. SPDIF OUT 1 (Pin 40) Behavior Table 6. Input Multiplexers Table 7. Function state vs. AFG power state Table 10. EAPD Behavior Table 11. Valid Digital Mic Configurations Table 12. DMIC_CLK and DMIC_0,1 Operation During Power States                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                        |

| Table 1. Port Functionality Table 2. Analog I/O Port Behavior Table 4. SPDIF OUT 0 (Pin 48) Behavior Table 5. SPDIF OUT 1 (Pin 40) Behavior Table 6. Input Multiplexers Table 7. Function state vs. AFG power state Table 10. EAPD Behavior Table 11. Valid Digital Mic Configurations Table 12. DMIC_CLK and DMIC_0,1 Operation During Power States Table 13. GPIO Pin mapping                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                        |

| Table 1. Port Functionality Table 2. Analog I/O Port Behavior Table 4. SPDIF OUT 0 (Pin 48) Behavior Table 5. SPDIF OUT 1 (Pin 40) Behavior Table 6. Input Multiplexers Table 7. Function state vs. AFG power state Table 10. EAPD Behavior Table 11. Valid Digital Mic Configurations Table 12. DMIC_CLK and DMIC_0,1 Operation During Power States Table 13. GPIO Pin mapping Table 14. Electrical Specification: Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                        |

| Table 1. Port Functionality Table 2. Analog I/O Port Behavior Table 4. SPDIF OUT 0 (Pin 48) Behavior Table 5. SPDIF OUT 1 (Pin 40) Behavior Table 6. Input Multiplexers Table 7. Function state vs. AFG power state Table 10. EAPD Behavior Table 11. Valid Digital Mic Configurations Table 12. DMIC_CLK and DMIC_0,1 Operation During Power States Table 13. GPIO Pin mapping Table 14. Electrical Specification: Maximum Ratings Table 15. Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                         |                                                                                        |

| Figure 16. Solder Reflow Profile  LIST OF TABLES  Table 1. Port Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                        |

| Table 1. Port Functionality Table 2. Analog I/O Port Behavior Table 4. SPDIF OUT 0 (Pin 48) Behavior Table 5. SPDIF OUT 1 (Pin 40) Behavior Table 6. Input Multiplexers Table 7. Function state vs. AFG power state Table 10. EAPD Behavior Table 11. Valid Digital Mic Configurations Table 12. DMIC_CLK and DMIC_0,1 Operation During Power States Table 14. Electrical Specification: Maximum Ratings Table 15. Recommended Operating Conditions Table 16. 92HD73E Analog Performance Characteristics Table 17. High Definition Audio Widget                                                                                                                                                                                                                                                                        |                                                                                        |

| Table 1. Port Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 55<br>56<br>57<br>57<br>58<br>59<br>59<br>59<br>59<br>59<br>59<br>59<br>59<br>59<br>59 |

| Table 1. Port Functionality Table 2. Analog I/O Port Behavior Table 4. SPDIF OUT 0 (Pin 48) Behavior Table 5. SPDIF OUT 1 (Pin 40) Behavior Table 6. Input Multiplexers Table 7. Function state vs. AFG power state Table 10. EAPD Behavior Table 11. Valid Digital Mic Configurations Table 12. DMIC_CLK and DMIC_0,1 Operation During Power States Table 13. GPIO Pin mapping Table 14. Electrical Specification: Maximum Ratings Table 15. Recommended Operating Conditions Table 16. 92HD73E Analog Performance Characteristics Table 17. High Definition Audio Widget Table 18. Pin Configuration Default Settings Table 19. Command Format for Verb with 4-bit Identifier                                                                                                                                        |                                                                                        |

| LIST OF TABLES  Table 1. Port Functionality Table 2. Analog I/O Port Behavior Table 4. SPDIF OUT 0 (Pin 48) Behavior Table 5. SPDIF OUT 1 (Pin 40) Behavior Table 6. Input Multiplexers Table 7. Function state vs. AFG power state Table 10. EAPD Behavior Table 11. Valid Digital Mic Configurations Table 12. DMIC_CLK and DMIC_0,1 Operation During Power States Table 13. GPIO Pin mapping Table 14. Electrical Specification: Maximum Ratings Table 15. Recommended Operating Conditions Table 16. 92HD73E Analog Performance Characteristics Table 17. High Definition Audio Widget Table 18. Pin Configuration Default Settings Table 19. Command Format for Verb with 4-bit Identifier Table 20. Command Format for Verb with 12-bit Identifier                                                               |                                                                                        |

| LIST OF TABLES  Table 1. Port Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                        |

| LIST OF TABLES  Table 1. Port Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                        |

| LIST OF TABLES  Table 1. Port Functionality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                        |

| LIST OF TABLES  Table 1. Port Functionality Table 2. Analog I/O Port Behavior Table 4. SPDIF OUT 0 (Pin 48) Behavior Table 5. SPDIF OUT 1 (Pin 40) Behavior Table 6. Input Multiplexers Table 7. Function state vs. AFG power state Table 10. EAPD Behavior Table 11. Valid Digital Mic Configurations Table 12. DMIC_CLK and DMIC_0,1 Operation During Power States Table 13. GPIO Pin mapping Table 14. Electrical Specification: Maximum Ratings Table 15. Recommended Operating Conditions Table 16. 92HD73E Analog Performance Characteristics Table 17. High Definition Audio Widget Table 18. Pin Configuration Default Settings Table 19. Command Format for Verb with 4-bit Identifier Table 20. Command Format for Verb with 12-bit Identifier Table 21. Solicited Response Format Table 23. 48QFP Pin Table |                                                                                        |

#### 1. DESCRIPTION

## 1.1. Overview

The 92HD73E is a high fidelity, 10-channel audio codec compatible with the Intel High Definition (HD) Audio Interface. The 92HD73E codec provides high quality, HD Audio capability to desktop and multi-media notebook.

The 92HD73E is designed to meet or exceed premium logo requirements for Microsoft's Windows Logo Program (WLP) 3.09 and revisions 4 as indicated in WLP 3.09.

The 92HD73E provides stereo 24-bit, full duplex resolution supporting sample rates up to 192kHz by the DAC and ADC. 92HD73E SPDIF outputs support sample rates of 192kHz, 176.4kHz, 96kHz, 88.2kHz, 48kHz, and 44.1kHz. 92HD73E SPDIF input supports sample rates of 96kHz, 88.2kHz, 48kHz, and 44.1kHz. Additional sample rates are supported by the driver software.

The 92HD73E supports a wide range of desktop and consumer 8/10 channel configurations. The 2 independent SPDIF output interfaces provides connectivity to Consumer Electronic equipment like Dolby Digital decoders, powered speakers, mini disk drives or to a home entertainment system. Simultaneous HDMI and SPDIF output is possible.

MIC inputs can be programmed with 0/10/20/30dB boost. For more advanced configurations, the 92HD73E has 8 General Purpose I/O (GPIO) in the 48QFP package.

The port presence detect capabilities allow the codecs to detect when audio devices are connected to the codec. Load impedance sensing helps identify attached peripherals for easy set-up and a better user experience. The fully parametric IDT SoftEQ can be initiated upon headphone jack insertion and removal for protection of notebook speakers.

The 92HD73E operates with a 3.3V digital supply and a 5V analog supply. It can also work with 1.5V and 3.3V HDA signaling; the correct signalling level is selected dynamically based on the power supply voltage on the DVDD-IO pin in the 48QFP package. The 40QFN package allows for 3.3V HDA signalling.

#### 1.2. Orderable Part Numbers

| 92HD73E1X5PRGXB2X*<br>92HD73E1X5PRGXC1X | 48QFP                  |

|-----------------------------------------|------------------------|

| 92HD73E1T5PRGIC1X                       | 48QFP, Industrial Temp |

| 92HD73E2X5NDGXC1X                       | 40QFN                  |

<sup>\*</sup> limited quantities of the B2 available, contact IDT sales.

Add an "8" to the end for tape and reel delivery.

### 1.3. Detailed Description

#### 1.3.1. Port Functionality

Multi-function (Input / output) ports allow for the highest possible flexibility. 8 bi-directional ports (3 headphone capable) support a wide variety of consumer desktop and mobile system use models.

| Port        | Input | Output | Headphone | Mic Bias<br>(Vref pin) | Input<br>boost amp <sup>1</sup> | CD<br>(pseudo differential) |

|-------------|-------|--------|-----------|------------------------|---------------------------------|-----------------------------|

| Α           | Yes   | Yes    | Yes       | Yes                    | Yes                             |                             |

| В           | Yes   | Yes    | Yes       | Yes                    | Yes                             |                             |

| С           | Yes   | Yes    |           | Yes                    | Yes                             |                             |

| D           | Yes   | Yes    | Yes       |                        | Yes                             |                             |

| E           | Yes   | Yes    |           | Yes                    | Yes                             |                             |

| F           | Yes   | Yes    |           |                        | Yes                             |                             |

| G           | Yes   | Yes    |           |                        | Yes                             |                             |

| Н           | Yes   | Yes    |           |                        | Yes                             |                             |

| CD (Port I) | Yes   |        |           |                        |                                 | Yes                         |

| SPDIF_OUT0  |       | Yes    |           |                        |                                 |                             |

| SPDIF_OUT1  |       | Yes    |           |                        |                                 |                             |

| SPDIF_IN    | Yes   |        |           |                        |                                 |                             |

| DMIC0       | Yes   |        |           |                        | Yes                             |                             |

| DMIC1       | Yes   |        |           |                        | Yes                             |                             |

**Table 1. Port Functionality**

Note<sup>1</sup>: 40dB boost requires using the IDT driver. When the 40dB mic boost feature is enabled, additional gain increases greater than 6dB may result in significant audio quality degradation of the microphone audio input. In particular, when the 40dB MIC boost is active, the SNR, THD+N and DC offset will significantly degrade regardless of the input signal level.

#### 1.3.2. Port Characteristics

Universal (Bi-directional) jacks are supported on all ports except the CD input. Ports A, B, and D are designed to drive a set of 32 ohm (nominal) headphones or a 10K (nominal) load with on board shunt resistance as low as 20K ohms (typical - used to maintain coupling CAP bias.) Line Level outputs are intended to drive an external 10K speaker load (nominal) and an on board shunt resistor of 20K-47K (nominal). However, applications may support load impedances of 5K ohms and above. Input ports are 47K (nominal) at the pin.

DAC full scale output and intended full scale input levels are 1V rms. Line output ports and Headphone output ports on 92HD73E may be configured for +3dBV full scale output levels by using a vendor specific verb.

Output ports are always on to prevent pops/clicks associated with charging and discharging output coupling capacitors. This maintains proper bias on output coupling caps even in D3 as long as AVDD is available. Unused ports should be left unconnected. When updating existing designs to use the 92HD73E, ensure that there are no conflicts between the output ports on 92HD73E and existing circuitry.

| AFG Power<br>State | Input Enable | Output Enable | Mute | Port Behavior                                                                             |

|--------------------|--------------|---------------|------|-------------------------------------------------------------------------------------------|

|                    | 1            | 1             | -    | Not allowed. Port becomes input.                                                          |

|                    | 1            | 0             | -    | Active - port enabled as input                                                            |

| D0-D2              | 0            | 1             | 0    | Active - port enabled as output                                                           |

| 50 52              | 0            | 1 1           |      | Mute - port enabled as output but drives silence                                          |

|                    | 0            | 0             | -    | Inactive - Port keeps coupling caps charged (same as mute.)                               |

| D3                 |              | -             | -    | Inactive (lower power) - Port keeps output coupling caps charged but consumes less power. |

Table 2. Analog I/O Port Behavior

#### 1.3.3. Jack Detect

Plugs inserted to a jack on Ports A, B, C, & D are detected using SENSE\_A. Plugs inserted to a jack on Ports E, F, G, and H are detected using SENSE\_B. The following table summarizes the proper resistor tolerances for different analog supply voltages.

SENSE\_C, is different from SENSE\_A and SENSE\_B. Because SENSE\_C only determines the presence of a plug for the CD port (port I), SENSE\_C is a simple digital input pin referenced to the analog supply. An internal pull-up resistor is provided. No external resistors are needed (jack switch shorts to ground when a plug is inserted.) If external components are added, or if the pin is driven by a logic gate, care should be taken to ensure that the pin voltage is above 70% of AVDD when no plug is in the jack and less than 30% AVDD when a plug is inserted.

| AVdd Nominal<br>Voltage (+/- 5%) | Resistor Tolerance<br>SENSE_A<br>(If port D used) | Resistor Tolerance<br>SENSE_A<br>(If port D is not used) | Resistor Tolerance<br>SENSE_B<br>(If port H used) | Resistor Tolerance<br>SENSE_B<br>(If port H is not used) |

|----------------------------------|---------------------------------------------------|----------------------------------------------------------|---------------------------------------------------|----------------------------------------------------------|

| 5V                               | 1%                                                | 1%                                                       | 1%                                                | 1%                                                       |

| 4.75V                            | 1%                                                | 1%                                                       | 1%                                                | 1%                                                       |

| 4V                               | 0.50%                                             | 1%                                                       | 0.50%                                             | 1%                                                       |

| 3.3V                             | 0.10%                                             | 1%                                                       | 0.10%                                             | 1%                                                       |

**Table 3: SENSE Resistor Tolerance**

See reference design for more information on Jack Detect implementation.

#### 1.3.4. SPDIF Output

All SPDIF Outputs can operate at 44.1kHz, 48kHz, 88.2kHz, 96kHz, 176.4KHz, and 192KHz as defined in the Intel High Definition Audio Specification with resolutions up to 24 bits. This insures compatibility with all consumer audio gear and allows for convenient integration into home theater systems and media center PCs.

A second independent SPDIF Output is provided as an option for WLP compliant HDMI and SPDIF outputs, available only of 48QFP package. Its function is identical to the primary SPDIF output.

Note: Peak to peak jitter is currently limited to less than 4.5nS (half of the internal master clock cycle) which does not meet the IEC-60958-3 0.05UI requirement at 192KHz.

The two SPDIF output converters can not be aligned in phase with the DACs. Even when attached to the same stream, the two SPDIF output converters may be misaligned with respect to their frame boundaries.

SPDIF Outputs on pins 48 and 40 are outlined in tables below. Pin 47 behavior table resides in the EAPD section

| AFG Power<br>State | RESET#             | Output Enable | Converter Dig<br>Enable | Stream ID | Pin Behavior                                                                                                                           |

|--------------------|--------------------|---------------|-------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------|

| D0-D3              | Asserted (Low)     | -             | -                       | -         | Hi-Z (internal pull-down enabled) immediately after power on, otherwise the previous state is retained until the rising edge of RESET# |

|                    | De-Asserted (High) | Disabled      | -                       | -         | Hi-Z (internal pull-down enabled)                                                                                                      |

|                    | De-Asserted (High) | Enabled       | Disabled                | -         | Active - Pin drives 0 (internal pull-down NA)                                                                                          |

| D0                 | De-Asserted (High) | Enabled       | Enabled                 | 0         | Active - Pin drives SPDIF-format,<br>but data is zeroes (internal<br>pull-down NA)                                                     |

|                    | De-Asserted (High) | Enabled       | Enabled                 | 1-15      | Active - Pin drives SPDIFOut0 data (internal pull-down NA)                                                                             |

|                    | De-Asserted (High) | Disabled      | -                       | -         | Hi-Z (internal pull-down enabled)                                                                                                      |

| D1-D2              |                    | Enabled       | -                       | -         | Active - Pin drives 0 (internal pull-down NA)                                                                                          |

| D3                 | De-Asserted (High) | -             | -                       | -         | Hi-Z (internal pull-down enabled)                                                                                                      |

Table 4. SPDIF OUT 0 (Pin 48) Behavior

| AFG Power<br>State | RESET#             | GPIO 3<br>Enable | Output<br>Enable | Converter<br>Dig Enable | Stream ID | Pin Behavior                                                                                                                           |

|--------------------|--------------------|------------------|------------------|-------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------|

| D0-D3              | Asserted (Low)     | -                | -                | -                       | -         | Hi-Z (internal pull-down enabled) immediately after power on, otherwise the previous state is retained until the rising edge of RESET# |

| D0-D3              | De-Asserted (High) | Enabled          | -                | -                       | -         | Active - Pin reflects GPIO7<br>configuration (internal pull-up<br>enabled)                                                             |

|                    | De-Asserted (High) | Disabled         | Disabled         | -                       | -         | Hi-Z (internal pull-down enabled)                                                                                                      |

|                    | De-Asserted (High) | Disabled         | Enabled          | Disabled                | -         | Active - Pin drives 0 (internal pull-down enabled)                                                                                     |

| D0                 | De-Asserted (High) | Disabled         | Enabled          | Enabled                 | 0         | Active - Pin drives SPDIF-format,<br>but data is zeroes (internal<br>pull-down enabled)                                                |

|                    | De-Asserted (High) | Disabled         | Enabled          | Enabled                 | 1-15      | Active - Pin drives SPDIFOut1 data (internal pull-down enabled)                                                                        |

Table 5. SPDIF OUT 1 (Pin 40) Behavior

| AFG Power<br>State | RESET#             | GPIO 3<br>Enable | Output<br>Enable | Converter<br>Dig Enable | Stream ID | Pin Behavior                                  |

|--------------------|--------------------|------------------|------------------|-------------------------|-----------|-----------------------------------------------|

|                    | De-Asserted (High) | Disabled         | Disabled         | -                       | -         | Hi-Z (internal pull-down enabled)             |

| D1-D2              | De-Asserted (High) | Disabled         | Enabled          | -                       | -         | Active - Pin drives 0 (internal pull-down NA) |

| D3                 | De-Asserted (High) | Disabled         | -                | -                       | -         | Hi-Z (internal pull-down enabled)             |

Table 5. SPDIF OUT 1 (Pin 40) Behavior

## 1.3.5. SPDIF Input

SPDIF IN can operate at 44.1 KHz, 48 KHz, 88.2 KHz or 96 KHz, and implements internal Jack Sensing.

A sophisticated digital PLL allows automatic rate detection and accurate data recovery. The ability to directly accept consumer SPDIF voltage levels eliminates the need for costly external receiver ICs. Advanced features such as record-slot-select and SPDIF\_IN routing to the DAC allow for simultaneous record and play.

## 1.3.6. Analog Mixer

An analog mixer is available on the 92HD73E. The mixer supports independent gain (-34.5 to +12dB in 1.5dB steps) on each input as well as independent mutes on each input. A master volume follows mixing and provides gain from -46.5dB to 0dB in 1.5dB steps.

The following inputs are available:

- CD

- Analog PC Beep

- Inport0\_Mux

- Inport1\_Mux

- Inport2\_Mux

- Inport3 mux

#### 1.3.7. Input Multiplexers

92HD73E implements 4 port input multiplexers. These multiplexers allow a preselection of one of four possible inputs:

| Inport0_Mux | Inport1_Mux | Inport2_Mux | Inport3_mux |

|-------------|-------------|-------------|-------------|

| Port A      | Port A      | Port B      | DAC 0       |

| Port B      | Port E      | Port C      | DAC 1       |

| Port D      | Port G      | Port G      | DAC 2       |

| Port F      | Port H      | Port H      | DAC 3       |

**Table 6. Input Multiplexers**

## 1.3.8. ADC Multiplexers

92HD73E implements 2 ADC input multiplexers. These multiplexers incorporate the ADC record gain function (0 to +22.5dB gain in 1.5dB steps) as an output amp and allow a preselection of one of 12 possible inputs:

- DMIC 0 (not on 40QFN)

- DMIC 1 (not on 40QFN)

- Mixer output

- CD input

- · Ports A H

#### 1.3.9. Power Management

The HD Audio specification defines power states, power state widgets, and power state verbs. Power management is implemented at several levels. The Audio Function Group (AFG) and all converter widgets support the power state verb F05/705 (as well as the pin widget associated with pin 47.) Converter widgets are active in D0 and inactive in D1-D3.

The following table describes what functionality is active in each power state supported by the AFG.

| Function                  | D0 | D1 <sup>1</sup> | D2  | D3                     | vendor specific           |

|---------------------------|----|-----------------|-----|------------------------|---------------------------|

| SPDIF Outputs             | On | Off             | Off | Off                    | -                         |

| SPDIF Inputs              | On | Off             | Off | Off                    | -                         |

| Digital Microphone inputs | On | Off             | Off | Off                    | -                         |

| DAC                       | On | Off             | Off | Off                    | -                         |

| D2S                       | On | Off             | Off | Off                    | -                         |

| ADC                       | On | Off             | Off | Off                    | -                         |

| ADC Volume Control        | On | Off             | Off | Off                    | -                         |

| Ref ADC                   | On | Off             | Off | Off                    | -                         |

| Analog Clocks             | On | Off             | Off | Off                    | -                         |

| GPIO pins                 | On | On              | On  | On                     | -                         |

| VrefOut Pins              | On | On              | Off | Off                    | -                         |

| Input Boost               | On | On              | Off | Off                    | -                         |

| Analog mixer              | On | On              | Off | Off                    | -                         |

| Mixer Volumes             | On | On              | Off | Off                    |                           |

| Analog PC_Beep            | On | On              | Off | Off                    |                           |

| Digital PC_Beep           | On | On              | On  | On                     | -                         |

| Lo Amp                    | On | On              | On  | Low Drive <sup>2</sup> | Programmable              |

| HP Amps                   | On | On              | On  | Low Drive <sup>2</sup> | Programmable              |

| VAG amp                   | On | On              | On  | Low Drive <sup>3</sup> | Programmable              |

| Port Sense                | On | On              | On  | On <sup>4</sup>        | Programmable              |

| Reference Bias generator  | On | On              | On  | On                     | Programmable <sup>5</sup> |

| Reference Bandgap core    | On | On              | On  | On                     | Programmable <sup>5</sup> |

| HD Audio-Link             | On | On              | On  | On <sup>6</sup>        | -                         |

Table 7. Function state vs. AFG power state

<sup>1.</sup>No DAC or ADC streams are active. Analog mixing and loop thru are supported.

<sup>2.</sup>VAG is kept active when ports are disabled or in D2/D3. Ports may be powered down using vendor specific verbs.

#### Ten Channel HD Audio Codec

- 3.VAG is always ramped up and down gradually, except in the case of a sudden power removal. VAG is active in D2/D3 but in a low power state.

- 4. BITCLK must be active and both AVDD and DVDD must be available for Port Sense to operate.

- 5. Vendor specific bit for Ref Top controls VAG generator, Bandgap Reference, and Reference bias generator. Place part into D3 and power down all ports (using vendor specific verbs) before powering down Ref Top.

- 6. Obviously not active if BITCLK is not running (Controller in D3).

#### 1.3.9.1. AFG D0

The AFG D0 state is the active state for the device. All functions are active if their power state (if they support power management at their node level) has been set to D0.

#### 1.3.9.2. AFG D1

D1 is a lower power mode where all converter widgets are disabled. Analog mixer and port functions are active.

#### 1.3.9.3. AFG D2

The D2 state further reduces power by disabling the mixer and port functions. The port amplifiers and internal references remain active to keep port coupling caps charged and the system ready for a quick resume to either the D1 or D0 state.

#### 1.3.9.4. AFG D3

The D3-default state is available for HD Audio compliance. All converters are shut down. Port amplifiers and references are active but in a low power state to prevent pops. Resume times may be longer than those from D2, but still very fast to meet Intel low power goals.

The traditional use for D3 was as a transitional state before power was removed (D3 cold) before the system entered into standby, hibernate, or shut-down. To conserve power, Intel now promotes using D3 whenever there are no active streams or other activity that requires the part to consume full power. The system remains in S0 during this time. When a stream request or user activity requires the CODEC to become active, the driver will immediately transition the CODEC from D3 to D0. To enable this use model, the CODEC must resume within 10mS and not pop.

The default power state for the Audio Function Group after reset is D3-default

#### 1.3.9.5. AFG D3 and vendor specific verbs

The programmable values, exposed via vendor-specific settings, are under the IDT Device Driver control for further power reduction.

## 1.3.10. Low-voltage HDA Signaling

The 92HD73E is compatible with either 1.5V or 3.3V HDA bus signaling; the voltage selection is done dynamically based on the input voltage of DVDD\_IO on the 48QFP package. The 40QFN allows for 3.3V only.

When in 1.5V mode, the 92HD73E can correctly decode BITCLK, SYNC, RESET# and SDO as they operate at 1.5V; additionally it will drive SDI and SDO at 1.5V. None of the GPIOs are affected, as they always function at their nominal voltage (DVDD or AVDD).

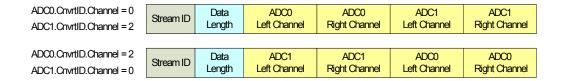

## 1.3.11. Multi-channel capture

The capability to assign multiple ADC "Input Converters" to the same stream is supported to meet the microphone array requirements of Vista and future operating systems. Single converter streams are still supported and is done by assigning unique non zero Stream IDs to each converter. All cap-

10

V 1.3 08/11

ture devices (ADCs 0 and 1) may be used to create a multi-channel input stream. There are no restrictions regarding digital microphones. However, the SPDIF input can not be used with an ADC to create a 4-channel stream. SPDIF\_In only supports stereo capture.

The ADC Converters can be associated with a single stream as long as the sample rate and the bits per sample are the same. The assignment of converter to channel is done using the "CnvtrID" widget and is restricted to even values. The ADC converters will always put out a stereo sample and therefore require 2 channels per converter.

The stream will not be generated unless all entries for the targeted converters are set identically, and the total number of assigned converter channels matches the value in the NmbrChan field. These are listed the "Multi-Converter Stream Critical Entries" table.

An example of a 4 Channel Steam with ADC0 supplying channels 0&1 and ADC1 supplying channels 2&3 is shown below. A 4 Channel stream can be created by assigning the same non-zero stream id "Strm= N" to both ADC0 and ADC1. The sample rates must be set the same and the number of channels must be set to 4 channels "NmbrChan = 0011".

| ADC1 CnvtrID | (NID = 0x08) |        |

|--------------|--------------|--------|

|              | [3:0]        | Ch = 2 |

| ADC0 CnvtrID | (NID = 0x07) |        |

|              | [3:0]        | Ch = 0 |

Table 8: Example channel mapping

Figure 1. Multi-channel capture

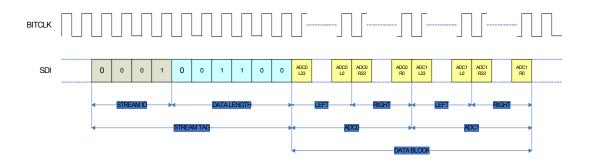

The following figure describes the bus waveform for a 24-bit, 48KHz capture stream with ID set to 1.

Figure 2. Multi-channel timing diagram

| ADC[1:0] Cnvtr   | Bit Number | Sub Field Name | Description                                                                                                                                                                                                                                                                              |

|------------------|------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | [15]       | StrmType       | Stream Type (TYPE): 0: PCM 1: Non-PCM (not supported)                                                                                                                                                                                                                                    |

|                  | [14]       | FrmtSmplRate   | Sample Base Rate<br>0= 48kHz<br>1=44.1KHz                                                                                                                                                                                                                                                |

|                  | [13:11]    | SmplRateMultp  | Sample Base Rate Multiple 000=48kHz/44.1kHz or less 001= x2 010= x3 (not supported) 011= x4 100-111= Reserved                                                                                                                                                                            |

|                  | [10:8]     | SmplRateDiv    | Sample Base Rate Divisor  000= Divide by 1  001= Divide by 2 (not supported)  010= Divide by 3 (not supported)  011= Divide by 4 (not supported)  100= Divide by 5 (not supported)  101= Divide by 6 (not supported)  110= Divide by 7 (not supported)  111= Divide by 8 (not supported) |

|                  | [6:4]      | BitsPerSmpl    | Bits per Sample 000= 8 bits (not supported) 001= 16 bits 010= 20 bits 011= 24 bits 100-111= Reserved                                                                                                                                                                                     |

|                  | [3:0]      | NmbrChan       | Number of Channels Number of channels for this stream in each "sample block" of the "packets" in each "frame" on the link. 0000=1 channel (not supported) 0001 = 2 channels 1111= 16 channels.                                                                                           |

| ADC[1:0] CnvtrlD | Bit Number | Sub Field Name | Description                                                                                                                                                                                                                                                                              |