### **General Description**

The MAX667 low-dropout, positive, linear voltage regulator supplies up to 250mA of output current. With no load, it has a typical quiescent current of 20µA. At 200mA of output current, the input/output voltage differential is typically 150mV. Other features include a lowvoltage detector to indicate power failure, as well as early-warning and low-dropout detectors to indicate an imminent loss of output voltage regulation. A shutdown control disables the output and puts the circuit into a low quiescent-current mode.

The MAX667 employs Dual Mode™ operation. One mode uses internally trimmed feedback resistors to produce +5V. In the other mode, the output may be varied from +1.3V to +16V by connecting two external resistors.

The MAX667 is a pin-compatible upgrade to the MAX666 in most applications where the input voltages are above +3.5V. Choose the MAX667 when high output currents and/or low dropout voltages are desired, as well as for improved performance at higher temperatures.

#### **Applications**

Battery-Powered Devices Pagers and Radio Control Receivers Portable Instruments Solar-Powered Instruments

#### Features

- ♦ 350mV Max Dropout at 200mA

- ◆ 250mA Output Current

- ♦ Normal Mode: 20µA Typ Quiescent Current Shutdown Mode: 0.2µA Typ Quiescent Current

- **♦ Low-Battery Detector**

- ♦ Fixed +5V (Min Component Count) or **Adjustable Output**

- ♦ +3.5V to +16.5V Input

- **♦ Dropout Detector Output**

- ♦ 10µF Output Capacitor

#### **Ordering Information**

| PART           | TEMP RANGE      | PIN-PACKAGE   |

|----------------|-----------------|---------------|

| MAX667CPA      | 0°C to +70°C    | 8 Plastic DIP |

| MAX667CSA      | 0°C to +70°C    | 8 SO          |

| MAX667C/D      | 0°C to +70°C    | Dice*         |

| MAX667EPA      | -40°C to +85°C  | 8 Plastic DIP |

| MAX667ESA      | -40°C to +85°C  | 8 SO          |

| MAX667MJA      | -55°C to +125°C | 8 CERDIP**    |

| MAX667MSA/PR   | -55°C to +125°C | 8 SO†         |

| MAX667MSA/PR-T | -55°C to +125°C | 8 SO†         |

<sup>\*</sup>Contact factory for dice specifications.

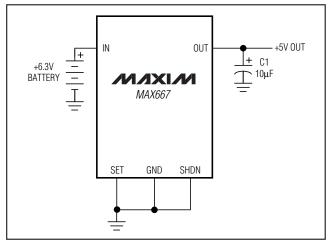

### Typical Operating Circuit

TM Dual Mode is a trademark of Maxim Integrated Products.

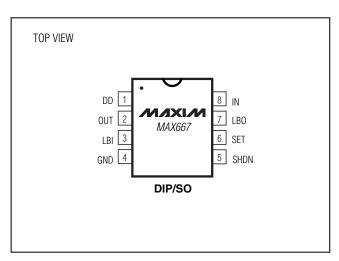

### Pin Configuration

<sup>\*\*</sup>Contact factory for availability and processing to MIL-STD-883. †Contact factory for availability.

#### **ABSOLUTE MAXIMUM RATINGS**

| Input Supply Voltage                | +18V                      | SO (dera    |

|-------------------------------------|---------------------------|-------------|

| Output Short Circuited to Ground    | 1sec                      | CERDIP (    |

| LBO Output Sink Current             | 50mA                      | Operating T |

| LBO Output Voltage                  |                           | MAX6670     |

| SHDN Input Voltage                  | 0.3V to $(V_{IN} + 0.3V)$ | MAX667E     |

| Input Voltages LBI, SET             |                           | MAX667N     |

| Continuous Power Dissipation        |                           | Storage Ter |

| Plastic DIP (derate 9.09mW/°C above | ve +70°C)727mW            | Lead Temp   |

| SO (derate 5.88mW/°C above +70°C)   | 471mW          |

|-------------------------------------|----------------|

| CERDIP (derate 8.00mW/°C above +70  | °C)640mW       |

| Operating Temperature Ranges        |                |

| MAX667C_A                           | 0°C to +70°C   |

| MAX667E_A                           | 40°C to +85°C  |

| MAX667MJA                           | 55°C to +125°C |

| Storage Temperature Range           | 65°C to +160°C |

| Lead Temperature (soldering, 10sec) | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(GND = 0V,  $V_{IN}$  = +9V,  $V_{OUT}$  = +5V, C1 = 10 $\mu$ F, unless otherwise noted.)

| PARAMETER                                  | SYMBOL            | CONDITIONS                                                                                                |                          | MIN                                      | T <sub>A</sub> = +25°<br>TYP | C<br>MAX | T <sub>A</sub> = T <sub>MIN</sub> to | T <sub>MAX</sub><br>MAX | UNITS |

|--------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------|------------------------------|----------|--------------------------------------|-------------------------|-------|

| Input Voltage                              | VIN               |                                                                                                           |                          |                                          |                              |          | 3.5                                  | 16.5                    | V     |

| Output Voltage                             | Vout              | $V_{SET} = 0V$ , $V_{IN} = 6V$ , $I_{OUT} = 10$ mA, $T_A = -40$ °C to $+85$ °C                            |                          |                                          | 5                            |          | 4.8                                  | 5.2                     | V     |

| Cutput voltage                             | V001              | V <sub>SET</sub> = 0V, V <sub>IN</sub> = 6V, I <sub>OUT</sub> = 10mA,<br>T <sub>A</sub> = -55°C to +125°C |                          |                                          | 5                            |          | 4.75                                 | 5.25                    | V     |

| Maximum Output Current                     | I <sub>OUT</sub>  | $V_{IN} = 6V, 4.5V <$                                                                                     | V <sub>OUT</sub> < 5.5V  | 250                                      |                              |          | 250                                  |                         | mA    |

|                                            |                   | V <sub>SHDN</sub> = 2V                                                                                    |                          |                                          | 0.2                          | 1        |                                      | 2                       |       |

| Quiescent Current                          | l <sub>Q</sub>    | W- 0W                                                                                                     | $I_{OUT} = 0\mu A$       |                                          | 20                           | 25       |                                      | 35                      | μΑ    |

| Quiescent Current                          | 'Q                | $V_{SHDN} = 0V,$<br>$V_{SET} = 0V$                                                                        | $I_{OUT} = 100\mu A$     |                                          | 20                           | 30       |                                      | 50                      |       |

|                                            |                   | VSET = SV                                                                                                 | I <sub>OUT</sub> = 200mA |                                          | 5                            | 15       |                                      | 20                      | mA    |

| Dropout Voltage (Note1)                    |                   | $I_{OUT} = 100\mu A$                                                                                      |                          |                                          | 5                            | 60       |                                      | 75                      | mV    |

| Dropout voltage (Note I)                   |                   | I <sub>OUT</sub> = 200mA                                                                                  |                          |                                          | 150                          | 250      |                                      | 350                     | 1110  |

| Load Regulation                            |                   | $I_{OUT} = 10$ mA to 200mA                                                                                |                          |                                          | 50                           | 100      |                                      | 250                     | mV    |

| Line Regulation                            |                   | $V_{IN} = 6V$ to 10V, $I_{OUT} = 10$ mA                                                                   |                          |                                          | 5                            | 10       |                                      | 15                      | mV    |

| SET Reference Voltage                      | V <sub>SET</sub>  |                                                                                                           |                          |                                          | 1.225                        |          | 1.20                                 | 1.25                    | V     |

| SET Input Leakage Current                  | I <sub>SET</sub>  | V <sub>SET</sub> = 1.5V                                                                                   |                          |                                          | 0.01                         | ±10      |                                      | ±1000                   | nA    |

| Output Leakage Current                     | I <sub>OUT</sub>  | V <sub>SHDN</sub> = 2V                                                                                    |                          |                                          | 0.1                          |          |                                      | 1                       | μΑ    |

| Short-Circuit Current                      | lout              | (Note 2)                                                                                                  |                          |                                          |                              | 400      |                                      | 450                     | mA    |

| Low-Battery Detector<br>Reference Voltage  | V <sub>LBI</sub>  |                                                                                                           |                          |                                          | 1.225                        |          | 1.195                                | 1.255                   | V     |

| Low-Battery Detector Input Leakage Current | I <sub>LBI</sub>  | V <sub>LBI</sub> = 1.5V                                                                                   |                          |                                          | 0.01                         | ±10      |                                      | ±1000                   | nA    |

| Low-Battery Detector<br>Output Voltage     | V <sub>LBO</sub>  | V <sub>IN</sub> = 9V, V <sub>LBI</sub> = 2V, I <sub>LBO</sub> = 10mA                                      |                          |                                          |                              | 0.25     |                                      | 0.4                     | V     |

| SHDN Threshold                             | VSHDN             | V <sub>IH</sub>                                                                                           |                          | 1.5                                      |                              | 0.3      | 1.5                                  | 0.3                     | V     |

| SHDN Leakage Current                       | I <sub>SHDN</sub> | V <sub>SHDN</sub> = 0V to V <sub>IN</sub>                                                                 |                          |                                          | 0.01                         | ±10      |                                      | ±1000                   | nA    |

| Dropout Detector Output<br>Voltage         |                   | V <sub>SET</sub> = 0V,<br>V <sub>SHDN</sub> = 0V,                                                         | V <sub>IN</sub> = 7V     |                                          |                              |          |                                      | 0.25                    | V     |

|                                            |                   |                                                                                                           |                          | $R_{DD} = 100k\Omega$ , $I_{OUT} = 10mA$ | V <sub>IN</sub> = 4.5V       |          |                                      |                         | 3.5   |

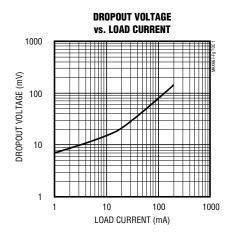

**Note 1:** Dropout Voltage is  $V_{IN}$ - $V_{OUT}$  when  $V_{OUT}$  falls to 0.1V below its value at  $V_{IN} = V_{OUT} + 2V$ .

Note 2: Short-Circuit Current is pulse tested to maintain junction temperature. Short-circuit duration is limited by package dissipation.

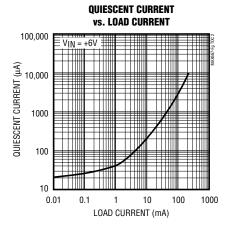

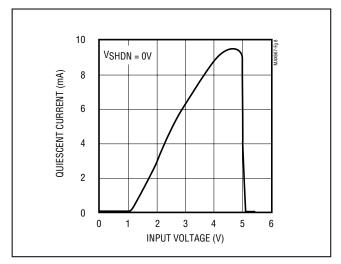

#### **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

#### **Pin Description**

| PIN | NAME | FUNCTION                                                                                                                                                                                           |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | DD   | Dropout Detector Output—the collector of a PNP pass transistor. Normally an open circuit, it sources current as dropout is reached.                                                                |

| 2   | OUT  | Regulated Output Voltage. OUT falls to 0V when SHDN is above 1.5V. SET determines output voltage when SET is above 50mV; otherwise, it is 5V. OUT must be connected to an output filter capacitor. |

| 3   | LBI  | Low-Battery Detector. A CMOS input to an internal 1.255V comparator whose output is the LBO pin.                                                                                                   |

| 4   | GND  | Ground                                                                                                                                                                                             |

| 5   | SHDN | Shutdown Input. Connect to GND for normal operation (output active). Pull above 1.5V to disable OUT, LBO, and DD and to reduce quiescent current to less than 1µA.                                 |

| 6   | SET  | (Output) Voltage Set, CMOS Input.<br>Connect to GND for 5V output. For<br>other voltages, connect external resis-<br>tive divider from OUT.                                                        |

| 7   | LBO  | Low-Battery Output. An open-drain N-channel transistor that sinks current to GND when LBI is less than 1.22V.                                                                                      |

| 8   | IN   | Positive Input Voltage (unregulated)                                                                                                                                                               |

#### \_Detailed Description

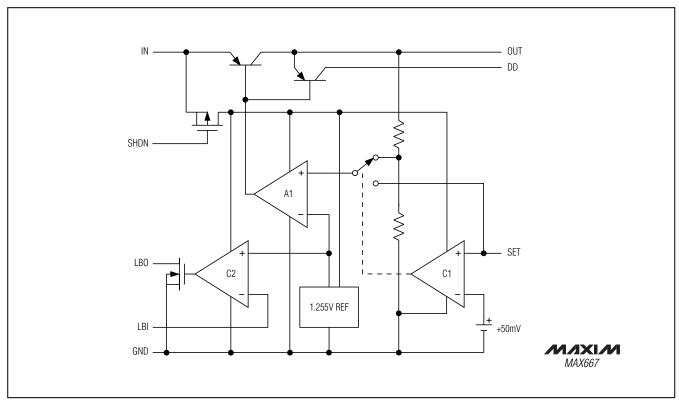

Figure 1 shows a micropower bandgap reference, an error amplifier, a PNP pass transistor, and two comparators as the main elements of the MAX667. One comparator, C1, selects the fixed 5V or adjustable operation with an external voltage divider. The other comparator, C2, is a low-battery detector.

The bandgap reference, which is trimmed to 1.22V, connects internally to one input of the error amplifier, A1. The feedback signal from the regulator output supplies the other input of A1 from either an on-chip voltage divider or two external resistors. When SET is grounded, the internal divider provides the error amplifier feedback signal for a fixed 5V output. When SET is more than 50mV above ground, the error amplifier's input switches directly to SET while an external resistor divider from OUT determines the output voltage.

A second comparator, C2, compares the LBI input to the internal reference voltage. LBO is an open-drain FET connected to GND. The low-battery threshold can also be set with a voltage divider at LBI. In addition, the MAX667 has a shutdown input (SHDN) that disables the load and the device while reducing quiescent current when it is pulled high.

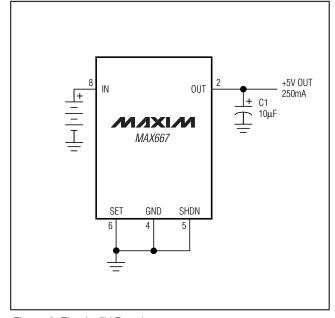

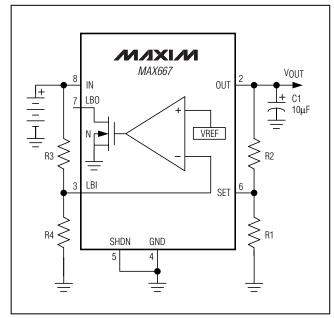

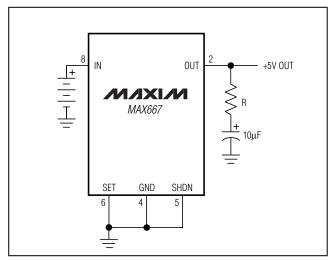

#### +5V Output

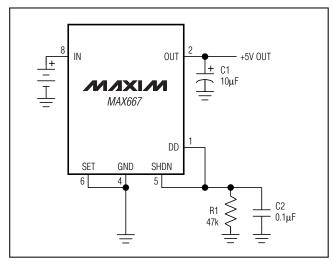

Figure 2 shows the connection for a fixed 5V output. The SET input is grounded, and no external resistors are required. Figure 3 shows adjustable output operation. R1 and R2 set the output voltage. SHDN should be grounded if not used.

Figure 1. MAX667 Block Diagram

Figure 2. Fixed +5V Regulator

Figure 3. Adjustable Output and Low-Battery Detector

#### **Output-Voltage Selection**

If SET is connected to a resistive voltage divider (Figure 3), the output voltage is set by the equation:

$\label{eq:VOUT} V_{OUT} = V_{SET} ~x~(R1~+~R2)~/~R1,$  where  $V_{SET} = 1.22V$

To simplify resistor selection:

$R2 = R1 \times (VOUT / VSET - 1)$

Since the input bias current at SET has a maximum value of 10nA, relatively large values can be used for R1 and R2 with no loss of accuracy.  $1M\Omega$  is a typical value for R1. The VSET tolerance is less than  $\pm 25 \text{mV}$ . This allows the output to be preset without trim pots, using only fixed resistors in most cases. However, when resistor values greater than  $1M\Omega$  are used, pay special attention to printed circuit board leakage that can introduce error at the SET input.

#### Shutdown (Standby) Mode

SHDN puts the device into standby mode to conserve power. When this pin is held low, the IC operates normally. If it is driven above 1.5V, the chip shuts down. Quiescent current of the MAX667 is then reduced to less than  $1\mu$ A, and OUT turns off.

Note that the voltage for SHDN must never be more than 0.3V higher than  $V_{\text{IN}}$ .

#### **Low-Battery Function**

The MAX667 contains circuitry for low-battery detection. If the voltage at LBI falls below the regulator's internal reference (1.22V), LBO, an open-drain output, sinks current to GND. The threshold can be set to any level above the reference voltage by connecting a resistive divider to LBI based on the equation:

$$R3 = R4 \times (V_{BATT} / V_{LBI} - 1)$$

where V<sub>BATT</sub> is the desired threshold of the low-battery detector, and R3 and R4 are the LBI input divider resistors

Since LBI input current is no more than 10nA, high values for R3 and R4 minimize loading. If VOUT is 5V, a 5.5V low-battery threshold can be set using  $8.2M\Omega$  for R3 and  $2.4M\Omega$  for R4. When resistor values greater than  $1M\Omega$  are used, pay special attention to PC board leakage that can introduce error at the LBI input.

When the voltage at LBI is below the internal threshold, LBO sinks current to GND. A pull-up resistor of  $10k\Omega$  or more connected to OUT can be used with this pin when driving CMOS circuits. Any pull-up resistor connected to LBO should  $\boldsymbol{not}$  be returned to a voltage source greater than VOUT. When LBI is above the threshold or the MAX667 is in SHDN mode, the LBO output is off.

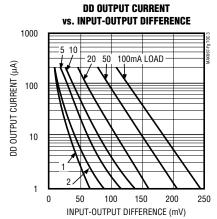

#### **Dropout Detector**

The minimum input-output differential, or dropout voltage, determines the regulator's lowest usable input voltage. In battery-operated systems, this determines the useful end-of-life battery voltage. The MAX667 features very low dropout voltage (see *Electrical Characteristics*). In addition, the MAX667 has a dropout detector output, DD, that changes as the dropout voltage approaches its limit. DD is an open collector of a PNP transistor. The dropout voltage and the dropout detector both depend on the output current and temperature. When the input voltage is more than 300mV above the output voltage, the dropout detector will not conduct. As the differential decreases below 300mV, the DD source current increases abruptly. This current signals a warning that regulation is about to be lost.

Connecting a resistor (typically  $100k\Omega$ ) from DD to ground develops a voltage that can be monitored by analog circuits or changed to digital levels by a comparator. LBI may be used for this purpose.

### Applications Information

#### **Output Capacitor**

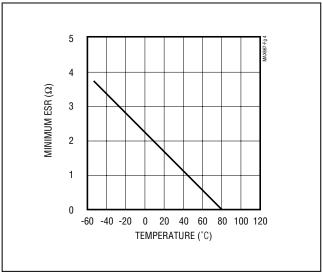

As with all PNP output regulators, an output capacitor (C1, Figure 2) is required to maintain stability. 10µF is recommended. To ensure stability, the output-capacitor ESR must be sufficiently high. Figure 4 shows the minimum required output-capacitor ESR for a given temperature. Alternatively, a resistor may be added in series with the output capacitor (Figure 5); the sum of the out-

Figure 4. Minimum Required Output-Capacitor ESR vs. Temperature

Figure 5. Alternative Stability Scheme Using Resistor R

Figure 6. Quiescent-Current Reduction Below Dropout

put-capacitor ESR and this series resistance should, at minimum, meet the requirements shown in Figure 4.

An upper limit to the output-capacitor ESR is important only if step changes to the load are anticipated. Higher ESR results in higher-amplitude output-voltage transients when the output current is varied. A Sanyo OS-CON capacitor, whose ESR is nearly flat over temperature (and is low to begin with), in series with the appropriate resistor ensures the best load-transient performance. A less expensive alternative is to use a tantalum capacitor in series with the resistor.

Figure 7. Connection for Minimum Quiescent Current Near Dropout

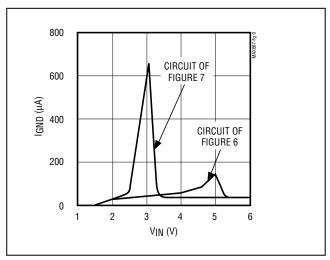

Figure 8. Quiescent Current Below Dropout for Circuit of Figure 2

In most cases, inexpensive aluminum-electrolytic capacitors work well with the MAX667 over their entire temperature range, having sufficient ESR to ensure stability without the need for a series resistor. The ESR of aluminum electrolytics rises, often dramatically, as temperature decreases. For surface-mount applications, certain tantalum capacitors have sufficient ESR; an example is the TAJB106K016 chip capacitor made by AVX (phone: (803) 448-9411, fax: (803) 448-1943).

#### **Battery Drain**

The MAX667 uses a PNP output transistor. When the input voltage falls below the desired output voltage, the

Figure 9. Quiescent Current Below Dropout with Connections of Figures 6 and 7

PNP transistor is turned on fully as regulation is lost. Even with a load current of a few microamperes, the base current will be driven above 5mA. Figure 8 shows how this base current may be significant. Consequently, a mostly discharged battery can be further discharged at end-of-life.

Figure 6 shows how this condition can be modified by connecting DD to SHDN with a 47k $\Omega$  resistor, R1, paralleled with a 0.1µF capacitor to GND. This modification reduces the no-load quiescent current to approximately 160µA when dropout is reached (Figure 9), but increases the dropout voltage by about 0.1V. The output voltage drops to approximately 3V once DD begins to activate SHDN, but it does not fall to zero because SHDN is only partially activated.

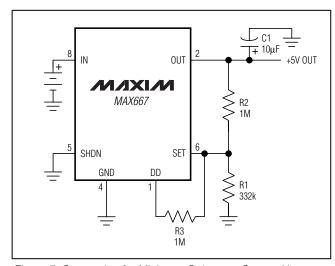

A second alternate connection (Figure 7) further reduces quiescent current near the dropout voltage, compared to the circuit in Figure 6. The output must be set with external resistors (R1, R2), so DD lowers the output voltage as the input voltage falls by sourcing current into SET via R3. Quiescent current remains low for inputs down to 3.5V, and peaks before falling to 0 at low input voltages. Although the current peak is higher than with the connection in Figure 6, this may be more useful because the quiescent current peaks at an input voltage well below the useful range of most batteries (Figure 9). Also, as IN falls below 5V, OUT tracks IN minus the dropout voltage. This connection still allows separate use of the SHDN input.

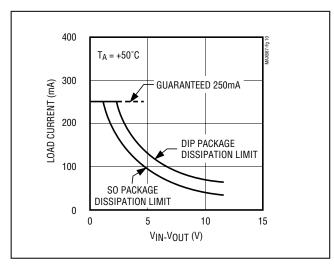

#### **Power Dissipation**

The MAX667 can regulate currents as high as 250mA and withstand input-output differential voltages as high

Figure 10. MAX667 Load Current vs. Input-Output Differential Voltage

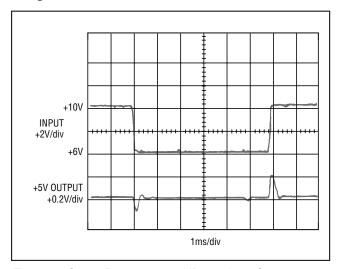

Figure 11. Output Response to +4V/100µs Input Step

as 15.2V, but not simultaneously. The maximum power dissipation is dependent on the package and the temperature (see *Absolute Maximum Ratings*). Figure 10 shows the maximum output current at various input-output differential voltages for the plastic DIP and SO packages. The MAX667 can withstand short-circuit loads up to 1 second.

#### **Operation from AC Sources**

The MAX667 is a micropower CMOS regulator intended principally for battery operation. When operating from AC sources, consider power-supply ripple rejection. The MAX667's error amplifier produces very low gain bandwidth, and the input power-supply rejection ratio

Figure 12. Output Response to 10mA/100mA Load Step with  $10\mu F$  Output Capacitor (1.5 $\Omega$  ESR)

(PSRR) is therefore not specified. Since the output must be connected to a 10µF or larger filter capacitor, the capacitor characteristics dominate the PSRR. Large values of input and output capacitors reduce the ripple.

In addition, both DD and LBI/LBO can trigger on the lowest DC component of the ripple, particularly at high load currents. In the case of the low-battery detector, the ripple can be effectively filtered out by placing a capacitor to ground in parallel with the LBI input pin. The high resistance values that can be used for the voltage divider allow relatively small capacitance values to form an effective lowpass filter at 120Hz. When power is first applied, however, this filter tends to hold LBO low longer than normal.

#### **Transient Considerations**

The low operating current and gain-bandwidth product of the internal reference and amplifier result in limited rejection of fast-step input changes. Negative-going steps, which occur in under 100µs, may turn off the output for several milliseconds. An input filter (nominally 10µF) is recommended if input changes greater than 1V and faster than 100µs (other than turn-on or turn-off) are anticipated. Figure 12 shows the output response to a 10mA/100mA instantaneous load step. The relationship between output-capacitor ESR and load-transient response is explained in the *Output Capacitor* section.

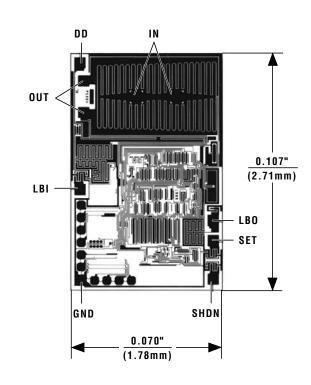

#### Chip Topography

TRANSISTOR COUNT: 65

SUBSTRATE MUST BE LEFT UNCONNECTED

### Package Information

For the latest package outline information and land patterns, go to  $\underline{\text{www.maxim-ic.com/packages}}.$

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 8 PDIP       | P8-T         | <u>21-0043</u> |

| 8 SO         | S8-4         | <u>21-0041</u> |

| 8 CERDIP     | J8-2         | <u>21-0045</u> |

### **Revision History**

| REVISION | REVISION | DESCRIPTION                                  | PAGES   |

|----------|----------|----------------------------------------------|---------|

| NUMBER   | DATE     |                                              | CHANGED |

| 4        | 9/08     | Added information for rugged plastic product | 1, 8    |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.