## **Description**

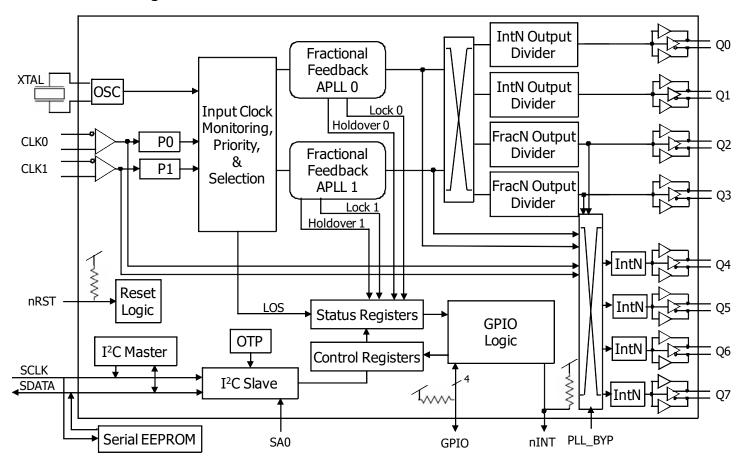

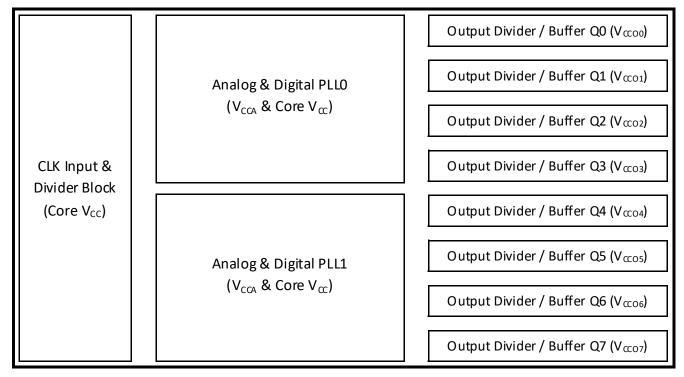

The 8T49N287 has two independent, fractional-feedback PLLs that can be used as jitter attenuators and frequency translators. It is equipped with six integer and two fractional output dividers, allowing the generation of up to 8 different output frequencies, ranging from 8kHz to 1GHz. Four of these frequencies are completely independent of each other and the inputs. The other four are related frequencies. The eight outputs may select among LVPECL, LVDS, HCSL, or LVCMOS output levels.

This makes it ideal to be used in any frequency translation application, including 1G, 10G, 40G and 100G Synchronous Ethernet, OTN, and SONET/SDH, including ITU-T G.709 (2009) FEC rates. The device may also behave as a frequency synthesizer.

The 8T49N287 accepts up to two differential or single-ended input clocks and a crystal input. Each of the two internal PLLs can lock to different input clocks which may be of independent frequencies. Each PLL can use the other input for redundant backup of the primary clock, but in this case, both input clocks must be related in frequency.

The device supports hitless reference switching between input clocks. The device monitors all input clocks for Loss of Signal (LOS), and generates an alarm when an input clock failure is detected. Automatic and manual hitless reference switching options are supported. LOS behavior can be set to support gapped or un-gapped clocks.

The 8T49N287 supports holdover for each PLL. The holdover has an initial accuracy of ±50ppB from the point where the loss of all applicable input reference(s) has been detected. It maintains a historical average operating point for each PLL that may be returned to in holdover at a limited phase slope.

The device places no constraints on input to output frequency conversion, supporting all FEC rates, including the new revision of ITU-T Recommendation G.709 (2009), most with 0ppm conversion error.

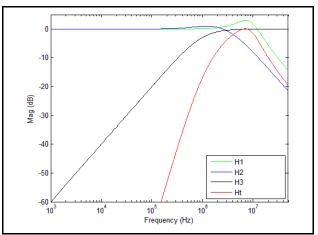

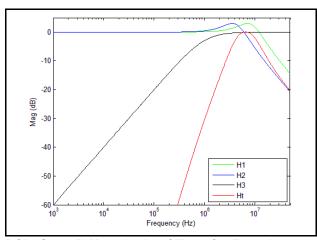

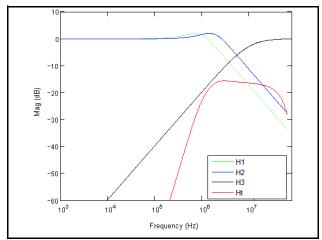

Each PLL has a register-selectable loop bandwidth from 1.4Hz to 360Hz.

Each output supports individual phase delay settings to allow output-output alignment.

The device supports Output Enable inputs and Lock, Holdover and LOS status outputs.

The device is programmable through an  $I^2C$  interface. It also supports  $I^2C$  master capability to allow the register configuration to be read from an external EEPROM.

## **Typical Applications**

- OTN or SONET / SDH equipment Line cards (up to OC-192, and supporting FEC ratios)

- OTN de-mapping (Gapped Clock and DCO mode)

- Gigabit and Terabit IP switches / routers including support of Synchronous Ethernet

- SyncE (G.8262) applications

- Wireless base station baseband

- Data communications

- 100G Ethernet

#### **Features**

- Supports SDH/SONET and Synchronous Ethernet clocks including all FEC rate conversions

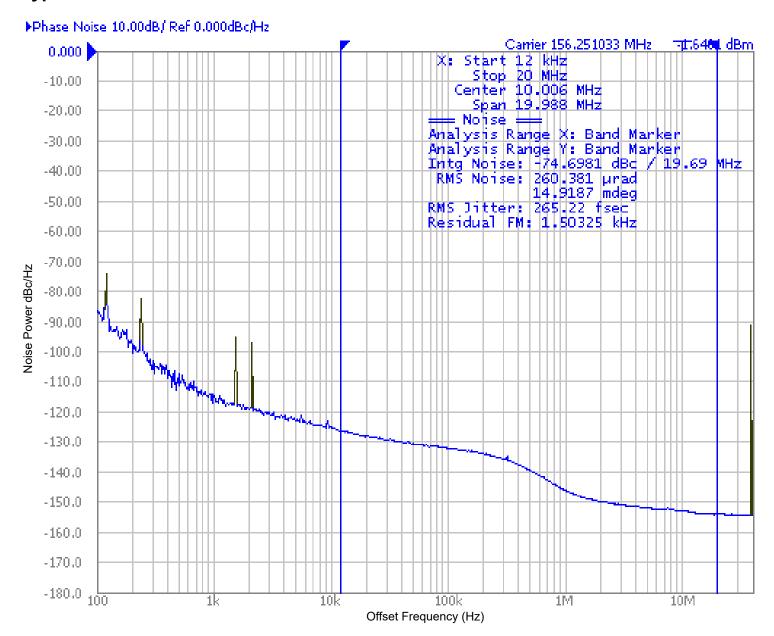

- <0.3ps RMS Typical jitter (including spurs), 12kHz to 20MHz</li>

- Operating modes: locked to input signal, holdover and free-run

- Initial holdover accuracy of ±50ppb

- Accepts up to two LVPECL, LVDS, LVHSTL, HCSL, or LVCMOS input clocks

- Accepts frequencies ranging from 8kHz up to 875MHz

- · Auto and manual input clock selection with hitless switching

- · Clock input monitoring, including support for gapped clocks

- Phase-Slope Limiting and Fully Hitless Switching options to control output phase transients

- Operates from a 10MHz to 40MHz fundamental-mode crystal

- Generates 8 LVPECL / LVDS / HCSL or 16 LVCMOS output clocks

- Output frequencies ranging from 8kHz up to 1.0GHz (diff)

- Output frequencies ranging from 8kHz to 250MHz (LVCMOS)

- Four General Purpose I/O pins with optional support for status & control:

- Four Output Enable control inputs may be mapped to any of the eight outputs

- Lock, Holdover and Loss-of-Signal status outputs

- · Open-drain Interrupt pin

- Nine programmable loop bandwidth settings for each PLL from 1.4Hz to 360Hz

- Optional Fast Lock function

- Programmable output phase delays in steps as small as 16ps

- Register programmable through I<sup>2</sup>C or via external I<sup>2</sup>C EEPROM

- Bypass clock paths for system tests

- Power supply modes

V<sub>CC</sub> / V<sub>CCA</sub> / V<sub>CCO</sub>

3.3V / 3.3V / 3.3V

3.3V / 3.3V / 2.5V

3.3V / 3.3V / 1.8V (LVCMOS)

2.5V / 2.5V / 3.3V

2.5V / 2.5V / 2.5V

2.5V / 2.5V / 1.8V (LVCMOS)

- -40°C to 85°C ambient operating temperature

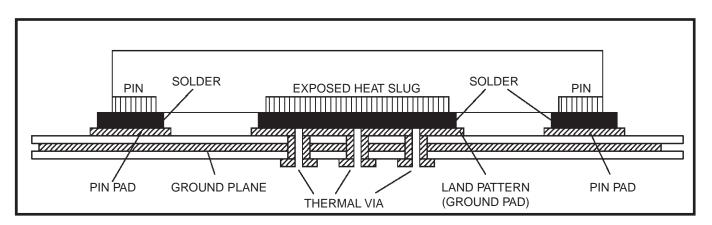

- Package: 56QFN, lead-free (RoHS 6)

## 8T49N287 Block Diagram

Figure 1. 8T49N287 Functional Block Diagram

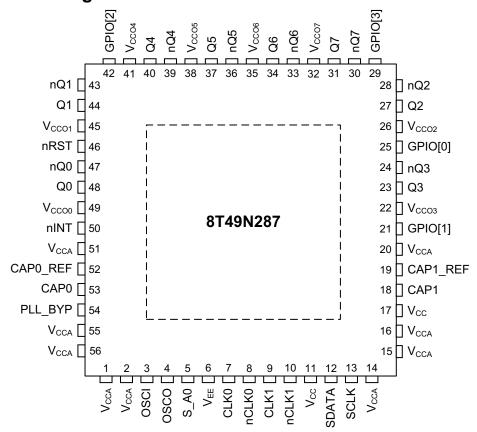

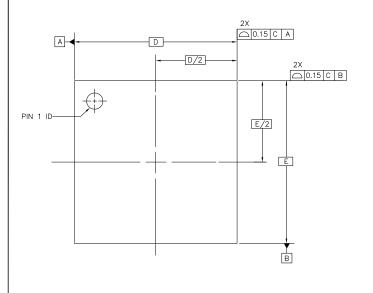

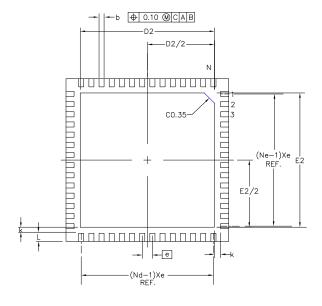

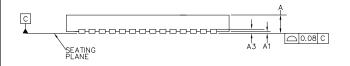

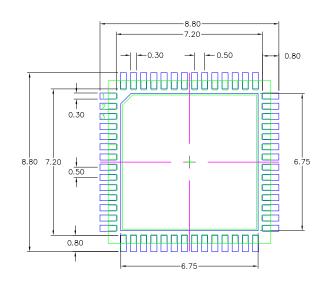

# **Pin Assignment**

56-pin, 8mm x 8mm VFQFN Package

Figure 2. Pinout Drawing

# **Pin Description and Pin Characteristic Tables**

**Table 1. Pin Descriptions**

| Number         | Name              | Ty    | уре                    | Description                                                                                                                                          |

|----------------|-------------------|-------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3              | OSCI              | I     |                        | Crystal Input. Accepts a 10MHz-40MHz reference from a clock oscillator or a 12pF fundamental mode, parallel-resonant crystal.                        |

| 4              | osco              | 0     |                        | Crystal Output. This pin should be connected to a crystal. If an oscillator is connected to OSCI, then this pin must be left unconnected.            |

| 5              | S_A0              | I     | Pulldown               | I <sup>2</sup> C lower address bit A0.                                                                                                               |

| 12             | SDATA             | I/O   | Pullup                 | I <sup>2</sup> C interface bi-directional Data.                                                                                                      |

| 13             | SCLK              | I/O   | Pullup                 | I <sup>2</sup> C interface bi-directional Clock.                                                                                                     |

| 7              | CLK0              | I     | Pulldown               | Non-inverting differential clock input.                                                                                                              |

| 8              | nCLK0             | 1     | Pullup /<br>Pulldown   | Inverting differential clock input. $V_{\rm CC}/2$ when left floating (set by the internal pullup and pulldown resistors.)                           |

| 9              | CLK1              | I     | Pulldown               | Non-inverting differential clock input.                                                                                                              |

| 10             | nCLK1             | 1     | Pullup /<br>Pulldown   | Inverting differential clock input. $V_{\rm CC}/2$ when left floating (set by the internal pullup and pulldown resistors.)                           |

| 48, 47         | Q0, nQ0           | 0     | Universal              | Output Clock 0. Please refer to the Output Drivers section for more details.                                                                         |

| 44, 43         | Q1, nQ1           | 0     | Universal              | Output Clock 1. Please refer to the Output Drivers section for more details.                                                                         |

| 27, 28         | Q2, nQ2           | 0     | Universal              | Output Clock 2. Please refer to the Output Drivers section for more details.                                                                         |

| 23, 24         | Q3, nQ3           | 0     | Universal              | Output Clock 3. Please refer to the Output Drivers section for more details.                                                                         |

| 40, 39         | Q4, nQ4           | 0     | Universal              | Output Clock 4. Please refer to the Output Drivers section for more details.                                                                         |

| 37, 36         | Q5, nQ5           | 0     | Universal              | Output Clock 5. Please refer to the Output Drivers section for more details.                                                                         |

| 34, 33         | Q6, nQ6           | 0     | Universal              | Output Clock 6. Please refer to the Output Drivers section for more details.                                                                         |

| 31, 30         | Q7, nQ7           | 0     | Universal              | Output Clock 7. Please refer to the Output Drivers section for more details.                                                                         |

| 46             | nRST              | I     | Pullup                 | Master Reset input. LVTTL / LVCMOS interface levels: 0 = All registers and state machines are reset to their default values 1 = Device runs normally |

| 50             | nINT              | 0     | Open-drain with pullup | Interrupt output.                                                                                                                                    |

| 29, 42, 21, 25 | GPIO[3:0]         | I/O   | Pullup                 | General-purpose input-outputs. LVTTL / LVCMOS Input levels Open-drain output. Pulled-up with $5.1 k\Omega$ resistor to $V_{CC}$ .                    |

| 54             | PLL_BYP           | I     | Pulldown               | Bypass Selection. Allow input references to bypass both PLLs. LVTTL / LVCMOS interface levels.                                                       |

| 6, ePad        | V <sub>EE</sub>   | Power |                        | Negative supply voltage. All $V_{\text{EE}}$ pins and EPAD must be connected before any positive supply voltage is applied.                          |

| 11             | V <sub>CC</sub>   | Power |                        | Core and digital functions supply voltage.                                                                                                           |

| 17             | V <sub>CC</sub>   | Power |                        | Core and digital functions supply voltage.                                                                                                           |

| 2              | V <sub>CCA</sub>  | Power |                        | Analog functions supply voltage for core analog functions.                                                                                           |

| 14, 15, 16, 20 | V <sub>CCA</sub>  | Power |                        | Analog functions supply voltage for analog functions associated with PLL1.                                                                           |

| 1, 51, 55, 56  | V <sub>CCA</sub>  | Power |                        | Analog functions supply voltage for analog functions associated with PLL0.                                                                           |

| 49             | V <sub>CCO0</sub> | Power |                        | High-speed output supply voltage for output pair Q0, nQ0.                                                                                            |

| 45             | V <sub>CCO1</sub> | Power |                        | High-speed output supply voltage for output pair Q1, nQ1.                                                                                            |

| 26             | V <sub>CCO2</sub> | Power |                        | High-speed output supply voltage for output pair Q2, nQ2.                                                                                            |

|                | - 0002            |       | 1                      |                                                                                                                                                      |

| Number   | Name              | Туре   | Description                                               |

|----------|-------------------|--------|-----------------------------------------------------------|

| 41       | V <sub>CCO4</sub> | Power  | High-speed output supply voltage for output pair Q4, nQ4. |

| 38       | V <sub>CCO5</sub> | Power  | High-speed output supply voltage for output pair Q5, nQ5. |

| 35       | V <sub>CCO6</sub> | Power  | High-speed output supply voltage for output pair Q6, nQ6. |

| 32       | V <sub>CCO7</sub> | Power  | High-speed output supply voltage for output pair Q7, nQ7. |

| 53<br>52 | CAP0,<br>CAP0_REF | Analog | PLL0 External Capacitance.                                |

| 18<br>19 | CAP1,<br>CAP1_REF | Analog | PLL1 External Capacitance.                                |

NOTE: Pullup and Pulldown refer to internal input resistors. See Table 2, Pin Characteristics, for typical values.

Table 2. Pin Characteristics,  $V_{CC} = V_{CCOX} = 3.3V \pm 5\%$  or  $2.5V \pm 5\%$

| Symbol                      | Parameter                  |                                            | Test Conditions                      | Minimum | Typical | Maximum | Units |

|-----------------------------|----------------------------|--------------------------------------------|--------------------------------------|---------|---------|---------|-------|

| C <sub>IN</sub> Input Capac |                            | ince; NOTE 1                               |                                      |         | 3.5     |         | pF    |

| _                           | Internal                   | nRST,<br>SDATA, SCLK                       |                                      |         | 51      |         | kΩ    |

| R <sub>PULLUP</sub>         | Pullup<br>Resistor         | nINT                                       |                                      |         | 50      |         | kΩ    |

|                             | 110010101                  | GPIO[3:0]                                  |                                      |         | 5.1     |         | kΩ    |

| R <sub>PULLDOWN</sub>       | Internal Pulldo            | wn Resistor                                |                                      |         | 51      |         | kΩ    |

|                             |                            | LVCMOS;<br>Q[0:1], Q[4:7]                  | V <sub>CCOX</sub> = 3.465V           |         | 14.5    |         | pF    |

|                             |                            | LVCMOS Q[2:3]                              | V <sub>CCOX</sub> = 3.465V           |         | 18.5    |         | pF    |

|                             |                            | LVCMOS;<br>Q[0:1], Q[4:7]                  | V <sub>CCOX</sub> = 2.625V           |         | 13      |         | pF    |

|                             | Power Dissipation          | LVCMOS; Q[2:3]                             | V <sub>CCOX</sub> = 2.625V           |         | 17.5    |         | pF    |

| C <sub>PD</sub>             | Capacitance<br>(per output | LVCMOS;<br>Q[0:1], Q[4:7]                  | V <sub>CCOX</sub> = 1.89V            |         | 12.5    |         | pF    |

|                             | pair)                      | LVCMOS; Q[2:3]                             | V <sub>CCOX</sub> = 1.89V            |         | 17      |         | pF    |

|                             |                            | LVDS, HCSL or<br>LVPECL;<br>Q[0:1], Q[4:7] | V <sub>CCOx</sub> = 3.465V or 2.625V |         | 2       |         | pF    |

|                             |                            | LVDS, HCSL or<br>LVPECL; Q[2:3]            | V <sub>CCOx</sub> = 3.465V or 2.625V |         | 4.5     |         | pF    |

|                             |                            | GPIO [3:0]                                 | Output HIGH                          |         | 5.1     |         | kΩ    |

| R <sub>OUT</sub>            | Output                     | GF10 [3.0]                                 | Output LOW                           |         | 25      |         | Ω     |

| 001                         | Impedance                  | LVCMOS;<br>Q[0:7], nQ[0:7]                 |                                      |         | 20      |         | Ω     |

NOTE:  $V_{CCOX}$  denotes:  $V_{CCO0}$ ,  $V_{CCO1}$ ,  $V_{CCO2}$ ,  $V_{CCO3}$ ,  $V_{CCO4}$ ,  $V_{CCO5}$ ,  $V_{CCO6}$ ,  $V_{CCO7}$ . NOTE 1: This specification does not apply to OSCI and OSCO pins.

## **Principles of Operation**

The 8T49N287 has two PLLs that can each independently be locked to any of the input clocks and generate a wide range of synchronized output clocks.

It incorporates two completely independent PLLs. These could be used for example in the transmit and receive path of Synchronous Ethernet equipment. Either of the input clocks can be selected as the reference for either PLL. From the output of the two PLLs a wide range of output frequencies can be simultaneously generated.

The 8T49N287 accepts up to two differential input clocks ranging from 8kHz up to 875MHz. It generates up to eight output clocks ranging from 8kHz up to 1.0GHz.

Each PLL path within the 8T49N287 supports three states: Lock, Holdover and Free-run. Lock & holdover status may be monitored on register bits and pins. Each PLL also supports automatic and manual hitless reference switching. In the locked state, the PLL locks to a valid clock input and its output clocks have a frequency accuracy equal to the frequency accuracy of the input clock. In the Holdover state, the PLL will output a clock which is based on the selected holdover behavior. Each of the PLL paths within the 8T49N287 has an initial holdover frequency offset of ±50ppb. In the Free-run state, the PLL outputs a clock with the same frequency accuracy as the external crystal.

Upon power up, each PLL will enter Free-run state, in this state it generates output clocks with the same frequency accuracy as the external crystal. The 8T49N287 continuously monitors each input for activity (signal transitions).

In automatic reference switching, when an input clock has been validated the PLL will transition to the locked state. If the selected input clock fails and there are no other valid input clocks, the PLL will quickly detect that and go into holdover. In the Holdover state, the PLL will output a clock which is based on the selected holdover behavior. If the selected input clock fails and another input clock is available then the 8T49N287 will hitlessly switch to that input clock. The reference switch can be either revertive or non-revertive.

The device supports conversion of any input frequency to four different, independent output frequencies on the Q[0:3]outputs. Additionally, a further four output frequencies may be generated that are integer-related to the four independent frequencies. These additional four frequencies are on the Q[4:7] outputs.

The 8T49N287 has a programmable loop bandwidth from 1.4Hz to 360Hz.

The device monitors all input clocks and generates an alarm when an input clock failure is detected.

The device supports programmable individual output phase adjustments in order to allow control of input to output phase adjustments and output to output phase alignment.

The device is programmable through an I<sup>2</sup>C and may also autonomously read its register settings from an internal One-Time Programmable (OTP) memory or an external serial I<sup>2</sup>C EEPROM.

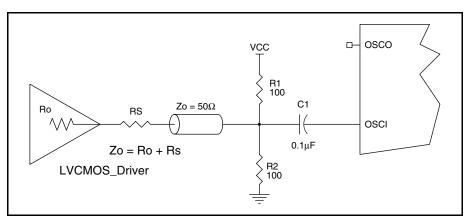

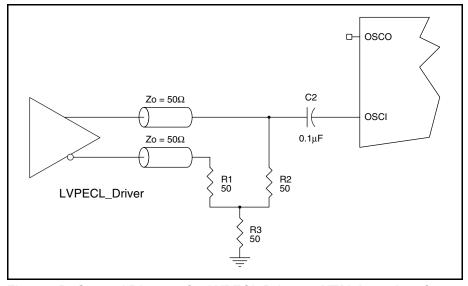

## **Crystal Input**

The crystal input on the 8T49N287 is capable of being driven by a parallel-resonant, fundamental mode crystal with a frequency range of 10MHz - 40MHz.

The oscillator input also supports being driven by a single-ended crystal oscillator or reference clock.

The initial holdover frequency offset is set by the device, but the long term drift depends on the quality of the crystal or oscillator attached to this port.

### **Bypass Path**

For system test purposes, each of PLL0 and PLL1 may be bypassed. When PLL\_BYP is asserted the CLK0 input reference will be presented directly on the Q4 output. The CLK1 input reference will be presented directly on the Q5 output.

Additionally, CLK0 or CLK1 may be used as a clock source for the output dividers of Q[4:7]. This may only be done for input frequencies of 250MHz or less.

### Input Clock Selection

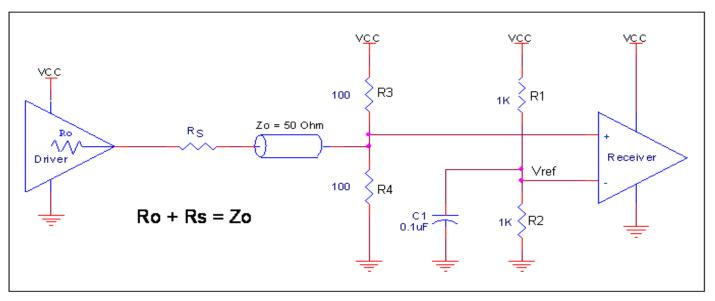

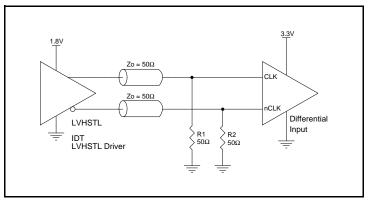

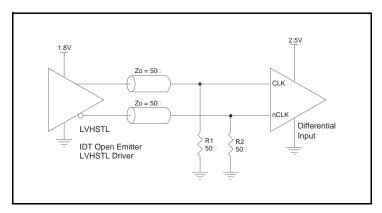

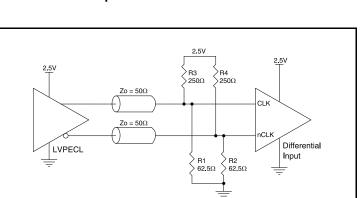

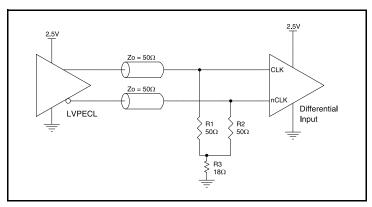

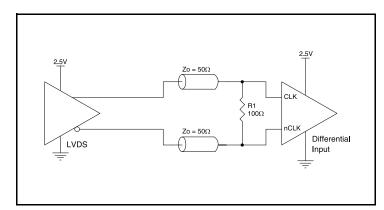

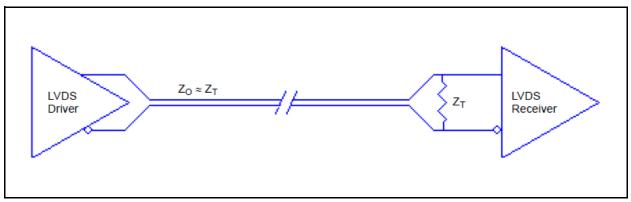

The 8T49N287 accepts up to two input clocks with frequencies ranging from 8kHz up to 875MHz. Each input can accept LVPECL, LVDS, LVHSTL, HCSL or LVCMOS inputs using 1.8V, 2.5V or 3.3V logic levels. To use LVCMOS inputs, refer to the Application Note, *Wiring the Differential Input to Accept Single-Ended Levels* for biasing instructions.

The device has independent input clock selection control for each PLL. In Manual mode, only one of these inputs may be chosen per PLL and if that input fails that PLL will enter holdover.

Manual mode may be operated by directly selecting the desired input reference in the REFSEL register field. It may also operate via pin-selection of the desired input clock by selecting that mode in the REFSEL register field. In that case, GPIOs must be used as Clock Select inputs (CSELn). CSEL0 = 0 will select the CLK0 input and CSEL0 = 1 will select the CLK1 input for PLL0. CSEL1 will perform the same function for PLL1.

In addition, the crystal frequency may be passed directly to the output dividers for Q[4:7] for use as a reference.

Inputs do not support transmission of spread-spectrum clocking sources. Since this family is intended for high-performance applications, it will assume input reference sources to have stabilities of ±100ppm or better, except where gapped clock inputs are used.

If the PLL is working in automatic mode, then each of the input reference sources is assigned a priority of 1-2. At power-up or if the currently selected input reference fails, the PLL will switch to the highest priority input reference that is valid at that time (see Input Clock Monitor section for details).

Automatic mode has two sub-options: revertive or non-revertive. In revertive mode, the PLL will switch to a reference with a higher priority setting whenever one becomes valid. In non-revertive mode the PLL remains with the currently selected source as long as it remains valid.

The clock input selection is based on the input clock priority set by the Clock Input Priority control registers. It is recommended that all input references for a PLL be given different priority settings in the Clock Input Priority control registers for that PLL.

## **Input Clock Monitor**

Each clock input is monitored for Loss of Signal (LOS). If no activity has been detected on the clock input within a user-selectable time period then the clock input is considered to be failed and an internal Loss-of-Signal status flag is set, which may cause an input switchover depending on other settings. The user-selectable time period has sufficient range to allow a gapped clock missing many consecutive edges to be considered a valid input.

User-selection of the clock monitor time-period is based on a counter driven by a monitor clock. The monitor clock is fixed at the frequency of PLL0's VCO divided by 8. With a VCO range of 3GHz - 4GHz, the monitor clock has a frequency range of 375MHz to 500MHz.

The monitor logic for each input reference will count the number of monitor clock edges indicated in the appropriate Monitor Control register. If an edge is received on the input reference being monitored, then the count resets and begins again. If the target edge count is reached before an input reference edge is received, then an internal soft alarm is raised and the count re-starts. During the soft alarm period, the PLL(s) tracking this input will not be adjusted. If an input reference edge is received before the count expires for the second time, then the soft alarm status is cleared and the PLL(s) will resume adjustments. If the count expires again without any input reference edge being received, then a Loss-of-Signal alarm is declared.

It is expected that for normal (non-gapped) clock operation, users will set the monitor clock count for each input reference to be slightly longer than the nominal period of that input reference. A margin of 2-3 monitor clock periods should give a reasonably quick reaction time and yet prevent false alarms.

For gapped clock operation, the user will set the monitor clock count to a few monitor clock periods longer than the longest expected clock gap period. The monitor count registers support 17-bit count values, which will support at least a gap length of two clock periods for any supported input reference frequency, with longer gaps being supported for faster input reference frequencies. Since gapped clocks usually occur on input reference frequencies above 100MHz, gap lengths of thousands of periods can be supported.

Using this configuration for a gapped clock, the PLL will continue to adjust while the normally expected gap is present, but will freeze once the expected gap length has been exceeded and alarm after twice the normal gap length has passed.

Once a LOS on any of the input clocks is detected, the appropriate internal LOS alarm will be asserted and it will remain asserted until that input clock returns and will be validated by the receipt of 8 rising clock edges on that input reference. If another error condition on the same input clock is detected during the validation time then the alarm remains asserted and the validation time starts over.

Each LOS flag may also be reflected on one of the GPIO[3:0] outputs. Changes in status of any reference can also generate an interrupt if not masked.

#### Holdover

8T49N287 supports a small initial holdover frequency offset for each PLL path in non-gapped clock mode. When the input clock monitor is set to support gapped clock operation, this initial holdover frequency offset is indeterminate since the desired behavior with gapped clocks is for the PLL to continue to adjust itself even if clock edges are missing. In gapped clock mode, the PLL will not enter holdover until the input is missing for two LOS monitor periods.

The holdover performance characteristics of a clock are referred as its accuracy and stability, and are characterized in terms of the fractional frequency offset. The 8T49N287 can only control the initial frequency accuracy. Longer-term accuracy and stability are determined by the accuracy and stability of the external oscillator.

When a PLL loses all valid input references, it will enter the holdover state. In non-gapped clock mode, the PLL will initially maintain its most recent frequency offset setting and then transition at a rate dictated by its selected phase-slope limit setting to a frequency offset setting that is based on historical settings.

This behavior is intended to compensate for any frequency drift that may have occurred on the input reference before it was detected to be lost.

The historical holdover value will have three options:

- Return to center of tuning range within the VCO band.

- Instantaneous mode the holdover frequency will use the DPLL current frequency 100msec before it entered holdover. The accuracy is shown in the AC Electrical Characteristics, Table 11A.

- Fast average mode an internal IIR (Infinite Impulse Response) filter is employed to get the frequency offset.

The IIR filter gives a 3 dB attenuation point corresponding to a nominal period of 20 minutes. The accuracy is shown in the AC Electrical Characteristics, *Table 11A*.

When entering holdover, each PLL will set a separate internal HOLD alarm internally. This alarm may be read from internal status register, appear on the appropriate GPIO pin and/or assert the nINT output.

While a PLL is in holdover, its frequency offset is now relative to the crystal input and so the output clocks derived from that PLL will be tracing their accuracy to the local oscillator or crystal. At some point in time, depending on the stability & accuracy of that source, the clock(s) derived from that PLL will have drifted outside of the limits of the holdover state and the system will be considered to be in a free-run state. Since this borderline is defined outside the PLL and dictated by the accuracy and stability of the external local crystal or oscillator, the 8T49N287 cannot know or influence when that transition occurs. As a result, the 8T49N287 will remain in the holdover state internally.

## Input to Output Clock Frequency

The 8T49N287 is designed to accept any frequency in its input range and generate eight different output frequencies that are independent from each other and from the input frequencies. The internal architecture of the device ensures that most such translations will result in the exact output frequency specified. Where exact frequency translation is not possible, the frequency translation error will be minimized. Please contact IDT for configuration software or other assistance in determining if a desired configuration will be supported exactly.

#### **Synthesizer Mode Operation**

The device may also act as a frequency synthesizer with either or both PLL's generating their operating frequency from just the crystal input. By setting the SYN\_MODEn register bit and setting the STATEn[1:0] field to Freerun, no input clock references are required to generate the desired output frequencies.

## Loop Filter and Bandwidth

When operating in Synthesizer Mode as described above, the 8T49N287 has a fixed loop bandwidth of approximately 200kHz. When operating in all other modes, the following information applies:

The 8T49N287 uses no external components to support a range of loop bandwidths: 1.40625Hz, 2.8125Hz, 5.625Hz, 11.25Hz, 22.5Hz, 45Hz, 90Hz, 180Hz or 360Hz. Each PLL shall support separate loop filter settings.

The device supports two different loop bandwidth settings for each PLL: acquisition and locked. These loop bandwidths are selected from the list of options described above. If enabled, the acquisition bandwidth is used while lock is being acquired to allow the PLL to "fast-lock". Once locked the PLL will use the locked bandwidth setting. If the acquisition bandwidth setting is not used, the PLL will use the locked bandwidth setting at all times.

## **Output Dividers and Mapping to PLLs**

The 8T49N287 will support eight output dividers that may be mapped to either PLL. Six of the output dividers will have IntN capability only (see *Table 3*) and the other two will support FracN division.

#### Integer Output Divider Programming (Q[0:1], Q[4:7] only)

Each integer output divider block consists of two divider stages in a series to achieve the desired total output divider ratio. The first stage divider may be set to divide by 4, 5 or 6. The second stage of the divider may be bypassed (i.e. divide-by-1) or programmed to any even divider ratio from 2 to 131,070. The total divide ratios, settings and possible output frequencies are shown in Table 3.

In addition, the first divider stage for the Q[4:7] outputs supports a bypass (i.e. divide-by-1) operation for some clock sources.

Table 3. Q[0:1], Q[4:7] Output Divide Ratios

| 1st-Stage<br>Divide | 2nd-Stage<br>Divide | Total<br>Divide | Minimum<br>F <sub>OUT</sub> MHz | Maximum<br>F <sub>OUT</sub> MHz |

|---------------------|---------------------|-----------------|---------------------------------|---------------------------------|

| 4                   | 1                   | 4               | 750                             | 1000                            |

| 5                   | 1                   | 5               | 600                             | 800                             |

| 6                   | 1                   | 6               | 500                             | 666.7                           |

| 4                   | 2                   | 8               | 375                             | 500                             |

| 5                   | 2                   | 10              | 300                             | 400                             |

| 6                   | 2                   | 12              | 250                             | 333.3                           |

| 4                   | 4                   | 16              | 187.5                           | 250                             |

| 5                   | 4                   | 20              | 150                             | 200                             |

| 6                   | 4                   | 24              | 125                             | 166.7                           |

|                     |                     |                 |                                 |                                 |

| 4                   | 131,070             | 524,280         | 0.0057                          | 0.0076                          |

| 5                   | 131,070             | 655,350         | 0.0046                          | 0.0061                          |

| 6                   | 131,070             | 786,420         | 0.0038                          | 0.0051                          |

NOTE: Above frequency ranges for Q[4:7] apply when driven directly from PLL0 or PLL1.

### Fractional Output Divider Programming (Q[2:3] only)

For the FracN output dividers Q[2:3], the output divide ratio is given by:

Output Divide Ratio = (N.F)x2

$N = Integer Part: 4, 5, ...(2^{18}-1)$

F = Fractional Part:  $[0, 1, 2, ...(2^{28}-1)]/(2^{28})$

For integer operation of these outputs dividers, N=3 is also supported.

## **Output Divider Frequency Sources**

Output dividers associated with the Q[0:3] outputs can take their input frequencies from either PLL0 or PLL1.

Output dividers associated with the Q[4:7] outputs can take their input frequencies from PLL0, PLL1, Q2 or Q3 output dividers, CLK0 or CLK1 input frequencies or the crystal frequency.

## **Output Banks**

Outputs of the 8T49N287 are divided into three banks for purposes of output skew measurement:

- Q0, nQ0, Q1, nQ1

- Q4, nQ4, Q5, nQ5

- Q6, nQ6, Q7, nQ7

## **Output Phase Control on Switchover**

When the 8T49N287 switches between input references, enters or leaves the holdover state for either PLL, there are two options on how the output phase can be controlled in these events: phase-slope limiting or fully hitless switching (sometimes called phase build-out) may be selected. The SWMODEn bit selects which behavior is to be followed for PLLn.

If fully hitless switching is selected, then the output phase will remain unchanged under any of these conditions. Note that fully hitless switching is not supported when external loopback is being used. Fully hitless switching should not be used unless all input references are in the same clock domain. Note that use of this mode may prevent an output frequency and phase from being able to trace its alignment back to a primary reference source.

If phase-slope limiting is selected, then the output phase will adjust from its previous value until it is tracking the new condition at a rate dictated by the SLEWn[1:0] bits. Phase-slope limiting should be used if all input references are not in the same clock domain or users wish to retain traceability to a primary reference source.

### Input-Output Delay Control

When using the 8T49N287 in external loopback or in a situation where input-output delay needs to be known and controlled, it is necessary to examine the exact signal path through the device. Due to the flexibility of the device, there are a large number of potential signal paths from input to output through it that depend on the desired configuration. Each of those potential paths may include or exclude logic blocks from the path and change the absolute value of the delay (Static Phase Offset or SPO) through the device. Considering the range of SPO values to cover all those potential paths would not be useful in achieving the target delays for any specific user configuration. Please contact IDT for the specific SPO value associated with a desired input-output path. Note that events such as switchovers, entering or leaving holdover or re-configuring the signal path can result in one-time changes to the SPO due to that path re-configuration. The AC Electrical Characteristics, (*Table 11A*) indicates the maximum variation in SPO that could be expected for a particular path through the device.

### **Output Phase Alignment**

The device has a programmable output to output phase alignment for each of the eight output dividers. After power-up and the PLLs have achieved lock, the device will be in a state where the outputs are synchronized with a deterministic offset relative to each other. After synchronization, the output alignment will depend on the particular configuration of each output according to the following rules. The step size is defined as the period of the clock to that divider:

- 1) Only outputs derived from the same source will be aligned with each other. 'Source' means the reference selected to drive the output divider as controlled by the CLK\_SELn bit for each output.

- 2) For integer dividers (Q[0:1], Q[4:7]) when both divider stages are active, edges are aligned. This case is used as a baseline to compare the other cases here.

- 3) For integer dividers where the 1st-stage divider is bypassed (only Q[4:7] support this), coarse delay adjustments can't be performed. The output phase will be one step earlier than in Case 2.

- 4) Fractional output dividers (Q2 or Q3) do not guarantee any specific phase on power-up or after a synchronization event.

- 5) Integer dividers using Q2 or Q3 as a source (Q[4:7] support this option) will be aligned to their source divider's output (Q2 or Q3). Note that the output skews described above are not included in any of the phase adjustments described here.

Once the device is in operation, the outputs associated with each PLL may have their phase adjustments re-synced in one of two ways:

- 1) If the PLL becomes unlocked, the coarse phase adjustments will be reset and the fine phase adjustments will be re-loaded once it becomes locked again.

- 2) Toggling of a register bit for either PLL (PLLn\_SYN bits in register 00A8h) may also be used to force a re-sync / re-load for outputs associated with that PLL.

The user may apply adjustments that are proportional to the period of the clock source each output divider is operating from. For example, if the divider associated with Output Q3 is running off PLL0, which has a VCO frequency of 4GHz, then the appropriate period would be 250ps. The output phase may be adjusted in these steps across the full period of the output.

- Coarse Adjustment: all Output Dividers may have their phase adjusted in steps of the source clock period. For example a 4GHz VCO gives a step size of 250ps. The user may request an adjustment of phase of up to 31 steps using a single register write. The phase will be adjusted by lengthening the period of the output by 250ps at a time. This process will be repeated every four output clock periods until the full requested adjustment has been achieved. A busy signal will remain asserted in the phase delay register until the requested adjustment is complete. Then a further adjustment may be setup and triggered by toggling the trigger bit.

- Fine Adjustment: For the Fractional Output Dividers associated with the Q2 and Q3 outputs, the phase of those outputs may be further adjusted with a granularity of 1/16th of the VCO period. For example a 4GHz VCO frequency gives a granularity of 16ps. This is performed by directly writing the required offset (from the nominal rising edge position) in units of 1/16th of the output period into a register. Then the appropriate PLLn\_SYN bit must be toggled to load the new value. Note that toggling this bit will clear all Coarse Delays for all outputs associated with that PLL, so Fine Delays should be set first, before Coarse Delays. The output will then jump directly to that new offset value. For this reason, this adjustment should be made as the input is initially programmed or in High-Impedance.

Each output has the capability of being inverted (180° phase shift).

#### **Jitter and Wander Tolerance**

The 8T49N287 can be used as a line card device and therefore is expected to tolerate the jitter and wander output of a timing card PLL (e.g. 82P33714).

## **Output Drivers**

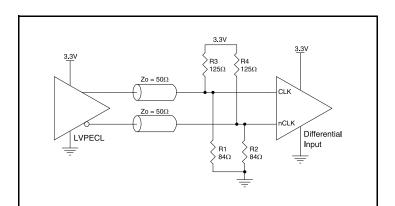

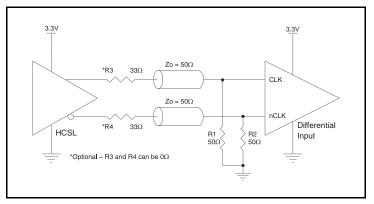

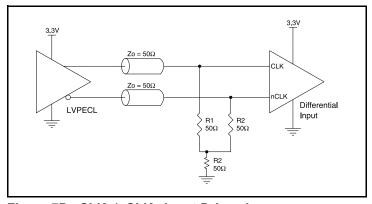

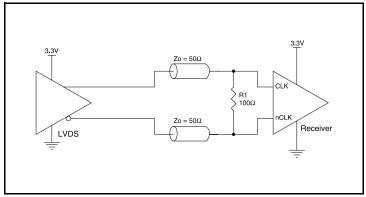

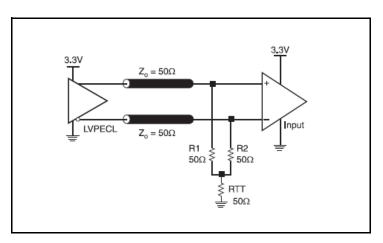

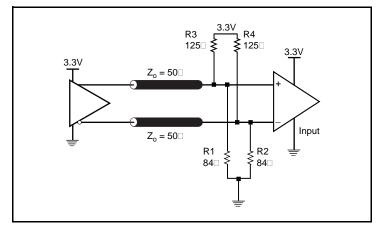

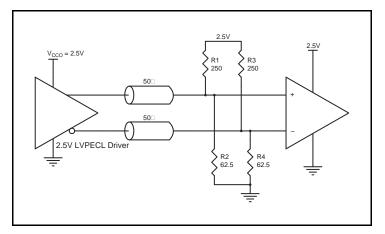

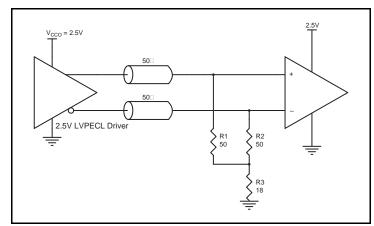

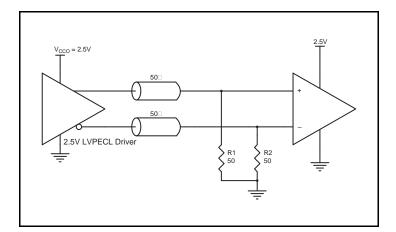

The Q0 to Q7 clock outputs are provided with register-controlled output drivers. By selecting the output drive type in the appropriate register, any of these outputs can support LVCMOS, LVPECL, HCSL or LVDS logic levels.

The operating voltage ranges of each output is determined by its independent output power pin ( $V_{CCO}$ ) and thus each can have different output voltage levels. Output voltage levels of 2.5V or 3.3V are supported for differential operation and LVCMOS operation. In addition, LVCMOS output operation supports 1.8V  $V_{CCO}$ .

Each output may be enabled or disabled by register bits and/or GPIO pins configured as Output Enables. The outputs will be enabled if the register bit and the associated OE pin are both asserted (high). When disabled an output will be in a high impedance state.

#### **LVCMOS Operation**

When a given output is configured to provide LVCMOS levels, then both the Q and nQ outputs will toggle at the selected output frequency. All the previously described configuration and control apply equally to both outputs. Frequency, phase alignment, voltage levels and enable / disable status apply to both the Q and nQ pins. When configured as LVCMOS, the Q and nQ outputs can be selected to be phase-aligned with each other or inverted relative to one another. Phase-aligned outputs will have increased simultaneous switching currents which can negatively affect phase noise performance and power consumption. It is recommended that use of this selection be kept to a minimum.

## **Power-Saving Modes**

To allow the device to consume the least power possible for a given application, the following functions are included under register control:

- PLL1 may be shut down.

- Any unused output, including all output divider and phase adjustment logic, can be individually powered-off.

- · Clock gating on logic that is not being used.

### Status / Control Signals and Interrupts

#### General-Purpose I/Os & Interrupts

The 8T49N287 provides 4 General Purpose Input / Output (GPIO) pins for miscellaneous status & control functions. Each GPIO may be configured as an input or an output. Each GPIO may be directly controlled from register bits or be used as a predefined function as shown in *Table 4*. Note that the default state prior to configuration being loaded from internal OTP or external EEPROM will be to set each GPIO to function as an Output Enable.

**Table 4. GPIO Configuration**

|             |                               | Configure        | d as Inpu       | Configured as Output |                |         |                    |

|-------------|-------------------------------|------------------|-----------------|----------------------|----------------|---------|--------------------|

|             | Fix                           | ed Function      | on              |                      | Fixed Function |         |                    |

| GPIO<br>Pin | Output<br>Enable<br>(default) | Output<br>Enable | Clock<br>Select | General<br>Purpose   |                |         | General<br>Purpose |

| 3           | OE[3]                         | OE[7]            | CSEL1           | GPI[3]               | -              | -       | GPO[3]             |

| 2           | OE[2]                         | OE[6]            | CSEL0           | GPI[2]               | LOS[0]         | LOS[1]  | GPO[2]             |

| 1           | OE[1]                         | OE[5]            | -               | GPI[1]               | HOLD[0]        | HOLD[1] | GPO[1]             |

| 0           | OE[0]                         | OE[4]            | -               | GPI[0]               | LOL[0]         | LOL[1]  | GPO[0]             |

If used in the Fixed Function mode of operation, the GPIO bits will reflect the real-time status of their respective status bits as shown in *Table 4*. Note that the LOL signal represents the lock status of the PLL. It does not account for the process of synchronization of the output dividers associated with that PLL. The output dividers programmed to operate from that PLL will automatically go through a re-synchronization process when the PLL locks or re-locks, or if the user triggers a re-sync manually via register bit PLLn\_SYN. This synchronization process may result in a period of instability on the affected outputs for a duration of up to 350ns after the re-lock (LOL de-asserts) or the PLLn\_SYN bit is de-asserted.

## **Interrupt Functionality**

Interrupt functionality includes an interrupt status flag for each of PLL Loss-of-Lock Status (LOL[1:0]), PLL Holdover Status (HOLD[1:0]) and Input Reference Status (LOS[1:0]) that is set whenever there is an alarm on any of those signals. The Status Flag will remain set until the alarm has been cleared and a '1' has been written to the Status Flag's register location or if a reset occurs. Each Status Flag will also have an Interrupt Enable bit that will determine if that Status Flag is allowed to cause the Interrupt Status to be affected (enabled) or not (disabled). All Interrupt Enable bits will be in the disabled state after reset. The Device Interrupt Status flag and nINT output pin are asserted if any of the enabled Interrupt Status flags are set.

## **Device Hardware Configuration**

The 8T49N287 supports an internal One-Time Programmable (OTP) memory that can be pre-programmed at the factory with 1 complete device configuration. If the device is set to read a configuration from an external, serial EEPROM, then the values read will overwrite the OTP-defined values.

This configuration can be over-written using the serial interface once reset is complete. Any configuration written via the programming interface needs to be re-written after any power cycle or reset. Please contact IDT if a specific factory-programmed configuration is desired.

## **Device Start-up and Reset Behavior**

The 8T49N287 has an internal power-up reset (POR) circuit and a Master Reset input pin nRST. If either is asserted, the device will be in the Reset State.

For highly programmable devices, it is common practice to reset the device immediately after the initial power-on sequence. IDT recommends connecting the nRST input pin to a programmable logic source for optimal functionality. It is recommended that a minimum pulse width of 10ns be used to drive the nRST input pin.

While in the reset state (nRST input asserted or POR active), the device will operate as follows:

- All registers will return to & be held in their default states as indicated in the applicable register description.

- · All internal state machines will be in their reset conditions.

- · The serial interface will not respond to read or write cycles.

- The GPIO signals will be configured as General-Purpose inputs.

- · All clock outputs will be disabled.

- All interrupt status and Interrupt Enable bits will be cleared, negating the nINT signal.

Upon the later of the internal POR circuit expiring or the nRST input negating, the device will exit reset and begin self-configuration.

The device will load an initial block of its internal registers using the configuration stored in the internal One-Time Programmable (OTP) memory. Once this step is complete, the 8T49N287 will check the register settings to see if it should load the remainder of its configuration from an external I<sup>2</sup>C EEPROM at a defined address or continue loading from OTP. See the section on I<sup>2</sup>C Boot Initialization for details on how this is performed.

Once the full configuration has been loaded, the device will respond to accesses on the serial port and will attempt to lock both PLLs to the selected sources and begin operation. Once the PLLs are locked, all the outputs derived from a given PLL will be synchronized and output phase adjustments can then be applied if desired.

## **Serial Control Port Description**

#### **Serial Control Port Configuration Description**

The device has a serial control port capable of responding as a slave in an  $I^2C$  compatible configuration, to allow access any of the internal registers for device programming or examination of internal status. All registers are configured to have default values. See the specifics for each register for details.

The device has the additional capability of becoming a master on the  $I^2C$  bus only for the purpose of reading its initial register configurations from a serial EEPROM on the  $I^2C$  bus. Writing of the configuration to the serial EEPROM must be performed by another device on the same  $I^2C$  bus or pre-programmed into the device prior to assembly.

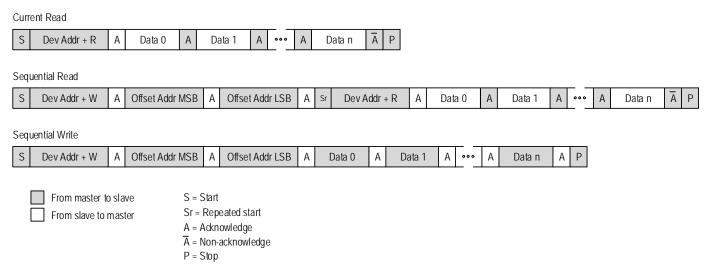

## I<sup>2</sup>C Mode Operation

The  $I^2C$  interface is designed to fully support v2.1 of the  $I^2C$  Specification for Normal and Fast mode operation. The device acts as a slave device on the  $I^2C$  bus at 100kHz or 400kHz using the address defined in the Status Interface Control register (0006h), as modified by the S\_A0 input pin setting. The interface accepts byte-oriented block write and block read operations. Two address bytes specify the register address of the byte position of the first register to write or read. Data bytes (registers) are accessed in sequential order from the lowest to the highest byte (most significant bit first). Read and write block transfers can be stopped after any complete byte transfer. During a write operation, data will not be moved into the registers until the STOP bit is received, at which point, all data received in the block write will be written simultaneously.

For full electrical I $^2$ C compliance, it is recommended to use external pull-up resistors for SDATA and SCLK. The internal pull-up resistors have a size of 51k $\Omega$  typical.

Figure 3. I<sup>2</sup>C Slave Read and Write Cycle Sequencing

#### I<sup>2</sup>C Master Mode

When operating in  $I^2C$  mode, the 8T49N287 has the capability to become a bus master on the  $I^2C$  bus for the purposes of reading its configuration from an external  $I^2C$  EEPROM. Only a block read cycle will be supported.

As an  $\rm I^2C$  bus master, the 8T49N287 will support the following functions:

- · 7-bit addressing mode

- · Base address register for EEPROM

- Validation of the read block via CCITT-8 CRC check against value stored in last byte (E0h) of EEPROM

- Support for 100kHz and 400kHz operation with speed negotiation. If bit d0 is set at Byte address 05h in the EEPROM, this will shift from 100kHz operation to 400kHz operation.

- · Support for 1 or 2-byte addressing mode

- · Master arbitration with programmable number of retries

- Fixed-period cycle response timer to prevent permanently hanging the I<sup>2</sup>C bus.

- Read will abort with an alarm (BOOTFAIL) if any of the following conditions occur: Slave NACK, Arbitration Fail, Collision during Address Phase, CRC failure, Slave Response time-out

- The 8T49N287 will not support the following functions:

- I<sup>2</sup>C General Call

- · Slave clock stretching

- I<sup>2</sup>C Start Byte protocol

- · EEPROM Chaining

- · CBUS compatibility

- · Responding to its own slave address when acting as a master

- Writing to external I<sup>2</sup>C devices including the external EEPROM used for booting

Sequential Read (1-Byte Offset Address) Dev Addr + W Offset Addr Dev Addr + R Data 0 Data 1 Data n Sequential Read (2-Byte Offset Address) Offset Addr LSB Dev Addr + W Offset Addr MSB Dev Addr + R Α Ā Data 0 Data 1 Data n From master to slave S = Start Sr = Repeated start From slave to master A = Acknowledge  $\overline{A}$  = Non-acknowledge P = Stop

Figure 4. I<sup>2</sup>C Master Read Cycle Sequencing

### I<sup>2</sup>C Boot-up Initialization Mode

If enabled (via the BOOT\_EEP bit in the Startup register), once the nRST input has been de-asserted (high) and its internal power-up reset sequence has completed, the device will contend for ownership of the I²C bus to read its initial register settings from a memory location on the I²C bus. The address of that memory location is kept in non-volatile memory in the Startup register. During the boot-up process, the device will not respond to serial control port accesses. Once the initialization process is complete, the contents of any of the device's registers can be altered. It is the responsibility of the user to make any desired adjustments in initial values directly in the serial bus memory.

If a NACK is received to any of the read cycles performed by the device during the initialization process, or if the CRC does not match the one stored in address E0h of the EEPROM the process will be aborted and any uninitialized registers will remain with their default values. The BOOTFAIL bit (021Eh) in the Global Interrupt Status register will also be set in this event.

If the BOOTFAIL bit is set, then both LOL[n] indicators will be set.

Contents of the EEPROM should be as shown in Table 5.

**Table 5. External Serial EEPROM Contents**

| EEPROM Offset |                   |                                                |          |                           | Contents     |    |    |                                                  |  |  |

|---------------|-------------------|------------------------------------------------|----------|---------------------------|--------------|----|----|--------------------------------------------------|--|--|

| (Hex)         | D7                | D6                                             | D5       | D4                        | D3           | D2 | D1 | D0                                               |  |  |

| 00            | 1                 | 1                                              | 1        | 1                         | 1            | 1  | 1  | 1                                                |  |  |

| 01            | 1                 | 1                                              | 1        | 1                         | 1            | 1  | 1  | 1                                                |  |  |

| 02            | 1                 | 1                                              | 1        | 1                         | 1            | 1  | 1  | 1                                                |  |  |

| 03            | 1                 | 1                                              | 1        | 1                         | 1            | 1  | 1  | 1                                                |  |  |

| 04            | 1                 | 1                                              | 1        | 1                         | 1            | 1  | 1  | 1                                                |  |  |

| 05            | 1                 | 1                                              | 1        | 1                         | 1            | 1  | 1  | Serial EEPROM Speed Select 0 = 100kHz 1 = 400kHz |  |  |

| 06            | 1                 |                                                | 8T49N287 | Device I <sup>2</sup> C A | ddress [6:2] |    | 0  | 1                                                |  |  |

| 07            | 0                 | 0                                              | 0        | 0                         | 0            | 0  | 0  | 0                                                |  |  |

| 08 - DF       |                   | Desired contents of Device Registers 08h - DFh |          |                           |              |    |    |                                                  |  |  |

| E0            | Serial EEPROM CRC |                                                |          |                           |              |    |    |                                                  |  |  |

| E1 - FF       |                   |                                                |          |                           | Unused       |    |    |                                                  |  |  |

# **Register Descriptions**

## **Table 6A.Register Blocks**

| Register Ranges Offset (Hex) | Register Block Description                |

|------------------------------|-------------------------------------------|

| 0000 - 0001                  | Startup Control Registers                 |

| 0002 - 0005                  | Device ID Control Registers               |

| 0006 - 0007                  | Serial Interface Control Registers        |

| 0008 - 003A                  | Digital PLL0 Control Registers            |

| 003B - 006D                  | Digital PLL1 Control Registers            |

| 006E - 0076                  | GPIO Control Registers                    |

| 0077 - 00AB                  | Output Clock Control Registers            |

| 00AC - 00AF                  | Analog PLL0 Control Registers             |

| 00B0 - 00B3                  | Analog PLL1 Control Registers             |

| 00B4 - 00B8                  | Power-Down Control Registers              |

| 00B9 - 00C6                  | Input Monitor Control Registers           |

| 00C7                         | Interrupt Enable Register                 |

| 00C8 - 00CB                  | Digital Phase Detector Control Registers  |

| 00CC - 01FF                  | Reserved <sup>1</sup>                     |

| 0200 - 0203                  | Interrupt Status Registers                |

| 0204                         | Output Phase Adjustment Status Register   |

| 0205 - 020E                  | Digital PLL0 Status Registers             |

| 020F - 0218                  | Digital PLL1 Status Registers             |

| 0219                         | General-Purpose Input Status Register     |

| 021A - 021F                  | Global Interrupt and Boot Status Register |

| 0220 - 03FF                  | Reserved <sup>1</sup>                     |

NOTE 1: Reserved. Always write 0 to this bit location. Read values are not defined.

Table 6B. Startup Control Register Bit Field Locations and Descriptions

| Startup Control Register Block Field Locations |                                                                                                       |  |              |  |             |      |           |           |  |  |  |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|--------------|--|-------------|------|-----------|-----------|--|--|--|

| Address (Hex)                                  | Address (Hex)         D7         D6         D5         D4         D3         D2         D1         D0 |  |              |  |             |      |           |           |  |  |  |

| 0000                                           |                                                                                                       |  | EEP_RTY[4:0] |  |             | Rsvd | nBOOT_OTP | nBOOT_EEP |  |  |  |

| 0001                                           | EEP_A15                                                                                               |  |              |  | EEP_ADDR[6: | 0]   |           |           |  |  |  |

|                | Startup Control Register Block Field Descriptions |               |                                                                                                                                                                                          |  |  |  |  |  |  |

|----------------|---------------------------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Bit Field Name | Field Type                                        | Default Value | Description                                                                                                                                                                              |  |  |  |  |  |  |

| EEP_RTY[4:0]   | R/W                                               | 00001b        | Select number of times arbitration for the I <sup>2</sup> C bus to read the serial EEPROM will be retried before being aborted. Note that this number does not include the original try. |  |  |  |  |  |  |

| nBOOT_OTP      | R/W                                               | NOTE 1        | Internal One-Time Programmable (OTP) memory usage on power-up:  0 = Load power-up configuration from OTP  1 = Only load 1st eight bytes from OTP                                         |  |  |  |  |  |  |

| nBOOT_EEP      | R/W                                               | NOTE 1        | External EEPROM usage on power-up:  0 = Load power-up configuration from external serial EEPROM (overwrites OTP values)  1 = Don't use external EEPROM                                   |  |  |  |  |  |  |

| EEP_A15        | R/W                                               | NOTE 1        | Serial EEPROM supports 15-bit addressing mode (multiple pages).                                                                                                                          |  |  |  |  |  |  |

| EEP_ADDR[6:0]  | R/W                                               | NOTE 1        | I <sup>2</sup> C base address for serial EEPROM.                                                                                                                                         |  |  |  |  |  |  |

| Rsvd           | R/W                                               | -             | Reserved. Always write 0 to this bit location. Read values are not defined.                                                                                                              |  |  |  |  |  |  |

NOTE 1: These values are specific to the device configuration and can be customized when ordering. Refer to the *FemtoClock NG Universal Frequency Translator Ordering Product Information guide* for more details.

Table 6C. Device ID Control Register Bit Field Locations and Descriptions

|               | Device ID Control Register Block Field Locations |                              |    |       |         |    |    |    |  |  |  |

|---------------|--------------------------------------------------|------------------------------|----|-------|---------|----|----|----|--|--|--|

| Address (Hex) | D7                                               | D6                           | D5 | D4    | D3      | D2 | D1 | D0 |  |  |  |

| 0002          |                                                  | REV_ID[3:0] DEV_ID[15:12]    |    |       |         |    |    |    |  |  |  |

| 0003          |                                                  |                              |    | DEV_I | D[11:4] |    |    |    |  |  |  |

| 0004          |                                                  | DEV_ID[3:0] DASH_CODE [10:7] |    |       |         |    |    |    |  |  |  |

| 0005          |                                                  | DASH_CODE [6:0]              |    |       |         |    |    |    |  |  |  |

|                                                     | Device ID Control Register Block Field Descriptions |        |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|-----------------------------------------------------|-----------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Bit Field Name Field Type Default Value Description |                                                     |        |                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| REV_ID[3:0]                                         | R/W                                                 | 0000b  | Device revision.                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| DEV_ID[15:0]                                        | R/W                                                 | 605h   | Device ID code.                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| DASH CODE<br>[10:0]                                 | R/W                                                 | NOTE 1 | Device Dash Code: Decimal value assigned by IDT to identify the configuration loaded at the factory. May be over-written by users at any time. Refer to FemtoClock NG Universal Frequency Translator Ordering Product Information guide to identify major configuration parameters associated with this Dash Code value. |  |  |  |  |  |  |

NOTE 1: These values are specific to the device configuration and can be customized when ordering. Refer to the *FemtoClock NG Universal Frequency Translator Ordering Product Information guide* or custom datasheet addendum for more details.

## Table 6D. Serial Interface Control Register Bit Field Locations and Descriptions

|               | Serial Interface Control Block Field Locations                                                        |                                            |  |      |  |  |   |   |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------|--|------|--|--|---|---|--|--|--|

| Address (Hex) | Address (Hex)         D7         D6         D5         D4         D3         D2         D1         D0 |                                            |  |      |  |  |   |   |  |  |  |

| 0006          | Rsvd                                                                                                  | Rsvd         UFTADD[6:2]         UFTADD[1] |  |      |  |  |   |   |  |  |  |

| 0007          |                                                                                                       |                                            |  | Rsvd |  |  | · | 1 |  |  |  |

|                | Serial Interface Control Register Block Field Descriptions |               |                                                                                                                                                 |  |  |  |  |  |

|----------------|------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit Field Name | Field Type                                                 | Default Value | Description                                                                                                                                     |  |  |  |  |  |

| UFTADD[6:2]    | R/W                                                        | NOTE 1        | Configurable portion of I <sup>2</sup> C Base Address (bits 6:2) for this device.                                                               |  |  |  |  |  |

| UFTADD[1]      | R/O                                                        | 0b            | I <sup>2</sup> C Base Address bit 1. This bit is fixed at 0.                                                                                    |  |  |  |  |  |

| UFTADD[0]      | R/O                                                        | 0b            | I <sup>2</sup> C base address bit 0. This address bit reflects the status of the S_A0 external input pin. See <i>Table 1</i> , Pin Description. |  |  |  |  |  |

| Rsvd           | R/W                                                        | -             | Reserved. Always write 0 to this bit location. Read values are not defined.                                                                     |  |  |  |  |  |

NOTE 1: These values are specific to the device configuration and can be customized when ordering. Generic dash codes -900 through -908, -998 and-999 are available and programmed with the default I<sup>2</sup>C address of 1111100b. Please refer to the FemtoClock NG Universal Frequency Translator Ordering Product Information guide for more details.

Table 6E. Digital PLL0 Input Control Register Bit Field Locations and Descriptions

|               | Digital PLL0 Input Control Register Block Field Locations |            |           |           |             |              |       |         |  |

|---------------|-----------------------------------------------------------|------------|-----------|-----------|-------------|--------------|-------|---------|--|

| Address (Hex) | D7                                                        | D6         | D5        | D4        | D3          | D2           | D1    | D0      |  |

| 8000          |                                                           | REFSEL0[2: | 0]        |           | FBSEL0[1:0] |              | RVRT0 | SWMODE0 |  |

| 0009          |                                                           | 11         | 1         | 10        | PRI0_       | _1[1:0]      | PRI0  | _0[1:0] |  |

| 000A          | 1                                                         | 1          | REFDIS0_1 | REFDIS0_0 | Rsvd        | Rsvd         | STAT  | E0[1:0] |  |

| 000B          |                                                           | Rsvd       |           |           |             | PRE0_0[20:16 | ]     |         |  |

| 000C          |                                                           |            |           | PRE0_     | 0[15:8]     |              |       |         |  |

| 000D          |                                                           |            |           | PRE0_     | _0[7:0]     |              |       |         |  |

| 000E          |                                                           | Rsvd       |           |           |             | PRE0_1[20:16 | ]     |         |  |

| 000F          |                                                           |            |           | PRE0_     | 1[15:8]     |              |       |         |  |

| 0010          |                                                           |            |           | PRE0_     | _1[7:0]     |              |       |         |  |

| 0011          |                                                           | Rsvd       |           |           |             | Rsvd         |       |         |  |

| 0012          |                                                           | Rsvd       |           |           |             |              |       |         |  |

| 0013          |                                                           | Rsvd       |           |           |             |              |       |         |  |

| 0014          | Rsvd                                                      |            |           |           |             |              |       |         |  |

| 0015          | Rsvd                                                      |            |           |           |             |              |       |         |  |

| 0016          |                                                           |            |           | Rs        | vd          |              |       |         |  |

|                | Digital PLL0 Input Control Register Block Field Descriptions |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|----------------|--------------------------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit Field Name | Field<br>Type                                                | Default Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| REFSEL0[2:0]   | R/W                                                          | 000Ь          | Input reference selection for Digital PLL0:  000 = Automatic selection  001 = Manual selection by GPIO inputs  010 through 011 = Reserved  100 = Force selection of Input Reference 0  101 = Force selection of Input Reference 1  110 = Do not use  111 = Do not use                                                                                                                                                                                                                                                      |  |  |  |  |

| FBSEL0[2:0]    | R/W                                                          | 000b          | Feedback mode selection for Digital PLL0: 000 through 011 = internal feedback divider 100 = external feedback from Input Reference 0 101 = external feedback from Input Reference 1 110 = do not use 111 = do not use                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| RVRT0          | R/W                                                          | 1b            | Automatic switching mode for Digital PLL0:  0 = non-revertive switching  1 = revertive switching                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| SWMODE0        | R/W                                                          | 1b            | Controls how Digital PLL0 adjusts output phase when switching between input references: 0 = Absorb any phase differences between old and new input references at the PLL output. Recommended for use when both input references are in the same clock domain.  1 = Limit the maximum rate of phase change at the PLL output when adjusting to a new input reference's phase/frequency using phase-slope limiting as set in the SLEWn bits. Recommended for use when the input references are not in the same clock domain. |  |  |  |  |

| PRI0_0[1:0]    | R/W                                                          | 00b           | Switchover priority for Input Reference 0 when used by Digital PLL0:  00 = 1st priority  01 = 2nd priority  10 = do not use  11 = do not use                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |