#### Integrated valve driver

Datasheet - production data

#### **Features**

- Excitation switch  $S_1 = 60 \text{ m}\Omega$

- Recirculation switch S<sub>2</sub> = 60 mΩ

- CMOS compatible inputs

- Load current up to 14 A

- · Integrated clamp structure

- Switch S<sub>1</sub> clamp voltage = 45 V (minimum)

- Current sense amplifier with internal sense resistor

- S<sub>1</sub> switch PWM operation above 10 KHz

- I<sup>2</sup>C standard interface for mode control and enhanced diagnostic

- Diagnostic output:

- Open drain fault detection

- Flag of clamp activation at the end of injection cycle

- · Input for voltage monitoring and feedback

- Thermal shutdown and warning

- Overcurrent shutdown and diagnostic

- Undervoltage and overvoltage detection

- Open-load detection

#### **Description**

The L99SD01-E is a device intended for driving inductive loads.

The inputs are CMOS-compatible. The diagnostic outputs CLAMP\_FLAG and FAULT provide an indication of demagnetization mode and fault conditions, respectively.

The integrated standard serial interface (I<sup>2</sup>C) allows to digitally set peak and hold current values and other injection parameters. It also provides detailed diagnostic information. The device should work with pre-programmed peak and hold current values when values are not set by external micro. All injection parameters can be changed during operating conditions and taken into account at the first injection rising edge after the end of communication. Diagnostic information is available in case of overcurrent, overtemperature, overvoltage and open-load.

Table 1. Device summary

| Package     | Order codes |               |  |  |

|-------------|-------------|---------------|--|--|

| rackage     | Tube        | Tape and reel |  |  |

| PowerSSO-36 | L99SD01-E   | L99SD01TR-E   |  |  |

Contents L99SD01-E

# **Contents**

| 1 | Bloc               | ck diagram and pin description               | 6  |

|---|--------------------|----------------------------------------------|----|

| 2 | Injed              | ction cycle description                      | 9  |

|   | 2.1                | Phase 1                                      | 10 |

|   | 2.2                | Phase 2                                      | 10 |

|   | 2.3                | Phase 3                                      | 10 |

|   | 2.4                | Phase 4                                      | 10 |

|   | 2.5                | Phase 5                                      |    |

| 3 | Diag               | gnostic                                      | 14 |

| 4 | Ι <sup>2</sup> C μ | protocol description                         | 17 |

|   | 4.1                | SDA and SCL signals                          | 17 |

|   | 4.2                | Data validity                                | 17 |

|   | 4.3                | START and STOP conditions                    | 18 |

|   | 4.4                | Byte format                                  | 18 |

|   | 4.5                | Acknowledge (ACK) and Not Acknowledge (NACK) | 19 |

|   | 4.6                | Device addressing                            | 19 |

|   | 4.7                | Write operation                              | 20 |

|   | 4.8                | Read operation                               | 21 |

|   | 4.9                | Registers Addresses and Fault register       | 22 |

| 5 | Regi               | ister description                            | 24 |

|   | 5.1                | Register A                                   | 24 |

|   | 5.2                | Register B                                   | 24 |

|   | 5.3                | Register C                                   | 24 |

|   | 5.4                | Register D                                   | 25 |

|   | 5.5                | Register E                                   | 25 |

|   | 5.6                | Register F                                   | 26 |

|   | 5.7                | Register G                                   | 26 |

|   | 5.8                | Register H                                   | 26 |

|   | 5.9                | Fault register                               | 27 |

L99SD01-E Contents

| 6  | Elect | rical specification             | 28 |

|----|-------|---------------------------------|----|

|    | 6.1   | Absolute maximum rating         | 28 |

|    | 6.2   | Thermal data                    | 29 |

|    | 6.3   | Electrical characteristics      | 29 |

| 7  | ОТР   | (One Time Programmable Memory)  | 38 |

| 8  | Appli | cation schematic                | 39 |

| 9  | Pack  | age and PCB thermal data        | 40 |

|    | 9.1   | PowerSSO-36 thermal data        | 40 |

| 10 | Pack  | age and packing Information     | 43 |

|    | 10.1  | ECOPACK® packages               | 43 |

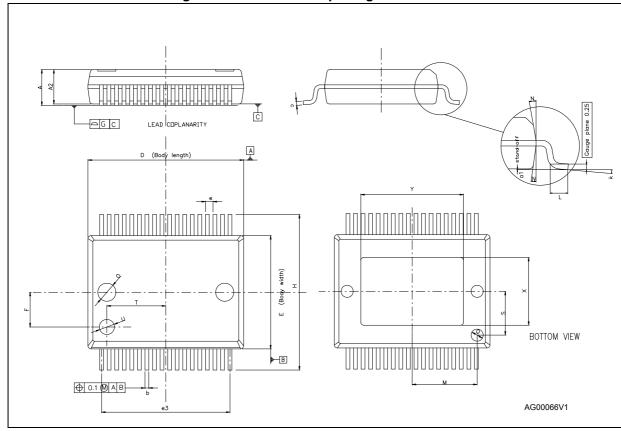

|    | 10.2  | PowerSSO-36 package information | 43 |

| 11 | Revis | sion history                    | 45 |

List of tables L99SD01-E

# List of tables

| l able 1. | Device summary                                                     | 1    |

|-----------|--------------------------------------------------------------------|------|

| Table 2.  | Pin description                                                    | 7    |

| Table 3.  | Diagnostic fault                                                   | . 14 |

| Table 4.  | Registers addresses                                                | . 22 |

| Table 5.  | Absolute maximum rating                                            | . 28 |

| Table 6.  | Thermal data                                                       |      |

| Table 7.  | V <sub>BATT</sub> supply                                           |      |

| Table 8.  | Power switches $S_1 - S_2$                                         | . 29 |

| Table 9.  | S <sub>1</sub> switching (excitation path)                         | . 30 |

| Table 10. | Switching (recirculating path)                                     | . 30 |

| Table 11. | V <sub>DDL</sub> undervoltage detection                            | . 30 |

| Table 12. | Enable                                                             |      |

| Table 13. | Input: SYNC_INJ                                                    | . 31 |

| Table 14. | Input: PWM                                                         |      |

| Table 15. | Inputs: E0, E1, E2                                                 |      |

| Table 16. | IN_SIGNAL VOLTAGE MONITOR, CHECK_SIGNAL                            |      |

| Table 17. | Differential current sense amplifier                               |      |

| Table 18. | Current sense comparator                                           |      |

| Table 19. | 8-bit digital to analog converter                                  |      |

| Table 20. | S <sub>1</sub> protections and diagnostic                          |      |

| Table 21. | Application registers range                                        |      |

| Table 22. | IPEAK, IHOLD (-40 °C < $T_j$ < 150 °C, unless otherwise specified) |      |

| Table 23. | Charge pump                                                        |      |

| Table 24. | I <sup>2</sup> C-bus SDA, SCL I/O stages                           |      |

| Table 25. | I <sup>2</sup> C-bus SDA, SCL bus lines characteristics            |      |

| Table 26. | Electrical transient requirements (part 1)                         |      |

| Table 27. | Electrical transient requirements (part 2)                         |      |

| Table 28. | Electrical transient requirements (part 3)                         |      |

| Table 29. | 16 bit OTP modules                                                 |      |

| Table 30. | Thermal parameters                                                 |      |

| Table 31. | PowerSSO-36 mechanical data                                        |      |

| Table 32. | Document revision history                                          | . 45 |

L99SD01-E List of figures

# **List of figures**

| Figure 1.  | Block diagram                                                  | . 6 |

|------------|----------------------------------------------------------------|-----|

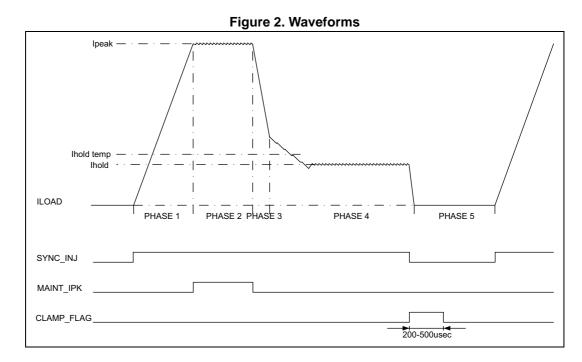

| Figure 2.  | Waveforms                                                      | . 9 |

| Figure 3.  | Load configuration                                             | . 9 |

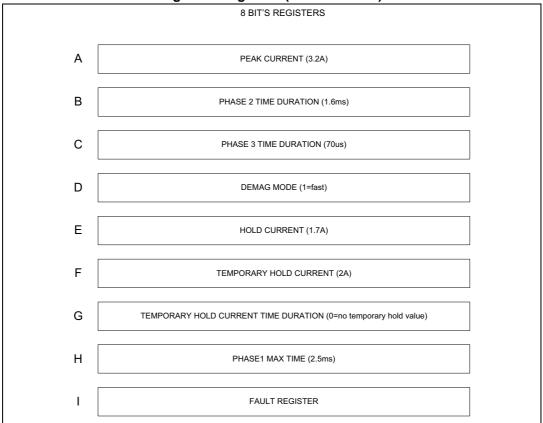

| Figure 4.  | Registers (default values)                                     | 12  |

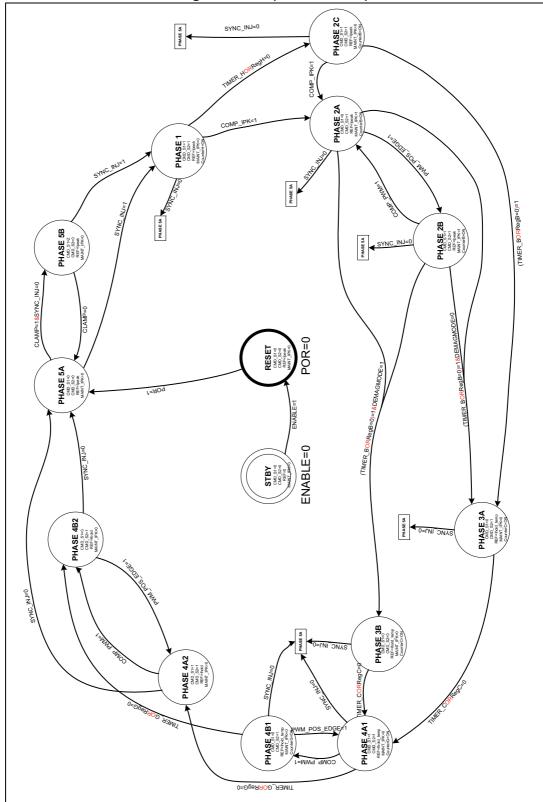

| Figure 5.  | FSM (state machine)                                            | 13  |

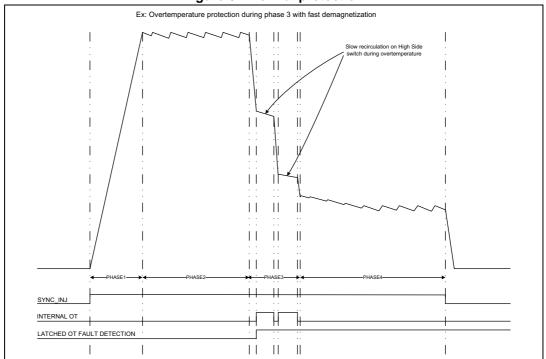

| Figure 6.  | Thermal protection                                             | 15  |

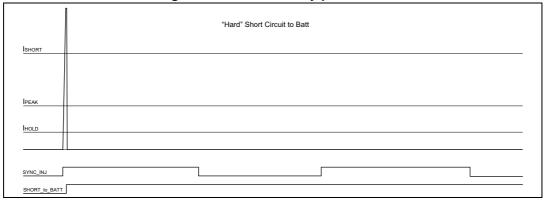

| Figure 7.  | Short to battery protection                                    | 15  |

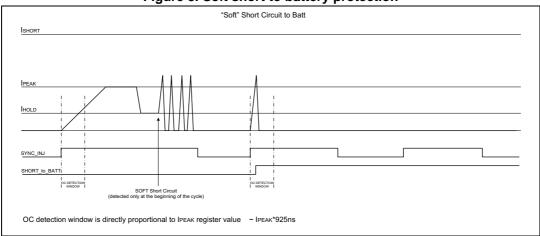

| Figure 8.  | Soft short to battery protection                               | 16  |

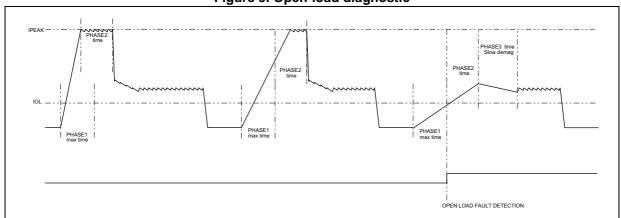

| Figure 9.  | Open-load diagnostic                                           |     |

| Figure 10. | Connection of I <sup>2</sup> C-devices to I <sup>2</sup> C-bus |     |

| Figure 11. | Bit transfer on the I <sup>2</sup> C-bus                       |     |

| Figure 12. | START and STOP conditions                                      | 18  |

| Figure 13. | Data transfer on the I <sup>2</sup> C-bus                      | 19  |

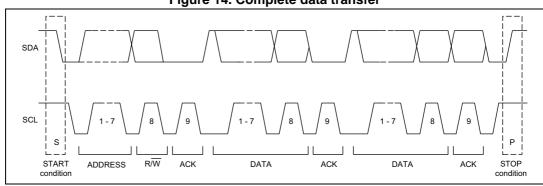

| Figure 14. | Complete data transfer                                         | 19  |

| Figure 15. | The first byte after the START procedure                       | 20  |

| Figure 16. | WRITE command                                                  | 20  |

| Figure 17. | Current READ command                                           | 21  |

| Figure 18. | Random READ command                                            |     |

| Figure 19. | Fault Register                                                 |     |

| Figure 20. | Definition of timing on the I <sup>2</sup> C-bus               |     |

| Figure 21. | Application schematic                                          |     |

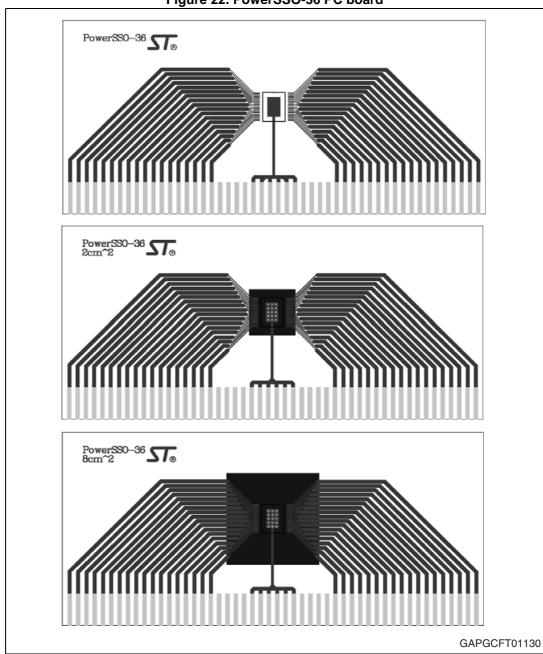

| Figure 22. | PowerSSO-36 PC board                                           |     |

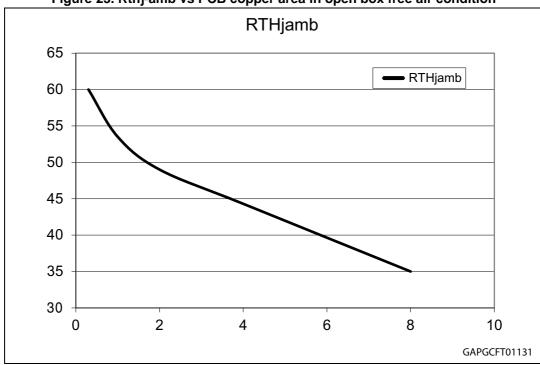

| Figure 23. | Rthj-amb vs PCB copper area in open box free air condition     | 41  |

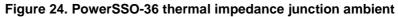

| Figure 24. | PowerSSO-36 thermal impedance junction ambient                 | 41  |

| Figure 25. | Thermal fitting model of a HSD in PowerSSO-36                  | 42  |

| Figure 26. | PowerSSO-36 package dimensions                                 | 43  |

# 1 Block diagram and pin description

Figure 1. Block diagram S 売中 KSENSE CHARGE PUMP CLAMP REF\_OC=FS\_DAC\_REF \_\_\_\_CMD\_S2\_\_ § 0 VDDL(5V) FSM-REGISTERS-OTP ANALOG CONTROL F D POR\_ ENABLE TERMICA MAINT\_IPK SCL COND SCL COND SCL COND SCL COND SCL COND SCR COND SC PWM IN\_SIGNAL CHECK\_SIGNAL

Table 2. Pin description

|               | Table 2. Fill description |                                                                                                                                                                        |  |  |  |

|---------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin<br>number | Pin name                  | Description                                                                                                                                                            |  |  |  |

| 1             | OTP_15V                   | Power supply for OTP test purposes. Not connected.                                                                                                                     |  |  |  |

| 2 IN_SIGNAL   |                           | This pin is used to acquire (through an external resistor) the signal coming from the Main ECU                                                                         |  |  |  |

| 3             | CHECK_SIGNAL              | The voltage on the "IN_SIGNAL" pin is compared with V <sub>BATT</sub> /2:  IF IN_SIGNAL > Vbatt/2 then CHECK_SIGNAL = H  IF IN_SIGNAL <= Vbatt/2 then CHECK_SIGNAL = L |  |  |  |

| 4             | MAINT_IPK                 | Diagnostic pin going high when device is regulating Ipeak current value                                                                                                |  |  |  |

| 5             | CLAMP_FLAG                | Reporting the CLAMP intervention and the end of injection cycle                                                                                                        |  |  |  |

| 6             | SDA                       | I <sup>2</sup> C serial interface data line                                                                                                                            |  |  |  |

| 7             | SCL                       | I <sup>2</sup> C serial interface clock line (100 kHz)                                                                                                                 |  |  |  |

| 8             | FAULT                     | The FAULT pin is pulled low whenever a fault condition is detected.                                                                                                    |  |  |  |

| 9             | PWM                       | External PWM clock                                                                                                                                                     |  |  |  |

| 10            | SYNC_INJ                  | It is used for injection synchronization and to set the single injection duration.                                                                                     |  |  |  |

| 11 ENABLE     |                           | This pin is used to enable/disable the device. When low, device enters standby low consumption mode                                                                    |  |  |  |

| 12 TEST       |                           | Test activation. Not connected.                                                                                                                                        |  |  |  |

| 13            | TEST_OUT3                 | Pin for test purposes. Not connected                                                                                                                                   |  |  |  |

| 14            | SGND                      | Signal ground pin. Do not connect to ground module. Use for local capacitor connection                                                                                 |  |  |  |

| 15-18         | PGND                      | Power ground pin                                                                                                                                                       |  |  |  |

| 19-22         | REC                       | Recirculation path – the external recirculation diode is connected between this pin and battery.                                                                       |  |  |  |

| 23            | TEST_OUT2                 | Pin for test purposes. Not connected                                                                                                                                   |  |  |  |

| 24            | TEST_OUT1                 | Pin for test purposes. Not connected                                                                                                                                   |  |  |  |

| 25            | BATT                      | Power supply voltage                                                                                                                                                   |  |  |  |

| 26            | CPUMP1                    | Charge pump pin for external capacitor connection                                                                                                                      |  |  |  |

| 27            | CPUMP2                    | Charge pump pin for external capacitor connection                                                                                                                      |  |  |  |

| 28            | CTANK                     | Supply voltage for high side driver                                                                                                                                    |  |  |  |

| 29            | VDDL                      | 5 V external supply voltage                                                                                                                                            |  |  |  |

| 30            | C3V3                      | 3.3 V supply pin for external capacitor connection                                                                                                                     |  |  |  |

| 31            | SGND                      | Signal ground pin. Do not connect to ground module. Use for local capacitor connection                                                                                 |  |  |  |

| 32            | E0                        | Address pin externally hard wired to ground or VDDL to address till 8 devices in parallel                                                                              |  |  |  |

| 33            | E1                        | Address pin externally hard wired to ground or VDDL to address till 8 devices in parallel                                                                              |  |  |  |

|               |                           |                                                                                                                                                                        |  |  |  |

Table 2. Pin description (continued)

| Pin<br>number | Pin name | Description                                                                               |  |  |  |  |

|---------------|----------|-------------------------------------------------------------------------------------------|--|--|--|--|

| 34            | E2       | Address pin externally hard wired to ground or VDDL to address till 8 devices in parallel |  |  |  |  |

| 35 SGND       |          | Signal ground pin. Do not connect to ground module. Use for local capacitor connection    |  |  |  |  |

| 36            | OTP_0V   | Power ground for OTP test purposes. Not connect                                           |  |  |  |  |

| Tab           | OUT      | Excitation path – the injector is connected between battery and this pin                  |  |  |  |  |

# 2 Injection cycle description

*Figure 2* includes the main waveforms showing a typical injection cycle while *Figure 3* shows typical load connection and recirculation diode.

REC

FLOATING DRIVER

CLAMP

C

Figure 3. Load configuration

#### 2.1 Phase 1

Injection phase starts by closing  $S_1$  switch when there is a rising edge of SYNC\_INJ signal. During this phase current on injector rises till an  $I_{PEAK}$  value set in the register A. If current doesn't reach  $I_{PEAK}$  value within a maximum time fixed in register H, the device status switches from phase 1 to phase 2.

#### 2.2 Phase 2

If current hasn't still reached  $I_{PEAK}$  value  $S_1$  switch continues to be ON and current continues to flow through load during all phase 2 whose length is set in register B. As soon as current reaches  $I_{PEAK}$  value it will be regulated in PWM mode at this value. PWM frequency is fixed by external clock via PWM pin.

Current is controlled by shutting-down  $S_1$  when current reaches  $I_{PEAK}$  value. During the remaining period injector current is re-circulating through  $S_2$  switch which should be always closed during phase 1 and phase 2. We speak about slow-recirculation during this phase.

Pin MAINT\_IPK should be kept high (5 V) when current has reached and is regulated around  $I_{\text{PFAK}}$  value.

#### 2.3 Phase 3

This is the temporary phase to go from  $I_{PEAK}$  to  $I_{HOLD}$  value. During this phase  $S_1$  is open. Register C sets the time length of this phase. Register D sets the recirculation mode:

- Slow recirculation: S<sub>2</sub> closed.

- Fast recirculation: S<sub>2</sub> open and clamp on S<sub>1</sub> activated.

A particular case is when at the end of phase 2 current has not reached  $I_{PEAK}$  value yet. In this case device will go to phase 3 in slow recirculation mode whatever the value set in register D.

#### 2.4 Phase 4

During this phase current is controlled to  $I_{HOLD}$  value. During this phase  $S_2$  is always closed. Register E sets  $I_{HOLD}$  current value. Current is controlled by shutting-down  $S_1$  when current reaches  $I_{HOLD}$  value. Recirculation is slow because  $S_2$  is closed during this phase.

PWM clock signal is given externally on pin PWM.

This phase starts at the end of phase 3 when current on injector has slowed down but not below the holding value. For this reason at the beginning of this phase PWM duty cycle will be fixed by the minimum turn-on time of regulation loop, till the current reaches I<sub>HOLD</sub> value.

This phase lasts till the end of injection given by the falling edge of SYNC\_INJ signal. Shutting of injector is done by turning off  $S_1$  and  $S_2$ . Fast recirculation happens through  $S_1$  by clamp activation. CLAMP\_FLAG is set to high value (5 V) during 350 µsec minimum. To minimize the current ripple during the passage from phase 3 to phase 4, a temporary hold value could be used for some PWM cycles. Register F sets this temporary hold current value, whilst Register G sets time length.

#### 2.5 Phase 5

System is waiting for next injection cycle. No current is flowing through injector. Switches  $S_1$  and  $S_2$  are open.

End of injection cycle could happen everywhere during injection cycle. So device should sustain fast recirculation even during phase 2 with high current values.

If the time duration of one phase is set to zero then the corresponding phase should be skipped and device must enter the following phase.

All registers have pre-programmed values hard coded in the device. So device can operate as it is without needing of a first programming phase (for typical application). In all other applications first register writing is done automatically at the beginning of communication. All registers could be modified during the operating phase. Modified values are activated at the beginning of the first injection cycle following the end of the serial communication. Synchronization event is the rising edge of SYNC\_INJ signal. In reset state all registers are cleared.

Enable pin allows device to enter standby mode with very low current consumption. Enable signal can be supplied directly by microcontroller.

Typical applications include 4 to 8 injectors which are driven via a microcontroller through a serial interface (I<sup>2</sup>C). Each device is recognizable by a unique hard wired address code. Three pins are devoted to code up to 8 device addresses.

Each communication between microcontroller and each device is closed by an acknowledgment message. If this message does not arrive it means that something is not working in communication between microcontroller and L99SD01-E.

Figure 4. Registers (default values)

Figure 5. FSM (state machine)

Diagnostic L99SD01-E

# 3 Diagnostic

Device is auto-protected against some failures and is able to send the information fault to microcontroller via FAULT pin and serial communication line. The following table resumes all the fault conditions detected by the device and the corresponding device behavior.

**Table 3. Diagnostic fault**

| Fault condition                          | Device behavior                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| THERMAL                                  | Shutdown S <sub>1</sub> with slow recirculation (S <sub>2</sub> on). Fault pin low and fault register set.                                                                                                                                                                                                                                                                                                                   |  |  |

| SHUTDOWN                                 | Device restarts when temperature slows down the reset value. Fault register reset by microcontroller.                                                                                                                                                                                                                                                                                                                        |  |  |

| THERMAL WARNING                          | Normal mode. Fault register set. Fault register reset by microcontroller. No action on Fault pin.                                                                                                                                                                                                                                                                                                                            |  |  |

| UNDERVOLTAGE                             | Normal mode. Fault pin low and fault register set. Fault register reset by microcontroller.                                                                                                                                                                                                                                                                                                                                  |  |  |

| OVERVOLTAGE                              | Normal mode. Fault pin low and fault register set. Fault register reset by microcontroller.                                                                                                                                                                                                                                                                                                                                  |  |  |

| OUTPUT SHORTED<br>TO BATT <sup>(1)</sup> | Shut down immediately after minimum turn on time. Fault pin low and fault register set. To avoid false overcurrent detections, fault is latched in register only if happens during phase 1 or 2.  In case of resistive short circuit, at the beginning of injection cycle current through load rises too fast and this will set as a short fault.  Device couldn't restart until fault register is reset by microcontroller. |  |  |

| OPEN LOAD <sup>(2)</sup>                 | Normal mode. Fault pin low and fault register set. Fault register reset by microcontroller.                                                                                                                                                                                                                                                                                                                                  |  |  |

<sup>1.</sup> No internal current limiter. Response time of current limiter would be longer than shut-off time.

<sup>2.</sup> CHECK during PHASE 1. If max duration time of phase1 is reached (register H value) Open-load detection signal is read by control logic and validated.

L99SD01-E Diagnostic

Figure 7. Short to battery protection

Diagnostic L99SD01-E

Figure 8. Soft short to battery protection

Figure 9. Open-load diagnostic

# 4 I<sup>2</sup>C protocol description

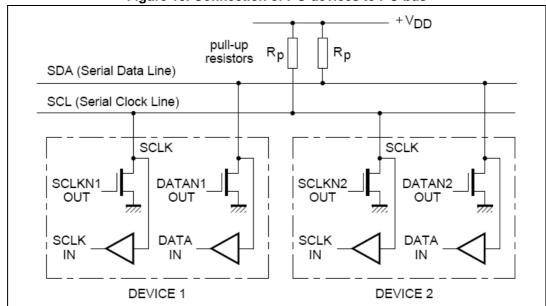

The L99SD01-E is compatible with the standard I<sup>2</sup>C serial bus. This is a two wire serial interface that uses a bi-directional data bus (SDA) and serial clock (SCL). Each device connected to the bus is recognized by a unique address (whether it is a microcontroller, memory or injector driver) and can operate as either a transmitter or receiver, depending on the function of the device. In addition to transmitters and receivers, devices can also be considered as masters or slaves when performing data transfers. A master is the device which initiates a data transfer on the bus and generates the clock signals to permit that transfer. At that time, any device addressed is considered a slave. L99SD01-E can only be a slave, transmitter or receiver, during communication.

Figure 10. Connection of I<sup>2</sup>C-devices to I<sup>2</sup>C-bus

### 4.1 SDA and SCL signals

Both SDA and SCL are bidirectional lines, connected to a positive supply voltage via a current-source or pull-up resistor. When the bus is free, both lines are HIGH. The output stages of devices connected to the bus must have an open-drain or open-collector to perform the wired-AND function.

Data on the I<sup>2</sup>C bus can be transferred at rates up to 100 kbit/s in the standard-mode. The number of devices connected to the bus is limited by the max bus capacitance.

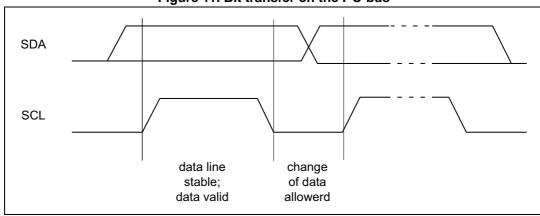

### 4.2 Data validity

The data on the SDA line must be stable during the HIGH period of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW. One clock pulse is generated for each data bit transferred.

Figure 11. Bit transfer on the I<sup>2</sup>C-bus

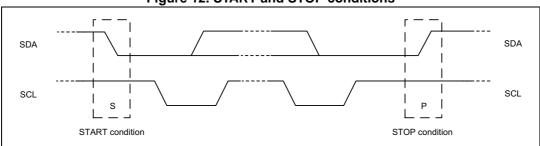

#### 4.3 START and STOP conditions

All transactions begin with a START (S) and can be terminated by a STOP (P).

A HIGH to LOW transition on the SDA line while SCL is HIGH defines a START condition. A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition.

START and STOP conditions are always generated by the master. The bus is considered to be busy after the START condition. The bus is considered to be free again a certain time after a STOP condition.

The bus stays busy if a repeated START (Sr) is generated instead of a STOP signal. In this respect, the START (S) and repeated START (Sr) conditions are functionally identical.

Figure 12. START and STOP conditions

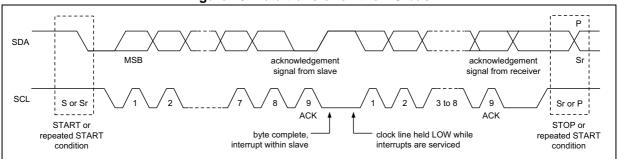

### 4.4 Byte format

Every byte put on the SDA line must be 8 bits long. The number of bytes that can be transmitted per transfer is unrestricted. Each byte has to be followed by an Acknowledge bit. Data is transferred with the Most Significant Bit (MSB) first.

577

Figure 13. Data transfer on the I<sup>2</sup>C-bus

#### 4.5 Acknowledge (ACK) and Not Acknowledge (NACK)

The acknowledge takes place after every byte. The acknowledge bit allows the receiver to signal the transmitter that the byte was successfully received and another byte may be sent. All clock pulses including the acknowledge 9<sup>th</sup> clock pulse are generated by the master.

The acknowledge signal is defined as follows: the transmitter releases the SDA line during the acknowledge clock pulse so the receiver can pull the SDA line LOW and it remains stable LOW during the HIGH period of this clock pulse. Setup and hold times must also be taken into account.

When the SDA remains HIGH during this 9<sup>th</sup> clock pulse, this is defined as the Not Acknowledge signal. The master can then generate either a STOP condition to abort the transfer, or a repeated START condition to start a new transfer.

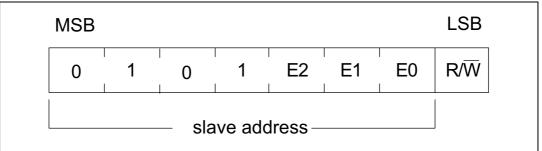

#### 4.6 **Device addressing**

Data transfers follow the format shown in fig.10. After the START condition (S), a slave address is sent. This address is 7 bits long followed by an eighth bit which is a data direction bit (R/W). A 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ). A data transfer is always terminated by a STOP condition (P) generated by the master. However, if a master still wishes to communicate on the bus, it can generate a repeated START condition (Sr) and address another slave without first generating a STOP condition. Various combinations of read/write formats are then possible within such a transfer.

Figure 14. Complete data transfer

Figure 15. The first byte after the START procedure

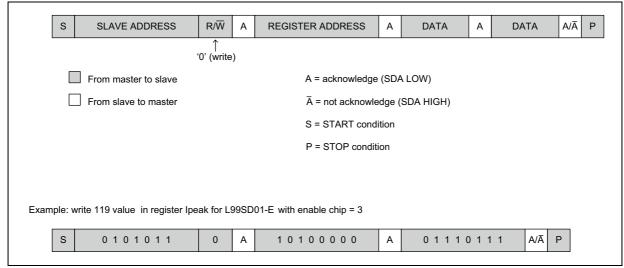

#### 4.7 Write operation

WRITE command in L99SD01-E is used to store data into volatile memory.

Master initiates a START condition (S) and then sends the first byte which is the slave address followed by the R/W= '0'. If L99SD01-E recognizes its address then it generates an ACK signal.

Each L99SD01-E has a different slave address. The first four bits of the address are the device type identifier and do not change for all L99SD01-E devices. The following three bits are used to address till 8 different L99SD01-E on the same bus.

Second byte sent by master in write mode is the register address where data must be written. After Acknowledge from slave, master starts to send the data, which can be one or more bytes. Eight different registers may be written in L99SD01-E. If more than eight data bytes are sent by the master, roll-over occurs.

The transfer finishes when master sends a STOP condition (P).

After the successful completion of write operations, the device internal address counter is incremented automatically, to point to the next byte address after the last one that was modified.

Figure 16. WRITE command

#### 4.8 Read operation

READ command in L99SD01-E is used to read data contained into volatile memory. There are essentially two different Read operation modes: Current Read and Random Read.

In Random READ mode a dummy write is first performed to load the address into the address counter, then without sending a STOP condition, the Master sends another START condition, and repeats the slave address, with the R/W bit set to '1' (READ). At this point slave acknowledges and starts sending data output from the addressed register. One or more bytes can be sent to master. L99SD01-E stops sending data when it receives a NACK signal from master. At this point master can decide to stop transmission by sending a STOP condition or to generate a repeated START condition to start communication with another slave. At the end of communication internal address counter is incremented automatically, to point to the next byte address after the last one that was read.

In Current READ mode, following a START condition, the master sends a slave address with a R/W bit set to '1'. At this point slave acknowledges and starts sending data output from the register addressed by the internal counter. One or more bytes can be sent to master. L99SD01-E stops sending data when it receives a NACK signal from master. At this point master can decide to stop transmission by sending a STOP condition or to generate a repeated START condition to start communication with another slave.

SLAVE ADDRESS R/W Ā S DATA Α Α DATA Р DATA '1' (read) From master to slave A = acknowledge (SDA LOW) From slave to master  $\bar{A}$  = not acknowledge (SDA HIGH) S = START condition P = STOP condition Example: Read two registers values for L99SD01-E with enable chip = 1. Internal register counter is pointing to register 7 (0:7) Ρ S 0 1 0 1 0 0 1 Ā Α Phase1 time max Α Ipeak current After read operation internal register counter is pointing to register 1

Figure 17. Current READ command

SLAVE ADDRESS R/W REGISTER ADDRESS SLAVE ADDRESS DATA DATA Ā '0' (write From master to slave A = acknowledge (SDA LOW) From slave to master Ā = not acknowledge (SDA HIGH) S = START condition P = STOP condition Example:Read Hold current and temporary hold current registers values for L99SD01-E with enable chip = 0. 0 1 0 1 0 0 0 After read operation internal register counter is pointing to register 6

Figure 18. Random READ command

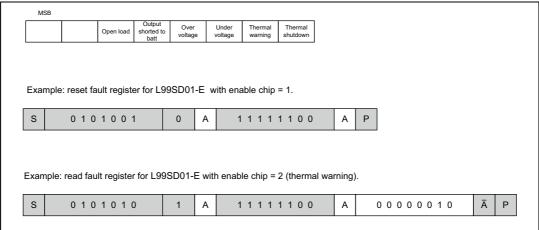

Besides the eight parameter registers, there is another eight bit register which corresponds to the fault register. It can only be reset and read via dedicated commands.

#### 4.9 Registers Addresses and Fault register

L99SD01-E does not need to be first configured via I<sup>2</sup>C-bus line. Default application parameters are hard-wired in the device. At first turn-on default application parameters are transferred inside registers which can be further modified by customer via I<sup>2</sup>C-bus if needed. In order to permit "real-time" parameter changes each register will have an equivalent temporary register to store the data until the first low-to-high transition on SYNC\_INJ signal at the end of communication. At this time temporary registers are transferred into the actual parameter registers.

Each register can be read/written via serial interface. Fault register can be read and reset (fault cleared).

|     | Register<br>address | Register content                     | Length | Access | Purpose         |

|-----|---------------------|--------------------------------------|--------|--------|-----------------|

| R0  | 1010 0000           | I peak current                       | 1 byte | R/W    | Read/Store data |

| R1  | 1010 0001           | Phase 2 duration                     | 1 byte | R/W    | Read/Store data |

| R2  | 1010 0010           | Phase 3 duration                     | 1 byte | R/W    | Read/Store data |

| R3  | 1010 0011           | Demag mod                            | 1 byte | R/W    | Read/Store data |

| R4  | 1010 0100           | Hold Current                         | 1 byte | R/W    | Read/Store data |

| R5  | 1010 0101           | Temporary hold current               | 1 byte | R/W    | Read/Store data |

| R6  | 1010 0110           | Temporary hold current time duration | 1 byte | R/W    | Read/Store data |

| R7  | 1010 0111           | Phase 1 time max                     | 1 byte | R/W    | Read/Store data |

| R8  | 1111 1100           | Fault Register                       | 1 byte | W      | Clear Fault     |

| 110 | 1111 1100           | r adit register                      | 1 byte | R      | Read Fault      |

Table 4. Registers addresses

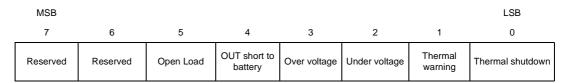

#### Figure 19. Fault Register

Register description L99SD01-E

## 5 Register description

#### 5.1 Register A

| MSB    |        |        |        |        |        |        | LSB    |

|--------|--------|--------|--------|--------|--------|--------|--------|

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

| IPK[7] | IPK[6] | IPK[5] | IPK[4] | IPK[3] | IPK[2] | IPK[1] | IPK[0] |

Address: 0xA0

Type: R/W

**Reset:** 0010 1000b

**Description:** IPK[7...0]: I<sub>PEAK</sub> current value.

$I_{\mbox{\scriptsize PEAK}}$  current in ampere can be computed as IPK[7...0] \* 20.55 / 255. Value are only

guaranteed between 2 A and 14 A.

### 5.2 Register B

Address: 0xA1

Type: R/W

**Reset:** 0101 0010b

**Description:** TPK[7...0]: Phase 2 (I<sub>PEAK</sub> current) duration.

Phase 2 duration in ms can be computed as TPK[7...0] \* 5 / 255.

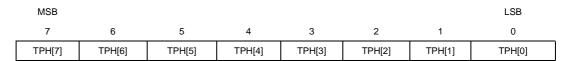

## 5.3 Register C

Address: 0xA2 Type: R/W

**Reset:** 0010 0100b

**Description:** TPH[7...0]: t<sub>PEAK\_TO\_HOLD</sub> (Phase 3) duration.

If DEMAG\_MODE bit is 0,  $t_{PEAK\_TO\_HOLD}$  in microseconds can be computed as

TPH[7...0] \* 500 / 255.

If DEMAG\_MODE bit is set to 1,  $t_{PEAK\_TO\_HOLD}$  in milliseconds can be computed as TPH[7...0] \* 10 / 255.

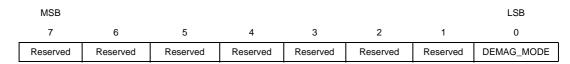

### 5.4 Register D

Address: 0xA3

Type: R/W

**Reset:** 0000 0001b

**Description:** DEMAG\_MODE: demagnatization during phase 3 is fast if this bit is set to 1 or slow

otherwise.

Note: If at the end of phase 2 the current has not reached I<sub>PEAK</sub> value, slow demagnatization

mode will be applied during phase 3 whatever the value of DEMAG\_MODE bit.

#### 5.5 Register E

MSB LSB 7 0 6 5 4 3 2 IH[7] IH[6] IH[5] IH[4] IH[3] IH[2] IH[1] IH[0]

Address: 0xA4

Type: R/W

**Reset:** 0110 1001b

**Description:** IH[7...0]: I<sub>HOLD</sub> current value.

$I_{\mbox{\scriptsize HOLD}}$  current value in ampere can be computed as IH[7...0] \* 4.11 / 255. Value are

only guaranteed between 0.5 A and 3 A.

Register description L99SD01-E

#### 5.6 Register F

| MSB      |          |          |          |          |          |          | LSB      |

|----------|----------|----------|----------|----------|----------|----------|----------|

| 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

| IHTMP[7] | IHTMP[6] | IHTMP[5] | IHTMP[4] | IHTMP[3] | IHTMP[2] | IHTMP[1] | IHTMP[0] |

Address: 0xA5 Type: R/W

**Reset:** 0111 1100b

**Description:** IHTMP[7...0]: I<sub>HOLD TEMP</sub> current value (reference current during Phase 4).

The current value in ampere can be computed as IHTMP[7...0] \* 4.11 / 255. Value

are only guaranteed between 0.5 A and 3.5 A.

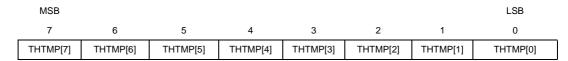

#### 5.7 Register G

Address: 0xA6 Type: R/W

**Reset:** 0000 0000b

**Description:** THTMP[7..0]: I<sub>HOLD TEMP</sub> duration inside Phase 4.

Phase3 duration in ms can be computed as THTMP[7...0] \* 5 / 255.

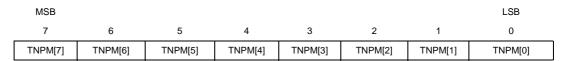

### 5.8 Register H

Address: 0xA7

Type: R/W

**Reset:** 0100 0000b

**Description:** TNPKM[7...0]:  $t_{NO\_PEAK\_MAX}$  value.

During phase 1, if  $I_{PEAK}$  value is not reached within  $t_{NO\_PEAK\_MAX}$ , the device switches into Phase 2.  $t_{NO\_PEAK\_MAX}$  in millisecond can be computed as

TNPKM[7...0] \* 10 / 255.

#### 5.9 Fault register

Address: 0xFC

**Type:** R/W. Any write action will result in a register clear.

**Reset:** 0000 0000b

Bit [4] Output shorted to battery flag.

Bit is set by HW when an over current is detected on the output at the beginning of the injection cycle (phases 1 and 2). Write the register to clear this bit.

Bit [3] Over voltage flag.

Bit is set by HW when an over voltage is detected on the battery voltage, write the register to clear this bit.

Bit [2] Under voltage flag.

Bit is set by HW when an under voltage is detected on the battery voltage, write the register to clear this bit.

Bit [1] Thermal warning flag.

Bit is set by HW when the die temperature exceeds  $T_{TW}$  threshold, write the register to clear this bit.

Bit [0] Thermal shutdown flag.

Bit is set by HW when the die temperature exceeds  $T_{TSD}$  threshold, a register writing clears this bit only if the die temperature is lower than  $T_{TR}$ .

# 6 Electrical specification

# 6.1 Absolute maximum rating

Table 5. Absolute maximum rating

| Symbol                                                                                   | abol Parameter Value                                                                                                      |                                          | Unit |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------|

| V <sub>BATT</sub>                                                                        | Maximum DC supply voltage                                                                                                 | 40                                       | V    |

| V <sub>BATT_REV</sub>                                                                    | Reverse DC supply voltage                                                                                                 | -0.3                                     | V    |

| $V_{LOAD}$                                                                               | Maximum DC load voltage                                                                                                   | Internally limited                       | V    |

| I <sub>LOAD</sub>                                                                        | Maximum DC load current                                                                                                   | Internally limited to I <sub>SHORT</sub> | А    |

| I <sub>R(LOAD)</sub>                                                                     | Maximum reverse output current, $T_C = 25$ °C; $t = 5$ ms.                                                                | -20                                      | А    |

| E <sub>AS</sub>                                                                          | Single pulse energy S1 switch; $V_{BATT}$ = 13.5 V; $T_j$ = 150°C; L = 6 mH; $R_L$ = 0 $\Omega$ , typical clamp voltage   | 88                                       | mJ   |

| E <sub>REP1</sub>                                                                        | Repetitive energy S1 switch. $V_{BATT}$ = 13.5 V; $T_{j}$ = 125°C; L = 6 mH; $R_{L}$ = 0 $\Omega$ , typical clamp voltage | 38.6                                     | mJ   |

| E <sub>REP2</sub>                                                                        | Repetitive energy S1 switch. $V_{BATT}$ = 13.5 V; $T_{j}$ = -40°C; L = 6 mH; $R_{L}$ = 0 $\Omega$ , typical clamp voltage | 70                                       | mJ   |

| V <sub>C3V3</sub>                                                                        | 3.3 V logic supply voltage range                                                                                          | -0.3 to 3.6                              | V    |

| V <sub>VDDL</sub>                                                                        | 5 V external supply voltage                                                                                               | 5.5                                      | V    |

| VSYNC_INJ VE0 VE1 VE2 VCHECK_SIGNAL VSCL VSDA VMAINT_IPK VPWM VCLAMP_FLAG VFAULT VENABLE | Logic input / output voltage range                                                                                        | -0.3 to V <sub>DDL</sub> +0.3            | V    |

| V <sub>IN_SIGNAL</sub><br>V <sub>REC</sub>                                               | HV signal pins                                                                                                            | -0.3 to V <sub>BATT</sub>                | V    |

| V <sub>OUT</sub>                                                                         | Output pin                                                                                                                | 55                                       | V    |

| V <sub>CTANK</sub>                                                                       | Maximum charge pump output voltage                                                                                        | V <sub>BATT</sub> + 15V                  | V    |

| V <sub>CPUMP1</sub><br>V <sub>CPUMP2</sub>                                               | Maximum charge pump pins voltage                                                                                          | V <sub>BATT</sub>                        | V    |

| V <sub>ESD</sub>                                                                         | Electrostatic discharge (R = 1.5kW, C = 100pF, all pins)                                                                  | +/-2000                                  | V    |

| T <sub>j</sub>                                                                           | Junction operating temperature                                                                                            | -40 to 150                               | °C   |

| T <sub>STG</sub>                                                                         | Storage temperature                                                                                                       | -55 to 150                               | °C   |

#### 6.2 Thermal data

Table 6. Thermal data

| Symbol               | Parameter                           | Value         | Unit |

|----------------------|-------------------------------------|---------------|------|

| R <sub>thj-amb</sub> | Thermal resistance junction-ambient | See Figure 23 | °C/W |

### 6.3 Electrical characteristics

6 V <  $V_{BATT}$  < 28 V; -40°C <  $T_j$  < 150°C; unless otherwise specified

Table 7. V<sub>BATT</sub> supply

| Symbol               | Parameter                                                            | Test conditions                                                                                           | Min | Тур | Max | Unit |

|----------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>BATT</sub>    | Operating supply voltage                                             |                                                                                                           | 6   |     | 28  | V    |

| I <sub>SON</sub>     | V <sub>BATT</sub> DC supply current                                  | V <sub>BATT</sub> = 13 V; V <sub>DDL</sub> = 5 V;<br>V <sub>ENABLE</sub> = 5 V; Output floating           |     | 2   |     | mA   |

| I <sub>STBY</sub>    | V <sub>BATT +</sub> V <sub>VDDL</sub><br>quiescent supply<br>current | $V_{BATT}$ = 13V; $V_{DDL}$ = 5V;<br>$V_{ENABLE}$ = 0V ; Output floating<br>-40°C < T <sub>j</sub> < 85°C |     |     | 10  | μΑ   |

| I <sub>DDL</sub>     | V <sub>DDL</sub> DC supply current                                   | V <sub>BATT</sub> = 13 V; V <sub>DDL</sub> = 5 V;<br>V <sub>ENABLE</sub> = 5 V                            |     | 8   | 10  | mA   |

| V <sub>OV</sub>      | Overvoltage threshold                                                |                                                                                                           | 34  |     | 40  | V    |

| V <sub>UV</sub>      | Undervoltage threshold                                               |                                                                                                           |     |     | 6   | ٧    |

| V <sub>UV_hyst</sub> | Undervoltage threshold hysteresis                                    |                                                                                                           | 0.4 | 0.6 |     | V    |

Table 8. Power switches  $S_1 - S_2$

| Symbol | Parameter                              | Test conditions                                                                                  | Min | Тур | Max   | Unit |

|--------|----------------------------------------|--------------------------------------------------------------------------------------------------|-----|-----|-------|------|

|        |                                        | I <sub>LOAD</sub> = 5 A; S <sub>1</sub> = ON;<br>V <sub>BATT</sub> = 13 V; T <sub>j</sub> = 25°C | 1   |     | 0.060 | Ω    |

| RON1   | On state resistance (excitation path)  | $I_{LOAD} = 5 \text{ A}; S_1 = ON;$<br>$V_{BATT} = 13 \text{ V}$                                 | l   | l   | 0.120 | Ω    |

|        |                                        | $I_{LOAD} = 5 \text{ A}; S_1 = ON;$<br>$V_{BATT} = 6 \text{ V}$                                  | l   |     | 0.150 | Ω    |

|        |                                        | I <sub>LOAD</sub> = 5 A; S <sub>2</sub> = ON;<br>V <sub>BATT</sub> = 13 V; T <sub>j</sub> = 25°C |     |     | 0.060 | Ω    |

| RON2   | On state resistance Recirculation Path | $I_{LOAD} = 5 \text{ A}; S_2 = ON;$<br>$V_{BATT} = 13 \text{ V}$                                 |     |     | 0.120 | Ω    |

|        |                                        | $I_{LOAD} = 5 \text{ A}; S_2 = ON;$<br>$V_{BATT} = 6 \text{ V}$                                  |     |     | 0.150 | Ω    |

Table 9. S<sub>1</sub> switching (excitation path)

| Symbol                | Parameter                           | Test conditions                                                   | Min | Тур  | Max  | Unit |

|-----------------------|-------------------------------------|-------------------------------------------------------------------|-----|------|------|------|

| TD <sub>ON_S1</sub>   | Turn-on delay time                  | V <sub>BATT</sub> = 13.5 V;                                       | 100 | 180  | 300  | ns   |

| T <sub>R_S1</sub>     | Rise time of output voltage         |                                                                   |     | 500  | 900  | ns   |

| TD <sub>OFF_S1</sub>  | Turn-off delay time                 |                                                                   | 600 | 1400 | 2000 | ns   |

| T <sub>F_S1</sub>     | Fall time of output voltage         |                                                                   |     | 600  | 1000 | ns   |

| V <sub>CLAMP_S1</sub> | Switch S <sub>1</sub> clamp voltage | $I_{LOAD} = 0.5/14 \text{ A}; S_1 = \text{off}; S_2 = \text{off}$ | 44  |      | 55   | V    |

#### Table 10. Switching (recirculating path)

| Symbol               | Parameter                   | Test conditions                                     | Min | Тур  | Max  | Unit |

|----------------------|-----------------------------|-----------------------------------------------------|-----|------|------|------|

| TD <sub>ON_S2</sub>  | Turn-on delay time          | $V_{BATT} = 13.5 \text{ V};$ $R_{LOAD} = 2.5\Omega$ |     | 280  | 600  | ns   |

| T <sub>R_S2</sub>    | Rise time of output voltage |                                                     |     | 1500 | 3000 | ns   |

| TD <sub>OFF_S2</sub> | Turn-off delay time         |                                                     | _   | 150  | 600  | ns   |

| T <sub>F_S2</sub>    | Fall time of output voltage |                                                     | 1   | 200  | 800  | ns   |

#### Table 11. V<sub>DDL</sub> undervoltage detection

| Symbol                | Parameter                    | Test conditions                            | Min | Тур | Max | Unit |

|-----------------------|------------------------------|--------------------------------------------|-----|-----|-----|------|

| V <sub>POR_OFF</sub>  | power-on-reset<br>threshold  | V <sub>DDL</sub> increasing                | 3.8 | 4   | 4.2 | V    |

| V <sub>POR_ON</sub>   | power-on-reset<br>threshold  | V <sub>DDL</sub> decreasing                | 3.2 | 3.4 | 3.6 | ٧    |

| V <sub>POR_hyst</sub> | power-on-reset<br>hysteresis | V <sub>POR_OFF</sub> - V <sub>POR_ON</sub> | 0.3 |     |     | V    |

#### Table 12. Enable

| Symbol                   | Parameter                 | Test conditions           | Min | Тур | Max | Unit |

|--------------------------|---------------------------|---------------------------|-----|-----|-----|------|

| V <sub>ENABLE H</sub>    | Enable voltage threshold  | V <sub>BATT</sub> = 13 V  | 1   | 1.8 | 2.3 | V    |

| V <sub>ENABLE_L</sub>    | Enable voltage reset      | V <sub>BATT</sub> = 13 V  | 0.8 | 1.5 | 1.9 | V    |

| V <sub>ENABLE_HYST</sub> | Enable voltage hysteresis | V <sub>BATT</sub> = 13 V  | 0.1 | 0.3 |     | V    |

| I <sub>ENABLE</sub>      | Enable pull down current  | V <sub>ENABLE</sub> = 5 V | 20  | 50  | 100 | μΑ   |

Table 13. Input: SYNC\_INJ

| Symbol                 | Parameter                           | Test conditions               | Min  | Тур | Max  | Unit |

|------------------------|-------------------------------------|-------------------------------|------|-----|------|------|

| V <sub>SYNC_L</sub>    | Input low level voltage             | V <sub>DDL</sub> = 5 V        |      |     | 1.08 | V    |

| V <sub>SYNC_H</sub>    | Input high level voltage            | V <sub>DDL</sub> = 5 V        | 2.1  |     |      | V    |

| V <sub>SYNC_HYST</sub> | Input hysteresis voltage            | V <sub>DDL</sub> = 5 V        | 0.15 |     |      | V    |

| I <sub>SYNC_INJ</sub>  | pull down current at SYNC_INJ input | V <sub>SYNC_INJ</sub> = 1.5 V | 20   | 50  | 80   | μΑ   |

#### Table 14. Input: PWM

| Symbol                | Parameter                      | Test conditions          | Min  | Тур | Max  | Unit |

|-----------------------|--------------------------------|--------------------------|------|-----|------|------|

| V <sub>PWM_L</sub>    | Input low level voltage        | V <sub>DDL</sub> = 5 V   |      |     | 1.08 | V    |

| V <sub>PWM_H</sub>    | Input high level voltage       | V <sub>DDL</sub> = 5 V   | 2.1  |     |      | V    |

| V <sub>PWM_HYST</sub> | Input hysteresis voltage       | V <sub>DDL</sub> = 5 V   | 0.15 |     |      | V    |

| I <sub>PWM</sub>      | Pull down current at PWM input | V <sub>PWM</sub> = 1.5 V | 20   | 50  | 80   | μΑ   |

#### **Table 15. Inputs: E0, E1, E2**

| Symbol               | Parameter                     | Test conditions        | Min  | Тур | Max  | Unit |

|----------------------|-------------------------------|------------------------|------|-----|------|------|

| $V_{Ex\_L}$          | Input low level voltage       | V <sub>DDL</sub> = 5V  |      |     | 1.08 | V    |

| V <sub>Ex_H</sub>    | Input high level voltage      | V <sub>DDL</sub> = 5V  | 2.1  |     |      | V    |

| V <sub>Ex_HYST</sub> | Input hysteresis voltage      | V <sub>DDL</sub> = 5V  | 0.15 |     |      | V    |

| I <sub>Ex_IN</sub>   | Pull down current at Ex input | V <sub>Ex</sub> = 1.5V | 20   | 50  | 80   | μΑ   |

#### Table 16. IN\_SIGNAL VOLTAGE MONITOR, CHECK\_SIGNAL

| Symbol                      | Parameter                          | Test conditions                                                   | Min                      | Тур                       | Max                      | Unit |

|-----------------------------|------------------------------------|-------------------------------------------------------------------|--------------------------|---------------------------|--------------------------|------|

| V <sub>IN_SIGNAL_L</sub>    | Input low level voltage threshold  |                                                                   | 0.4<br>V <sub>BATT</sub> | 0.45<br>V <sub>BATT</sub> | 0.5<br>V <sub>BATT</sub> | V    |

| V <sub>IN_SIGNAL_</sub> H   | Input high level voltage threshold |                                                                   | 0.5<br>V <sub>BATT</sub> | 0.55<br>V <sub>BATT</sub> | 0.6<br>V <sub>BATT</sub> | V    |

| V <sub>IN_SIGNAL_HYST</sub> | Input hysteresis voltage           |                                                                   |                          | 0.1<br>V <sub>BATT</sub>  |                          | V    |

| V <sub>CHECK_</sub> SIGNAL  | Check_signal output voltage        | V <sub>IN_SIGNAL</sub> = 0 V;<br>I <sub>CHECK_SIGNAL</sub> = 1 mA |                          |                           | 0.9                      | V    |

#### Table 17. Differential current sense amplifier

| Symbol               | Parameter                         | Test conditions | Min | Тур | Max | Unit |

|----------------------|-----------------------------------|-----------------|-----|-----|-----|------|

| V <sub>ICM_AMP</sub> | Input voltage range – common mode |                 | 0   |     | 0.8 | V    |

Table 17. Differential current sense amplifier (continued)

| Symbol                  | Parameter                          | Test conditions                                                                                                                           | Min  | Тур | Max | Unit |

|-------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| V                       | Input voltage range                | Gain = 20; V <sub>DDL</sub> = 5 V                                                                                                         | 10   |     | 80  | mV   |

| V <sub>IDIFF_AMP</sub>  | - differential mode                | Gain = 4; V <sub>DDL</sub> = 5 V                                                                                                          | 20   |     | 400 | mV   |

| V <sub>IOFF_AMP</sub>   | Input offset voltage               | V <sub>DDL</sub> = 5 V                                                                                                                    | -500 |     | 500 | μV   |

| Gain                    | Opamp gain                         | I <sub>LOAD</sub> = I <sub>HOLD</sub>                                                                                                     |      | 20  |     |      |

| Gain <sub>AMP</sub>     | Орапір дапі                        | I <sub>LOAD</sub> = I <sub>PEAK</sub>                                                                                                     |      | 4   |     |      |

| CBW                     | Gain bandwidth                     | G = 20                                                                                                                                    |      | 2   |     | MHz  |

| GBW <sub>AMP</sub>      | product                            | G = 4                                                                                                                                     |      | 0.4 |     | MHz  |

| CMRR <sub>AMP</sub>     | Input common mode rejection        | F = 1 KHz                                                                                                                                 | 60   |     |     | dB   |

| PSRR+ <sub>AMP</sub>    | 3.3 V power supply rejection ratio |                                                                                                                                           |      | 55  |     | dB   |

| PSRR- <sub>AMP</sub>    | GND power supply rejection ratio   |                                                                                                                                           |      | 40  |     | dB   |

| T <sub>SETTLING_R</sub> | Rising settling time               | $G = 20$ ; $(V_{RSP} - V_{RSN}) = 0 \text{ V to}$<br>10 mV in 10 ns<br>$G = 4$ ; $(V_{RSP} - V_{RSN}) = 0 \text{ V to}$<br>20 mV in 10 ns |      |     | 3.5 | μs   |

| T <sub>SETTLING_F</sub> | Falling settling time              | $G = 20$ ; $(V_{RSP} - V_{RSN}) = 10 \text{ mV}$<br>to 0 V in 10 ns<br>$G = 4$ ; $(V_{RSP} - V_{RSN}) = 20 \text{ mV}$ to<br>0 V in 10 ns |      |     | 3.5 | μs   |

#### Table 18. Current sense comparator

| Symbol Parameter          |                                   | Test conditions                                  | Min  | Тур | Max | Unit |

|---------------------------|-----------------------------------|--------------------------------------------------|------|-----|-----|------|

| V <sub>ICM_PWMCOMP</sub>  | Input voltage range – common mode |                                                  | 0.05 | _   | 2   | V    |

| V <sub>IOFF_PWMCOMP</sub> | Input offset voltage              | V <sub>DDL</sub> = 5 V                           | -15  | _   | 6   | mV   |

| TD <sub>PWMCOMP</sub>     | Input to output delay             | V <sub>INPUT</sub> from 200 mV to 1.7 V in 10 ns |      | _   | 200 | ns   |

#### Table 19. 8-bit digital to analog converter

| Symbol              | Parameter                    | Test conditions | Min | Тур   | Max | Unit |

|---------------------|------------------------------|-----------------|-----|-------|-----|------|

| VLSB <sub>DAC</sub> | Less significant bit voltage |                 | 1   | 4.851 | 1   | mV   |

Table 20. S<sub>1</sub> protections and diagnostic

| Symbol                     | Parameter                                       | Test conditions                                                 | Min                             | Тур                  | Max                             | Unit |

|----------------------------|-------------------------------------------------|-----------------------------------------------------------------|---------------------------------|----------------------|---------------------------------|------|

| T <sub>TW</sub>            | Thermal warning threshold junction temperature  | S <sub>1</sub> = ON                                             | 130                             |                      |                                 | °C   |

| T <sub>TSD</sub>           | Thermal shutdown threshold junction temperature | S <sub>1</sub> = ON                                             | 155                             | 175                  |                                 | °C   |

| T <sub>TR</sub>            | Thermal reset threshold junction temperature    | S <sub>1</sub> = ON                                             | 130                             |                      |                                 | °C   |

| I <sub>SHORT</sub>         | Over current detection                          | S <sub>1</sub> = ON                                             | 15                              |                      |                                 | Α    |

|                            |                                                 | S <sub>1</sub> = ON;<br>I <sub>PEAK</sub> = 3.2 A               | 0.2 *<br>(I <sub>PEAK</sub> /4) | I <sub>PEAK</sub> /4 | 1.2 *<br>(I <sub>PEAK</sub> /4) | Α    |

| I <sub>OL</sub>            | Open-load<br>detection                          | S <sub>1</sub> = ON; I <sub>PEAK</sub> = 5 A                    | 0.4 *<br>(I <sub>PEAK</sub> /4) | I <sub>PEAK</sub> /4 | 1.2 *<br>(I <sub>PEAK</sub> /4) | Α    |

|                            |                                                 | S <sub>1</sub> = ON; I <sub>PEAK</sub> ≥ 8 A                    | 0.7 *<br>(I <sub>PEAK</sub> /4) | I <sub>PEAK</sub> /4 | 1.3 *<br>(I <sub>PEAK</sub> /4) | Α    |

| V <sub>FAULT_</sub> OUT    | Status output voltage                           | Diagnostic output<br>active (low);<br>I <sub>FAULT</sub> = 1 mA |                                 |                      | 0.9                             | V    |

|                            | Clamp diagnostic                                | I <sub>CLAMPFLAG</sub> = 100 μA                                 |                                 |                      | 0.1                             | V    |

| V <sub>CLAMPFLAG_OUT</sub> | pin output voltage                              | I <sub>CLAMPFLAG</sub> = -100μA                                 | V <sub>DDL</sub> - 0.1          |                      |                                 | V    |

|                            | MAINT_IPK                                       | I <sub>MAINTIPK</sub> = 100 μA                                  |                                 |                      | 0.1                             | V    |

| V <sub>MAINTIPK</sub> OUT  | diagnostic pin voltage                          | I <sub>MAINTIPK</sub> = -100 μA                                 | V <sub>DDL</sub> - 0.1          |                      |                                 | V    |

Table 21. Application registers range

| Symbol                    | Parameter  | Test conditions                                            | Min | Тур | Max   | Unit |

|---------------------------|------------|------------------------------------------------------------|-----|-----|-------|------|

| I <sub>PEAK</sub>         | Register A | Application useful range = 2 → 14 A                        | 0   | 3.2 | 20.55 | Α    |

| I <sub>HOLD</sub>         | Register E | Application useful range = $0.5 \rightarrow 3 \text{ A}$   |     |     | 4.11  | Α    |

| I <sub>HOLD_TEMP</sub>    | Register F | Application useful range = $0.5 \rightarrow 3.5 \text{ A}$ | 0   | 2   | 4.11  | Α    |

| t <sub>PEAK</sub>         | Register B |                                                            | 0   | 1.6 | 5     | ms   |

| t <sub>HOLD_TEMP</sub>    | Register G |                                                            | 0   | 0   | 5     | ms   |

| t <sub>NO_PEAK_MAX</sub>  | Register H |                                                            | 0   | 2.5 | 10    | ms   |

| t                         | Register C | DEMAG MODE = 0 (slow)                                      | 0   |     | 10    | ms   |

| <sup>t</sup> PEAK_TO_HOLD | register 0 | DEMAG MODE = 1 (fast)                                      | 0   | 70  | 500   | μs   |

Table 22. IPEAK, IHOLD (-40  $^{\circ}$ C < T $_{\rm j}$  < 150  $^{\circ}$ C, unless otherwise specified)

| Symbol             | Parameter      | Test conditions <sup>(1)</sup> | Min   | Тур | Max   | Unit |

|--------------------|----------------|--------------------------------|-------|-----|-------|------|

|                    |                | RegisterA = IDEFAULT           | 2.72  | 3.2 | 3.7   | Α    |

|                    |                | RegisterA = 2 A                | 1.60  | 2   | 2.40  | Α    |

|                    |                | T = 125°C; RegisterA = 2 A     | 1.70  | 2   | 2.30  | Α    |

| I <sub>PEAK</sub>  | Peak current   | RegisterA = 5 A                | 4.25  | 5   | 5.75  | Α    |

|                    |                | RegisterA = 8 A                | 6.8   | 8   | 9.2   | Α    |

|                    |                | T = 125°C; RegisterA = 14 A    | 12.6  | 14  | 15.4  | Α    |

|                    |                | RegisterA = 14 A               | 11.9  | 14  | 16.1  | Α    |

|                    |                | RegisterE = IDEFAULT           | 1.445 | 1.7 | 1.955 | Α    |

|                    |                | T = 125°C; RegisterE = 0.5 A   | 0.325 | 0.5 | 0.6   | Α    |

| I <sub>HOLD</sub>  | Hold current   | T = 125°C; RegisterE = 1 A     | 0.9   | 1   | 1.1   | Α    |

|                    |                | RegisterE = 1 A                | 0.85  | 1   | 1.15  | Α    |

|                    |                | RegisterE = 3 A                | 2.55  | 3   | 3.45  | Α    |

| F <sub>PWM</sub>   | PWM frequency  | Design guaranteed              | 10    | 20  |       | KHz  |

| D <sub>CYCLE</sub> | PWM duty cycle | F <sub>PWM</sub> = 20 KHz      | 0.15  |     |       | -    |

<sup>1.</sup> V<sub>BATT</sub> > 8 V

Table 23. Charge pump

| Symbol             | Parameter                                                             | Test conditions                                                                        | Min                      | Тур                      | Max                       | Unit |

|--------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------|--------------------------|---------------------------|------|

| V <sub>CP</sub>    | Charge pump output voltage <sup>(1)</sup>                             | I <sub>CP</sub> = 200 μA                                                               | V <sub>BATT</sub><br>+ 7 | V <sub>BATT</sub><br>+ 9 | V <sub>BATT</sub><br>+ 13 | ٧    |

| C <sub>PUMP1</sub> | External charge pump capacitor                                        |                                                                                        |                          | 4.7                      |                           | nF   |

| C <sub>PUMP2</sub> | External charge pump capacitor                                        |                                                                                        |                          | 4.7                      |                           | nF   |

| C <sub>TANK</sub>  | External charge pump capacitor for S <sub>2</sub> driver peak current |                                                                                        |                          | 100                      |                           | nF   |

| I <sub>CP1</sub>   | Charge pump output current positive                                   | V <sub>BATT</sub> + 7 V < V <sub>CTAK</sub><br>< V <sub>BATT</sub> + 13 V test<br>mode | 15                       | 27                       | 34                        | mA   |

| I <sub>CP2</sub>   | Charge pump output current negative                                   | V <sub>BATT</sub> + 7 V < V <sub>CTAK</sub><br>< V <sub>BATT</sub> + 13 V test<br>mode | -140                     | -100                     | -55                       | mA   |

Guaranteed by design using suggested external network: C<sub>PUMP1</sub>, C<sub>PUMP2</sub>: 4.7 nF - 50 V ceramic capacitors; C<sub>TANK</sub>: 100 nF - 50 V ceramic capacitor; Charge pump diodes: BAT41 type

34/46 DocID022573 Rev. 3

Table 24. I<sup>2</sup>C-bus SDA, SCL I/O stages

| Symbol           | Parameter                                                                  | Test conditions                                                  | Min             | Тур | Max            | Unit |

|------------------|----------------------------------------------------------------------------|------------------------------------------------------------------|-----------------|-----|----------------|------|

| V <sub>IL</sub>  | Low level input voltage                                                    |                                                                  |                 | _   | 0.3 *<br>VC3V3 | V    |

| V <sub>IH</sub>  | High level input voltage                                                   |                                                                  | 0.7 *<br>VC3V3  | _   |                | V    |

| V <sub>HYS</sub> | Hysteresis of Schmitt trigger inputs                                       |                                                                  | 0.05 *<br>VC3V3 | _   |                | V    |

| V <sub>OL</sub>  | Low level output voltage                                                   | I <sub>SINK</sub> = 3 mA                                         |                 | _   | 0.4            | V    |

| I <sub>OL</sub>  | Low level output current                                                   | V <sub>OL</sub> = 0.4 V                                          | 3               | _   |                | mA   |

| t <sub>OFF</sub> | Output fall time from V <sub>IHmim</sub> to V <sub>ILmax</sub>             |                                                                  |                 | _   | 250            | ns   |

| t <sub>SP</sub>  | Pulse width of spikes<br>that must be<br>suppressed by the<br>input filter |                                                                  |                 | _   | 50             | ns   |

| Ii               | Input current                                                              | 0.1 * V <sub>DDL</sub> < V <sub>I</sub> < 0.9 * V <sub>DDL</sub> | -10             | _   | 10             | μΑ   |

| C <sub>i</sub>   | I/O pin capacitance                                                        |                                                                  |                 | _   | 10             | pF   |

## Table 25. I<sup>2</sup>C-bus SDA, SCL bus lines characteristics <sup>(1)</sup>

| Symbol              | Parameter                                        | Test conditions                                      | Min                | Тур | Max  | Unit |

|---------------------|--------------------------------------------------|------------------------------------------------------|--------------------|-----|------|------|

| f <sub>SCL</sub>    | SCL clock frequency                              |                                                      |                    | _   | 100  | kHz  |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition             | After this period the first clock pulse is generated | 4.0                |     |      | μs   |

| t <sub>LOW</sub>    | LOW period of the SCL clock                      |                                                      | 4.7                | _   |      | μs   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                     |                                                      | 4.0                | _   |      | μs   |

| t <sub>SU;STA</sub> | Set-up time for a repeated START condition       |                                                      | 4.7                | _   |      | μs   |

| t <sub>HD;DAT</sub> | Data hold time <sup>(2)</sup>                    |                                                      | 300 <sup>(3)</sup> | —   | (4)  | ns   |

| t <sub>SU;DAT</sub> | Data set-up time                                 |                                                      | 250                | _   |      | ns   |

| t <sub>r</sub>      | Rise time of both SDA and SCL signals            |                                                      |                    |     | 1000 | ns   |