### Watchdog timer circuit

Datasheet - production data

### **Applications**

- Telecommunications

- Alarm systems

- Industrial equipment

- Networking

- Medical equipment

- UPS (uninterruptible power supply)

#### **Features**

- Current consumption 13 μA typ.

- Available watchdog timeout periods are 3.4 ms, 6.3 ms, 102 ms and 1.6 s

- · Chip enable input

- Open drain or push-pull WDO output

- Operating temperature range: –40 to +125 °C

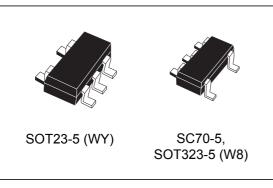

- Package SOT23-5, SC70-5 (SOT323-5)

- ESD performanceHBM: 2000 VRCDM: 1000 V

Table 1. Device summary

|                               |                   | no ii Bovioo oaiiiinary     |               |                    |

|-------------------------------|-------------------|-----------------------------|---------------|--------------------|

| Order code                    | Temperature range | Package                     | Packing       | Topside<br>marking |

| STWD100NWWY3F                 | -40/+125 °C       | SOT23-5L                    | Tape and reel | WNW                |

| STWD100YNWWY3F <sup>(1)</sup> | -40/+125 °C       | SOT23-5L (automotive grade) | Tape and reel | WYNW               |

| STWD100NYWY3F                 | -40/+125 °C       | SOT23-5L                    | Tape and reel | WNY                |

| STWD100YNYWY3F <sup>(1)</sup> | -40/+125 °C       | SOT23-5L(automotivegrade)   | Tape and reel | WYNY               |

| STWD100NPWY3F                 | -40/+125 °C       | SOT23-5L                    | Tape and reel | WNP                |

| STWD100YNPWY3F <sup>(1)</sup> | -40/+125 °C       | SOT23-5L(automotivegrade)   | Tape and reel | WYNP               |

| STWD100PYW83F                 | -40/+125 °C       | SOT323-5L                   | Tape and reel | WPY                |

Qualification and characterization according to AEC Q100 and Q003 or equivalent, advanced screening according to AEC Q001 and Q002 or equivalent

Contents STWD100

## **Contents**

| 1 | Description                  | 5 |

|---|------------------------------|---|

| 2 | Operation                    | 7 |

|   | 2.1 Watchdog input (WDI)     | 7 |

|   | 2.2 Watchdog output (WDO)    | 7 |

|   | 2.3 Chip enable input (EN)   | 8 |

|   | 2.4 Applications information | 8 |

| 3 | Watchdog timing1             | 0 |

| 4 | Maximum ratings              | 5 |

| 5 | DC and AC parameters         | 6 |

| 6 | Package information          | 8 |

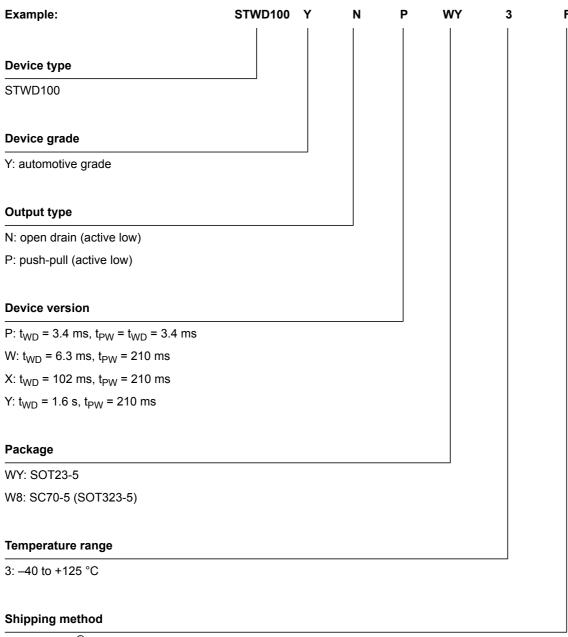

| 7 | Part numbering               | 2 |

| 8 | Package marking information  | 3 |

| 9 | Revision history             | 4 |

STWD100 List of tables

## List of tables

| Table 1.  | Device summary                                                            | 1    |

|-----------|---------------------------------------------------------------------------|------|

| Table 2.  | SOT23-5 and SC70-5 (SOT323-5) pin description                             | 5    |

| Table 3.  | Absolute maximum ratings                                                  |      |

| Table 4.  | Operating and AC measurement conditions                                   | . 16 |

| Table 5.  | DC and AC characteristics                                                 | . 17 |

| Table 6.  | SOT23-5 - 5-lead small outline transistor package mechanical data         | . 19 |

| Table 7.  | SC70 (SOT323-5) – 5-lead small outline transistor package mechanical data | . 21 |

| Table 8.  | Ordering information scheme                                               | . 22 |

| Table 9.  | Device versions with marking descriptions                                 | . 23 |

| Table 10. | Document revision history                                                 | . 24 |

List of figures STWD100

# List of figures

| SOT23-5 and SC70-5 (SOT323-5) package connections                 | . 5                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

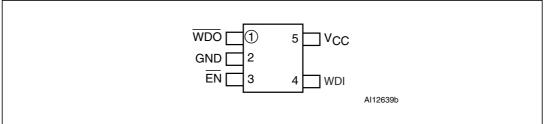

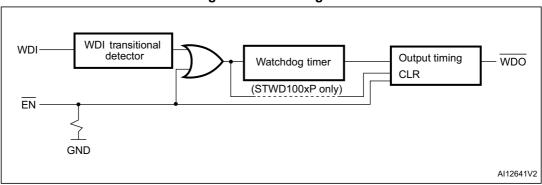

| Logic diagram                                                     | . 6                                                                                                                                                                                                                                                                                                                                                                                                                      |

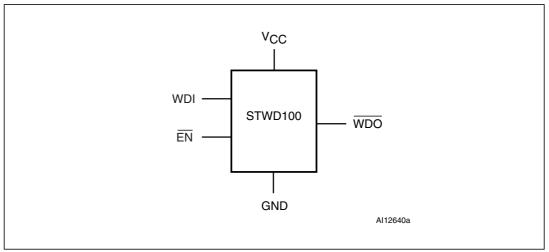

| Block diagram                                                     | . 6                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Open drain WDO output connection                                  | . 8                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Interfacing to microprocessors with bidirectional reset I/O       | . 9                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Power-up                                                          | 10                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Normal triggering                                                 | 11                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Timeout without re-trigger                                        | 12                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Trigger after timeout                                             | 13                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Enable pin, $\overline{\overline{\text{EN}}}$ , triggering        | 14                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SOT23-5 - 5-lead small outline transistor package outline         | 19                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SC70 (SOT323-5) - 5-lead small outline transistor package outline | 20                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                   | SOT23-5 and SC70-5 (SOT323-5) package connections  Logic diagram  Block diagram  Open drain WDO output connection  Interfacing to microprocessors with bidirectional reset I/O  Power-up  Normal triggering  Timeout without re-trigger  Trigger after timeout  Enable pin, EN, triggering  SOT23-5 - 5-lead small outline transistor package outline  SC70 (SOT323-5) - 5-lead small outline transistor package outline |

STWD100 Description

### 1 Description

The STWD100 watchdog timer circuits are self-contained devices which prevent system failures that are caused by certain types of hardware errors (non-responding peripherals, bus contention, etc.) or software errors (bad code jump, code stuck in loop, etc.).

The STWD100 watchdog timer has an input, WDI, and an output,  $\overline{\text{WDO}}$ . The input is used to clear the internal watchdog timer periodically within the specified timeout period,  $t_{\text{wd}}$ . While the system is operating correctly, it periodically toggles the watchdog input, WDI. If the system fails, the watchdog timer is not reset, a system alert is generated and the watchdog output,  $\overline{\text{WDO}}$ , is asserted.

The STWD100 circuit also has an enable pin,  $\overline{\text{EN}}$ , which can enable or disable the watchdog functionality. The  $\overline{\text{EN}}$  pin is connected to the internal pull-down resistor. The device is enabled if the  $\overline{\text{EN}}$  pin is left floating.

Figure 1. SOT23-5 and SC70-5 (SOT323-5) package connections

Table 2. SOT23-5 and SC70-5 (SOT323-5) pin description

| Pin number | Name              | Description    |  |

|------------|-------------------|----------------|--|

| 1          | WDO Watchdog outp |                |  |

| 2          | GND               | Ground         |  |

| 3          | ĒN                | Enable pin     |  |

| 4          | WDI               | Watchdog input |  |

| 5          | V <sub>CC</sub>   | Supply voltage |  |

Description STWD100

Figure 2. Logic diagram

Note: WDO output is available in open drain or push-pull configuration.

Figure 3. Block diagram

Note: Positive pulse on enable pin  $\overline{EN}$  longer than 1  $\mu$ s resets the watchdog timer.

STWD100 Operation

### 2 Operation

The STWD100 device is used to detect an out-of-control MCU. The user has to ensure watchdog reset within the watchdog timeout period, otherwise the watchdog output is asserted and MCU is restarted. The STWD100 can be also enabled or disabled by the chip enable pin.

#### 2.1 Watchdog input (WDI)

The WDI input has to be toggled within the watchdog timeout period,  $t_{WD}$ , otherwise the watchdog output,  $\overline{WDO}$ , is asserted. The internal watchdog timer, which counts the  $t_{WD}$  period, is cleared either:

- 1. by a transition on watchdog output, WDO (see Figure 8 on page 12) or

- 2. by a pulse on enable pin,  $\overline{\text{EN}}$  (see *Figure 10 on page 14*) or

- 3. by toggling WDI input (low-to-high on all versions and high-to-low on STWD100xW, STWD100xX and STWD100xY only).

The pulses on WDI input with a duration of at least 1  $\mu$ s are detected and glitches shorter than 100 ns are ignored.

If WDI is permanently tied high or low and  $\overline{\text{EN}}$  is tied low, the  $\overline{\text{WDO}}$  toggles every 3.4 ms (t<sub>WD</sub>) on STWD100xP and every t<sub>WD</sub> and t<sub>PW</sub> on STWD100xW, STWD100xX and STWD100xY (see *Figure 8 on page 12*).

### 2.2 Watchdog output (WDO)

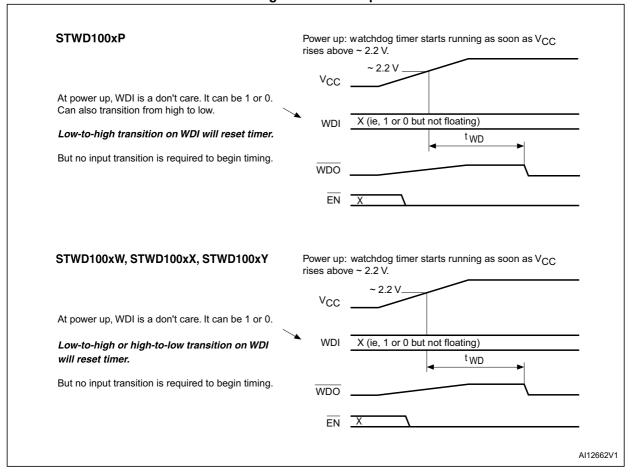

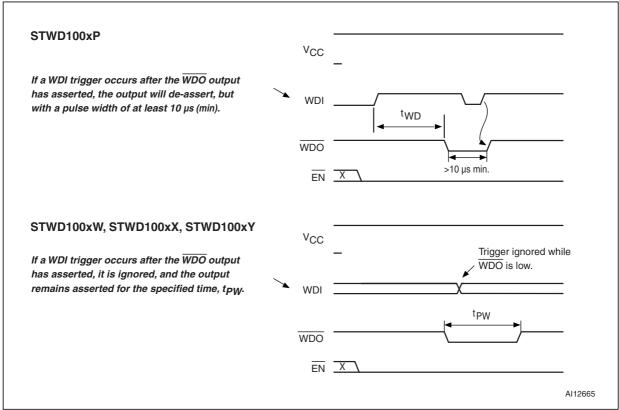

When the  $V_{CC}$  exceeds the timer startup voltage  $V_{START}$  after power-up, the internal watchdog timer starts counting. If the timer is not cleared within the  $t_{WD}$ , the  $\overline{WDO}$  will go low (see *Figure 6*).

After exceeding the  $t_{WD}$ , the  $\overline{WDO}$  is asserted for  $t_{PW}$  on STWD100xW, STWD100xX and STWD100xY regardless of possible WDI transitions (see *Figure 9 on page 13*). On STWD100xP  $\overline{WDO}$  is asserted for a minimum of 10  $\mu$ s and a maximum of  $t_{WD}$  after exceeding the  $t_{WD}$  period (see *Figure 8 on page 12* and *Figure 9 on page 13*).

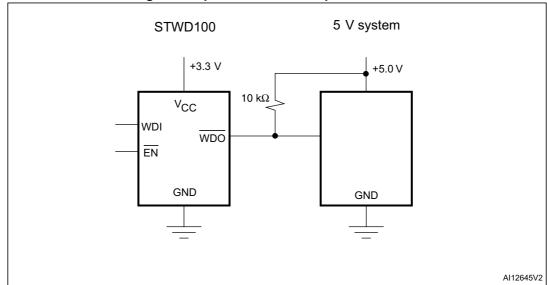

The STWD100 has an active low open drain or push-pull output. An external <u>pull-up</u> resistor connected to any supply voltage up to 6 V is required in case of open drain  $\overline{\text{WDO}}$  output (see *Figure 4*). Select a resistor value large enough to register a logic low, and small enough to register a logic high while supplying all input current and leakage paths connected to the reset output line. A 10 k $\Omega$  pull-up resistor is sufficient in most applications.

Operation STWD100

Figure 4. Open drain WDO output connection

### 2.3 Chip enable input $(\overline{EN})$

All states mentioned in Section 2.1: Watchdog input (WDI) and Section 2.2: Watchdog output (WDO) are valid under the condition that EN is in logical low state.

The behavior of  $\overline{EN}$  is common to all versions (i.e. STWD100xP, STWD100xW, STWD100xX and STWD100xY).

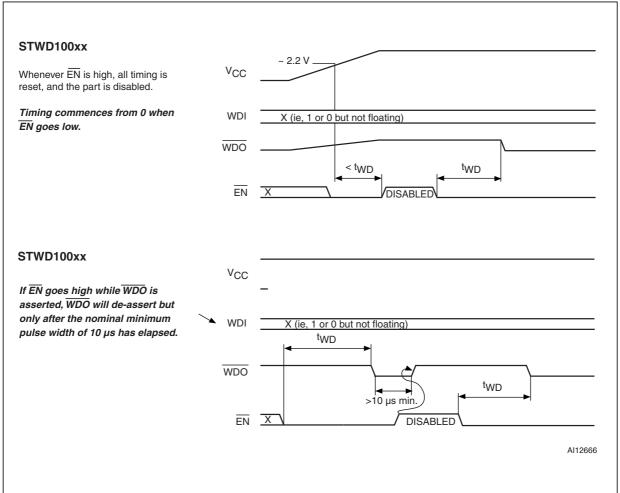

If the  $\overline{EN}$  goes high after power-up in less than  $t_{WD}$  from the moment that  $V_{CC}$  exceeds the timer startup voltage,  $V_{START}$ , the  $\overline{WDO}$  will stay high for the same time period as  $\overline{EN}$ , plus  $t_{WD}$  (see *Figure 10 on page 14*).

If the  $\overline{EN}$  goes high anytime during normal operation, the  $\overline{WDO}$  will go high as well, but the minimum possible  $\overline{WDO}$  pulse width is 10 µs (see *Figure 10 on page 14*).

The pulses on the  $\overline{EN}$  pin with a duration of at least 1 µs are detected and glitches shorter than 100 ns are ignored.

### 2.4 Applications information

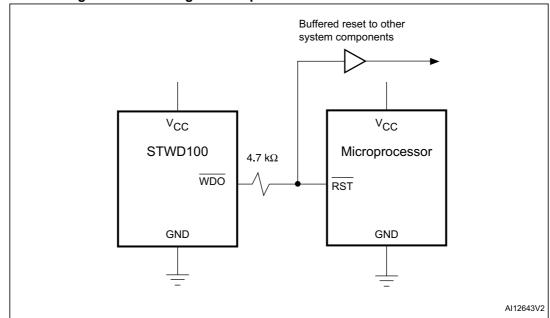

#### Interfacing to microprocessors with bidirectional reset pins

Microprocessors with bidirectional reset pins can contend with the STWD100 watchdog output,  $\overline{WDO}$ . For example, if the  $\overline{WDO}$  output is driven high and the micro wants to pull it low, signal contention will result. To prevent this from occurring, connect a 4.7 k $\Omega$  resistor between the  $\overline{WDO}$  output and the microprocessors reset I/O as in *Figure 5*.

577

STWD100 Operation

Figure 5. Interfacing to microprocessors with bidirectional reset I/O

Watchdog timing STWD100

## 3 Watchdog timing

Figure 6. Power-up

**577**

STWD100 Watchdog timing

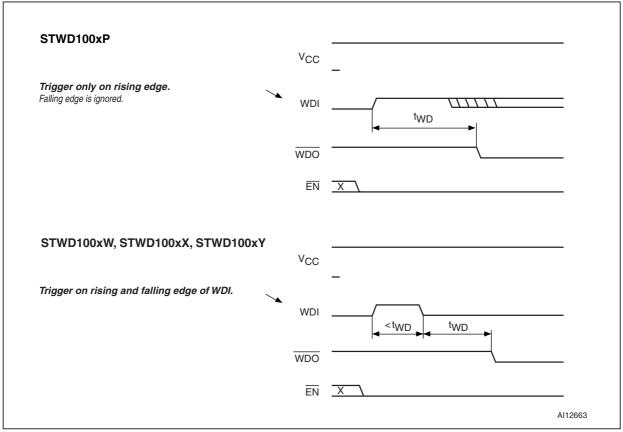

Figure 7. Normal triggering

Watchdog timing STWD100

STWD100xP  $V_{CC}$ After a timeout and  $\overline{WDO}$  is asserted, it will stay low for t<sub>WD</sub> time period, then WDI return high. If no WDI trigger event occurs, WDO will again  $t_{\text{WD}}$  $t_{\text{WD}}$  $t_{\text{WD}}$  $t_{\text{WD}}$  $t_{\text{WD}}$  $t_{WD}$ assert low after  $t_{WD}$  time period. This cycle repeats WDO until a WDI trigger event occurs. ĒΝ STWD100xW, STWD100xX, STWD100xY  $V_{CC}$ After a timeout and  $\overline{WDO}$  is asserted, it will stay low for t<sub>PW</sub> time period, then WDI return high. If no WDI trigger t<sub>PW</sub> tWD  $t_{PW}$ twD  $t_{PW}$ tWD tWD event occurs within t<sub>WD</sub> time period, WDO will again WDO assert low. This cycle repeats until a WDI trigger event EN X occurs while  $\overline{WDO}$  is high. AI12664

Figure 8. Timeout without re-trigger

STWD100 Watchdog timing

Figure 9. Trigger after timeout

Watchdog timing STWD100

Figure 10. Enable pin, EN, triggering

STWD100 Maximum ratings

### 4 Maximum ratings

Stressing the device above the rating listed in *Table 3* may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in *Table 4* of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE program and other relevant quality documents.

Table 3. Absolute maximum ratings

| Symbol                          | Parameter                                 | Value                        | Unit |

|---------------------------------|-------------------------------------------|------------------------------|------|

| T <sub>STG</sub>                | Storage temperature (V <sub>CC</sub> off) | -55 to 150                   | °C   |

| T <sub>SLD</sub> <sup>(1)</sup> | Lead solder temperature for 10 seconds    | 260                          | °C   |

| V <sub>IO</sub>                 | Input or output voltage                   | -0.3 to V <sub>CC</sub> +0.3 | V    |

| V <sub>CC</sub>                 | Supply voltage                            | -0.3 to 7.0                  | V    |

| I <sub>O</sub>                  | Output current                            | 20                           | mA   |

| P <sub>D</sub>                  | Power dissipation                         | 320                          | mW   |

<sup>1.</sup> Reflow at peak temperature of 260 °C (total thermal budget not to exceed 245 °C for greater than 30 seconds).

### 5 DC and AC parameters

This section summarizes the operating measurement conditions, and the DC and AC characteristics of the device. The parameters in *Table 5* that follows, are derived from tests performed under the measurement conditions summarized in *Table 4*. Designers should check that the operating conditions in their circuit match the operating conditions when relying on the quoted parameters.

Table 4. Operating and AC measurement conditions

| Parameter                                       | Value                      | Unit |

|-------------------------------------------------|----------------------------|------|

| V <sub>CC</sub> supply voltage                  | 2.7 to 5.5                 | V    |

| Ambient operating temperature (T <sub>A</sub> ) | -40 to 125                 | °C   |

| Input rise and fall times                       | ≤ 5                        | ns   |

| Input pulse voltages                            | 0.2 to 0.8 V <sub>CC</sub> | V    |

| Input and output timing ref. voltages           | 0.3 to 0.7 V <sub>CC</sub> | V    |

Table 5. DC and AC characteristics

| Symbol                                | Description                          | Test condition <sup>(1)</sup>                              | Min.                | Тур. | Max.                | Unit |

|---------------------------------------|--------------------------------------|------------------------------------------------------------|---------------------|------|---------------------|------|

| V <sub>CC</sub>                       | Operating voltage                    |                                                            | 2.7                 | 5    | 5.5                 | V    |

| I <sub>CC</sub>                       | V <sub>CC</sub> supply current       |                                                            |                     | 13   | 26                  | μA   |

| I <sub>LO</sub>                       | Open drain output leakage current    | From output to the GND or V <sub>CC</sub>                  | -1                  |      | +1                  | μA   |

|                                       | Input leakage current (WDI)          |                                                            | -1                  |      | +1                  | μΑ   |

| V <sub>IH</sub>                       | Input high voltage (WDI, EN)         |                                                            | 0.7 V <sub>CC</sub> |      |                     | V    |

| V <sub>IL</sub>                       | Input low voltage (WDI, EN)          |                                                            |                     |      | 0.3 V <sub>CC</sub> | V    |

| V                                     | Output low voltage (WDO)             | $V_{CC} \ge 2.7 \text{ V, I}_{SINK} = 1.2 \text{ mA}$      |                     |      | 0.3                 | V    |

| V <sub>OL</sub>                       | Output low voltage (VVDO)            | V <sub>CC</sub> ≥ 4.5 V, I <sub>SINK</sub> = 3.2 mA        |                     |      | 0.4                 | V    |

| \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | Output high voltage (WDO) (push-pull | $V_{CC} \ge 2.7 \text{ V, } I_{SOURCE} = 500  \mu\text{A}$ | 0.8 V <sub>CC</sub> |      |                     | V    |

| V <sub>OH</sub>                       | only)                                | V <sub>CC</sub> ≥ 4.5 V, I <sub>SOURCE</sub> = 800 μA      | 0.8 V <sub>CC</sub> |      |                     | V    |

| Enable p                              | in (EN)                              |                                                            |                     |      |                     |      |

|                                       | EN input pulse width                 |                                                            | 1                   |      |                     | μs   |

|                                       | EN glitch rejection                  |                                                            |                     | 100  |                     | ns   |

|                                       | EN-to-WDO delay <sup>(2)</sup>       |                                                            |                     | 200  |                     | ns   |

|                                       | EN pull-down resistance              |                                                            | 32                  | 63   | 100                 | kΩ   |

| Watchdo                               | g timer                              |                                                            | '                   |      | '                   |      |

| V <sub>START</sub>                    | Timer startup voltage                |                                                            | 1.9                 | 2.2  | 2.7                 | V    |

|                                       |                                      | STWD100xP                                                  | 2.3                 | 3.4  | 4.6                 | ms   |

|                                       |                                      | STWD100xW                                                  | 4.3                 | 6.3  | 8.6                 | ms   |

| t <sub>WD</sub>                       | Watchdog timeout period              | STWD100YxW                                                 | 5.1                 | 6.3  | 8.6                 | ms   |

|                                       |                                      | STWD100xX                                                  | 71                  | 102  | 142                 | ms   |

|                                       |                                      | STWD100xY                                                  | 1.12                | 1.6  | 2.24                | s    |

| t <sub>PW</sub>                       | Watchdog active time                 |                                                            | 140                 | 210  | 280                 | ms   |

|                                       | WDI-to-WDO delay <sup>(3)</sup>      |                                                            |                     | 150  |                     | ns   |

|                                       | WDI pulse width                      |                                                            | 1                   |      |                     | μs   |

|                                       | WDI glitch rejection                 |                                                            |                     | 100  |                     | ns   |

|                                       |                                      |                                                            |                     |      |                     |      |

<sup>1.</sup> Valid for ambient operating temperature:  $T_A = -40$  to 125 °C;  $V_{CC} = 2.7$  V to 5.5 V except where noted.

<sup>2.</sup>  $\overline{WDO}$  will assert for minimum of 10  $\mu s$  even if  $\overline{EN}$  transitions high.

<sup>3.</sup>  $\overline{WDO}$  will assert for minimum of 10  $\mu s$  regardless of transition on WDI (valid for STWD100xP only).

Package information STWD100

## 6 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: <a href="www.st.com">www.st.com</a>. ECOPACK is an ST trademark.

The maximum ratings related to soldering conditions are also marked on the inner box label.

18/25 DocID014134 Rev 8

STWD100 Package information

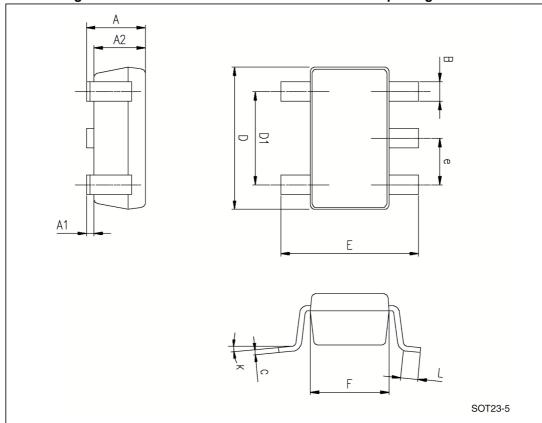

Figure 11. SOT23-5 - 5-lead small outline transistor package outline

Table 6. SOT23-5 - 5-lead small outline transistor package mechanical data

|        | Dimensions |      |      |       |        |       |

|--------|------------|------|------|-------|--------|-------|

| Symbol |            | mm   |      |       | inches |       |

|        | Тур.       | Min. | Max. | Тур.  | Min.   | Max.  |

| А      | 1.20       | 0.90 | 1.45 | 0.047 | 0.035  | 0.057 |

| A1     |            |      | 0.15 |       |        | 0.006 |

| A2     | 1.05       | 0.90 | 1.30 | 0.041 | 0.035  | 0.051 |

| В      | 0.40       | 0.35 | 0.50 | 0.016 | 0.014  | 0.020 |

| С      | 0.15       | 0.09 | 0.20 | 0.006 | 0.004  | 0.008 |

| D      | 2.90       | 2.80 | 3.00 | 0.114 | 0.110  | 0.118 |

| D1     | 1.90       |      |      | 0.075 |        |       |

| Е      | 2.80       | 2.60 | 3.00 | 0.110 | 0.102  | 0.118 |

| е      | 0.95       |      |      | 0.037 |        |       |

| F      | 1.60       | 1.50 | 1.75 | 0.063 | 0.059  | 0.069 |

| K      |            | 0°   | 10°  |       | 0°     | 10°   |

| L      | 0.35       | 0.10 | 0.60 | 0.014 | 0.004  | 0.024 |

Package information STWD100

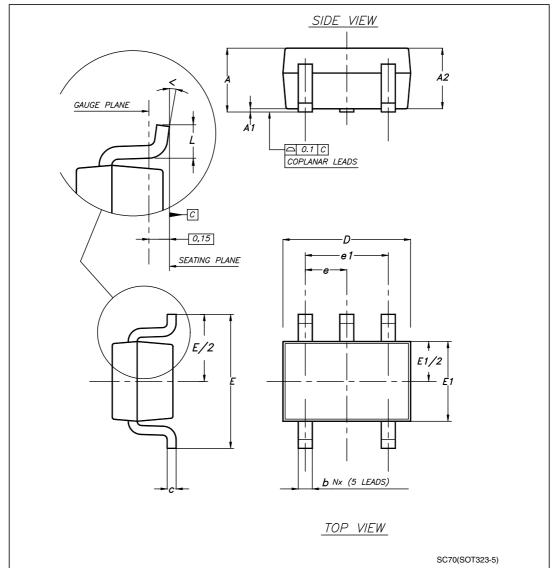

Figure 12. SC70 (SOT323-5) - 5-lead small outline transistor package outline

STWD100 Package information

Table 7. SC70 (SOT323-5) - 5-lead small outline transistor package mechanical data

|        |      | -    | Dimer | nsions |        |       |

|--------|------|------|-------|--------|--------|-------|

| Symbol |      | mm   |       |        | inches |       |

|        | Тур. | Min. | Max.  | Тур.   | Min.   | Max.  |

| Α      |      | 0.80 | 1.10  |        | 0.031  | 0.043 |

| A1     |      | 0.00 | 0.10  |        | 0.000  | 0.004 |

| A2     | 0.90 | 0.80 | 1.00  | 0.035  | 0.031  | 0.039 |

| b      |      | 0.15 | 0.30  |        | 0.006  | 0.012 |

| С      |      | 0.10 | 0.22  |        | 0.004  | 0.009 |

| D      | 2.00 | 1.80 | 2.20  | 0.079  | 0.071  | 0.087 |

| E      | 2.10 | 1.80 | 2.40  | 0.083  | 0.071  | 0.094 |

| E1     | 1.25 | 1.15 | 1.35  | 0.049  | 0.045  | 0.053 |

| е      | 0.65 |      |       | 0.026  |        |       |

| e1     | 1.30 |      |       | 0.051  |        |       |

| L      | 0.36 | 0.26 | 0.46  | 0.014  | 0.010  | 0.018 |

| <      | _    | 0°   | 8°    | _      | 0°     | 8°    |

| N      |      | 5    | •     |        | 5      |       |

Part numbering STWD100

## 7 Part numbering

Table 8. Ordering information scheme

F: ECOPACK® package, tape and reel

Note: Please check device version availability on www.st.com.

Please contact local ST sales office for new device version request.

# 8 Package marking information

Table 9. Device versions with marking descriptions

| Part number   |                                 | hdog<br>period | Output configuration | Topside marking | Bottomside<br>marking <sup>(1)</sup> |  |

|---------------|---------------------------------|----------------|----------------------|-----------------|--------------------------------------|--|

|               | t <sub>wd</sub> t <sub>pw</sub> |                |                      |                 | marking. /                           |  |

| STWD100NPxxxx | 3.4 ms                          | 3.4 ms         | Open drain           | WNP             | PYWW                                 |  |

| STWD100NWxxxx | 6.3 ms                          | 210 ms         | Open drain           | WNW             | PYWW                                 |  |

| STWD100NXxxxx | 102 ms                          | 210 ms         | Open drain           | WNX             | PYWW                                 |  |

| STWD100NYxxxx | 1.6 s                           | 210 ms         | Open drain           | WNY             | PYWW                                 |  |

| STWD100PWxxxx | 6.3 ms                          | 210 ms         | Push-pull            | WPW             | PYWW                                 |  |

| STWD100PXxxxx | 102 ms                          | 210 ms         | Push-pull            | WPX             | PYWW                                 |  |

| STWD100PYxxxx | 1.6 s                           | 210 ms         | Push-pull            | WPY             | PYWW                                 |  |

<sup>1.</sup> Description: P = assembly plant code, Y = assembly year (0 to 9), WW = assembly work week (01 to 52).

Revision history STWD100

# 9 Revision history

Table 10. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                   |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08-Nov-2007 | 1        | Initial release.                                                                                                                                                                                                                                                          |

| 23-Jan-2008 | 2        | Updated cover page and <i>Table 5</i> ; document status upgraded to full datasheet.                                                                                                                                                                                       |

| 28-Jan-2008 | 3        | Updated cover page.                                                                                                                                                                                                                                                       |

| 17-Mar-2008 | 4        | Updated cover page, Figure 4, 7, 9, and Table 5, 9.                                                                                                                                                                                                                       |

| 31-Jul-2008 | 5        | Updated Features on cover page and Table 5.                                                                                                                                                                                                                               |

| 05-Mar-2012 | 6        | Added product maturity information and section <i>Applications</i> , updated <i>Section 1</i> , <i>Section 2.4</i> , <i>Section 4</i> , <i>Section 5</i> , <i>Section 7</i> and <i>Section 8</i> , ECOPACK <sup>®</sup> text, minor text corrections throughout document. |

| 26-Oct-2012 | 7        | Updated Features (added ESD information). Added Table 1: Device summary. Updated Table 8 (added automotive grade version to the device type). Minor corrections throughout document.                                                                                      |

| 11-Mar-2014 | 8        | Updated <i>Table 1: Device summary</i> and <i>Table 8: Ordering information scheme</i> Added STWD100YxW and values to t <sub>WD</sub> in <i>Table 5: DC and AC characteristics</i>                                                                                        |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2014 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com