# **TW Type High Precision**

# 5.0 x 3.2 mm SMD Voltage Controlled Temperature Compensated Crystal Oscillator

### **FEATURE**

- Typical 5.0 x 3.2 x 1.55 mm ceramic SMD package.

- $\pm 0.28$ ppm,  $-40^{\circ}$ C $\sim +85^{\circ}$ C;  $\pm 0.05$ ppm,  $-10^{\circ}$ C $\sim +70^{\circ}$ C

- CMOS and Clipped Sine wave (without DC-cut capacitor) output optional.

### TYPICAL APPLICATION

- Base Stations, Stratum 3

- Femtocell

**RoHS Compliant**

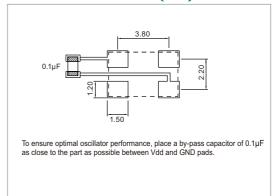

# **DIMENSION (mm)**

## **SOLDER PAD LAYOUT (mm)**

#### **ELECTRICAL SPECIFICATION**

| Parameter                                   | 5.0 V                                |                                      | 3.3V          |        | Unit   |  |

|---------------------------------------------|--------------------------------------|--------------------------------------|---------------|--------|--------|--|

| i didilietei                                | Min.                                 | Max.                                 | Min.          | Max.   |        |  |

| Supply Voltage Variation (VDD)              | VDD-5%                               | VDD+5%                               | VDD-5%        | VDD+5% | V      |  |

| Frequency Range                             | 10                                   | 52                                   | 10            | 52     |        |  |

| Standard Frequency (for CMOS)               | 10, 12.8,13, 19.2, 20, 25, 26, 30.72 |                                      |               |        | MHz    |  |

| Standard Frequency (for Clipped Sine Wave)  |                                      | 10, 12.8,13, 19.2, 20, 25, 26, 30.72 |               |        |        |  |

| Frequency Tolerance*                        | -                                    | ±2.0                                 | -             | ±2.0   | ppm    |  |

| Frequency Stability                         |                                      |                                      |               |        |        |  |

| Vs Supply Voltage (±5%) change              | _                                    | ±0.3                                 | -             | ±0.3   | ppm    |  |

| Vs Load (±10%) change                       | -                                    | ±0.2                                 | -             | ±0.2   |        |  |

| Vs Aging (@1st year)                        | -                                    | ±1.0                                 | -             | ±1.0   |        |  |

| Supply Current (CMOS output)                |                                      |                                      |               |        |        |  |

| 10 MHz≧Fo ≧40 MHz                           | _                                    | 6                                    | -             | 6      |        |  |

| 40 MHz>Fo≧52 MHz                            | _                                    | 8                                    | -             | 8      | mA     |  |

| Supply Current (Clipped Sine Wave)          | -                                    | 3.5                                  | _             | 3.5    |        |  |

| Output Level (CMOS) Output High (Logic "1") | 90%VDD                               | -                                    | 90%VDD        | _      | V      |  |

| Output Low (Logic "0")                      | _                                    | 10%VDD                               | -             | 10%VDD | v      |  |

| Duty                                        | 45                                   | 55                                   | 45            | 55     | %      |  |

| Output Level (Clipped Sine Wave)            | 0.8                                  | -                                    | 0.8           | _      | Vp-p   |  |

| Load (CMOS)                                 | 15pF                                 |                                      | 15pF          |        |        |  |

| Load (Clipped Sine Wave)                    | 10 KΩ // 10pF                        |                                      | 10 KΩ // 10pF |        |        |  |

| Control Voltage Range (VCTCXO)              | 0.5                                  | 2.5                                  | 0.5           | 2.5    | V      |  |

| Pulling Range (VCTCXO)                      | ±5.0                                 | -                                    | ±5.0          | _      | ppm    |  |

| Vc Input Impedance (VCTCXO)                 | 100                                  | _                                    | 100           | _      | kΩ     |  |

| Phase Noise @ 10 MHz 100 Hz                 | -125                                 |                                      | -125          |        |        |  |

| 1 kHz                                       | -14                                  | 45 -14                               |               | 45     | dBc/Hz |  |

| 10 kHz                                      | -15                                  | 50                                   | -150          |        |        |  |

| Start time                                  | -                                    | 2                                    | -             | 2      | mSec   |  |

| Storage Temp. Range                         | -55                                  | 125                                  | -55           | 125    | °C     |  |

Standard frequencies are frequencies which the crystal has been designed and does not imply a stock position. \*Frequency at 25°C, 1 hour after reflow.

### Frequency Stability vs. Temperature Range

| Temp. (°C) | ±0.05 | ±0.1 | ±0.2 | ±0.28 | ±0.5 |

|------------|-------|------|------|-------|------|

| -10 ~ +70  | 0     | 0    | 0    | 0     | 0    |

| -20 ~ +70  | ×     | 0    | 0    | 0     | 0    |

| -40 ~ +85  | ×     | X    | Δ    | 0     | 0    |

\* ○: Available △:Conditional X: Not available

Note: not all combination of options are available. Other specifications may be available upon request.