- Dual Issue, 32-bit CPU Core Complex (e200z7)

- Compliant with the Power Architecture® Embedded Category

- 16 KB I-Cache and 16 KB D-Cache

- Includes an Instruction Set Enhancement Allowing Variable Length Encoding (VLE), Optional Encoding of Mixed 16-bit and 32-bit Instructions, for Code Size Footprint Reduction

- Includes Signal Processing Extension (SPE2) Instruction Support for Digital Signal Processing (DSP) and Single-Precision Floating Point Operations

- 4 MB On-Chip Flash

- Supports Read During Program and Erase Operations, and Multiple Blocks Allowing EEPROM Emulation

- 256 KB On-Chip General-Purpose SRAM Including 32 KB of Standby RAM

- Two Direct Memory Access Controller (eDMA2) Blocks

- One Supporting 64 Channels

- One Supporting 32 Channels

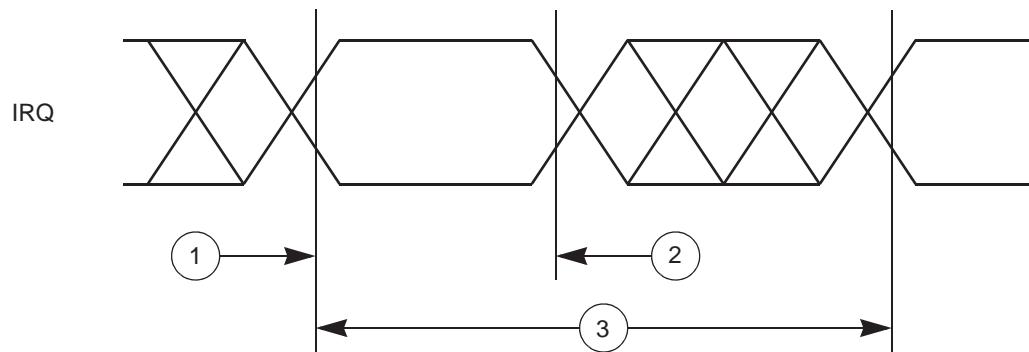

- Interrupt Controller (INTC)

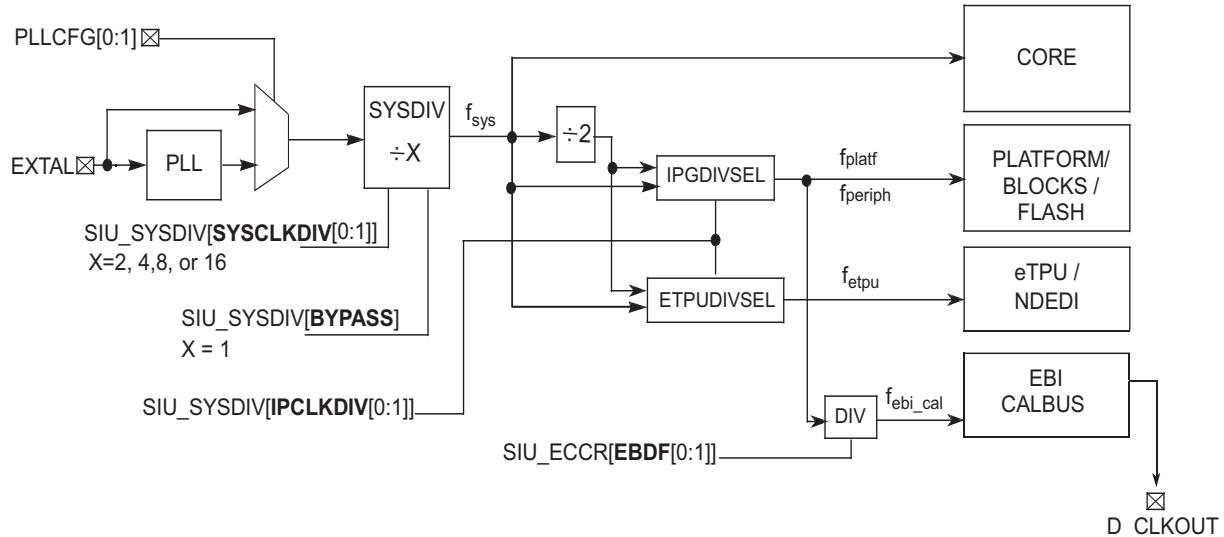

- Frequency Modulated Phase-Locked loop (FMPPLL)

- Crossbar Switch Architecture for Concurrent Access to Peripherals, Flash, or RAM from Multiple Bus Masters

- External Bus Interface (EBI) for Calibration and Application Development (not Available on all Packages)

- System Integration Unit (SIU)

- Error Correction Status Module (ECSM)

- Boot Assist Module (BAM) Supports Serial Bootload Via CAN or SCI

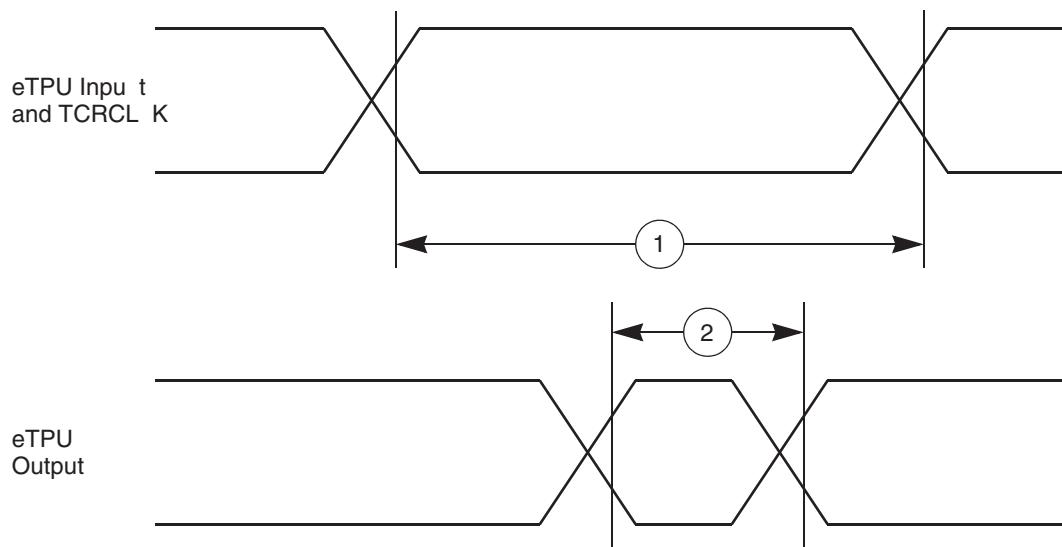

- Two Second-Generation Enhanced Time Processor Units (eTPU2) That Share Code and Data RAM

- 32 Standard Channels per eTPU2

- 24 KB Code RAM

- 6 KB Parameter (data) RAM

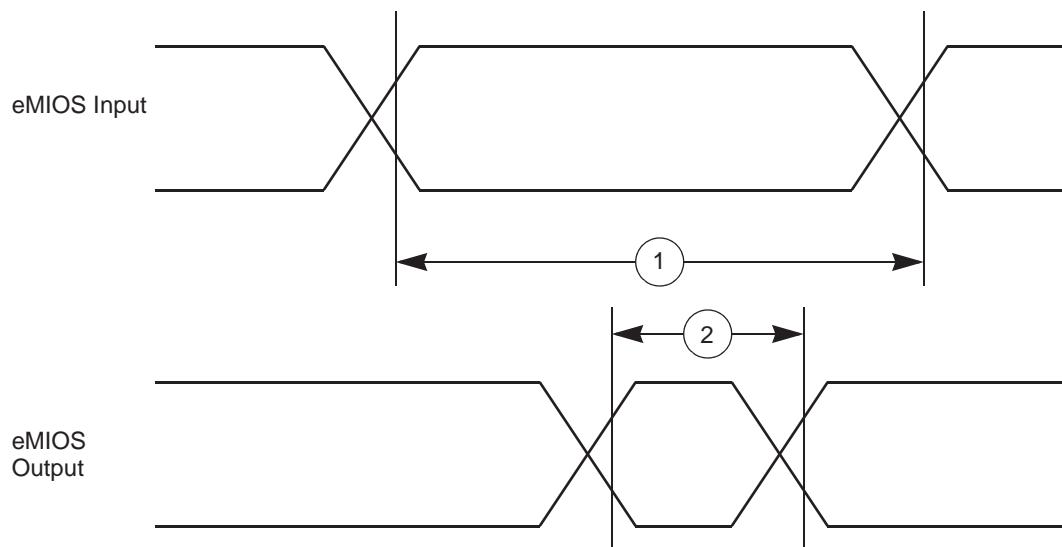

- Enhanced Modular Input Output System Supporting 32 Unified Channels (eMIOS) with Each Channel Capable of Single Action, Double Action, Pulse width Modulation (PWM) and Modulus Counter Operation

- Four Enhanced Queued Analog-to-Digital Converters (eQADC)

- Support for 64 Analog Channels

- Includes One Absolute Reference ADC Channel

- Includes Eight Decimation Filters

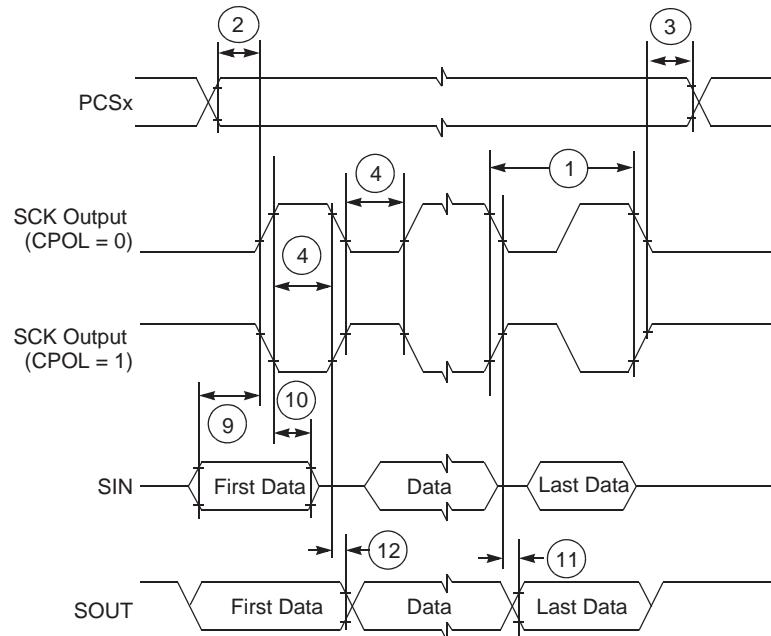

- Four Deserial Serial Peripheral Interface (DSPI) modules

- Three Enhanced Serial Communication Interface (eSCI)

- Modules

- Four Controller Area Network (FlexCAN) Modules

- Dual-Channel FlexRay Controller

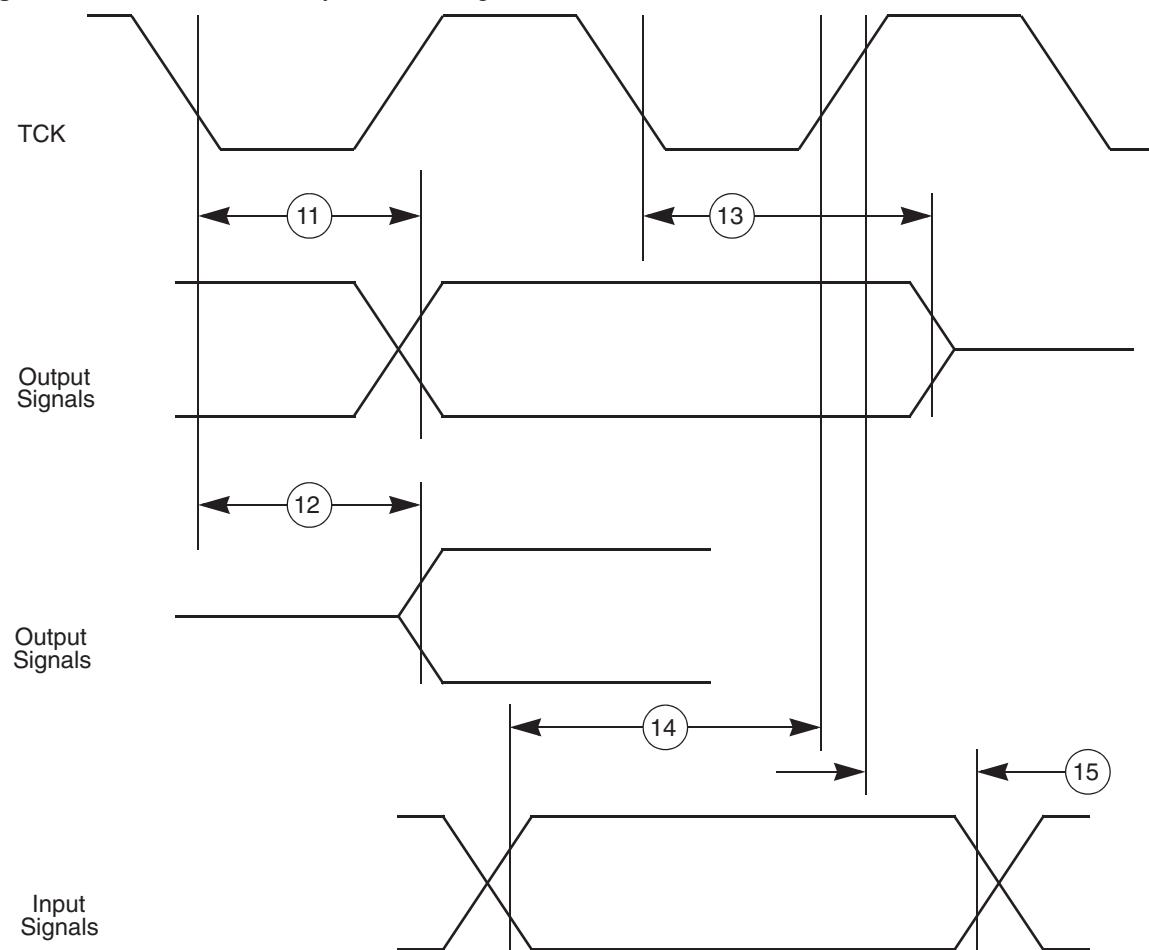

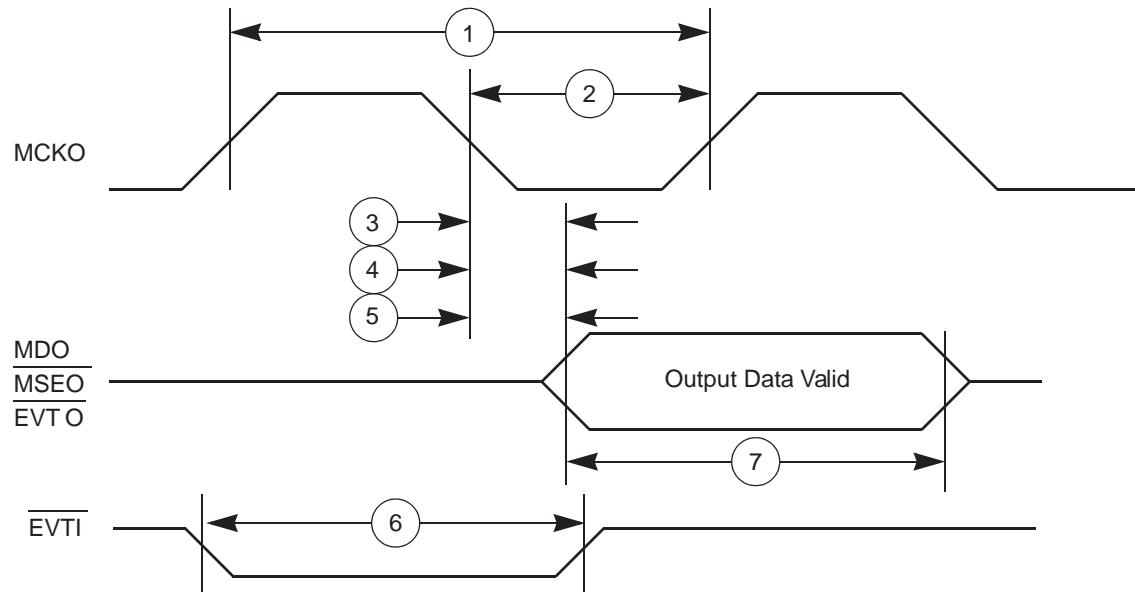

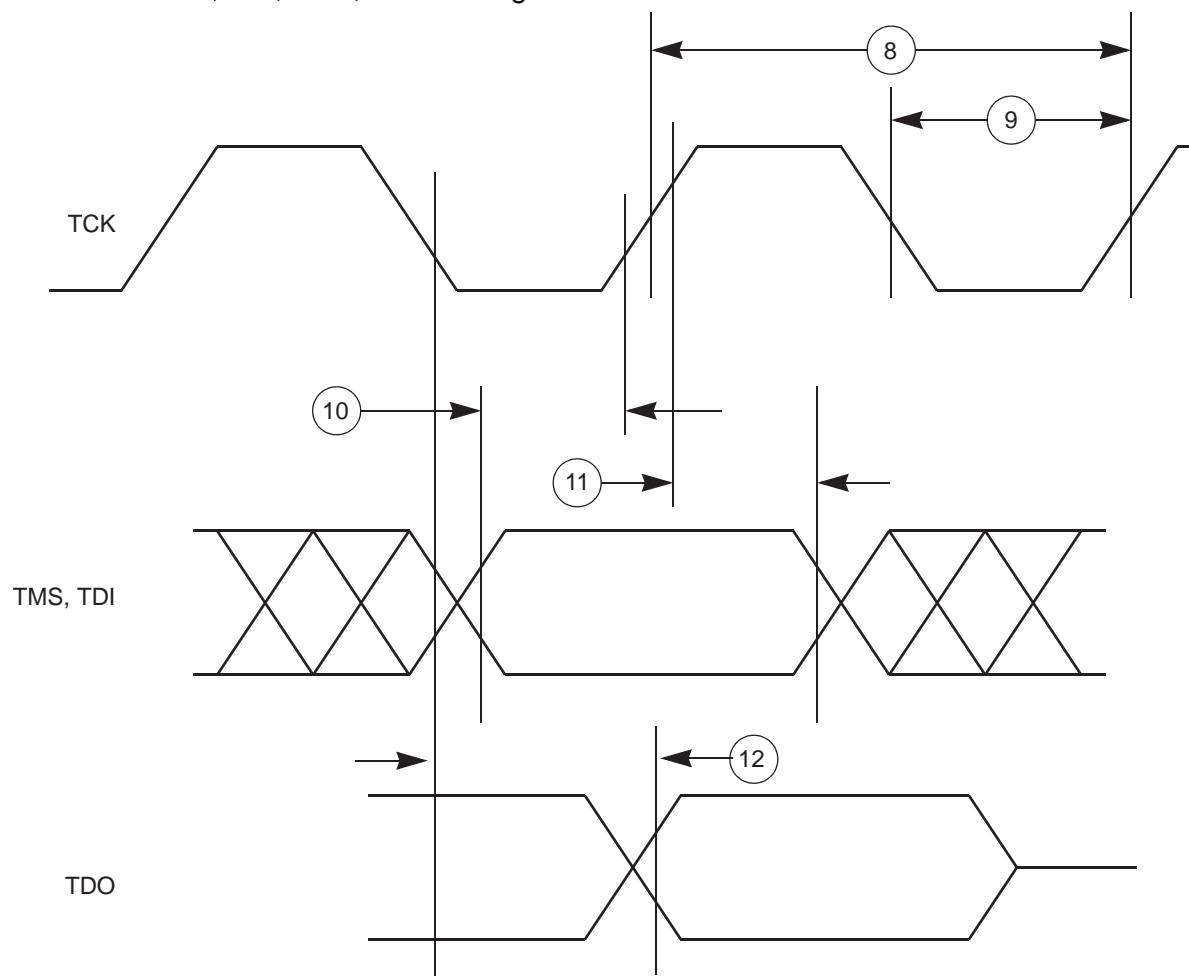

- Nexus Development Interface (NDI) per IEEE-ISTO 5001-2003/5001-2008 Standard

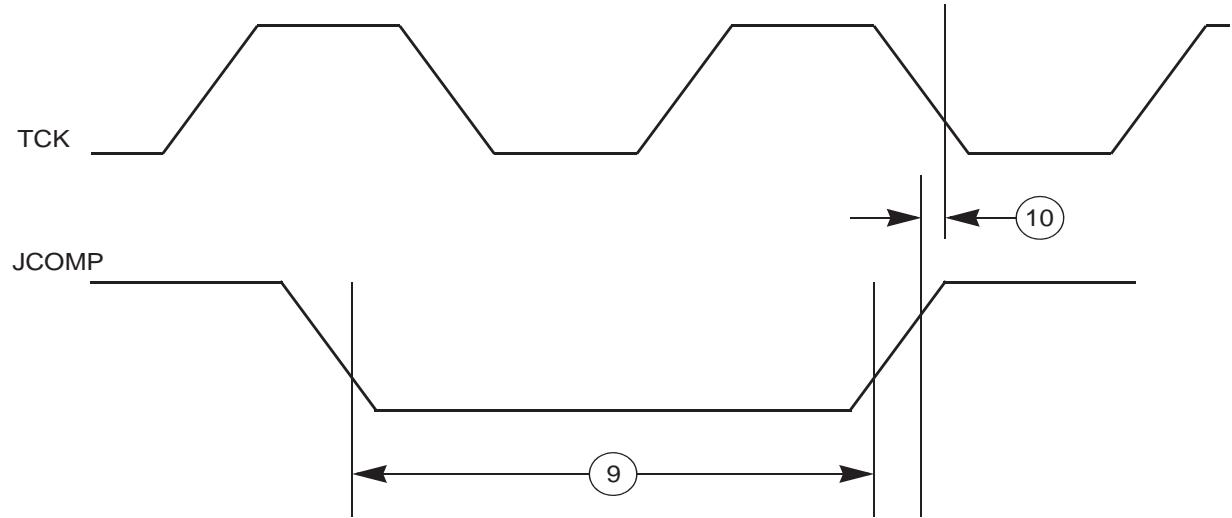

- Device and Board Test Support per Joint Test Action Group (JTAG) (IEEE 1149.1)

- On-Chip Voltage Regulator Controller Regulates Supply Voltage Down to 1.2 V for Core Logic

Whilst Teledyne e2v Semiconductors SAS has taken care to ensure the accuracy of the information contained herein it accepts no responsibility for the consequences of any use thereof and also reserves the right to change the specification of goods without notice. Teledyne e2v Semiconductors SAS accepts no liability beyond the set out in its standard conditions of sale in respect of infringement of third party patents arising from the use of the devices in accordance with information contained herein.

Teledyne e2v Semiconductors SAS, avenue de Rochepleine 38120 Saint-Egrève, France

Holding Company: Teledyne e2v Semiconductors SAS

Telephone: +33 (0)4 76 58 30 00

Contact Teledyne e2v by e-mail: [hotline-std@teledyne-e2v.com](mailto:hotline-std@teledyne-e2v.com) or visit [www.teledyne-e2v.com](http://www.teledyne-e2v.com) for global sales and operations centres

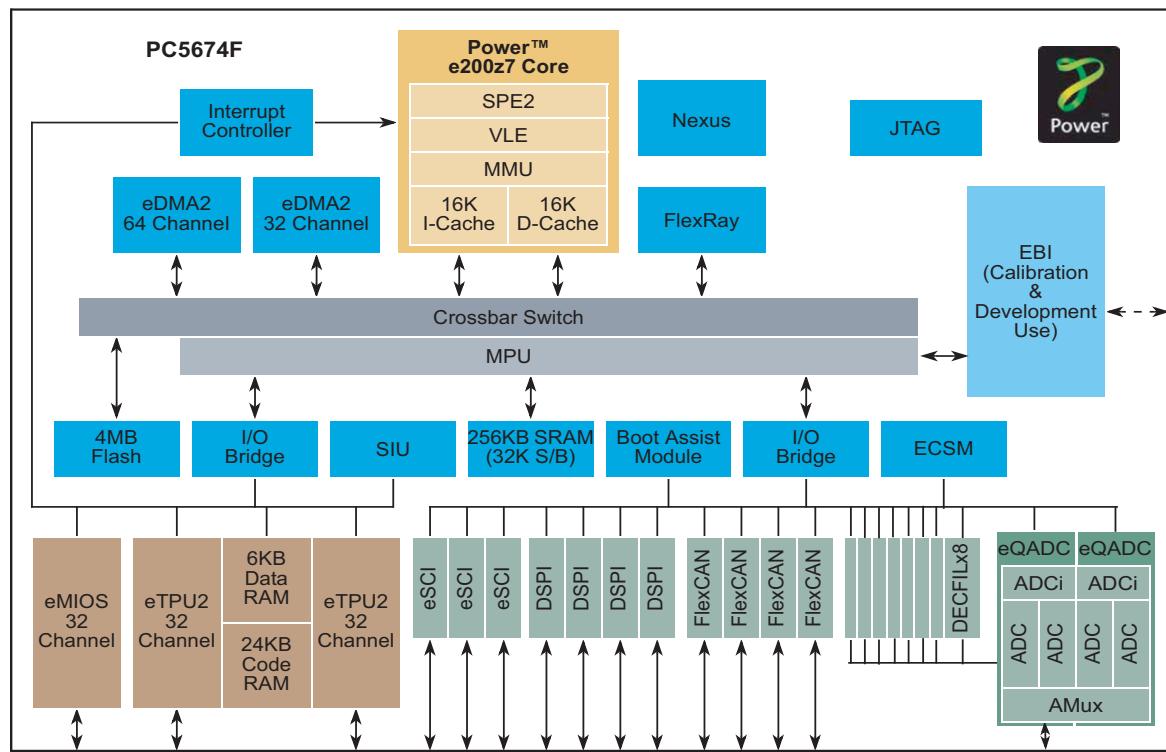

## 1. BLOCK DIAGRAM

### 1.1 Block diagram

Figure 1.1 shows a top-level block diagram of the PC5674F device.

Figure 1-1. Block Diagram

#### LEGEND

**ADC** – Analog to digital convertor interface

**ADCi** – ADC interface

**AMux** – Analog multiplexer

**DECFIL** – Decimation filter

**DSPI** – Deserial/serial peripheral interface

**EBI** – External bus interface

**ECSM** – Error correction status module

**eDMA2** – Enhanced direct memory access

**eMIOS** – Enhanced modular I/O system

**eQADC** – Enhanced queued A/D converter module

**eSCI** – Enhanced serial communications inter-

**eTPU2** – Enhanced time processing unit 2

**FlexCAN** – Controller area network

**MMU** – Memory management unit

**MPU** – Memory protection unit

**S/B** – Stand-by

**SIU** – System integration unit

**SPE2** – Signal processing engine 2

**SRAM** – General-purpose static RAM

**VLE** – Variable length instruction encoding

## 2. PIN ASSIGNMENTS

The figures in this section show the primary pin function. For the full signal properties and muxing table, see Appendix A, Signal Properties and Muxing.

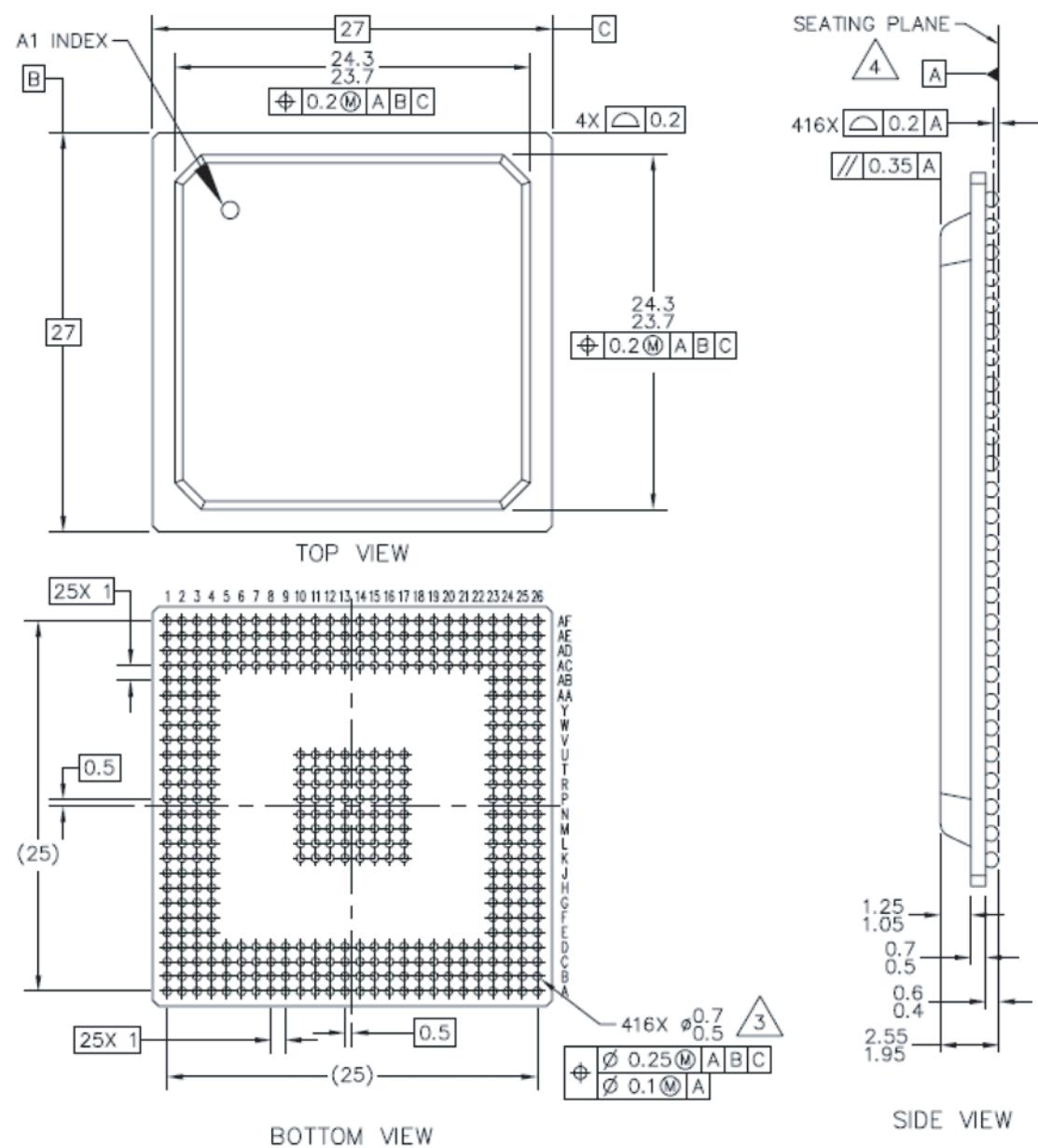

### 2.1 416-ball TEPBGA Pin Assignments

Figure 2-1 shows the 416-ball TEPBGA pin assignments in one figure. The same information is shown in Figure 2-2 through Figure 2-5.

**Figure 2-1. PC5674F 416-ball TEPBGA (Full Diagram)**

|    | 1       | 2         | 3          | 4          | 5       | 6     | 7     | 8     | 9       | 10        | 11        | 12     | 13      | 14      | 15      | 16      | 17        | 18        | 19    | 20    | 21     | 22     | 23    | 24      | 25      | 26      |         |         |   |

|----|---------|-----------|------------|------------|---------|-------|-------|-------|---------|-----------|-----------|--------|---------|---------|---------|---------|-----------|-----------|-------|-------|--------|--------|-------|---------|---------|---------|---------|---------|---|

| A  | VSS     | VDD       | RSTOUT     | ANAO       | ANA4    | ANA8  | ANA11 | ANA15 | VDDA_A0 | REF-BYPC1 | VRL_A     | VRH_A  | AN28    | AN32    | AN36    | VDDA_B0 | REF-BYPC1 | VRL_B     | VRH_B | ANB7  | ANB11  | ANB14  | ANB17 | ANB21   | ANB23   | VSS     | A       |         |   |

| B  | VDDEH1  | VSS       | VDD        | TEST       | ANA1    | ANA5  | ANA10 | ANA14 | VDDA_A1 | VSSA_A1   | REF-BYPC1 | AN24   | AN27    | AN29    | AN33    | VDDA_B1 | VSSA_B0   | REF-BYPCB | ANB6  | ANB8  | ANB10  | ANB15  | ANB18 | ANB22   | VSS     | TCRCLKC | B       |         |   |

| C  | ETPUA30 | ETPUA31   | VSS        | VDD        | ANA2    | ANA6  | ANA9  | ANA13 | ANA17   | ANA19     | ANA21     | ANA23  | AN26    | AN30    | AN34    | AN37    | AN38      | ANB0      | ANB4  | ANB5  | ANB12  | ANB16  | ANB19 | VSS     | ETPUC0  | ETPUC1  | C       |         |   |

| D  | ETPUA27 | ETPUA28   | ETPUA29    | VSS        | VDD     | ANA3  | ANA7  | ANA12 | ANA16   | ANA18     | ANA20     | ANA22  | AN25    | AN31    | AN35    | AN39    | ANB1      | ANB2      | ANB3  | ANB9  | ANB13  | ANB20  | VSS   | VDDEH7  | ETPUC2  | ETPUC3  | D       |         |   |

| E  | ETPUA23 | ETPUA24   | ETPUA25    | ETPUA26    |         |       |       |       |         |           |           |        |         |         |         |         |           |           |       |       |        |        |       | VDDEH7  | ETPUC4  | ETPUC5  | ETPUC6  | E       |   |

| F  | ETPUA19 | ETPUA20   | ETPUA21    | ETPUA22    |         |       |       |       |         |           |           |        |         |         |         |         |           |           |       |       |        |        |       | ETPUC7  | ETPUC8  | ETPUC9  | ETPUC10 | F       |   |

| G  | ETPUA15 | ETPUA16   | ETPUA17    | ETPUA18    |         |       |       |       |         |           |           |        |         |         |         |         |           |           |       |       |        |        |       | ETPUC11 | ETPUC12 | ETPUC13 | ETPUC14 | G       |   |

| H  | ETPUA11 | ETPUA12   | ETPUA14    | ETPUA13    |         |       |       |       |         |           |           |        |         |         |         |         |           |           |       |       |        |        |       | ETPUC15 | ETPUC16 | ETPUC17 | ETPUC18 | H       |   |

| J  | ETPUA7  | ETPUA8    | ETPUA9     | ETPUA10    |         |       |       |       |         |           |           |        |         |         |         |         |           |           |       |       |        |        |       | ETPUC19 | ETPUC20 | ETPUC21 | ETPUC22 | J       |   |

| K  | ETPUA3  | ETPUA4    | ETPUA5     | ETPUA6     |         |       |       |       |         |           |           |        |         |         |         | VSS     | VSS       | VSS       | VSS   | VSS   | VSS    | VSS    | VSS   |         | ETPUC23 | ETPUC24 | ETPUC25 | ETPUC26 | K |

| L  | TCRCLKA | ETPUA0    | ETPUA1     | ETPUA2     |         |       |       |       |         |           |           |        |         |         |         | VSS     | VSS       | VSS       | VSS   | VSS   | VSS    | VSS    | VSS   |         | ETPUC27 | ETPUC28 | ETPUC29 | ETPUC30 | L |

| M  | VDD33_1 | TXDA      | RXDA       | VSTBY      |         |       |       |       |         |           |           |        |         |         |         | VSS     | VSS       | VSS       | VSS   | VSS   | VSS    | VSS    | VSS   |         | ETPUC31 | ETPUB15 | ETPUB14 | VDDEH7  | M |

| N  | RXDB    | BOOT-CFG1 | WKPCFG     | VDD        |         |       |       |       |         |           |           |        |         |         |         | VDDE2   | VSS       | VSS       | VSS   | VSS   | VSS    | VSS    | VSS   |         | VDDEH6  | ETPUB11 | ETPUB12 | ETPUB13 | N |

| P  | TXDB    | PLLCFG1   | PLLCFG2    | VDDEH1     |         |       |       |       |         |           |           |        |         |         |         | VDDE2   | VDDE2     | VSS       | VSS   | VSS   | VSS    | VSS    | VSS   |         | ETPUB7  | ETPUB8  | ETPUB9  | ETPUB10 | P |

| R  | JCOMP   | RESET     | PLLCFG0    | RDY        |         |       |       |       |         |           |           |        |         |         |         | VDDE2   | VDDE2     | VSS       | VSS   | VSS   | VSS    | VSS    | VSS   |         | ETPUB3  | ETPUB4  | ETPUB5  | ETPUB6  | R |

| T  | VDDE2   | MCK0      | MSE01      | EVTI       |         |       |       |       |         |           |           |        |         |         |         | VDDE2   | VDDE2     | VDDE2     | VSS   | VSS   | VSS    | VSS    | VSS   |         | TCRCLKB | ETPUB0  | ETPUB1  | ETPUB2  | T |

| U  | EVTO    | MSE00     | MDO0       | MDO1       |         |       |       |       |         |           |           |        |         |         |         | VDDE2   | VDDE2     | VDDE2     | VSS   | VSS   | VSS    | VSS    | VSS   |         | ETPUB19 | ETPUB18 | ETPUB17 | ETPUB16 | U |

| V  | MDO2    | MDO3      | MDO4       | MDO5       |         |       |       |       |         |           |           |        |         |         |         | VDDE2   | VDDE2     | VDDE2     | VSS   | VSS   | VSS    | VSS    | VSS   |         | ETPUB26 | ETPUB22 | ETPUB21 | ETPUB20 | V |

| W  | MDO6    | MDO7      | MDO8       | VDDE2      |         |       |       |       |         |           |           |        |         |         |         |         |           |           |       |       |        |        |       | REGSEL  | ETPUB25 | ETPUB24 | ETPUB23 | W       |   |

| Y  | MDO9    | MDO10     | MDO11      | MDO15      |         |       |       |       |         |           |           |        |         |         |         |         |           |           |       |       |        |        |       | ETPUB29 | ETPUB28 | ETPUB27 | REGCTL  | Y       |   |

| AA | MDO12   | MDO13     | MDO14      | VDD33_2    |         |       |       |       |         |           |           |        |         |         |         |         |           |           |       |       |        |        |       | VDD33_3 | ETPUB30 | VDDREG  | VSSSYN  | AA      |   |

| AB | TDO     | TCK       | TMS        | VDD        |         |       |       |       |         |           |           |        |         |         |         |         |           |           |       |       |        |        |       | VDD     | ETPUB31 | VSSFL   | EXTAL   | AB      |   |

| AC | VDDE2   | TDI       | VDD        | VSS        | VDDE2   | PCSA1 | PCSA2 | PCSB4 | PCSB1   | VDDEH3    | VDDEH4    | VDD    | EMIOS8  | EMIOS14 | EMIOS18 | EMIOS22 | EMIOS27   | EMIOS31   | CNRXB | CNRXD | VDDEH5 | PCSC1  | VSS   | VDD     | VDDEH6  | XTAL    | AC      |         |   |

| AD | ENGCLK  | VDD       | VSS        | FR_A_Tx    | FR_B_Tx | PCSA5 | SOUTA | SCKA  | PCSB0   | PCSB3     | EMIOS2    | EMIOS5 | EMIOS9  | EMIOS15 | EMIOS19 | EMIOS23 | EMIOS26   | EMIOS30   | CNTXB | CNTXD | SCKC   | RXDC   | PCSC3 | VSS     | VDD     | VDDSYN  | AD      |         |   |

| AE | VDD     | VSS       | FR_A_RX    | FR_B_RX    | PCSA4   | PCSA0 | PCSA3 | SCKB  | SINB    | EMIOS0    | EMIOS3    | EMIOS6 | EMIOS10 | EMIOS13 | EMIOS17 | EMIOS21 | EMIOS25   | EMIOS29   | CNRXA | CNRXC | PCSC0  | SINC   | PCSC2 | PCSC5   | VSS     | VDD     | AE      |         |   |

| AF | VSS     | VDDE2     | FR_A_TX_EN | FR_B_TX_EN | VDDEH3  | PCSB5 | SINA  | PCSB2 | SOUTB   | EMIOS1    | MIOS4     | EMIOS7 | EMIOS11 | EMIOS12 | EMIOS16 | EMIOS20 | EMIOS24   | EMIOS28   | CNTXA | CNTXC | SOUTC  | VDDEH4 | TXDC  | PCSC4   | VDDEH5  | VSS     | AF      |         |   |

**Figure 2-2.** PC5674F 416-ball TEPBGA (1 of 4)

|   | 1       | 2        | 3       | 4       | 5    | 6    | 7     | 8     | 9       | 10         | 11       | 12    | 13   |   |

|---|---------|----------|---------|---------|------|------|-------|-------|---------|------------|----------|-------|------|---|

| A | VSS     | VDD      | RSTOUT  | ANA0    | ANA4 | ANA8 | ANA11 | ANA15 | VDDA_A0 | REFBYP-CA1 | VRL_A    | VRH_A | AN28 | A |

| B | VDDEH1  | VSS      | VDD     | TEST    | ANA1 | ANA5 | ANA10 | ANA14 | VDDA_A1 | VSSA_A1    | REFBYPCA | AN24  | AN27 | B |

| C | ETPUA30 | ETPUA31  | VSS     | VDD     | ANA2 | ANA6 | ANA9  | ANA13 | ANA17   | ANA19      | ANA21    | ANA23 | AN26 | C |

| D | ETPUA27 | ETPUA28  | ETPUA29 | VSS     | VDD  | ANA3 | ANA7  | ANA12 | ANA16   | ANA18      | ANA20    | ANA22 | AN25 | D |

| E | ETPUA23 | ETPUA24  | ETPUA25 | ETPUA26 |      |      |       |       |         |            |          |       |      | E |

| F | ETPUA19 | ETPUA20  | ETPUA21 | ETPUA22 |      |      |       |       |         |            |          |       |      | F |

| G | ETPUA15 | ETPUA16  | ETPUA17 | ETPUA18 |      |      |       |       |         |            |          |       |      | G |

| H | ETPUA11 | ETPUA12  | ETPUA14 | ETPUA13 |      |      |       |       |         |            |          |       |      | H |

| J | ETPUA7  | ETPUA8   | ETPUA9  | ETPUA10 |      |      |       |       |         |            |          |       |      | J |

| K | ETPUA3  | ETPUA4   | ETPUA5  | ETPUA6  |      |      |       |       |         | VSS        | VSS      | VSS   | VSS  | K |

| L | TCRCLKA | ETPUA0   | ETPUA1  | ETPUA2  |      |      |       |       |         | VSS        | VSS      | VSS   | VSS  | L |

| M | VDD33_1 | TXDA     | RXDA    | VSTBY   |      |      |       |       |         | VSS        | VSS      | VSS   | VSS  | M |

| N | RXDB    | BOOTCFG1 | WKPCFG  | VDD     |      |      |       |       |         | VDDE2      | VSS      | VSS   | VSS  | N |

|   | 1       | 2        | 3       | 4       | 5    | 6    | 7     | 8     | 9       | 10         | 11       | 12    | 13   |   |

**PC5674F 416-ball TEPBGA**

(as viewed from top through the package)

(1 of 4)

Figure 2-3. PC5674F 416-ball TEPBGA (2 of 4)

|   | 14                                                                                     | 15   | 16      | 17         | 18        | 19    | 20   | 21    | 22    | 23      | 24      | 25      | 26      |         |         |         |   |

|---|----------------------------------------------------------------------------------------|------|---------|------------|-----------|-------|------|-------|-------|---------|---------|---------|---------|---------|---------|---------|---|

| A | AN32                                                                                   | AN36 | VDDA_B0 | REFBYP-CB1 | VRL_B     | VRH_B | ANB7 | ANB11 | ANB14 | ANB17   | ANB21   | ANB23   | VSS     | A       |         |         |   |

| B | AN29                                                                                   | AN33 | VDDA_B1 | VSSA_B0    | REFBYPBCB | ANB6  | ANB8 | ANB10 | ANB15 | ANB18   | ANB22   | VSS     | TCRCLKC | B       |         |         |   |

| C | AN30                                                                                   | AN34 | AN37    | AN38       | ANB0      | ANB4  | ANB5 | ANB12 | ANB16 | ANB19   | VSS     | ETPUC0  | ETPUC1  | C       |         |         |   |

| D | AN31                                                                                   | AN35 | AN39    | ANB1       | ANB2      | ANB3  | ANB9 | ANB13 | ANB20 | VSS     | VDDEH7  | ETPUC2  | ETPUC3  | D       |         |         |   |

| E |                                                                                        |      |         |            |           |       |      |       |       | VDDEH7  | ETPUC4  | ETPUC5  | ETPUC6  | E       |         |         |   |

| F |                                                                                        |      |         |            |           |       |      |       |       | ETPUC7  | ETPUC8  | ETPUC9  | ETPUC10 | F       |         |         |   |

| G | <b>PC5674F 416-ball TEPBGA</b><br>(as viewed from top through the package)<br>(2 of 4) |      |         |            |           |       |      |       |       |         |         |         | ETPUC11 | ETPUC12 | ETPUC13 | ETPUC14 | G |

| H |                                                                                        |      |         |            |           |       |      |       |       | ETPUC15 | ETPUC16 | ETPUC17 | ETPUC18 | H       |         |         |   |

| J |                                                                                        |      |         |            |           |       |      |       |       | ETPUC19 | ETPUC20 | ETPUC21 | ETPUC22 | J       |         |         |   |

| K | VSS                                                                                    | VSS  | VSS     | VSS        |           |       |      |       |       | ETPUC23 | ETPUC24 | ETPUC25 | ETPUC26 | K       |         |         |   |

| L | VSS                                                                                    | VSS  | VSS     | VSS        |           |       |      |       |       | ETPUC27 | ETPUC28 | ETPUC29 | ETPUC30 | L       |         |         |   |

| M | VSS                                                                                    | VSS  | VSS     | VSS        |           |       |      |       |       | ETPUC31 | ETPUB15 | ETPUB14 | VDDEH7  | M       |         |         |   |

| N | VSS                                                                                    | VSS  | VSS     | VSS        |           |       |      |       |       | VDDEH6  | ETPUB11 | ETPUB12 | ETPUB13 | N       |         |         |   |

|   | 14                                                                                     | 15   | 16      | 17         | 18        | 19    | 20   | 21    | 22    | 23      | 24      | 25      | 26      |         |         |         |   |

Figure 2-4. PC5674F 416-ball TEPBGA (3 of 4)

|    | 1      | 2       | 3          | 4          | 5       | 6     | 7     | 8     | 9     | 10     | 11     | 12     | 13      |    |

|----|--------|---------|------------|------------|---------|-------|-------|-------|-------|--------|--------|--------|---------|----|

| P  | TXDB   | PLLCFG1 | PLLCFG2    | VDDEH1     |         |       |       |       |       | VDDE2  | VDDE2  | VSS    | VSS     | P  |

| R  | JCOMP  | RESET   | PLLCFG0    | RDY        |         |       |       |       |       | VDDE2  | VDDE2  | VSS    | VSS     | R  |

| T  | VDDE2  | MCKO    | MSE01      | EVTI       |         |       |       |       |       | VDDE2  | VDDE2  | VDDE2  | VSS     | T  |

| U  | EVTO   | MSE00   | MDO00      | MDO01      |         |       |       |       |       | VDDE2  | VDDE2  | VDDE2  | VSS     | U  |

| V  | MDO02  | MDO03   | MDO04      | MDO05      |         |       |       |       |       |        |        |        |         | V  |

| W  | MDO06  | MDO07   | MDO08      | VDDE2      |         |       |       |       |       |        |        |        |         | W  |

| Y  | MDO09  | MDO10   | MDO11      | MDO15      |         |       |       |       |       |        |        |        |         | Y  |

| AA | MDO12  | MDO13   | MDO14      | VDD33_2    |         |       |       |       |       |        |        |        |         | AA |

| AB | TDO    | TCK     | TMS        | VDD        |         |       |       |       |       |        |        |        |         | AB |

| AC | VDDE2  | TDI     | VDD        | VSS        | VDDE2   | PCSA1 | PCSA2 | PCSB4 | PCSB1 | VDDEH3 | VDDEH4 | VDD    | EMIOS8  | AC |

| AD | ENGCLK | VDD     | VSS        | FR_A_TX    | FR_B_TX | PCSA5 | SOUTA | SCKA  | PCSB0 | PCSB3  | MIOS2  | EMIOS5 | EMIOS9  | AD |

| AE | VDD    | VSS     | FR_A_RX    | FR_B_RX    | PCSA4   | PCSA0 | PCSA3 | SCKB  | SINB  | EMIOS0 | EMIOS3 | EMIOS6 | EMIOS10 | AE |

| AF | VSS    | VDDE2   | FR_A_TX_EN | FR_B_TX_EN | VDDEH3  | PCSB5 | SINA  | PCSB2 | SOUTB | EMIOS1 | EMIOS4 | EMIOS7 | EMIOS11 | AF |

|    | 1      | 2       | 3          | 4          | 5       | 6     | 7     | 8     | 9     | 10     | 11     | 12     | 13      |    |

**PC5674F 416-ball TEPBGA**

(as viewed from top through the package)

(3 of 4)

Figure 2-5. PC5674F 416-ball TEPBGA (4 of 4)

|    | 14      | 15      | 16      | 17      | 18      | 19    | 20    | 21     | 22     | 23      | 24      | 25      | 26      |    |

|----|---------|---------|---------|---------|---------|-------|-------|--------|--------|---------|---------|---------|---------|----|

| P  | VSS     | VSS     | VSS     | VSS     |         |       |       |        |        | ETPUB7  | ETPUB8  | ETPUB9  | ETPUB10 | P  |

| R  | VSS     | VSS     | VSS     | VSS     |         |       |       |        |        | ETPUB3  | ETPUB4  | ETPUB5  | ETPUB6  | R  |

| T  | VSS     | VSS     | VSS     | VSS     |         |       |       |        |        | TCRCLKB | ETPUB0  | ETPUB1  | ETPUB2  | T  |

| U  | VSS     | VSS     | VSS     | VSS     |         |       |       |        |        | ETPUB19 | ETPUB18 | ETPUB17 | ETPUB16 | U  |

| V  |         |         |         |         |         |       |       |        |        | ETPUB26 | ETPUB22 | ETPUB21 | ETPUB20 | V  |

| W  |         |         |         |         |         |       |       |        |        | REGSEL  | ETPUB25 | ETPUB24 | ETPUB23 | W  |

| Y  |         |         |         |         |         |       |       |        |        | ETPUB29 | ETPUB28 | ETPUB27 | REGCTL  | Y  |

| AA |         |         |         |         |         |       |       |        |        | VDD33_3 | ETPUB30 | VDDREG  | VSSSYN  | AA |

| AB |         |         |         |         |         |       |       |        |        | VDD     | ETPUB31 | VSSFL   | EXTAL   | AB |

| AC | EMIOS14 | EMIOS18 | EMIOS22 | EMIOS27 | EMIOS31 | CNRXB | CNRXD | VDDEH5 | PCSC1  | VSS     | VDD     | VDDEH6  | XTAL    | AC |

| AD | EMIOS15 | EMIOS19 | EMIOS23 | EMIOS26 | EMIOS30 | CNTXB | CNTXD | SCKC   | RXDC   | PCSC3   | VSS     | VDD     | VDDSYN  | AD |

| AE | EMIOS13 | EMIOS17 | EMIOS21 | EMIOS25 | EMIOS29 | CNRXA | CNRXC | PCSC0  | SINC   | PCSC2   | PCSC5   | VSS     | VDD     | AE |

| AF | EMIOS12 | EMIOS16 | EMIOS20 | EMIOS24 | EMIOS28 | CNTXA | CNTXC | SOUTCP | VDDEH4 | TXDC    | CSC4    | VDDEH5  | VSS     | AF |

|    | 14      | 15      | 16      | 17      | 18      | 19    | 20    | 21     | 22     | 23      | 24      | 25      | 26      |    |

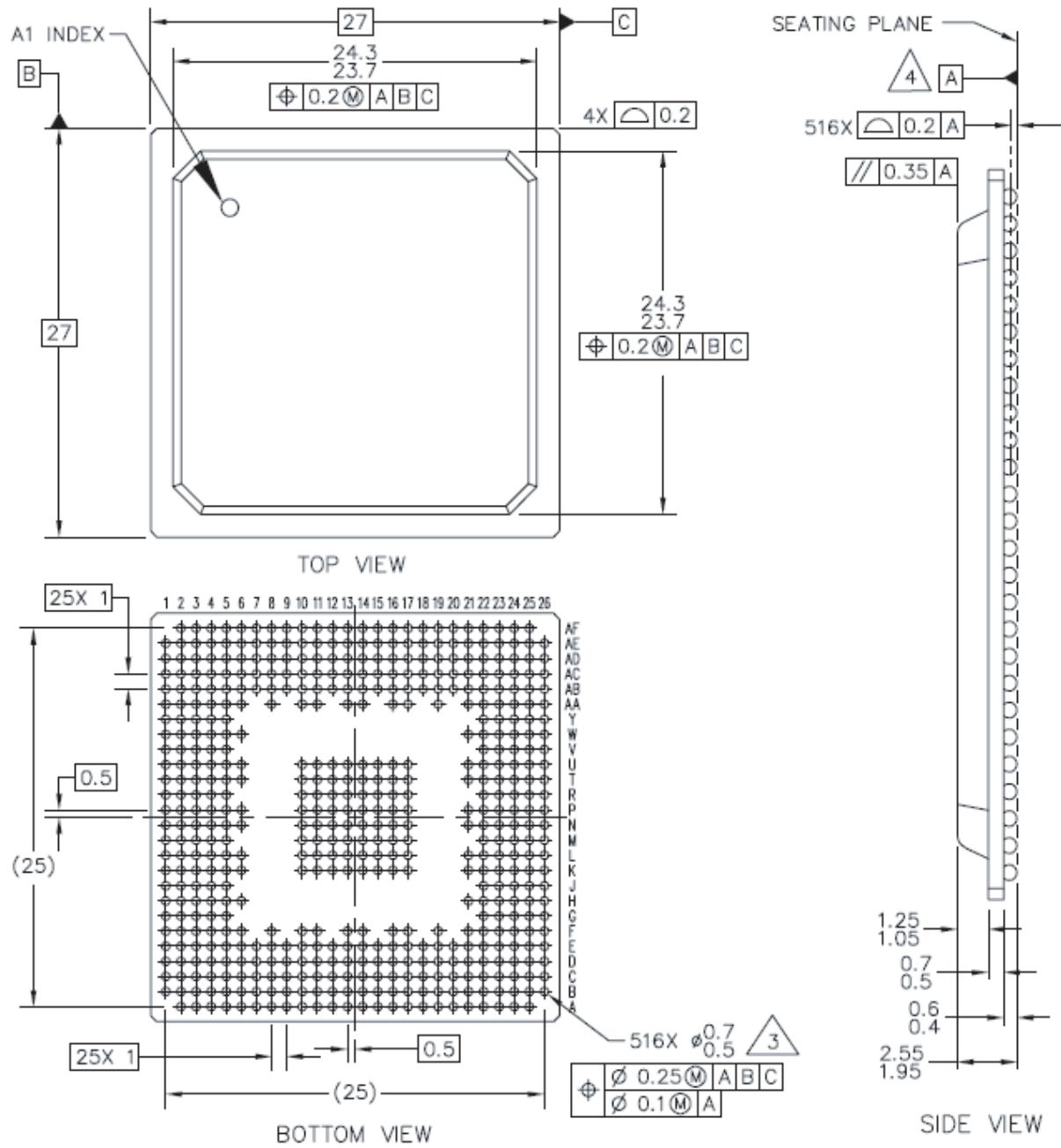

## 2.2 516-ball TEPBGA Pin Assignments

Figure 2-6 shows the 516-ball TEPBGA pin assignments in one figure. The same information is shown split into four quadrants in Figure 2-7 through Figure 2-10.

**Figure 2-6.** PC5674F 516-ball TEPBGA (Full Diagram)

|    | 1       | 2       | 3         | 4         | 5       | 6       | 7     | 8     | 9       | 10        | 11        | 12      | 13       | 14      | 15      | 16      | 17         | 18         | 19      | 20      | 21     | 22      | 23     | 24      | 25     | 26      |         |         |         |         |         |         |    |

|----|---------|---------|-----------|-----------|---------|---------|-------|-------|---------|-----------|-----------|---------|----------|---------|---------|---------|------------|------------|---------|---------|--------|---------|--------|---------|--------|---------|---------|---------|---------|---------|---------|---------|----|

| A  | VDD     | RSTOUT  | ANAO      | AN44      | AN4     | AN9     | AN11  | AN15  | VDDA_A0 | REF-BYPC4 | VRL_A     | VRH_A   | AN28     | AN29    | AN36    | VDDA_B0 | REF-BYPCB1 | VRL_B      | VRH_B   | ANB5    | ANB9   | ANB12   | ANB18  | ANB21   | VSS    | A       |         |         |         |         |         |         |    |

| B  | VDDEH1  | VSS     | VDD       | TEST      | AN41    | AN5     | AN10  | AN14  | VDDA_A1 | VSSA_A    | REF-BYPC4 | AN24    | AN27     | AN30    | AN32    | VDDA_B1 | VSSA_B0    | REF-BYPCB1 | ANB4    | ANB8    | ANB10  | ANB13   | ANB19  | ANB22   | VSS    | B       |         |         |         |         |         |         |    |

| C  | ETPUA30 | ETPUA31 | VSS       | VDD       | AN2     | AN4     | AN7   | AN13  | AN17    | AN19      | AN21      | AN22    | AN25     | AN31    | AN34    | AN39    | AN37       | ANB0       | ANB7    | ANB6    | ANB11  | ANB15   | ANB20  | VSS     | ETPUC0 | ETPUC1  | C       |         |         |         |         |         |    |

| D  | ETPUA27 | ETPUA28 | ETPUA29   | VSS       | VDD     | AN3     | AN8   | AN12  | AN16    | AN18      | AN20      | AN23    | AN26     | AN33    | AN35    | AN38    | ANB1       | ANB2       | ANB3    | ANB14   | ANB16  | ANB17   | VSS    | VDDEH7  | ETPUC2 | ETPUC3  | D       |         |         |         |         |         |    |

| E  | ETPUA23 | ETPUA24 | ETPUA25   | ETPUA26   | VSS     | VDD     | VSS   | VSS   | VSS     | VSS       | VSS       | VSS     | VSS      | VSS     | VSS     | VSS     | VSS        | VSS        | VSS     | ANB23   | VSS    | VSS     | VDDEH7 | ETPUC4  | ETPUC5 | ETPUC6  | E       |         |         |         |         |         |    |

| F  | ETPUA19 | ETPUA20 | ETPUA21   | ETPUA22   | VSS     | VDDE8   |       | VDDE8 |         | VDDE8     | VDDE8     |         | VSS      | VSS     |         | VDDE10  | VDDE10     |            | VDDE10  |         | VDDE10 | TCRCLKC | ETPUC7 | ETPUC8  | ETPUC9 | ETPUC10 | F       |         |         |         |         |         |    |

| G  | ETPUA11 | ETPUA13 | ETPUA15   | ETPUA17   | ETPUA18 |         |       |       |         |           |           |         |          |         |         |         |            |            |         |         |        |         |        |         |        | ETPUC11 | ETPUC12 | ETPUC13 | ETPUC14 | ETPUC15 | G       |         |    |

| H  | ETPUA5  | ETPUA7  | ETPUA8    | ETPUA3    | ETPUA14 | ETPUA16 |       |       |         |           |           |         |          |         |         |         |            |            |         |         |        |         |        |         |        |         | ETPUC19 | ETPUC16 | ETPUC17 | ETPUC18 | ETPUC20 | ETPUC21 | H  |

| J  | ETPUA1  | ETPUA2  | ETPUA9    | ETPUA4    | ETPUA12 |         |       |       |         |           |           |         |          |         |         |         |            |            |         |         |        |         |        |         |        |         | ETPUC22 | ETPUC23 | ETPUC24 | ETPUC26 | ETPUC27 | J       |    |

| K  | TXDB    | TXDA    | RXDA      | TCRCLKA   | ETPUA6  | ETPUA10 |       |       |         |           |           |         |          |         |         |         |            |            |         |         |        |         |        |         |        |         | ETPUC25 | ETPUC28 | ETPUC29 | ETPUC30 | ETPUC31 | D_DAT15 | K  |

| L  | PLLCFG1 | PLLCFG2 | BOOT-CFG1 | BOOT-CFG0 | RXDB    | ETPUA0  |       |       |         |           |           |         |          |         |         |         |            |            |         |         |        |         |        |         |        |         | VDD33_6 | D_DAT14 | D_DAT13 | D_DAT12 | D_DAT11 | D_DAT10 | L  |

| M  | VDD33_1 | D_BDIP  | PLLCFG0   | VSTBY     | WKPCFG  |         |       |       |         |           |           |         |          |         |         |         |            |            |         |         |        |         |        |         |        |         | D_DAT9  | D_DAT8  | D_DAT7  | D_DAT5  | VDDEH7  | M       |    |

| N  | D_WE0   | D_WE2   | D_WE3     | VDD       | RESET   | VDDE8   |       |       |         |           |           |         |          |         |         |         |            |            |         |         |        |         |        |         |        |         | VDDE10  | D_DAT6  | VDDEH6  | D_DAT2  | D_DAT3  | D_DAT4  | N  |

| P  | D_ADD9  | D_ADD10 | D_ADD11   | VDDEH1    | D_WE1   | VD33_1  |       |       |         |           |           |         |          |         |         |         |            |            |         |         |        |         |        |         |        |         | VDDE10  | ETPUB13 | D_OE    | D_ALE   | D_DAT0  | D_DAT1  | P  |

| R  | D_ADD12 | D_ADD13 | D_ADD14   | D_ADD15   | D_ADD16 |         |       |       |         |           |           |         |          |         |         |         |            |            |         |         |        |         |        |         |        |         | ETPUB9  | ETPUB12 | ETPUB14 | ETPUB15 | D_RDWR  | R       |    |

| T  | VDDE2   | D_ADD18 | D_ADD19   | D_ADD20   | D_ADD17 | D_CS3   |       |       |         |           |           |         |          |         |         |         |            |            |         |         |        |         |        |         |        |         | ETPUB17 | ETPUB3  | ETPUB7  | ETPUB8  | ETPUB10 | ETPUB11 | T  |

| U  | D_CS2   | JCOMP   | RDY       | MCKO      | MSE01   | MSE00   |       |       |         |           |           |         |          |         |         |         |            |            |         |         |        |         |        |         |        |         | ETPUB23 | ETPUB1  | ETPUB2  | ETPUB4  | ETPUB5  | ETPUB6  | U  |

| V  | ETVI    | EVTO    | MD00      | MD02      | MD03    |         |       |       |         |           |           |         |          |         |         |         |            |            |         |         |        |         |        |         |        |         | ETPUB21 | ETPUB22 | ETPUB16 | TCRCLKB | ETPUB0  | V       |    |

| W  | MD04    | MD05    | MD06      | VDDE2     | MD08    | MD01    |       |       |         |           |           |         |          |         |         |         |            |            |         |         |        |         |        |         |        |         | ETPUB25 | ETPUB29 | REGSEL  | ETPUB20 | ETPUB19 | ETPUB18 | W  |

| Y  | MD07    | MD09    | MD010     | MD011     | MD012   |         |       |       |         |           |           |         |          |         |         |         |            |            |         |         |        |         |        |         |        |         | ETPUB31 | ETPUB26 | ETPUB27 | ETPUB24 | REGCTL  | Y       |    |

| AA | MD013   | MD014   | MD015     | VDD33_1   | VDDE8   | VSS     |       |       |         | PCSA5     |           | SOUTB   | VDD33_4  |         |         | VDDE9   | VDD33_4    |            | EMIOS23 | EMIOS31 |        | CNRXB   |        |         |        |         | VSS     | VDDE10  | VDD33_3 | ETPUB28 | VDDREG  | VSSSYN  | AA |

| AB | TDO     | TCK     | TMS       | VDD       | VSS     | VDDE9   | VDDE9 | SCKA  | SINB    | D_CS1     | D_ADD21   | D_ADD29 | EMIOS1   | EMIOS11 | EMIOS17 | EMIOS19 | EMIOS29    | VDDE9      | VDDE9   | VDDE9   | VDDE9  | VSS     | VDD    | ETPUB30 | VSSFL  | EXTAL   | AB      |         |         |         |         |         |    |

| AC | VDDE2   | TDI     | VDD       | VSS       | VDDE2   | PCSA1   | SOUTA | VSCKB | PCSB3   | VDDEH3    | VDDEH4    | DD      | EMIOS0   | EMIOS8  | EMIOS13 | EMIOS22 | EMIOS24    | EMIOS28    | CNTXB   | CNRXD   | VDDEH5 | PCSC1   | VSS    | VDD     | ETPUB6 | XTAL    | AC      |         |         |         |         |         |    |

| AD | ENCLK   | VDD     | VSS       | FR_A_RX   | FR_B_RX | PCSA0   | PCSA3 | PCSB2 | D_CS0   | D_ADD22   | D_ADD25   | D_ADD28 | EMIOS2   | EMIOS7  | EMIOS12 | EMIOS16 | EMIOS18    | EMIOS27    | CNRXA   | CNTXD   | SCKC   | RXDC    | PCSC3  | VSS     | VDD    | VDDSYN  | AD      |         |         |         |         |         |    |

| AE | VDD     | VSS     | FR_A_RX   | FR_B_RX   | PCSA4   | PCSB5   | SINA  | PCSB1 | D_TS    | D_ADD23   | D_ADD26   | D_ADD30 | EMIOS3   | EMIOS6  | EMIOS10 | EMIOS15 | EMIOS21    | EMIOS26    | CNTXA   | CNRXC   | PCSC0  | SINC    | PCSC2  | PCSC5   | VSS    | VDD     | AE      |         |         |         |         |         |    |

| AF | VDDE2   | FR_A_RX | FR_B_RX   | TX_EN     | TX_EN   | VDDEH3  | PCSA2 | PCSB4 | PCSB0   | D_TA      | D_ADD24   | D_ADD27 | D_CLKOUT | EMIOS4  | EMIOS5  | EMIOS9  | EMIOS20    | EMIOS14    | EMIOS25 | EMIOS30 | CNTXC  | SOUTC   | VDDEH4 | TXDC    | PCSC4  | VDDEH5  |         | AF      |         |         |         |         |    |

**PC5674F 516-ball TEPBGA**

(as viewed from top through the package)

Figure 2-7. PC5674F 516-ball TEPBGA (1 of 4)

|   | 1       | 2       | 3        | 4        | 5       | 6       | 7     | 8     | 9       | 10        | 11        | 12    | 13   |   |

|---|---------|---------|----------|----------|---------|---------|-------|-------|---------|-----------|-----------|-------|------|---|

| A |         | VDD     | RSTOUT   | ANA0     | ANA4    | ANA9    | ANA11 | ANA15 | VDDA_A0 | REF-BYPC1 | VRL_A     | VRH_A | AN28 | A |

| B | VDDEH1  | VSS     | VDD      | TEST     | ANA1    | ANA5    | ANA10 | ANA14 | VDDA_A1 | VSSA_A1   | REFBYPCAA | N24   | AN27 | B |

| C | ETPUA30 | ETPUA31 | VSS      | VDD      | ANA2    | ANA6    | ANA7  | ANA13 | ANA17   | ANA19     | ANA21     | ANA22 | AN25 | C |

| D | ETPUA27 | ETPUA28 | ETPUA29  | VSS      | VDD     | ANA3    | ANA8  | ANA12 | ANA16   | ANA18     | ANA20     | ANA23 | AN26 | D |

| E | ETPUA23 | ETPUA24 | ETPUA25  | ETPUA26  | VSS     | VDD     | VSS   | VSS   | VSS     | VSS       | VSS       | VSS   | VSS  | E |

| F | ETPUA19 | ETPUA20 | ETPUA21  | ETPUA22  | VSS     | VDDE8   |       | VDDE8 |         | VDDE8     | VDDE8     |       | VSS  | F |

| G | ETPUA11 | ETPUA13 | ETPUA15  | ETPUA17  | ETPUA18 |         |       |       |         |           |           |       |      | G |

| H | ETPUA5  | ETPUA7  | ETPUA8   | ETPUA3   | ETPUA14 | ETPUA16 |       |       |         |           |           |       |      | H |

| J | ETPUA1  | ETPUA2  | ETPUA9   | ETPUA4   | ETPUA12 |         |       |       |         |           |           |       |      | J |

| K | TXDB    | TXDA    | RXDA     | TCRCLKA  | TPUA6   | ETPUA10 |       |       |         |           |           |       |      | K |

| L | PLLCFG1 | PLLCFG2 | BOOTCFG1 | BOOTCFG0 | XDB     | ETPUA0  |       |       |         |           |           |       |      | L |

| M | VDD33_1 | D_BDIP  | PLLCFG0  | WVSTBY   | KPCFG   |         |       |       |         |           |           |       |      | M |

| N | D_WE0   | D_WE2   | D_WE3    | VDD      | RESET   | VDDE8   |       |       |         |           |           |       |      | N |

|   | 1       | 2       | 3        | 4        | 5       | 6       | 7     | 8     | 9       | 10        | 11        | 12    | 13   |   |

**PC5674F 516-ball TEPBGA**

(as viewed from top through the package)

(1 of 4)

**Figure 2-8.** PC5674F 516-ball TEPBGA (2 of 4)

|   | 14   | 15   | 16      | 17         | 18       | 19     | 20    | 21      | 22      | 23      | 24      | 25      | 26      |   |

|---|------|------|---------|------------|----------|--------|-------|---------|---------|---------|---------|---------|---------|---|

| A | AN29 | AN36 | VDAA_B0 | REF-BYPCB1 | VRL_B    | VRH_B  | ANB5  | ANB9    | ANB12   | ANB18   | ANB21   | VSS     |         | A |

| B | AN30 | AN32 | VDAA_B1 | VSSA_B0    | REFBYPCB | ANB4   | ANB8  | ANB10   | ANB13   | ANB19   | ANB22   | VSS     | VSS     | B |

| C | AN31 | AN34 | AN39    | AN37       | ANB0     | ANB7   | ANB6  | ANB11   | ANB15   | ANB20   | VSS     | ETPUC0  | ETPUC1  | C |

| D | AN33 | AN35 | AN38    | ANB1       | ANB2     | ANB3   | ANB14 | ANB16   | ANB17   | VSS     | VDDEH7  | ETPUC2  | ETPUC3  | D |

| E | VSS  | VSS  | VSS     | VSS        | VSS      | VSS    | ANB23 | VSS     | VSS     | VDDEH7  | ETPUC4  | ETPUC5  | ETPUC6  | E |

| F | VSS  |      | VDDE10  | VDDE10     |          | VDDE10 |       | VDDE10  | TCRCLKC | ETPUC7  | ETPUC8  | ETPUC9  | ETPUC10 | F |

| G |      |      |         |            |          |        |       |         | ETPUC11 | ETPUC12 | ETPUC13 | ETPUC14 | ETPUC15 | G |

| H |      |      |         |            |          |        |       | ETPUC19 | ETPUC16 | ETPUC17 | ETPUC18 | ETPUC20 | ETPUC21 | H |

| J |      |      |         |            |          |        |       |         | ETPUC22 | ETPUC23 | ETPUC24 | ETPUC26 | ETPUC27 | J |

| K | VSS  | VSS  | VSS     | VSS        |          |        |       | ETPUC25 | ETPUC28 | ETPUC29 | ETPUC30 | ETPUC31 | D_DAT15 | K |

| L | VSS  | VSS  | VSS     | VSS        |          |        |       | VD33_6  | D_DAT14 | D_DAT13 | D_DAT12 | D_DAT11 | D_DAT10 | L |

| M | VSS  | VSS  | VSS     | VSS        |          |        |       |         | D_DAT9  | D_DAT8  | D_DAT7  | D_DAT5  | VDDEH7  | M |

| N | VSS  | VSS  | VSS     | VSS        |          |        |       | VDDE10  | D_DAT6  | VDDEH6  | D_DAT2  | D_DAT3  | D_DAT4  | N |

|   | 14   | 15   | 16      | 17         | 18       | 19     | 20    | 21      | 22      | 23      | 24      | 25      | 26      |   |

**PC5674F 516-ball TEPBGA**

(as viewed from top through the package)

(2 of 4)

Figure 2-9. PC5674F 516-ball TEPBGA (3 of 4)

|    | 1       | 2       | 3          | 4          | 5       | 6       | 7     | 8     | 9     | 10      | 11      | 12       | 13     |    |

|----|---------|---------|------------|------------|---------|---------|-------|-------|-------|---------|---------|----------|--------|----|

| P  | D_ADD9  | D_ADD10 | D_ADD11    | VDDEH1     | D_WE1   | VDD33_1 |       |       |       | VDDE2   | VDDE2   | VSS      | VSS    | P  |

| R  | D_ADD12 | D_ADD13 | D_ADD14    | D_ADD15    | D_ADD16 |         |       |       |       | VDDE2   | VDDE2   | VSS      | VSS    | R  |

| T  | VDDE2   | D_ADD18 | D_ADD19    | D_ADD20    | D_ADD17 | D_CS3   |       |       |       | VDDE2   | VDDE2   | VDDE2    | VSS    | T  |

| U  | D_CS2   | JCOMP   | RDY        | MCKO       | MSEOM   | SEO0    |       |       |       | VDDE2   | VDDE2   | VDDE2    | VSS    | U  |

| V  | EVTI    | EVTO    | MDO0       | MDO2       | MDO3    |         |       |       |       |         |         |          |        | V  |

| W  | MDO4    | MDO5    | MDO6       | VDDE2      | MDO8    | MDO1    |       |       |       |         |         |          |        | W  |

| Y  | MDO7    | MDO9    | MDO10      | MDO11      | MDO12   |         |       |       |       |         |         |          |        | Y  |

| AA | MDO13   | MDO14   | MDO15      | VDD33_1    | VDDE8   | VSS     |       | PCSA5 |       | SOUTB   | VDD33_4 |          | VDDE9  | AA |

| AB | TDO     | TCK     | TMS        | VDD        | VSS     | VDDE9   | VDDE9 | SCKA  | SINB  | D_CS1   | D_ADD21 | D_ADD29  | EMIOS1 | AB |

| AC | VDDE2   | TDI     | VDD        | VSSS       | VDDE2   | PCSA1   | OUTA  | SCKB  | PCSB3 | VDDEH3  | VDDEH4  | VDD      | EMIOS0 | AC |

| AD | ENGCLK  | VDD     | VSS        | FFR_A_TX   | R_B_TX  | PCSA0   | PCSA3 | PCSB2 | D_CS0 | D_ADD22 | D_ADD25 | D_ADD28  | EMIOS2 | AD |

| AE | VDD     | VSS     | FR_A_RX    | R_B_RX     | PCSA4   | PCSB5   | SINA  | PCSB1 | D_TS  | D_ADD23 | D_ADD26 | D_ADD30  | EMIOS3 | AE |

| AF |         | VDDE2   | FR_A_TX_EN | FR_B_TX_EN | VDDEH3  | PCSA2   | PCSB4 | PCSB0 | D_TA  | D_ADD24 | D_ADD27 | D_CLKOUT | EMIOS4 | AF |

|    | 1       | 2       | 3          | 4          | 5       | 6       | 7     | 8     | 9     | 10      | 11      | 12       | 13     |    |

## PC5674F 516-ball TEPBGA

(as viewed from top through the package)

(3 of 4)

Figure 2-10. PC5674F 516-ball TEPBGA (4 of 4)

|    | 14      | 15                                                                                     | 16      | 17      | 18      | 19      | 20    | 21      | 22      | 23      | 24      | 25      | 26      |    |

|----|---------|----------------------------------------------------------------------------------------|---------|---------|---------|---------|-------|---------|---------|---------|---------|---------|---------|----|

| P  | VSS     | VSS                                                                                    | VSS     | VSS     |         |         |       | VDDE10  | ETPUB13 | D_OE    | D_ALE   | D_DAT0  | D_DAT1  | P  |

| R  | VSS     | VSS                                                                                    | VSS     | VSS     |         |         |       | ETPUB9  | ETPUB12 | ETPUB14 | ETPUB15 | D_RD_WR |         | R  |

| T  | VSS     | VSS                                                                                    | VSS     | VSS     |         |         |       | ETPUB17 | ETPUB3  | ETPUB7  | EETPUB8 | ETPUB10 | TPUB11  | T  |

| U  | VSS     | VSS                                                                                    | VSS     | VSS     |         |         |       | ETPUB23 | ETPUB1  | ETPUB2  | ETPUB4  | ETPUB5  | ETPUB6  | U  |

| V  |         | <b>PC5674F 516-ball TEPBGA</b><br>(as viewed from top through the package)<br>(4 of 4) |         |         |         |         |       |         |         |         |         |         |         |    |

| W  |         |                                                                                        |         |         |         |         |       | ETPUB21 | ETPUB22 | ETPUB16 | TCRCLKB | ETPUB0  |         | V  |

| Y  |         |                                                                                        |         |         |         |         |       | ETPUB25 | ETPUB29 | REGSEL  | ETPUB20 | ETPUB19 | ETPUB18 | W  |

| AA | VDD33_4 |                                                                                        | EMIOS23 | EMIOS31 |         | CNRXB   |       | VSS     | VDDE10  | VDD33_3 | ETPUB28 | VDDREG  | VSSSYN  | AA |

| AB | EMIOS11 | EMIOS17                                                                                | EMIOS19 | EMIOS29 | VDDE9   | VDDE9   | VDDE9 | VSS     | VDD     | ETPUB30 | VSSFL   | EXTAL   |         | AB |

| AC | EMIOS8  | EMIOS13                                                                                | EMIOS22 | EMIOS24 | EMIOS28 | CNTXB   | CNRXD | VDDEH5  | PCSC1   | VSS     | VDD     | VDDEH6  | XTAL    | AC |

| AD | EMIOS7  | EMIOS12                                                                                | EMIOS16 | EMIOS18 | EMIOS27 | CNRXA   | CNTXD | SCKC    | RXDC    | PCSC3   | VSS     | VDD     | VDDSYN  | AD |

| AE | EMIOS6  | EMIOS10                                                                                | EMIOS15 | EMIOS21 | EMIOS26 | CNTXA   | CNRXC | PCSC0V  | SINC    | PCSC2   | PCSC5   | VSS     | DD      | AE |

| AF | EMIOS5  | EMIOS9                                                                                 | EMIOS20 | EMIOS14 | EMIOS25 | EMIOS30 | CNTXC | SOUTC   | VDDEH4P | TXDC    | CSC4    | VDDEH5  |         | AF |

|    | 14      | 15                                                                                     | 16      | 17      | 18      | 19      | 20    | 21      | 22      | 23      | 24      | 25      | 26      |    |

### 2.3 Signal Properties and Muxing

See Appendix A, Signal Properties and Muxing, for a listing and description of the pin functions and properties.

### 3. ELECTRICAL CHARACTERISTICS

This section contains detailed information on power considerations, DC/AC electrical characteristics, and AC timing specifications for the PC5674F.

The electrical specifications are preliminary and are from previous designs, design simulations, or initial evaluation. These specifications may not be fully tested or guaranteed at this stage of the product life cycle, however for production silicon these specifications will be met. Finalized specifications will be published after complete characterization and device qualifications have been completed.

#### 3.1 Maximum Ratings

**Table 3-1.** Absolute Maximum Ratings<sup>(1)</sup>

| Spec | Characteristic                                                                       | Symbol                   | Min               | Max                   | Unit |

|------|--------------------------------------------------------------------------------------|--------------------------|-------------------|-----------------------|------|

| 1    | 1.2 V Core Supply Voltage                                                            | $V_{DD}$                 | -0.3              | 2.0 <sup>(2)</sup>    | V    |

| 2    | SRAM Standby Voltage                                                                 | $V_{STBY}$               | -0.3              | 6.4 <sup>(3)(4)</sup> | V    |

| 3    | Clock Synthesizer Voltage                                                            | $V_{DDSYN}$              | -0.3              | 5.3 <sup>(4)(5)</sup> | V    |

| 4    | I/O Supply Voltage (I/O buffers and predrivers)                                      | $V_{DD33}$               | -0.3              | 5.3 <sup>(4)(5)</sup> | V    |

| 5    | Analog Supply Voltage (reference to $V_{SSA}$ <sup>(6)</sup> )                       | $V_{DDA}$ <sup>(7)</sup> | -0.3              | 6.4 <sup>(3)(4)</sup> | V    |

| 6    | I/O Supply Voltage (fast I/O pads)                                                   | $V_{DDE}$                | -0.3              | 5.3 <sup>(4)(5)</sup> | V    |

| 7    | I/O Supply Voltage (medium I/O pads)                                                 | $V_{DDEH}$               | -0.3              | 6.4 <sup>(3)(4)</sup> | V    |

| 8    | Voltage Regulator Input Supply Voltage                                               | $V_{DDREG}$              | -0.3              | 6.4 <sup>(3)(4)</sup> | V    |

| 9    | Analog Reference High Voltage (reference to $V_{RL}$ <sup>(8)</sup> )                | $V_{RH}$ <sup>(9)</sup>  | -0.3              | 6.4 <sup>(3)(4)</sup> | V    |

| 10   | $V_{SS}$ to $V_{SSA}$ <sup>(8)</sup> Differential Voltage                            | $V_{SS} - V_{SSA}$       | -0.1              | 0.1                   | V    |

| 11   | $V_{REF}$ Differential Voltage                                                       | $V_{RH} - V_{RL}$        | -0.3              | 6.4 <sup>(3)(4)</sup> | V    |

| 12   | $V_{RL}$ to $V_{SSA}$ Differential Voltage                                           | $V_{RL} - V_{SSA}$       | -0.3              | 0.3                   | V    |

| 13   | $V_{DD33}$ to $V_{DDSYN}$ Differential Voltage                                       | $V_{DD33} - V_{DDSYN}$   | -0.1              | 0.1                   | V    |

| 14   | $V_{SSSYN}$ to $V_{SS}$ Differential Voltage                                         | $V_{SSSYN} - V_{SS}$     | -0.1              | 0.1                   | V    |

| 15   | Maximum Digital Input Current <sup>(10)</sup> (per pin, applies to all digital pins) | $I_{MAXD}$               | -3.11             | 3 <sup>(11)</sup>     | mA   |

| 16   | Maximum Analog Input Current <sup>(12)</sup> (per pin, applies to all analog pins)   | $I_{MAXA}$               | -3 <sup>(7)</sup> | 3 <sup>(7)(11)</sup>  | mA   |

| 17   | Maximum Operating Temperature Range <sup>(13)</sup> – Die Junction Temperature       | $T_J$                    | -55.0             | 150.0                 | °C   |

| 18   | Storage Temperature Range                                                            | $T_{stg}$                | -55.0             | 150.0                 | °C   |

| 19   | Maximum Solder Temperature <sup>(14)</sup><br>Pb-free package<br>SnPb package        | $T_{sdr}$                | –                 | 260.0<br>245.0        | °C   |

| 20   | Moisture Sensitivity Level <sup>(15)</sup>                                           | MSL                      | –                 | 3                     | –    |

Notes:

1. Functional operating conditions are given in the DC electrical specifications. Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the listed maxima may affect device reliability or cause permanent damage to the device.

2. 2.0 V for 10 hours cumulative time, 1.2V +10% for time remaining.

3. 6.4 V for 10 hours cumulative time, 5.0V +10% for time remaining.

4. Voltage overshoots during a high-to-low or low-to-high transition must not exceed 10 seconds per instance.

5. 5.3 V for 10 hours cumulative time, 3.3V +10% for time remaining.

6. PC5674F has two analog power supply pins on the pinout: VDDA\_A and VDDA\_B.

7. PC5674F has two analog ground supply pins on the pinout: VSSA\_A and VSSA\_B.

8. PC5674F has two analog low reference voltage pins on the pinout: VRL\_A and VRL\_B.

9. PC5674F has two analog high reference voltage pins on the pinout: VRH\_A and VRH\_B.

10. Total injection current for all pins must not exceed 25 mA at maximum operating voltage.

11. Injection current of  $\pm 5$  mA allowed for limited duration for analog (ADC) pads and digital 5 V pads. The maximum accumulated time at this current shall be 60 hours. This includes an assumption of a 5.25 V maximum analog or  $V_{DDEH}$  supply when under this stress condition.

12. Total injection current for all analog input pins must not exceed 15 mA.

13. Lifetime operation at these specification limits is not guaranteed.

14. Solder profile per CDF-AEC-Q100.

15. Moisture sensitivity per JEDEC test method A112.

## 3.2 Thermal Characteristics

**Table 3-2.** Thermal Characteristics, 416-pin TEPBGA Package<sup>(1)</sup>

| Characteristic                                                                   | Symbol           | Value | Unit |

|----------------------------------------------------------------------------------|------------------|-------|------|

| Junction to Ambient <sup>(2)(3)</sup> Natural Convection (Single layer board)    | $R_{\theta JA}$  | 24    | °C/W |

| Junction to Ambient <sup>(2)(4)</sup> Natural Convection (Four layer board 2s2p) | $R_{\theta JA}$  | 18    | °C/W |

| Junction to Ambient (@200 ft./min., Single layer board)                          | $R_{\theta JMA}$ | 19    | °C/W |

| Junction to Ambient (@200 ft./min., Four layer board 2s2p)                       | $R_{\theta JMA}$ | 14    | °C/W |

| Junction to Board <sup>(5)</sup>                                                 | $R_{\theta JB}$  | 9     | °C/W |

| Junction to Case <sup>(6)</sup>                                                  | $R_{\theta JC}$  | 6     | °C/W |

| Junction to Package Top <sup>(7)</sup> Natural Convection                        | $\Psi_{JT}$      | 2     | °C/W |

Notes:

1. Thermal characteristics are targets based on simulation that are subject to change per device characterization. This data is PRELIMINARY based on similar package used on other devices.

2. Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

3. Per JEDEC JESD51-2 with the single layer board horizontal. Board meets JESD51-9 specification.

4. Per JEDEC JESD51-6 with the board horizontal.

5. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

6. Indicates the average thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1) with the cold plate temperature used for the case temperature.

7. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2.

**Table 3-3.** Thermal Characteristics, 516-pin Package<sup>(1)</sup>

| Characteristic                                                                   | Symbol           | Value | Unit |

|----------------------------------------------------------------------------------|------------------|-------|------|

| Junction to Ambient <sup>(2)(3)</sup> Natural Convection (Single layer board)    | $R_{\theta JA}$  | 25    | °C/W |

| Junction to Ambient <sup>(2)(4)</sup> Natural Convection (Four layer board 2s2p) | $R_{\theta JA}$  | 18    | °C/W |

| Junction to Ambient (@200 ft./min., Single layer board)                          | $R_{\theta JMA}$ | 20    | °C/W |

| Junction to Ambient (@200 ft./min., Four layer board 2s2p)                       | $R_{\theta JMA}$ | 15    | °C/W |

| Junction to Board <sup>(5)</sup>                                                 | $R_{\theta JB}$  | 10    | °C/W |

| Junction to Case <sup>(6)</sup>                                                  | $R_{\theta JC}$  | 6     | °C/W |

| Junction to Package Top <sup>(7)</sup> Natural Convection                        | $\Psi_{JT}$      | 2     | °C/W |

Notes: 1. Thermal characteristics are targets based on simulation that are subject to change per device characterization. This data is PRELIMINARY based on similar package used on other devices.

2. Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

3. Per JEDEC JESD51-2 with the single layer board horizontal. Board meets JESD51-9 specification.

4. Per JEDEC JESD51-6 with the board horizontal.

5. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

6. Indicates the average thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1) with the cold plate temperature used for the case temperature.

7. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2.

**Table 3-4.** Thermal Characteristics, 324-pin Package<sup>(1)</sup>

| PC5674F Thermal Characteristic                                                   | Symbol           | Value | Unit |

|----------------------------------------------------------------------------------|------------------|-------|------|

| Junction to ambient <sup>(2)(3)</sup> natural convection (one-layer board)       | $R_{\theta JA}$  | 29    | °C/W |

| Junction to ambient <sup>(1)(4)</sup> natural convection (four-layer board 2s2p) | $R_{\theta JA}$  | 19    | °C/W |

| Junction to ambient (@200 ft./min., one-layer board)                             | $R_{\theta JMA}$ | 23    | °C/W |

| Junction to ambient (@200 ft./min., four-layer board 2s2p)                       | $R_{\theta JMA}$ | 16    | °C/W |

| Junction to board <sup>(5)</sup> (four-layer board 2s2p)                         | $R_{\theta JB}$  | 10    | °C/W |

| Junction to case <sup>(6)</sup>                                                  | $R_{\theta JC}$  | 7     | °C/W |

| Junction to package top <sup>(7)</sup> , natural convection                      | $\Psi_{JT}$      | 2     | °C/W |

Notes: 1. Thermal characteristics are targets based on simulation that are subject to change per device characterization. This data is PRELIMINARY based on similar package used on other devices.

2. Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

3. Per SEMI G38-87 and JEDEC JESD51-2 with the single-layer board horizontal.

4. Per JEDEC JESD51-6 with the board horizontal.

5. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

6. Indicates the average thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1) with the cold plate temperature used for the case temperature.

7. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2.

### 3.2.1 General Notes for Specifications at Maximum Junction Temperature

An estimation of the chip junction temperature,  $T_J$ , can be obtained from the equation:

$$T_J = T_A + (R_{\theta JA} * P_D) \text{ Eqn. 1}$$

where:

$T_A$  = ambient temperature for the package (°C)

$R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)

$P_D$  = power dissipation in the package (W)

The junction to ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. Unfortunately, there are two values in common usage: the value determined on a single layer board and the value obtained on a board with two planes. For packages such as the TEPBGA, these values can be different by a factor of two. Which value is closer to the application depends on the power dissipated by other components on the board. The value obtained on a single layer board is appropriate for the tightly packed printed circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated.

When a heat sink is used, the thermal resistance is expressed as the sum of a junction to case thermal resistance and a case to ambient thermal resistance:

$$R_{\theta JA} = R_{\theta JC} + R_{\theta CA} \text{ Eqn. 2}$$

where:

$R_{\theta JA}$  = junction to ambient thermal resistance (°C/W)

$R_{\theta JC}$  = junction to case thermal resistance (°C/W)

$R_{\theta CA}$  = case to ambient thermal resistance (°C/W)

$R_{\theta JC}$  is device related and cannot be influenced by the user.

The user controls the thermal environment to change the case to ambient thermal resistance,  $R_{\theta CA}$ . For instance, the user can change the size of the heat sink, the air flow around the device, the interface material, the mounting arrangement on printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device.

To determine the junction temperature of the device in the application when heat sinks are not used, the Thermal Characterization Parameter ( $\psi_{JT}$ ) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using the following equation:

$$T_J = T_T + (\psi_{JT} * P_D) \text{ Eqn. 3}$$

where:

$T_T$  = thermocouple temperature on top of the package (°C)

$\psi_{JT}$  = thermal characterization parameter (°C/W)

$P_D$  = power dissipation in the package (W)

The thermal characterization parameter is measured per JESD51-2 specification using a 40 gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over about 1 mm. of wire extending from the junction.

The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.

**References:**

Semiconductor Equipment and Materials International

3081 Zanker Road

San Jose, CA 95134

(408) 943-6900

MIL-SPEC and EIA/JESD (JEDEC) specifications are available from Global Engineering Documents at 800-854-7179 or 303-397-7956.

JEDEC specifications are available on the WEB at <http://www.jedec.org>.

- C.E. Triplett and B. Joiner, "An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module," Proceedings of SemiTherm, San Diego, 1998, pp. 47-54.

- G. Kromann, S. Shidore, and S. Addison, "Thermal Modeling of a PBGA for Air-Cooled Applications," Electronic Packaging and Production, pp. 53-58, March 1998.

- B. Joiner and V. Adams, "Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling," Proceedings of SemiTherm, San Diego, 1999, pp. 212-220

### 3.3 EMI (Electromagnetic Interference) Characteristics

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions, go to [www.freescale.com](http://www.freescale.com) and perform a keyword search for "radiated emissions." The following tables list the values of the device's radiated emissions operating behaviors.

**Table 3-5.** EMC Radiated Emissions Operating Behaviors: 416 BGA

| Symbol        | Description                                           | Conditions                                                                                                                                                             | $f_{osc}$<br>$f_{sys}$                                           | Frequency band<br>(MHz) | Level<br>(max.) | Unit                   | Notes  |

|---------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------|-----------------|------------------------|--------|

| $V_{RE\_TEM}$ | Radiated emissions, electric field and magnetic field | $V_{DD} = 1.2 \text{ V}$<br>$V_{DDE} = 3.3 \text{ V}$<br>$V_{DDEH} = 5 \text{ V}$<br>$T_A = 25^\circ\text{C}$<br>416 BGA<br>EBI off<br>CLK on<br>FM off                | 40 MHz crystal<br>264 MHz<br>( $f_{EBI\_CAL} = 66 \text{ MHz}$ ) | 0.15–50                 | 26              | $\text{dB}\mu\text{V}$ | (1)    |

|               |                                                       |                                                                                                                                                                        |                                                                  | 50–150                  | 30              |                        |        |

|               |                                                       |                                                                                                                                                                        |                                                                  | 150–500                 | 34              |                        |        |

|               |                                                       |                                                                                                                                                                        |                                                                  | 500–1000                | 30              |                        |        |

|               |                                                       |                                                                                                                                                                        |                                                                  | IEC and SAE level       | $I^2$           |                        | (1)(3) |

| $V_{RE\_TEM}$ | Radiated emissions, electric field and magnetic field | $V_{DD} = 1.2 \text{ V}$<br>$V_{DDE} = 3.3 \text{ V}$<br>$V_{DDEH} = 5 \text{ V}$<br>$T_A = 25^\circ\text{C}$<br>416 BGA<br>EBI off<br>CLK off<br>FM on <sup>(4)</sup> | 40 MHz crystal<br>264 MHz<br>( $f_{EBI\_CAL} = 66 \text{ MHz}$ ) | 0.15–50                 | 24              | $\text{dB}\mu\text{V}$ | (1)    |

|               |                                                       |                                                                                                                                                                        |                                                                  | 50–150                  | 25              |                        |        |

|               |                                                       |                                                                                                                                                                        |                                                                  | 150–500                 | 25              |                        |        |

|               |                                                       |                                                                                                                                                                        |                                                                  | 500–1000                | 21              |                        |        |

|               |                                                       |                                                                                                                                                                        |                                                                  | IEC and SAE level       | $K^5$           |                        | (1)(3) |

Notes: 1. Determined according to IEC Standard 61967-2, Measurement of Radiated Emissions—TEM Cell and Wideband TEM Cell Method, and SAE Standard J1752-3, Measurement of Radiated Emissions from Integrated Circuits—TEM/Wideband TEM (GTEM) Cell Method.

2.  $I = 36 \text{ dB}\mu\text{V}$

3. Specified according to Annex D of IEC Standard 61967-2, Measurement of Radiated Emissions—TEM Cell and Wideband TEM Cell Method, and Appendix D of SAE Standard J1752-3, Measurement of Radiated Emissions from Integrated Circuits—TEM/Wideband TEM (GTEM) Cell Method.

4. "FM on" = FM depth of  $\pm 2\%$

5.  $K = 30 \text{ dB}\mu\text{V}$

**Table 3-6.** EMC Radiated Emissions Operating Behaviors: 516 BGA

| Symbol        | Description                                           | Conditions                                                                                                                                                        | $f_{osc}$<br>$f_{sys}$                                     | Frequency band (MHz) | Level (max) | Unit                   | Notes  |

|---------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------|-------------|------------------------|--------|

| $V_{RE\_TEM}$ | Radiated emissions, electric field and magnetic field | $V_{DD} = 1.2 \text{ V}$<br>$V_{DDE} = 3.3 \text{ V}$<br>$V_{DDEH} = 5 \text{ V}$<br>$T_A = 25^\circ\text{C}$<br>516 BGA<br>EBI on<br>CLK on<br>FM off            | 40 MHz crystal 264 MHz ( $f_{EBI\_CAL} = 66 \text{ MHz}$ ) | 0.15–50              | 40          | $\text{dB}\mu\text{V}$ | (1)    |

|               |                                                       |                                                                                                                                                                   |                                                            | 50–150               | 48          |                        |        |

|               |                                                       |                                                                                                                                                                   |                                                            | 150–500              | 48          |                        |        |

|               |                                                       |                                                                                                                                                                   |                                                            | 500–1000             | 47          |                        |        |

|               |                                                       |                                                                                                                                                                   |                                                            | IEC and SAE level    | $G^2$       | –                      | (1)(3) |

| $V_{RE\_TEM}$ | Radiated emissions, electric field and magnetic field | $V_{DD} = 1.2 \text{ V}$<br>$V_{DDE} = 3.3 \text{ V}$<br>$V_{DDEH} = 5 \text{ V}$<br>$T_A = 25^\circ\text{C}$<br>516 BGA<br>EBI on<br>CLK on FM on <sup>(4)</sup> | 40 MHz crystal 264 MHz ( $f_{EBI\_CAL} = 66 \text{ MHz}$ ) | 0.15–50              | 40          | $\text{dB}\mu\text{V}$ | (1)    |

|               |                                                       |                                                                                                                                                                   |                                                            | 50–150               | 44          |                        |        |

|               |                                                       |                                                                                                                                                                   |                                                            | 150–500              | 41          |                        |        |

|               |                                                       |                                                                                                                                                                   |                                                            | 500–1000             | 36          |                        |        |

|               |                                                       |                                                                                                                                                                   |                                                            | IEC and SAE level    | $G^2$       | –                      | (1)(3) |

Notes: 1. Determined according to IEC Standard 61967-2, Measurement of Radiated Emissions—TEM Cell and Wideband TEM Cell Method, and SAE Standard J1752-3, Measurement of Radiated Emissions from Integrated Circuits—TEM/Wideband TEM (GTEM) Cell Method.

2.  $G = 48 \text{ dB}\mu\text{V}$

3. Specified according to Annex D of IEC Standard 61967-2, Measurement of Radiated Emissions—TEM Cell and Wideband TEM Cell Method, and Appendix D of SAE Standard J1752-3, Measurement of Radiated Emissions from Integrated Circuits—TEM/Wideband TEM (GTEM) Cell Method.

4. “FM on” = FM depth of  $\pm 2\%$

### 3.4 ESD Characteristics

**Table 3-7.** ESD Ratings<sup>(1)</sup><sup>(2)</sup>

| Spec | Characteristic                     | Symbol    | Value                        | Unit |

|------|------------------------------------|-----------|------------------------------|------|

| 1    | ESD for Human Body Model (HBM)     | $V_{HBM}$ | 2000                         | V    |

| 2    | ESD for Charged Device Model (CDM) | $V_{CDM}$ | 750 (corners)<br>500 (other) | V    |

Notes: 1. All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

2. A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

### 3.5 PMC/POR/LVI Electrical Specifications

**Note:** For ADC internal resource measurements, see [Table 3-18](#) in [Section 3.9.1 "ADC Internal Resource Measurements" on page 30](#).

**Table 3-8.** PMC Operating conditions

| Name        | Parameter                                               | Condition           | Min  | Typ | Max  | Unit | Note                |

|-------------|---------------------------------------------------------|---------------------|------|-----|------|------|---------------------|

| $V_{DDREG}$ | Supply voltage $V_{DDREG}$<br>5V nominal                | LDO5V / SMPS5V mode | 4.5  | 5   | 5.5  | V    | <a href="#">(1)</a> |

| $V_{DDREG}$ | Supply voltage $V_{DDREG}$<br>3V nominal                | LDO3V mode          | 3.0  | 3.3 | 3.6  | V    | <a href="#">(1)</a> |

| $V_{DD33}$  | Supply voltage $V_{DDSYN}$ / $V_{DD33}$<br>3.3V nominal | LDO3V mode          | 3.0  | 3.3 | 3.6  | V    | <a href="#">(2)</a> |

| $V_{DD}$    | Core supply voltage                                     | —                   | 1.14 | 1.2 | 1.32 | V    | <a href="#">(3)</a> |

Notes:

1. Voltage should be higher than maximum  $V_{LVDREG}$  to avoid LVD event

2. Applies to both  $VDD33$  (flash supply) and  $VDDSYN$  (PLL supply) pads. Voltage should be higher than maximum  $V_{LVD33}$  to avoid LVD event

3. Voltage should be higher than maximum  $V_{LVD12}$  to avoid LVD event

**Note:** In the following table, "untrimmed" means "at reset" and "trimmed" means "after reset"

**Table 3-9.** PMC Electrical Specifications

| ID | Name            | Parameter                                                                                                                                                | Min                  | Typ           | Max                  | Unit |

|----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------|----------------------|------|

| 1  | $V_{BG}$        | Nominal bandgap reference voltage                                                                                                                        | 0.608                | 0.620         | 0.632                | V    |

| 1a | —               | Untrimmed bandgap reference voltage                                                                                                                      | $V_{BG} - 5\%$       | $V_{BG}$      | $V_{BG} + 5\%$       | V    |

| 2  | $V_{DD12OUT}$   | Nominal VRC regulated 1.2V output VDD                                                                                                                    | —                    | 1.27          | —                    | V    |

| 2a | —               | Untrimmed VRC 1.2V output variation before band gap trim (unloaded)<br><b>Note:</b> Voltage should be higher than maximum $V_{LVD12}$ to avoid LVD event | $V_{DD12OUT} - 14\%$ | $V_{DD12OUT}$ | $V_{DD12OUT} + 10\%$ | V    |

| 2b | —               | Trimmed VRC 1.2V output variation after band gap trim (REGCTL load max. 20mA, VDD load max. 1A) <a href="#">(1)</a>                                      | $V_{DD12OUT} - 10\%$ | $V_{DD12OUT}$ | $V_{DD12OUT} + 5\%$  | V    |

| 2c | $V_{STEPV12}$   | Trimming step $V_{DD12OUT}$                                                                                                                              | —                    | 10            | —                    | mV   |

| 3  | $V_{PORC}$      | POR rising VDD 1.2V                                                                                                                                      | —                    | 0.7           | —                    | V    |

| 3a | —               | POR VDD 1.2V variation                                                                                                                                   | $V_{PORC} - 30\%$    | $V_{PORC}$    | $V_{PORC} + 30\%$    |      |

| 3b | —               | POR 1.2V hysteresis                                                                                                                                      | —                    | 75            | —                    | mV   |

| 4  | $V_{LVD12}$     | Nominal rising LVD 1.2V<br><b>Note:</b> $\sim V_{DD12OUT} \times 0.87$                                                                                   | —                    | 1.100         | —                    | V    |

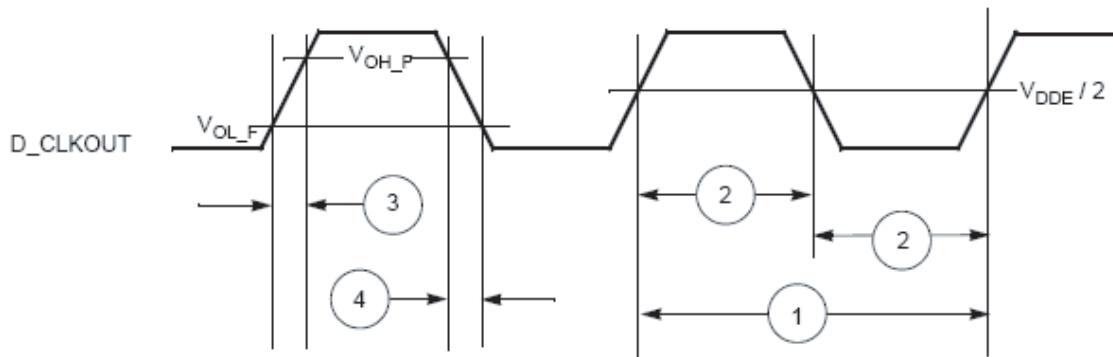

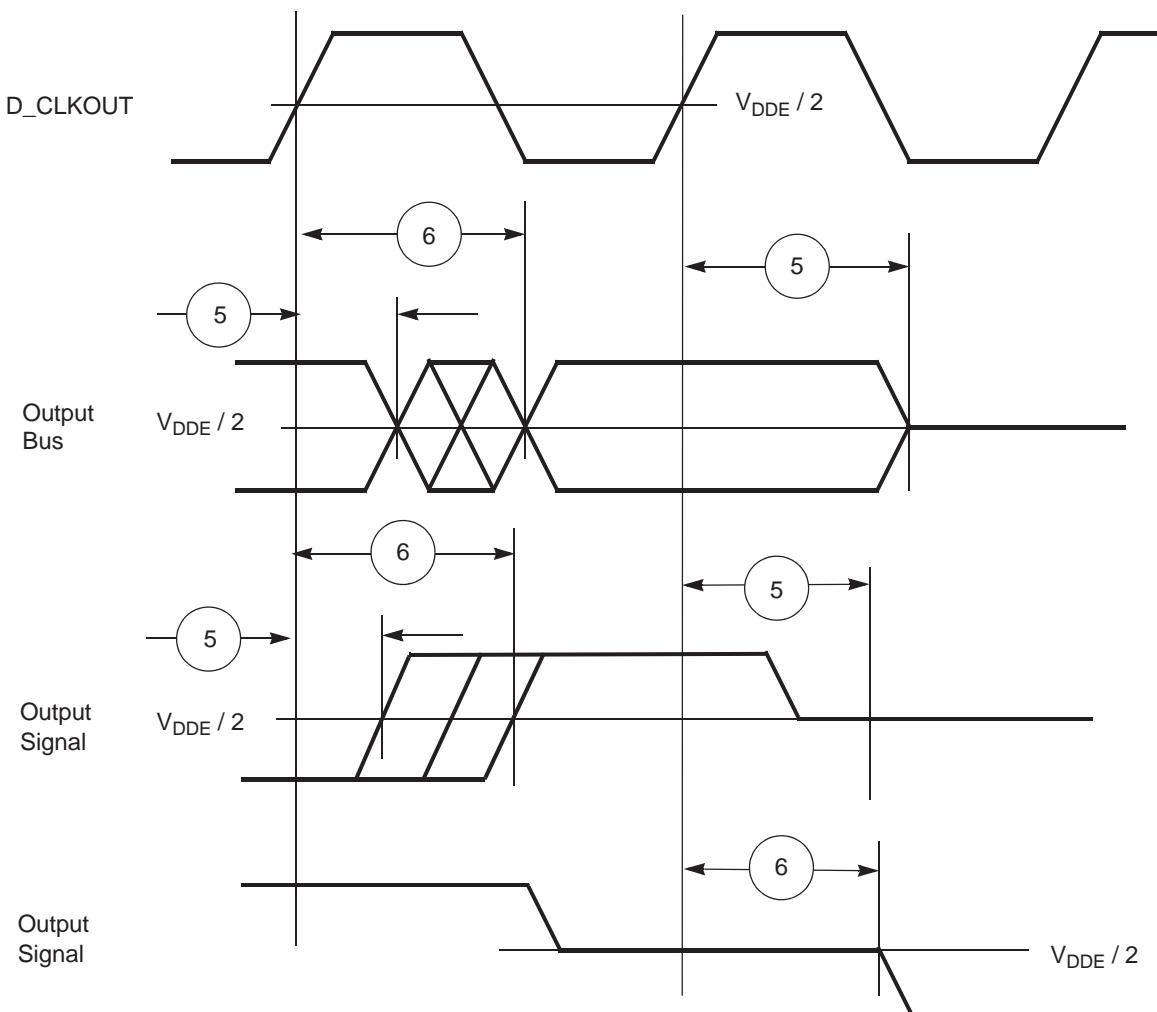

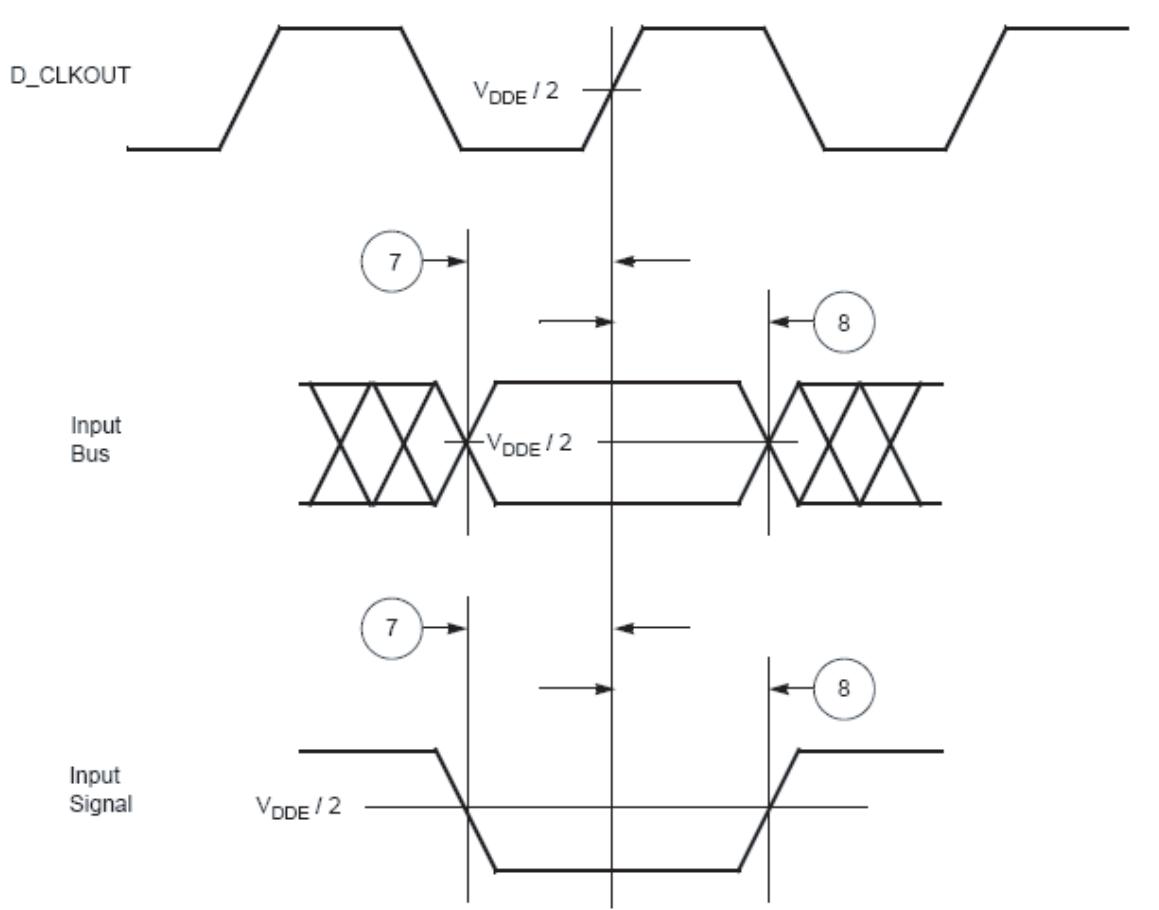

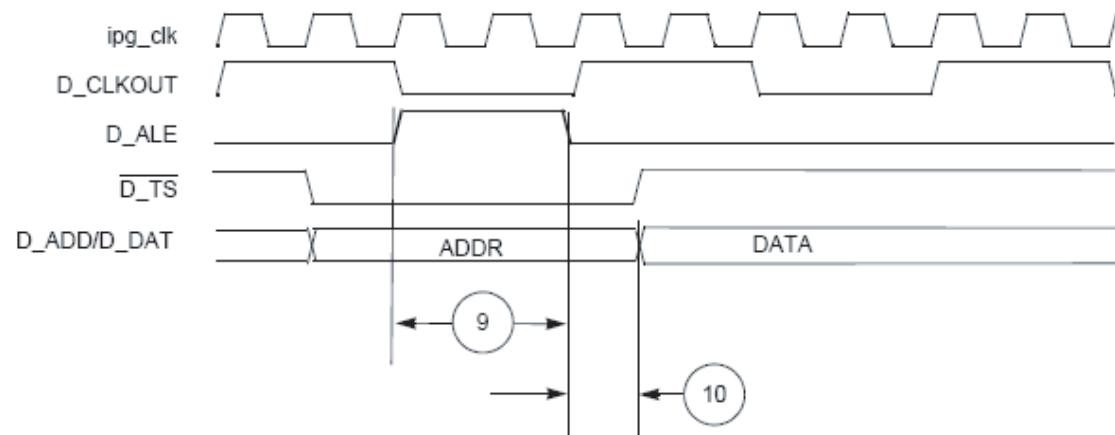

| 4a | —               | Untrimmed LVD 1.2V variation before band gap trim<br><b>Note:</b> Rising VDD                                                                             | $V_{LVD12} - 6\%$    | $V_{LVD12}$   | $V_{LVD12} + 6\%$    | V    |