## LM5041 Cascaded PWM Controller

Check for Samples: LM5041

#### **FEATURES**

- Internal Start-up Bias Regulator

- Programmable Line Under-Voltage Lockout (UVLO) with Adjustable Hysteresis

- Current Mode Control

- Internal Error Amplifier with Reference

- Dual Mode Over-Current Protection

- · Leading Edge Blanking

- Programmable Push-Pull Overlap or Dead Time

- Internal 1.5A Push-Pull Gate Drivers

- Programmable Soft-start

- Programmable Oscillator with Sync Capability

- Precision Reference

- Thermal Shutdown

## **APPLICATIONS**

- Telecommunication Power Converters

- Industrial Power Converters

- Multi-Output Power Converters

- +42V Automotive Systems

#### **PACKAGES**

- TSSOP-16

- WSON-16 (5x5 mm) Thermally Enhanced

#### DESCRIPTION

The LM5041 PWM controller contains all of the features necessary to implement either current-fed or voltage-fed push-pull or bridge power converters. These "Cascaded" topologies are well suited for multiple output and higher power applications. The LM5041's four control outputs include: the buck stage controls (HD and LD) and the push-pull control outputs (PUSH and PULL). Push-pull outputs are driven at 50% nominal duty cycle at one half of the switching frequency of the buck stage and can be configured for either a specified overlap time (for current-fed applications) or a specified both-off time (for voltage-fed applications). Push-pull stage MOSFETs can be driven directly from the internal gate drivers while the buck stage requires an external driver such as the LM5102. The LM5041 includes a high-voltage start-up regulator that operates over a wide input range of 15V to 100V. The PWM controller is designed for high-speed capability including an oscillator frequency range up to 1 MHz and total propagation delays of less than 100ns. Additional features include: line Under-Voltage Lockout (UVLO), soft-start, an error amplifier, precision voltage reference, and thermal shutdown.

₩.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

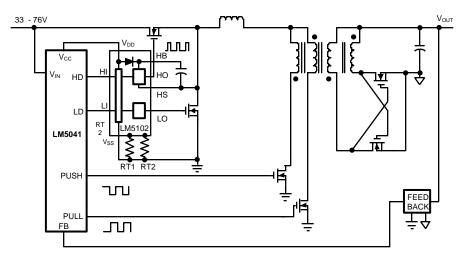

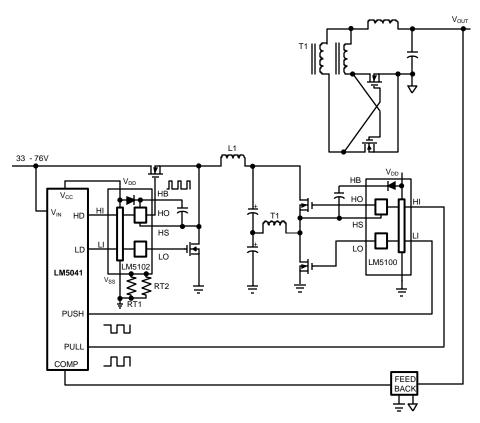

# **Typical Application Circuit**

Figure 1. Simplified Cascaded Push-Pull Power Converter

# **Connection Diagram**

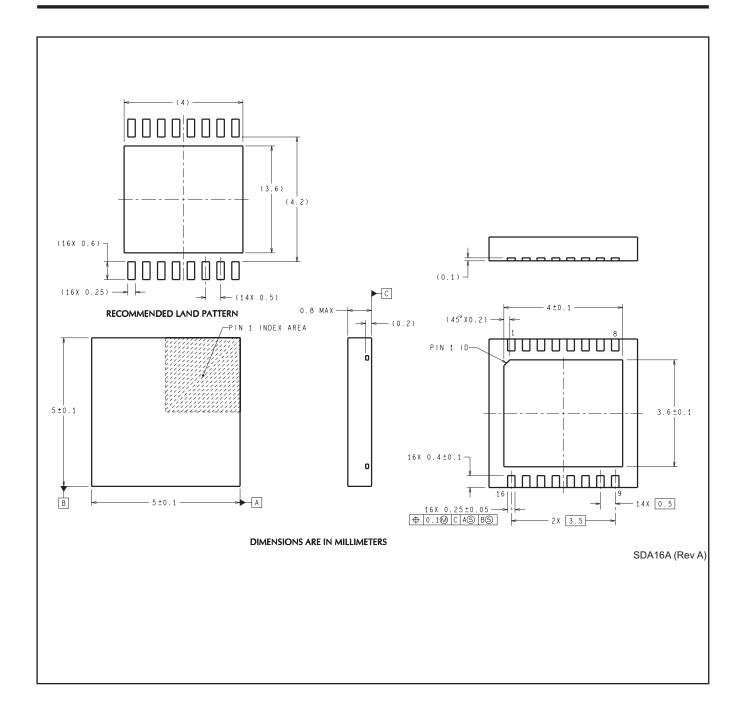

Figure 2. 16-Lead TSSOP, WSON Package Number PW, NHQ0016A

## **PIN DESCRIPTION**

| PIN         | NAME            | DESCRIPTION                                                                     | APPLICATION INFORMATION                                                                                                                                                                                                                                                                                |

|-------------|-----------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | V <sub>IN</sub> | Source Input Voltage                                                            | Input to start-up regulator. Input range 15V to 100V.                                                                                                                                                                                                                                                  |

| 2           | FB              | Feedback Signal                                                                 | Inverting input for the internal error amplifier. The non-inverting input is connected to a 0.75V reference.                                                                                                                                                                                           |

| 3           | COMP            | Output of the Internal Error Amplifier                                          | There is an internal $5k\Omega$ resistor pull-up on this pin. The error amplifier provides an active sink.                                                                                                                                                                                             |

| 4           | REF             | Precision 5 volt reference output                                               | Maximum output current: 10mA. Locally decouple with a $0.1\mu F$ capacitor. Reference stays low until the line UV and the $V_{CC}$ UV are satisfied.                                                                                                                                                   |

| 5           | HD              | Main Buck PWM control output                                                    | Buck switch PWM control output. The maximum duty cycle clamp for this output corresponds to an off time of typically 240ns per cycle. The LM5101 or LM5102 Buck stage gate driver can be used to level shift and drive the Buck switch.                                                                |

| 6           | LD              | Sync Switch control output                                                      | Sync Switch control output. Inversion of HD output. The LM5101 or LM5102 lower drive can be used to drive the synchronous rectifier switch.                                                                                                                                                            |

| 7           | V <sub>CC</sub> | Output from the internal high voltage start-up regulator. Regulated to 9 volts. | If an auxiliary winding raises the voltage on this pin above<br>the regulation setpoint, the internal start-up regulator will<br>shutdown, reducing the IC power dissipation.                                                                                                                          |

| 8           | PUSH            | Output of the push-pull drivers                                                 | Output of the push-pull gate driver. Output capability of 1.5A peak .                                                                                                                                                                                                                                  |

| 9           | PULL            | Output of the push-pull drivers                                                 | Output of the push-pull gate driver. Output capability of 1.5A peak.                                                                                                                                                                                                                                   |

| 10          | PGND            | Power ground                                                                    | Connect directly to analog ground.                                                                                                                                                                                                                                                                     |

| 11          | AGND            | Analog ground                                                                   | Connect directly to power ground.                                                                                                                                                                                                                                                                      |

| 12          | cs              | Current sense input                                                             | Current sense input to the PWM comparator (CM control). There is a 50ns leading edge blanking on this pin. Using separate dedicated comparators, if CS exceeds 0.5V the outputs will go into cycle by cycle current limit. If CS exceeds 0.6V the outputs will be disabled and a soft-start commenced. |

| 13          | SS              | Soft-start control                                                              | An external capacitor and an internal 10uA current source, set the soft-start ramp. The controller will enter a low power state if the SS pin is below the shutdown threshold of 0.45V                                                                                                                 |

| 14          | TIME            | Push-Pull overlap and dead time control                                         | An external resistor (R <sub>SET</sub> ) sets the overlap time or dead time for the push-pull outputs. A resistor connected between TIME and GND produces overlap. A resistor connected between TIME and REF produces dead time.                                                                       |

| 15          | RT / SYNC       | Oscillator timing resistor pin and sync                                         | An external resistor sets the oscillator frequency. This pin will also accept an external oscillator.                                                                                                                                                                                                  |

| 16          | UVLO            | Line Under-Voltage Shutdown                                                     | An external divider from the power converter source sets the shutdown levels. Threshold of operation equals 2.5V. Hysteresis is set by a switched internal current source (20µA).                                                                                                                      |

| WSON<br>DAP | SUB             | Die substrate                                                                   | The exposed die attach pad on the WSON package should be connected to a PCB thermal pad at ground potential. For additional information on using Texas Instruments' No Pull Back WSON package, please refer to LLP Application Note AN-1187 SNOA401.                                                   |

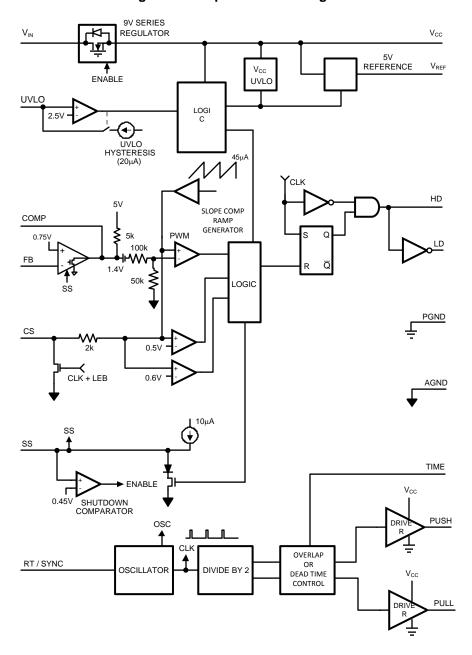

## **Block Diagram**

Figure 3. Simplified Block Diagram

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

www.ti.com

# Absolute Maximum Ratings(1)(2)

| V <sub>IN</sub> to GND    | 100V            |       |

|---------------------------|-----------------|-------|

| V <sub>CC</sub> to GND    | 16V             |       |

| All Other Inputs to GND   | -0.3 to 7V      |       |

| Junction Temperature      | 150°C           |       |

| Storage Temperature Range | -65°C to +150°C |       |

| ESD Rating                | 2 kV            |       |

| Lead temperature (3)      |                 |       |

| Wave                      | 4 seconds       | 260°C |

| Infrared                  | 10 seconds      | 240°C |

| Vapor Phase               | 75 seconds      | 219°C |

- (1) Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is intended to be functional. For verified specifications and test conditions, see the Electrical Characteristics.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

- (3) For detailed information on soldering plastic TSSOP and WSON packages, refer to the Packaging Data Book available from Texas Instruments.

# Operating Ratings<sup>(1)</sup>

| V <sub>IN</sub>      | 15 to 90V       |

|----------------------|-----------------|

| Junction Temperature | -40°C to +125°C |

<sup>(1)</sup> Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is intended to be functional. For verified specifications and test conditions, see the Electrical Characteristics.

#### **Electrical Characteristics**

Specifications with standard typeface are for  $T_J$  = 25°C, and those with **boldface** type apply over full **Operating Junction Temperature range**.  $V_{IN}$  = 48V,  $V_{CC}$  = 10V, RT = 26.7k $\Omega$ ,  $R_{SET}$  = 20k $\Omega$ ) unless otherwise stated.<sup>(1)</sup>

| Symbol                 | Parameter                                                                             | Conditions                        | s Min Typ                      |                             | Max   | Units |

|------------------------|---------------------------------------------------------------------------------------|-----------------------------------|--------------------------------|-----------------------------|-------|-------|

| Startup Reg            | julator                                                                               |                                   |                                |                             |       |       |

| V <sub>CC</sub> Reg    | V <sub>CC</sub> Regulation                                                            | open circuit                      | 8.7                            | 9                           | 9.3   | V     |

|                        | V <sub>CC</sub> Current Limit                                                         | See <sup>(2)</sup>                | 15                             | 25                          |       | mA    |

| I-V <sub>IN</sub>      | Startup Regulator<br>Leakage (external Vcc<br>Supply)                                 | V <sub>IN</sub> = 100V            |                                | 145                         | 500   | μА    |

|                        | Shutdown Current (lin)                                                                | UVLO = 0V, V <sub>CC</sub> = open |                                | 350                         | 450   | μA    |

| V <sub>CC</sub> Supply | •                                                                                     |                                   |                                |                             |       |       |

|                        | V <sub>CC</sub> Under-voltage<br>Lockout Voltage (positive<br>going V <sub>cc</sub> ) |                                   | V <sub>CC</sub> Reg -<br>400mV | V <sub>CC</sub> Reg - 275mV |       | V     |

|                        | V <sub>CC</sub> Under-voltage<br>Hysteresis                                           |                                   | 1.7                            | 2.1                         | 2.6   | V     |

|                        | Supply Current (I <sub>CC</sub> )                                                     | $C_L = 0$                         |                                | 3                           | 4     | mA    |

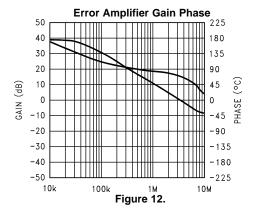

| Error Ampli            | fier                                                                                  |                                   |                                |                             |       |       |

| GBW                    | Gain Bandwidth                                                                        |                                   |                                | 3                           |       | MHz   |

|                        | DC Gain                                                                               |                                   |                                | 80                          |       | dB    |

|                        | Input Voltage                                                                         | V <sub>FB</sub> = COMP            | 0.735                          | 0.75                        | 0.765 | V     |

|                        | COMP Sink Capability                                                                  | V <sub>FB</sub> = 1.5V, COMP= 1V  | 4                              | 8                           |       | mA    |

<sup>(1)</sup> All limits are specified. All electrical characteristics having room temperature limits are tested during production with T<sub>A</sub> = T<sub>J</sub> = 25°C. All hot and cold limits are verified by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

(2) Device thermal limitations may limit usable range.

www.ti.com

## **Electrical Characteristics (continued)**

Specifications with standard typeface are for  $T_J = 25^{\circ}C$ , and those with **boldface** type apply over full **Operating Junction Temperature range**.  $V_{IN} = 48V$ ,  $V_{CC} = 10V$ ,  $RT = 26.7k\Omega$ ,  $R_{SET} = 20k\Omega$ ) unless otherwise stated. (1)

| Symbol      | Parameter                                              | Conditions                                                                               | Min               | Тур                   | Max               | Units |

|-------------|--------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------|-----------------------|-------------------|-------|

| Reference S | Supply                                                 |                                                                                          |                   |                       |                   | •     |

| $V_{REF}$   | Ref Voltage                                            | I <sub>REF</sub> = 0 mA                                                                  | 4.85              | 5                     | 5.15              | V     |

|             | Ref Voltage Regulation                                 | I <sub>REF</sub> = 0 to 10mA                                                             |                   | 25                    | 50                | mV    |

|             | Ref Current Limit                                      |                                                                                          | 15                | 20                    |                   | mA    |

| Current Lin | nit                                                    | <u> </u>                                                                                 |                   |                       |                   | *     |

|             | ILIM Delay to Output                                   | CS Step from 0 to 0.6V<br>Time to Onset of OUT<br>Transition (90%)<br>C <sub>L</sub> = 0 |                   | 40                    |                   | ns    |

|             | Cycle by Cycle Threshold Voltage                       |                                                                                          | 0.45              | 0.5                   | 0.55              | V     |

|             | Cycle Skip Threshold<br>Voltage                        | Resets SS capacitor; auto restart                                                        | 0.55              | 0.6                   | 0.65              | V     |

|             | Leading Edge Blanking<br>Time                          |                                                                                          |                   | 50                    |                   | ns    |

|             | CS Sink Current (clocked)                              | CS = 0.3V                                                                                | 2                 | 5                     |                   | mA    |

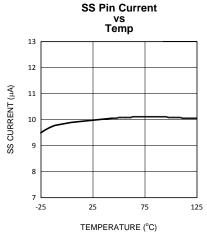

| Soft-Start  |                                                        | , -                                                                                      |                   |                       |                   |       |

|             | Soft-start Current Source                              |                                                                                          | 7                 | 10                    | 13                | μΑ    |

|             | Soft-start to COMP Offset                              |                                                                                          | 0.35              | 0.55                  | 0.75              | V     |

|             | Shutdown Threshold                                     |                                                                                          | 0.25              | 0.5                   | 0.75              | V     |

| Oscillator  | ,                                                      | <u> </u>                                                                                 |                   |                       |                   | *     |

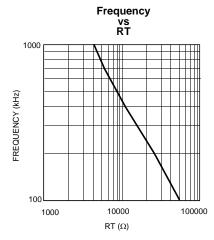

|             | Frequency1 (RT = 26.7KΩ)                               | T <sub>J</sub> = 25°C                                                                    | 180<br><b>175</b> | 200                   | 220<br><b>225</b> | kHz   |

|             | Frequency2 (RT = 7.87KΩ)                               |                                                                                          | 515               | 600                   | 685               | kHz   |

|             | Sync threshold                                         |                                                                                          |                   | 3                     | 3.5               | V     |

| PWM Comp    | arator                                                 |                                                                                          |                   |                       |                   |       |

|             | Delay to Output                                        | COMP set to 2V<br>CS stepped 0 to 0.4V, Time<br>to onset of OUT transition<br>low        |                   | 25                    |                   | ns    |

|             | Max Duty Cycle                                         | TS = Oscillator Period                                                                   |                   | (Ts-240ns)/Ts)        |                   | %     |

|             | Min Duty Cycle                                         | COMP = 0V                                                                                |                   |                       | 0                 | %     |

|             | COMP to PWM<br>Comparator Gain                         |                                                                                          |                   | 0.32                  |                   |       |

|             | COMP Open Circuit<br>Voltage                           | FB = 0V                                                                                  | 4.1               | 4.8                   | 5.5               | V     |

|             | COMP Short Circuit<br>Current                          | FB = 0V, COMP = 0V                                                                       | 0.6               | 1                     | 1.4               | mA    |

| Slope Com   | pensation                                              |                                                                                          |                   |                       |                   |       |

|             | Slope Comp Amplitude                                   | Delta increase at PWM<br>Comparator to CS                                                |                   | 110                   |                   | mV    |

| UVLO Shut   | down                                                   |                                                                                          |                   |                       |                   |       |

|             | Under-voltage Shutdown                                 |                                                                                          | 2.44              | 2.5                   | 2.56              | V     |

|             | Under-voltage Shutdown<br>Hysteresis Current<br>Source |                                                                                          | 16                | 20                    | 24                | μA    |

| Buck Stage  | Outputs                                                |                                                                                          |                   |                       |                   |       |

|             | Output High level                                      |                                                                                          |                   | 5 (V <sub>REF</sub> ) |                   | V     |

|             | Output High Saturation                                 | I <sub>OUT</sub> = 10mA<br>REF = V <sub>OUT</sub>                                        |                   | 0.5                   | 1                 | V     |

Submit Documentation Feedback

Copyright © 2003–2013, Texas Instruments Incorporated

## **Electrical Characteristics (continued)**

Specifications with standard typeface are for  $T_J$  = 25°C, and those with **boldface** type apply over full **Operating Junction Temperature range**.  $V_{IN}$  = 48V,  $V_{CC}$  = 10V, RT = 26.7k $\Omega$ ,  $R_{SET}$  = 20k $\Omega$ ) unless otherwise stated. (1)

| Symbol          | Parameter                      | Conditions                                                        | Min | Тур  | Max | Units |

|-----------------|--------------------------------|-------------------------------------------------------------------|-----|------|-----|-------|

|                 | Output Low Saturation          | I <sub>OUT</sub> = −10mA                                          |     | 0.5  | 1   | V     |

|                 | Rise Time                      | C <sub>L</sub> = 100pF                                            |     | 10   |     | ns    |

|                 | Fall Time                      | C <sub>L</sub> = 100pF                                            |     | 10   |     | ns    |

| Push-Pull C     | Outputs                        |                                                                   |     |      |     |       |

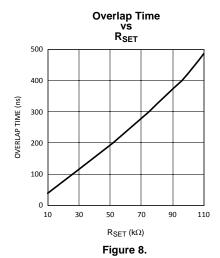

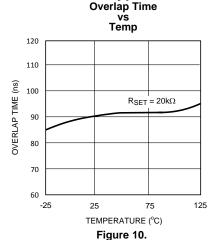

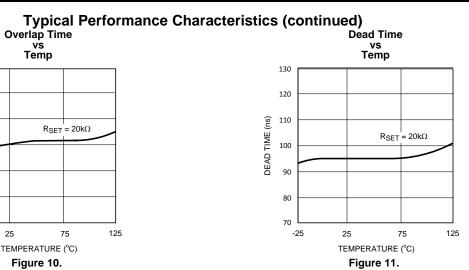

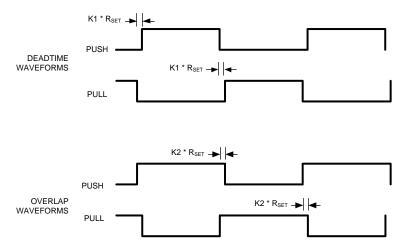

|                 | Overlap Time                   | $R_{SET}$ = 20k $\Omega$ Connected to GND, 50% to 50% Transitions | 60  | 90   | 120 | ns    |

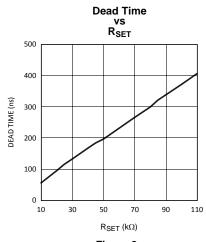

|                 | Dead Time                      | $R_{SET}$ = 20k $\Omega$ Connected to REF, 50% to 50% Transitions | 65  | 95   | 125 | ns    |

|                 | Output High Saturation         | I <sub>OUT</sub> = 50mA<br>V <sub>CC</sub> - V <sub>OUT</sub>     |     | 0.25 | 0.5 | V     |

|                 | Output Low Saturation          | I <sub>OUT</sub> = 100mA                                          |     | 0.5  | 1   | V     |

|                 | Rise Time                      | C <sub>L</sub> = 1nF                                              |     | 20   |     | ns    |

|                 | Fall Time                      | C <sub>L</sub> = 1nF                                              |     | 20   |     | ns    |

| Thermal Sh      | utdown                         |                                                                   |     |      |     | -     |

| T <sub>SD</sub> | Thermal Shutdown Temp.         |                                                                   |     | 165  |     | °C    |

|                 | Thermal Shutdown<br>Hysteresis |                                                                   |     | 25   |     | °C    |

| Thermal Re      | sistance                       |                                                                   |     |      |     |       |

| 0               | lunction to Ambient            | PW Package                                                        |     | 125  |     | °C/W  |

| $\theta_{JA}$   | Junction to Ambient            | NHQ0016A Package                                                  |     | 32   |     | °C/W  |

## **Typical Performance Characteristics**

Figure 6.

Figure 5.

Figure 7.

Figure 9.

#### **DETAILED OPERATING DESCRIPTION**

The LM5041 PWM controller contains all of the features necessary to implement either current-fed or voltage-fed push-pull or bridge power converters. These "Cascaded" topologies are well suited for multiple output and higher power applications. The LM5041's four control outputs include: the buck stage controls (HD and LD) and the push-pull control outputs (PUSH and PULL). Push-pull outputs are driven at 50% nominal duty cycle at one half of the switching frequency of the buck stage and can be configured for either a specified overlap time (for current-fed applications) or a specified both-off time (for voltage-fed applications). Push-pull stage MOSFETs can be driven directly from the internal gate drivers while the buck stage requires an external driver such as the LM5102. The LM5041 includes a high-voltage start-up regulator that operates over a wide input range of 15V to 100V. The PWM controller is designed for high-speed capability including an oscillator frequency range up to 1 MHz and total propagation delays of less than 100ns. Additional features include: line Under-Voltage Lockout (UVLO), soft-start, an error amplifier, precision voltage reference, and thermal shutdown.

#### **High Voltage Start-Up Regulator**

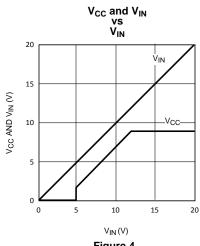

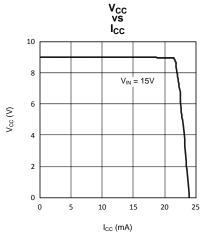

The LM5041 contains an internal high-voltage start-up regulator, thus the input pin (Vin) can be connected directly to the line voltage. The regulator output is internally current limited to 15mA. When power is applied, the regulator is enabled and sources current into an external capacitor connected to the Vcc pin. The recommended capacitance range for the Vcc regulator is 0.1uF to 100uF. When the voltage on the Vcc pin reaches the regulation point of 9V and the internal voltage reference (REF) reaches its regulation point of 5V, the controller outputs are enabled. The Buck stage outputs will remain enabled until Vcc falls below 7V or the line Under-Voltage Lockout detector indicates that Vin is out of range. The push-pull outputs continue switching until the REF pin voltage falls below approximately 3V. In typical applications, an auxiliary transformer winding is connected through a diode to the Vcc pin. This winding must raise the Vcc voltage above 9.3V to shut off the internal start-up regulator. Powering  $V_{CC}$  from an auxiliary winding improves efficiency while reducing the controller's power dissipation. The recommended capacitance range for the Vref regulator output is 0.1uF to 10uF.

The external  $V_{CC}$  capacitor must be sized such that the capacitor maintains a  $V_{CC}$  voltage greater than 7V during the initial start-up. During a fault mode when the converter auxiliary winding is inactive, external current draw on the  $V_{CC}$  line should be limited so the power dissipated in the start-up regulator does not exceed the maximum power dissipation of the controller.

An external start-up or other bias rail can be used instead of the internal start-up regulator by connecting the  $V_{CC}$  and the  $V_{IN}$  pins together and feeding the external bias voltage into the two pins.

#### **Line Under-Voltage Detector**

The LM5041 contains a line Under-Voltage Lockout (UVLO) circuit. An external set-point resistor divider from  $V_{IN}$  to ground sets the operational range of the converter. The divider must be designed such that the voltage at the UVLO pin will be greater than 2.5V when  $V_{IN}$  is in the desired operating range. If the Under-Voltage threshold is not met, all functions of the controller are disabled and the controller will enter a low-power state with input current <300 $\mu$ A. ULVO hysteresis is accomplished with an internal 20 $\mu$ A current source that is switched on or off into the impedance of the set-point divider. When the UVLO threshold is exceeded, the current source is activated to instantly raise the voltage at the UVLO pin. When the UVLO pin falls below the 2.5V threshold, the current source is turned off causing the voltage at the UVLO pin to fall. The UVLO pin can also be used to implement a remote enable / disable function. By shorting the UVLO pin to ground, the converter can be disabled. The controller can also be disabled through the soft-start pin (SS). The controller will enter a low-power off state if the SS pin is forced below the 0.45V shutdown threshold.

#### **Buck Stage Control Outputs**

The LM5041 Buck switch maximum duty cycle clamp ensures that there will be sufficient off time each cycle to recharge the bootstrap capacitor used in the high side gate driver. The Buck switch is specified to be off, and the sync switch on, for at least 250ns per switching cycle. The Buck stage control outputs (LD and HD) are CMOS buffers with logic levels of 0 to 5V.

During any fault state or Under-Voltage off state, the buck stage control outputs will default to HD low and LD high.

#### **Push-Pull Outputs**

The push pull outputs operate continuously at a nominal 50% duty cycle. A distinguishing feature of the LM5041 is the ability to accurately configure either dead time (both-off) or overlap time (both-on) on the complementary push-pull outputs. The overlap/dead time magnitude is controlled by a resistor connected to the TIME pin on the controller. The TIME pin holds one end of the resistor at 2.5V and the other end of the resistor should be connected to either REF for dead time control setting or to GND for overlap control. The polarity of the current in the TIME is detected by the LM5041 The magnitude of the overlap/dead time can be calculated as follows:

- Overlap Time (ns) = (3.66 x R<sub>SFT</sub>) + 7

- Overlap Time in ns, R<sub>SET</sub> connected to GND, R<sub>SET</sub> in kΩ

- Dead Time (ns) = (3.69 x R<sub>SFT</sub>) + 21

- Dead Time in ns, R<sub>SET</sub> connected to REF, R<sub>SET</sub> in kΩ

- Recommended  $R_{SET}$  programming range:  $10k\Omega$  to  $100k\Omega$

Current-fed designs require a period of overlap to insure there is a continuous path for the buck inductor current. Voltage-fed designs require a period of dead time to insure there is no time when the push-pull transformer acts as a shorted turn to the low impedance sourcing node. The push-pull outputs alternate continuously under all conditions provided REF the voltage is greater than 3V.

## **PWM Comparator**

The PWM comparator compares the slope compensated current ramp signal to the loop error voltage from the internal error amplifier (COMP pin). This comparator is optimized for speed in order to achieve minimum controllable duty cycles. The comparator polarity is such that 0V on the COMP pin will produce zero duty cycle in the buck stage.

## **Error Amplifier**

An internal high gain wide-bandwidth error amplifier is provided within the LM5041. The amplifier's non-inverting input is tied to a 0.75V reference. The inverting input is connected to the FB pin. In non-isolated applications the power converter output is connected to the FB pin via the voltage setting resistors. Loop compensation components are connected between the COMP and FB pins. For most isolated applications the error amplifier function is implemented on the secondary side of the converter and the internal error amp is not used. The internal error amplifier is configured as an open drain output and can be disabled by connecting the FB pin to ground. An internal  $5k\Omega$  pull-up resistor between the 5V reference and COMP can be used as the pull-up for an opto-coupler in isolated applications.

#### **Current Limit/Current Sense**

The LM5041 contains two levels of over-current protection. If the voltage at the CS pin exceeds 0.5V the present buck stage duty cycle is terminated (cycle by cycle current limit). If the voltage at the CS pin overshoots the 0.5V threshold and exceeds 0.6V, then the controller will terminate the present cycle and fully discharge the soft-start capacitor. A small RC filter located near the controller is recommended to filter current sense signals at the CS pin. An internal MOSFET discharges the external CS pin for an additional 50ns at the beginning of each cycle to reduce the leading edge spike that occurs when the buck stage MOSFET is turned on.

The LM5041 current sense and PWM comparators are very fast, and may respond to short duration noise pulses. Layout considerations are critical for the current sense filter and sense resistor. The capacitor associated with the CS filter must be placed close to the device and connected directly to the pins of the controller (CS and GND). If a current sense transformer is used, both leads of the transformer secondary should be routed to the sense resistor, which should also be located close to the IC. A resistor may be used for current sensing instead of a transformer, located in the push-pull transistor sources, but a low inductance type of resistor is required. When designing with a sense resistor, all of the noise sensitive low power grounds should be connected together around the IC and a single connection should be made to the high current power ground (sense resistor ground point).

The second level current sense threshold is intended to protect the power converter by initiating a low duty cycle hick-up mode when abnormally high currents are sensed. If the second level threshold is reached, the soft-start capacitor will be discharged and a start-up sequence will commence when the soft-start capacitor is determined to be fully discharged. The second level threshold will only be reached when a high dV/dt is present at the current sense pin. The current sense transient must be fast enough to reach the second level threshold before the first threshold detector turns off the buck stage driver. Very high current sense dV/dt can occur with a saturated power inductor or shorted load. Excessive filtering on the CS pin such as an extremely low value current sense resistor or an inductor that does not saturate with excessive loading, may prevent the second level threshold from being reached. If the second level threshold is never exceeded during an overload condition, the first level current sense will continue cycle by cycle limiting and the output characteristic of the converter will be that of a current source. However, a sustained overload current level can cause excessive temperatures in the power train especially the output rectifiers.

#### **Oscillator and Sync Capability**

The LM5041 oscillator is set by a single external resistor connected between the RT pin and GND. To set a desired oscillator frequency (F), the necessary RT resistor can be calculated from:

$$RT = \frac{(1/F) - 235 \times 10^{-9}}{182 \times 10^{-12}} \Omega$$

(1)

The buck stage will switch at the oscillator frequency and each push-pull output will switch at half the oscillator frequency in a push-pull configuration. The LM5041 can also be synchronized to an external clock. The external clock must have a higher frequency than the free running frequency set by the RT resistor. The clock signal should be capacitively coupled into the RT pin with a 100pF capacitor. A peak voltage level greater than 3V is required for detection of the sync pulse. The sync pulse width should be set in the 15 to 150ns range by the external components. The RT resistor is always required, whether the oscillator is free running or externally synchronized. The voltage at the RT pin is internally regulated to 2V. The RT resistor should be located very close to the device and connected directly to the pins of the IC (RT and GND).

#### Slope Compensation

The PWM comparator compares the current sense signal to the voltage at the COMP pin. The output stage of the internal error amplifier generally drives the COMP pin. At duty cycles greater than 50 percent, current mode control circuits are subject to sub-harmonic oscillation. By adding an additional fixed ramp signal (slope compensation) to the current sense ramp, oscillations can be avoided. The LM5041 integrates this slope compensation by buffering the internal oscillator ramp and summing a current ramp generated by the oscillator internally with the current sense signal. Additional slope compensation may be provided by increasing the source impedance of the current sense signal.

#### Soft-start and Shutdown

The soft-start feature allows the power converter to gradually reach the initial steady state operating point, thereby reducing start-up stresses and surges. At power on, a 10uA current is sourced out of the soft-start pin (SS) to charge an external capacitor. The capacitor voltage will ramp up slowly and will limit the maximum duty cycle of the buck stage. In the event of a fault as indicated by  $V_{CC}$  Under-voltage, line Under-voltage or second level current limit, the output drivers are disabled and the soft-start capacitor is discharged to ground. When the fault condition is no longer present, a soft-start sequence will begin again and buck stage duty cycle will gradually increase as the soft-start capacitor is charged. The SS pin also serves as an enable input. The controller will enter a low power state if the SS pin is forced below the 0.45V threshold.

#### **Thermal Protection**

Internal Thermal Shutdown circuitry is provided to protect the integrated circuit in the event that the maximum junction temperature is exceeded. When activated, typically at 165 degrees Celsius, the controller is forced into a low-power standby state, disabling the output drivers and the bias regulator. This feature is provided to prevent catastrophic failures from accidental device overheating.

#### **Typical Application**

Figure 13. Simplified Cascaded Half-Bridge

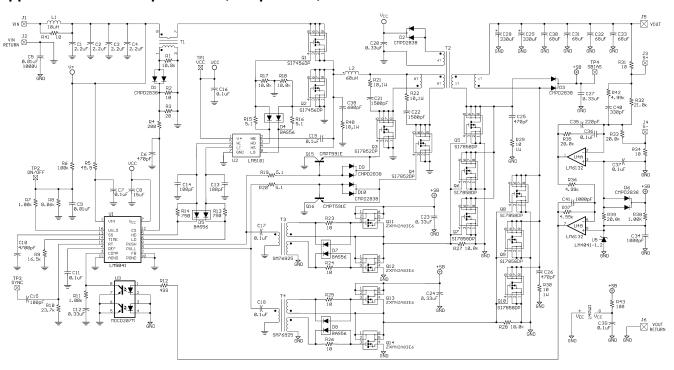

# Application Circuit: Input 35-80V, Output 2.5V, 50A

## **REVISION HISTORY**

| Cł | hanges from Revision C (March 2013) to Revision D  | Pag | ge |

|----|----------------------------------------------------|-----|----|

| •  | Changed layout of National Data Sheet to TI format |     | 13 |

26-Mar-2013

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package | Pins | Package | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|--------|--------------|---------|------|---------|----------------------------|------------------|--------------------|--------------|-------------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)                        |                  | (3)                |              | (4)               |         |

| LM5041MTC        | ACTIVE | TSSOP        | PW      | 16   | 92      | TBD                        | Call TI          | Call TI            | -40 to 125   | LM5041<br>MTC     | Samples |

| LM5041MTC/NOPB   | ACTIVE | TSSOP        | PW      | 16   | 92      | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 125   | LM5041<br>MTC     | Samples |

| LM5041MTCX       | ACTIVE | TSSOP        | PW      | 16   | 2500    | TBD                        | Call TI          | Call TI            | -40 to 125   | LM5041<br>MTC     | Samples |

| LM5041MTCX/NOPB  | ACTIVE | TSSOP        | PW      | 16   | 2500    | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 125   | LM5041<br>MTC     | Samples |

| LM5041SD         | ACTIVE | WSON         | NHQ     | 16   | 1000    | TBD                        | Call TI          | Call TI            | -40 to 125   | 5041SD            | Samples |

| LM5041SD/NOPB    | ACTIVE | WSON         | NHQ     | 16   | 1000    | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 125   | 5041SD            | Samples |

| LM5041SDX        | ACTIVE | WSON         | NHQ     | 16   | 4500    | TBD                        | Call TI          | Call TI            | -40 to 125   | 5041SD            | Samples |

| LM5041SDX/NOPB   | ACTIVE | WSON         | NHQ     | 16   | 4500    | Green (RoHS<br>& no Sb/Br) | CU SN            | Level-1-260C-UNLIM | -40 to 125   | 5041SD            | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free** (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between

the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

## **PACKAGE OPTION ADDENDUM**

26-Mar-2013

(4) Multiple Top-Side Markings will be inside parentheses. Only one Top-Side Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Top-Side Marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

www.ti.com 26-Mar-2013

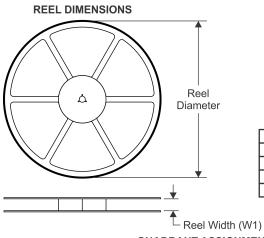

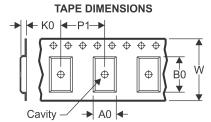

## TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

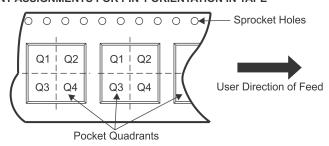

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device          |       | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------------|-------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM5041MTCX      | TSSOP | PW                 | 16 | 2500 | 330.0                    | 12.4                     | 6.95       | 8.3        | 1.6        | 8.0        | 12.0      | Q1               |

| LM5041MTCX/NOPB | TSSOP | PW                 | 16 | 2500 | 330.0                    | 12.4                     | 6.95       | 8.3        | 1.6        | 8.0        | 12.0      | Q1               |

| LM5041SD        | WSON  | NHQ                | 16 | 1000 | 178.0                    | 12.4                     | 5.3        | 5.3        | 1.3        | 8.0        | 12.0      | Q1               |

| LM5041SD/NOPB   | WSON  | NHQ                | 16 | 1000 | 178.0                    | 12.4                     | 5.3        | 5.3        | 1.3        | 8.0        | 12.0      | Q1               |

| LM5041SDX       | WSON  | NHQ                | 16 | 4500 | 330.0                    | 12.4                     | 5.3        | 5.3        | 1.3        | 8.0        | 12.0      | Q1               |

| LM5041SDX/NOPB  | WSON  | NHQ                | 16 | 4500 | 330.0                    | 12.4                     | 5.3        | 5.3        | 1.3        | 8.0        | 12.0      | Q1               |

www.ti.com 26-Mar-2013

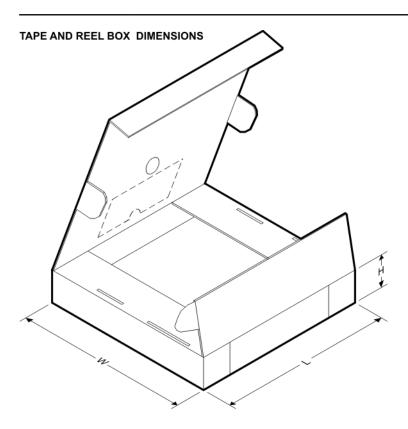

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM5041MTCX      | TSSOP        | PW              | 16   | 2500 | 367.0       | 367.0      | 35.0        |

| LM5041MTCX/NOPB | TSSOP        | PW              | 16   | 2500 | 367.0       | 367.0      | 35.0        |

| LM5041SD        | WSON         | NHQ             | 16   | 1000 | 203.0       | 190.0      | 41.0        |

| LM5041SD/NOPB   | WSON         | NHQ             | 16   | 1000 | 203.0       | 190.0      | 41.0        |

| LM5041SDX       | WSON         | NHQ             | 16   | 4500 | 367.0       | 367.0      | 35.0        |

| LM5041SDX/NOPB  | WSON         | NHQ             | 16   | 4500 | 367.0       | 367.0      | 35.0        |

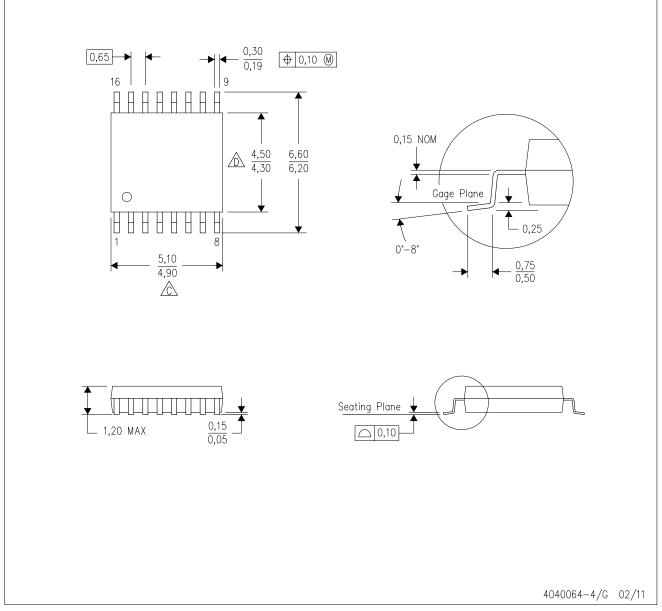

PW (R-PDSO-G16)

## PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M—1994.

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0,15 each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0,25 each side.

- E. Falls within JEDEC MO-153

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>