SBAS289B - JUNE 2003 - REVISED MARCH 2004

# Precision Analog-to-Digital Converter (ADC) and Digital-to-Analog Converter (DAC) with 8051 Microcontroller and Flash Memory

# **FEATURES**

## **ANALOG FEATURES**

- 24-BITS NO MISSING CODES

- 22-BITS EFFECTIVE RESOLUTION AT 10Hz Low Noise: 75nV

- PGA FROM 1 TO 128

- PRECISION ON-CHIP VOLTAGE REFERENCE

- 8 DIFFERENTIAL/SINGLE-ENDED CHANNELS

- ON-CHIP OFFSET/GAIN CALIBRATION

- OFFSET DRIFT: 0.02ppm/°C

- GAIN DRIFT: 0.5ppm/°C

- ON-CHIP TEMPERATURE SENSOR

- SELECTABLE BUFFER INPUT

- BURNOUT DETECT

- 8-BIT CURRENT DAC

#### **DIGITAL FEATURES**

#### **Microcontroller Core**

- 8051-COMPATIBLE

- HIGH-SPEED CORE:4 Clocks per Instruction Cycle

- DC TO 33MHz

- ON-CHIP OSCILLATOR

- PLL WITH 32kHz CAPABILITY

- SINGLE INSTRUCTION 121ns

- DUAL DATA POINTER

#### Memory

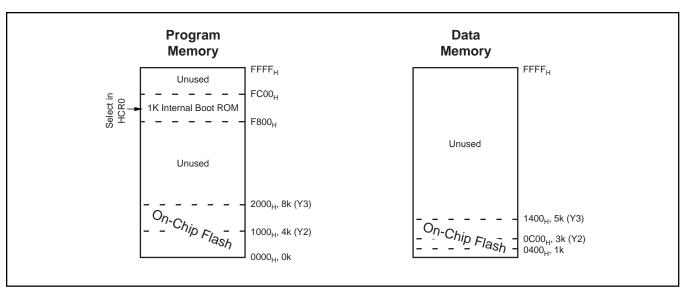

- 4kB OR 8kB OF FLASH MEMORY

- FLASH MEMORY PARTITIONING

- ENDURANCE 1M ERASE/WRITE CYCLES, 100 YEAR DATA RETENTION

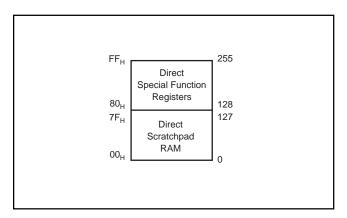

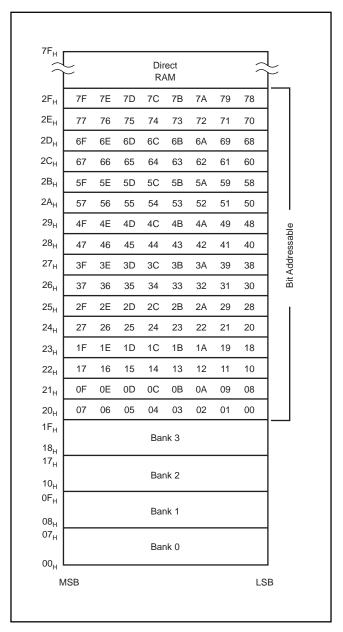

- 128 BYTES DATA SRAM

- IN-SYSTEM SERIALLY PROGRAMMABLE

- FLASH MEMORY SECURITY

- 1kB BOOT ROM

#### **Peripheral Features**

- 16 DIGITAL I/O PINS

- ADDITIONAL 32-BIT ACCUMULATOR

- TWO 16-BIT TIMER/COUNTERS

- SYSTEM TIMERS

- PROGRAMMABLE WATCHDOG TIMER

- FULL DUPLEX UART

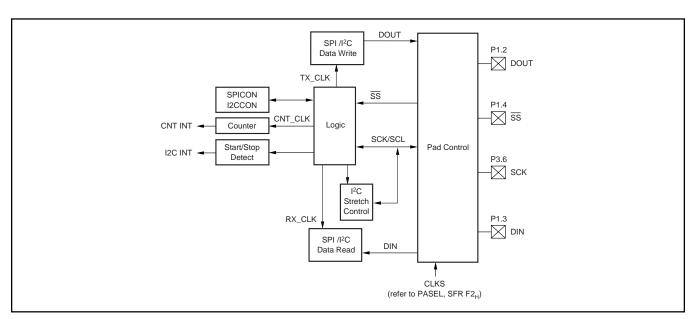

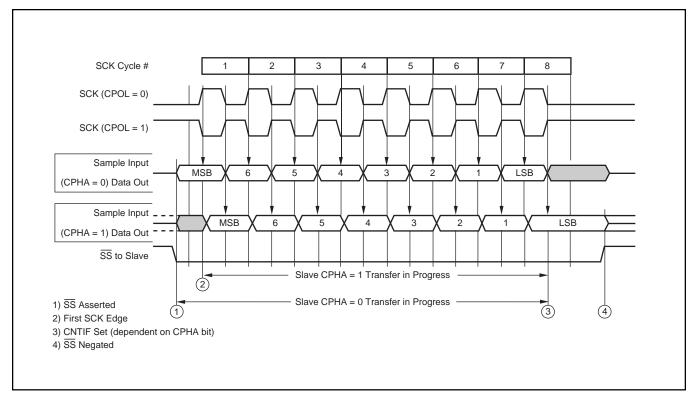

- BASIC SPI<sup>™</sup>

- BASIC I<sup>2</sup>C<sup>™</sup>

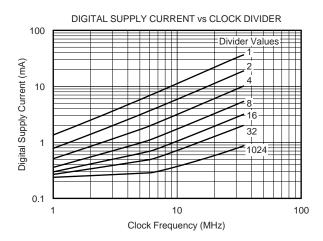

- POWER MANAGEMENT CONTROL

- INTERNAL CLOCK DIVIDER

- IDLE MODE CURRENT < 200µA

- STOP MODE CURRENT < 100nA

- DIGITAL BROWNOUT RESET

- ANALOG LOW VOLTAGE DETECT

- 20 INTERRUPT SOURCES

#### **GENERAL FEATURES**

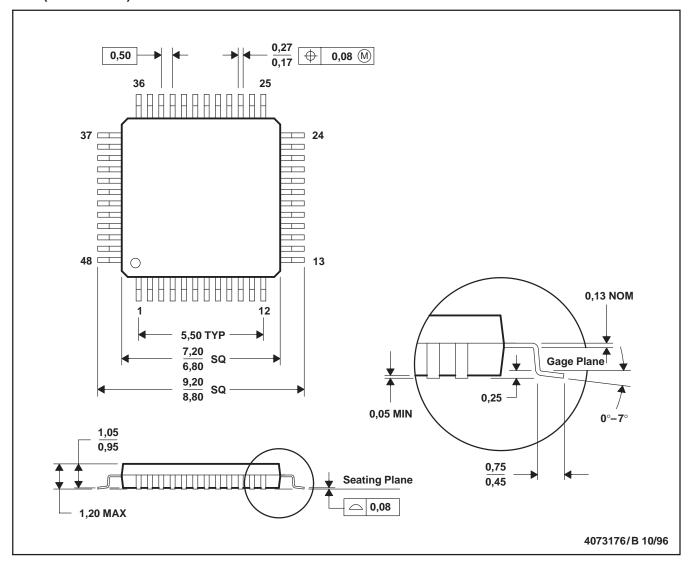

- PACKAGE: TQFP-48

- LOW POWER: 3mW

- INDUSTRIAL TEMPERATURE RANGE: -40°C to +85°C

- POWER SUPPLY: 2.7V to 5.25V

# **APPLICATIONS**

- INDUSTRIAL PROCESS CONTROL

- INSTRUMENTATION

- LIQUID/GAS CHROMATOGRAPHY

- BLOOD ANALYSIS

- SMART TRANSMITTERS

- PORTABLE INSTRUMENTS

- WEIGH SCALES

- PRESSURE TRANSDUCERS

- INTELLIGENT SENSORS

- PORTABLE APPLICATIONS

- DAS SYSTEMS

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

#### PACKAGE/ORDERING INFORMATION

| PRODUCT                | FLASH<br>MEMORY | PACKAGE-LEAD | PACKAGE<br>DESIGNATOR <sup>(1)</sup> | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER             | TRANSPORT<br>MEDIA, QUANTITY              |

|------------------------|-----------------|--------------|--------------------------------------|-----------------------------------|--------------------|--------------------------------|-------------------------------------------|

| MSC1200Y2<br>MSC1200Y2 | l               | TQFP-48      | PFB<br>"                             | -40°C to +85°C                    | MSC1200Y2          | MSC1200Y2PFBT<br>MSC1200Y2PFBR | Tape and Reel, 250<br>Tape and Reel, 2000 |

| MSC1200Y3<br>MSC1200Y3 | 8k<br>8k        | TQFP-48<br>" | PFB<br>"                             | –40°C to +85°C                    | MSC1200Y3<br>"     | MSC1200Y3PFBT<br>MSC1200Y3PFBR | Tape and Reel, 250<br>Tape and Reel, 2000 |

NOTE: (1) For the most current specifications and package information, refer to our web site at www.ti.com/msc.

#### **ABSOLUTE MAXIMUM RATINGS**(1)

| Analog Inputs                                                 |

|---------------------------------------------------------------|

| Input Current                                                 |

| Input Current                                                 |

| Input Voltage AGND – 0.5V to AV <sub>DD</sub> + 0.5V          |

| Power Supply                                                  |

| DV <sub>DD</sub> to DGND0.3V to 6V                            |

| AV <sub>DD</sub> to AGND0.3V to 6V                            |

| AGND to DGND0.3V to +0.3V                                     |

| V <sub>REF</sub> to AGND                                      |

| Digital Input Voltage to DGND0.3V to DV <sub>DD</sub> + 0.3V  |

| Digital Output Voltage to DGND0.3V to DV <sub>DD</sub> + 0.3V |

| Maximum Junction Temperature+150°C                            |

| Operating Temperature Range40°C to +85°C                      |

| Storage Temperature Range –65°C to +150°C                     |

| Lead Temperature (soldering, 10s)+300°C                       |

| Package Power Dissipation 1150mW                              |

| Output Current All Pins                                       |

| Output Pin Short Circuit10s                                   |

| Thermal Resistance, Junction-to-Ambient ( $\theta_{JA}$ )     |

| Thermal Resistance, Junction-to-Case ( $\theta_{JC}$ )        |

| Digital Outputs                                               |

| Output Current                                                |

| I/O Source/Sink Current                                       |

| Power Pin Maximum                                             |

NOTE: (1) Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### **MSC1200Yx FAMILY FEATURES**

| FEATURES(1)                     | MSC1200Y2 <sup>(2)</sup> | MSC1200Y3 <sup>(2)</sup> |

|---------------------------------|--------------------------|--------------------------|

| Flash Program Memory (Bytes)    | Up to 4k                 | Up to 8k                 |

| Flash Data Memory (Bytes)       | Up to 2k                 | Up to 4k                 |

| Internal Scratchpad RAM (Bytes) | 128                      | 128                      |

NOTES: (1) All peripheral features are the same on all devices; the flash memory size is the only difference. (2) The last digit of the part number (N) represents the onboard flash size =  $(2^N)$ kBytes.

# **ELECTRICAL CHARACTERISTICS:** AV<sub>DD</sub> = 5V

All specifications from  $T_{MIN}$  to  $T_{MAX}$ ,  $DV_{DD}$  = +2.7V to 5.25V,  $f_{MOD}$  = 15.625kHz, PGA = 1, Buffer ON,  $f_{DATA}$  = 10Hz, Bipolar, and  $V_{REF}$   $\equiv$  (REF IN+) – (REF IN-) = +2.5V, unless otherwise noted.

|                                  |                                    |             | MSC1200Yx                               |                        |            |

|----------------------------------|------------------------------------|-------------|-----------------------------------------|------------------------|------------|

| PARAMETER                        | CONDITION                          | MIN         | TYP                                     | MAX                    | UNITS      |

| ANALOG INPUT (AINO-AIN7, AINCOM) |                                    |             |                                         |                        |            |

| Analog Input Range               | Buffer OFF                         | AGND - 0.1  |                                         | $AV_{DD} + 0.1$        | V          |

|                                  | Buffer ON                          | AGND + 50mV |                                         | AV <sub>DD</sub> – 1.5 | V          |

| Full-Scale Input Voltage Range   | (ln+) − (ln−)                      |             |                                         | ±V <sub>REF</sub> /PGA | V          |

| Differential Input Impedance     | Buffer OFF                         |             | 7/PGA                                   |                        | MΩ         |

| Input Current                    | Buffer ON                          |             | 0.5                                     |                        | nA         |

| Bandwidth                        |                                    |             |                                         |                        |            |

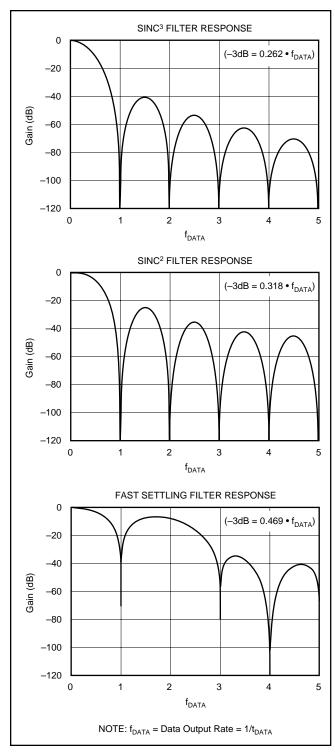

| Fast Settling Filter             | −3dB                               |             | 0.469 • f <sub>DATA</sub>               |                        |            |

| Sinc <sup>2</sup> Filter         | −3dB                               |             | 0.318 • f <sub>DATA</sub>               |                        |            |

| Sinc <sup>3</sup> Filter         | −3dB                               |             | 0.262 • f <sub>DATA</sub>               |                        |            |

| Programmable Gain Amplifier      | User-Selectable Gain Ranges        | 1           |                                         | 128                    |            |

| Input Capacitance                | Buffer ON                          |             | 7                                       |                        | pF         |

| Input Leakage Current            | Multiplexer Channel Off, T = +25°C |             | 0.5                                     |                        | pА         |

| Burnout Current Sources          | Buffer ON                          |             | ±2                                      |                        | μΑ         |

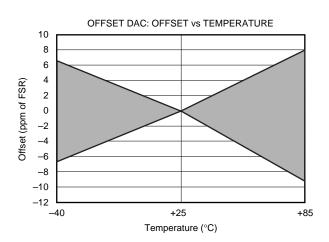

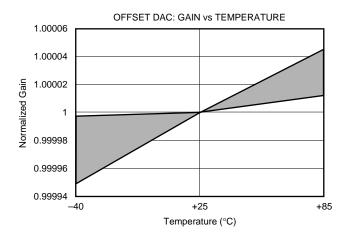

| ADC OFFSET DAC                   |                                    |             |                                         |                        |            |

| Offset DAC Range                 |                                    |             | ±V <sub>RFF</sub> /(2 • PGA)            |                        | V          |

| Offset DAC Monotonicity          |                                    | 8           | , ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                        | Bits       |

| Offset DAC Gain Error            |                                    |             | ±1.0                                    |                        | % of Range |

| Offset DAC Gain Error Drift      |                                    |             | 0.6                                     |                        | ppm/°C     |

# ELECTRICAL CHARACTERISTICS: AV<sub>DD</sub> = 5V (Cont.)

All specifications from  $T_{MIN}$  to  $T_{MAX}$ ,  $DV_{DD}$  = +2.7V to 5.25V,  $f_{MOD}$  = 15.625kHz, PGA = 1, Buffer ON,  $f_{DATA}$  = 10Hz, Bipolar, and  $V_{REF}$   $\equiv$  (REF IN+) - (REF IN-) = +2.5V, unless otherwise noted.

|                                                         |                                                                              |       | MSC1200Yx                |                                 |                                                  |

|---------------------------------------------------------|------------------------------------------------------------------------------|-------|--------------------------|---------------------------------|--------------------------------------------------|

| PARAMETER                                               | CONDITION                                                                    | MIN   | TYP                      | MAX                             | UNITS                                            |

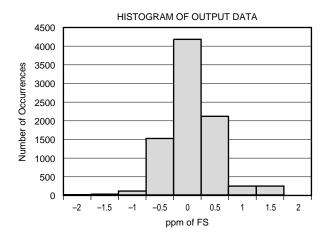

| SYSTEM PERFORMANCE Resolution ENOB                      |                                                                              | 24    | 22                       |                                 | Bits<br>Bits                                     |

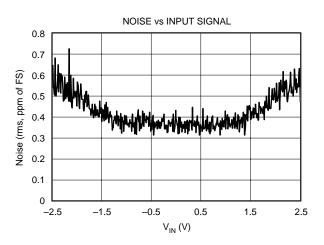

| Output Noise                                            |                                                                              | See - | ı 22<br>Гурісаl Characte | l<br>rietice                    | DILS                                             |

| No Missing Codes                                        | Sinc <sup>3</sup> Filter                                                     | 24    | l ypiodi Orididolo       | l                               | Bits                                             |

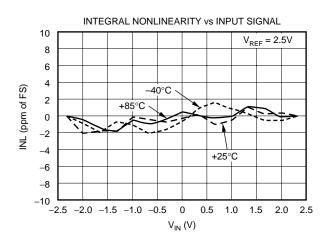

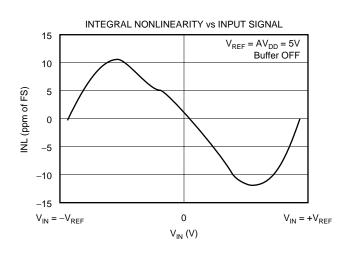

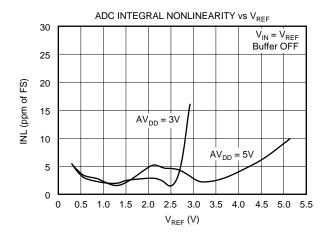

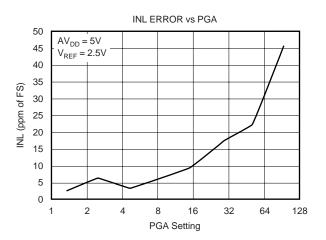

| Integral Nonlinearity                                   | End Point Fit, Differential Input                                            |       | ±0.0004                  | ±0.0015                         | %FSR                                             |

| Offset Error                                            | After Calibration                                                            |       | 1.5                      |                                 | ppm of FS                                        |

| Offset Drift <sup>(1)</sup>                             | Before Calibration                                                           |       | 0.02                     |                                 | ppm of FS/°C                                     |

| Gain Error <sup>(2)</sup>                               | After Calibration                                                            |       | 0.005                    |                                 | %                                                |

| Gain Error Drift <sup>(1)</sup>                         | Before Calibration                                                           |       | 0.5                      |                                 | ppm/°C                                           |

| System Gain Calibration Range                           |                                                                              | 80    |                          | 120                             | % of FS                                          |

| System Offset Calibration Range                         |                                                                              | -50   |                          | 50                              | % of FS                                          |

| Common-Mode Rejection                                   | At DC                                                                        | 100   | 120                      |                                 | dB                                               |

|                                                         | $f_{CM} = 60Hz$ , $f_{DATA} = 10Hz$                                          |       | 130                      |                                 | dB                                               |

|                                                         | $f_{CM} = 50Hz$ , $f_{DATA} = 50Hz$                                          |       | 120<br>120               |                                 | dB<br>dB                                         |

| Normal Mode Rejection                                   | $f_{CM} = 60$ Hz, $f_{DATA} = 60$ Hz                                         |       | 100                      |                                 | dB<br>dB                                         |

| Normal Mode Rejection                                   | $f_{SIG} = 50Hz$ , $f_{DATA} = 50Hz$<br>$f_{SIG} = 60Hz$ , $f_{DATA} = 60Hz$ |       | 100                      |                                 | dB<br>dB                                         |

| Power-Supply Rejection                                  | At DC, dB = $-20\log(\Delta V_{OUT}/\Delta V_{DD})^{(3)}$                    |       | 100                      |                                 | dB                                               |

| ,                                                       |                                                                              |       |                          |                                 | <del>                                     </del> |

| VOLTAGE REFERENCE INPUTS                                | DEE IN DEE IN                                                                | 40115 |                          | A) / (2)                        | .,                                               |

| Reference Input Range                                   | REF IN+, REF IN-                                                             | AGND  | 0.5                      | AV <sub>DD</sub> <sup>(2)</sup> | V                                                |

| V <sub>REF</sub>                                        | $V_{REF} \equiv (REF IN+) - (REF IN-)$ At DC                                 | 0.3   | 2.5<br>115               | AV <sub>DD</sub>                | V<br>dB                                          |

| Common-Mode Rejection Input Current                     | V <sub>REF</sub> = 2.5V, PGA = 1                                             |       | 1                        |                                 | μА                                               |

| •                                                       | VREF = 2.5V, 1 G/V = 1                                                       |       |                          |                                 | μ                                                |

| ON-CHIP VOLTAGE REFERENCE                               |                                                                              |       |                          |                                 |                                                  |

| Output Voltage                                          | VREFH = 1 at +25°C                                                           |       | 2.5                      |                                 | V                                                |

| Short-Circuit Current Source                            | VREFH = 0                                                                    |       | 1.25<br>9                |                                 | V                                                |

| Short-Circuit Current Source Short-Circuit Current Sink |                                                                              |       | 10                       |                                 | mA<br>mA                                         |

| Short-Circuit Current Sink Short-Circuit Duration       | Sink or Source                                                               |       | Indefinite               |                                 | IIIA                                             |

| Startup Time from Power ON                              | Sink of Source                                                               |       | 0.4                      |                                 | ms                                               |

| Temperature Sensor                                      |                                                                              |       | 0.4                      |                                 | 1113                                             |

| Temperature Sensor Voltage                              | T = +25°C                                                                    |       | 115                      |                                 | m∨                                               |

| Temperature Sensor Coefficient                          |                                                                              |       | 375                      |                                 | μV/°C                                            |

| IDAC OUTPUT CHARACTERISTICS                             |                                                                              |       |                          |                                 |                                                  |

| Full-Scale Output Current                               |                                                                              |       | 1                        |                                 | mA                                               |

| Maximum Short-Circuit Current Duration                  |                                                                              |       | Indefinite               |                                 | IIIA                                             |

| Compliance Voltage                                      |                                                                              |       | AV <sub>DD</sub> – 1.5   |                                 | V                                                |

|                                                         |                                                                              |       | 55                       |                                 | <del>                                     </del> |

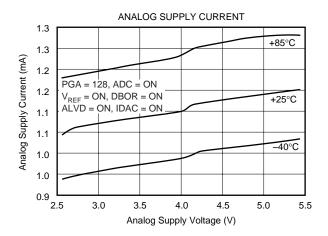

| ANALOG POWER-SUPPLY REQUIREMENTS Power-Supply Voltage   | Δ\/                                                                          | 4.75  | 5.0                      | 5.25                            | V                                                |

| Analog Current                                          | $AV_{DD}$ Analog OFF, ALVD OFF, PDADC = PDIDAC = 1                           | 4.73  | 3.0<br>< 1               | 3.23                            | l v                                              |

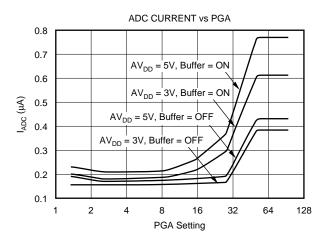

| ADC Current I <sub>ADC</sub>                            | PGA = 1, Buffer OFF                                                          |       | 170                      |                                 | μA                                               |

| TADC                                                    | PGA = 128, Buffer OFF                                                        |       | 430                      |                                 | μA                                               |

|                                                         | PGA = 1, Buffer ON                                                           |       | 230                      |                                 | μΑ                                               |

|                                                         | PGA = 128, Buffer ON                                                         |       | 770                      |                                 | μΑ                                               |

| V <sub>REF</sub> Supply Current I <sub>VREF</sub>       | ADC ON                                                                       |       | 360                      |                                 | μA                                               |

|                                                         | $IDAC = 00_{H}$                                                              |       |                          |                                 |                                                  |

NOTES: (1) Calibration can minimize these errors. (2) The gain calibration cannot have a REF IN+ of more than  $AV_{DD} - 1.5V$  with buffer ON. To calibrate gain, turn buffer off. (3)  $DV_{OUT}$  is change in digital result.

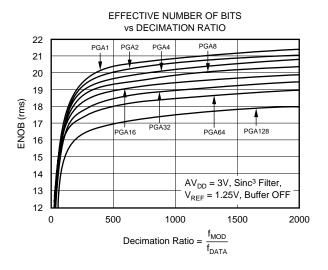

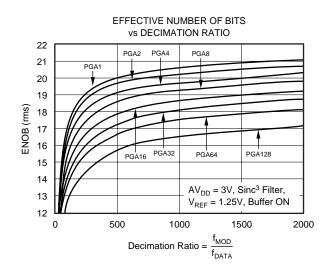

# **ELECTRICAL CHARACTERISTICS:** AV<sub>DD</sub> = 3V

All specifications from  $T_{MIN}$  to  $T_{MAX}$ ,  $AV_{DD}$  = +3V,  $DV_{DD}$  = +2.7V to 5.25V,  $f_{MOD}$  = 15.625kHz, PGA = 1, Buffer ON,  $f_{DATA}$  = 10Hz, Bipolar, and  $V_{REF}$   $\equiv$  (REF IN+) - (REF IN-) = +1.25V, unless otherwise noted.

|                                                                                                                                                         |                       |                                                                                                                                                                                                            | MSC1200Yx                 |                                                                                        |                                                     |                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------|

| PARAMETER                                                                                                                                               |                       | CONDITION                                                                                                                                                                                                  | MIN                       | TYP                                                                                    | MAX                                                 | UNITS                                                    |

| ANALOG INPUT (AIN0-AIN7, AINCO<br>Analog Input Range<br>Full-Scale Input Voltage Range<br>Differential Input Impedance<br>Input Current                 | M)                    | Buffer OFF<br>Buffer ON<br>(In+) – (In–)<br>Buffer OFF<br>Buffer ON                                                                                                                                        | AGND – 0.1<br>AGND + 50mV | 7/PGA<br>0.5                                                                           | $AV_{DD} + 0.1$ $AV_{DD} - 1.5$ $\pm V_{REF}/PGA$   | V<br>V<br>V<br>MΩ<br>nA                                  |

| Fast Settling Filter Sinc² Filter Sinc³ Filter Programmable Gain Amplifier Input Capacitance Input Leakage Current Burnout Current Sources              |                       | -3dB -3dB -3dB -3dB User-Selectable Gain Ranges Buffer On Multiplexer Channel Off, T = +25°C Buffer ON                                                                                                     | 1                         | 0.469 • f <sub>DATA</sub> 0.318 • f <sub>DATA</sub> 0.262 • f <sub>DATA</sub> 7 0.5 ±2 | 128                                                 | pF<br>pA<br>μΑ                                           |

| ADC OFFSET DAC Offset DAC Range Offset DAC Monotonicity Offset DAC Gain Error Offset DAC Gain Error Drift                                               |                       |                                                                                                                                                                                                            | 8                         | ±V <sub>REF</sub> /(2 • PGA)<br>±1.5<br>0.6                                            |                                                     | V<br>Bits<br>% of Range<br>ppm/°C                        |

| SYSTEM PERFORMANCE Resolution ENOB Output Naire                                                                                                         |                       |                                                                                                                                                                                                            | 24                        | 22 Typical Characte                                                                    | winting.                                            | Bits<br>Bits                                             |

| Output Noise  No Missing Codes Integral Nonlinearity Offset Error Offset Drift <sup>(1)</sup> Gain Error <sup>(2)</sup> Gain Error Drift <sup>(1)</sup> |                       | Sinc <sup>3</sup> Filter End Point Fit, Differential Input After Calibration Before Calibration After Calibration Before Calibration                                                                       | 24                        | ±0.0004<br>1.3<br>0.02<br>0.005<br>0.5                                                 | ±0.0015                                             | Bits<br>%FSR<br>ppm of FS<br>ppm of FS/°C<br>%<br>ppm/°C |

| System Gain Calibration Range<br>System Offset Calibration Range<br>Common-Mode Rejection                                                               |                       | At DC<br>$f_{CM} = 60Hz$ , $f_{DATA} = 10Hz$<br>$f_{CM} = 50Hz$ , $f_{DATA} = 50Hz$<br>$f_{CM} = 60Hz$ , $f_{DATA} = 60Hz$<br>$f_{SIG} = 50Hz$ , $f_{DATA} = 50Hz$<br>$f_{SIG} = 60Hz$ , $f_{DATA} = 60Hz$ | 80<br>-50<br>100          | 130<br>130<br>120<br>120<br>100                                                        | 120<br>50                                           | % of FS % of FS dB dB dB dB dB                           |

| Power-Supply Rejection  VOLTAGE REFERENCE INPUTS  Reference Input Range  V <sub>REF</sub>                                                               |                       | At DC, dB = $-20\log(DV_{OUT}/DV_{DD})^{(3)}$<br>REF IN+, REF IN-<br>$V_{REF} \equiv (REF IN+) - (REF IN-)$                                                                                                | AGND<br>0.3               | 1.25                                                                                   | AV <sub>DD</sub> <sup>(2)</sup><br>AV <sub>DD</sub> | dB<br>V<br>V                                             |

| Common-Mode Rejection Input Current ON-CHIP VOLTAGE REFERENCE                                                                                           |                       | At DC $V_{REF} = 1.25V, PGA = 1$                                                                                                                                                                           |                           | 110<br>0.5                                                                             |                                                     | dB<br>μA                                                 |

| Output Voltage Short-Circuit Current Source Short-Circuit Current Sink Short-Circuit Duration Startup Time from Power ON                                |                       | VREFH = 0 at +25°C Sink or Source                                                                                                                                                                          |                           | 1.25<br>4<br>5<br>Indefinite<br>0.2                                                    |                                                     | V<br>mA<br>μA<br>ms                                      |

| Temperature Sensor Temperature Sensor Voltage Temperature Sensor Coefficient                                                                            |                       | T = +25°C                                                                                                                                                                                                  |                           | 115<br>375                                                                             |                                                     | mV<br>μV/°C                                              |

| IDAC OUTPUT CHARACTERISTICS<br>Full-Scale Output Current<br>Maximum Short-Circuit Current Durati<br>Compliance Voltage                                  | on                    |                                                                                                                                                                                                            |                           | 1<br>Indefinite<br>AV <sub>DD</sub> – 1.5                                              |                                                     | mA<br>V                                                  |

| POWER-SUPPLY REQUIREMENTS Power-Supply Voltage Analog Current ADC Current                                                                               | I <sub>ADC</sub>      | AV <sub>DD</sub> Analog OFF, ALVD OFF, PDADC = PDIDAC = 1 PGA = 1, Buffer OFF PGA = 128, Buffer OFF PGA = 1, Buffer ON PGA = 128, Buffer ON                                                                | 2.7                       | 3.0<br>< 1<br>150<br>380<br>200<br>610                                                 | 3.6                                                 | V<br>nA<br>μA<br>μA<br>μA<br>μA                          |

| V <sub>REF</sub> Supply Current<br>I <sub>DAC</sub> Supply Current                                                                                      | $I_{VREF}$ $I_{IDAC}$ | ADC ON<br>IDAC = 00 <sub>H</sub>                                                                                                                                                                           |                           | 330<br>220                                                                             |                                                     | μA<br>μA                                                 |

NOTES: (1) Calibration can minimize these errors. (2) The gain calibration cannot have a REF IN+ of more than  $AV_{DD} - 1.5V$  with buffer ON. To calibrate gain, turn buffer off. (3)  $DV_{OUT}$  is change in digital result.

# DIGITAL CHARACTERISTICS: $DV_{DD} = 2.7V$ to 5.25V

All specifications from  $T_{\text{MIN}}$  to  $T_{\text{MAX}},$  unless otherwise specified.

|                                                      |                                                          |                        | MSC1200Yx              |                        |       |

|------------------------------------------------------|----------------------------------------------------------|------------------------|------------------------|------------------------|-------|

| PARAMETER                                            | CONDITION                                                | MIN                    | TYP                    | MAX                    | UNITS |

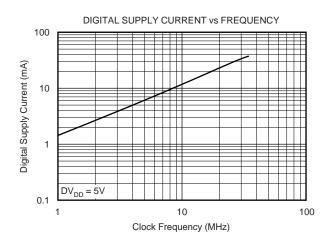

| POWER-SUPPLY REQUIREMENTS                            |                                                          |                        |                        |                        |       |

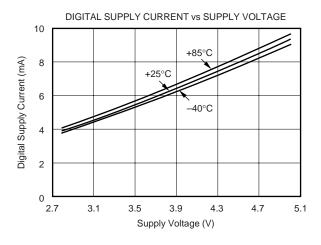

| Digital Supply Current                               | $DV_DD$                                                  | 2.7                    | 3.0                    | 3.6                    | V     |

|                                                      | Normal Mode, f <sub>OSC</sub> = 1MHz                     |                        | 0.6                    |                        | mA    |

|                                                      | Normal Mode, f <sub>OSC</sub> = 8MHz, All Peripherals ON |                        | 5                      |                        | mA    |

|                                                      | Internal Oscillator LF Mode (12.8MHz nominal)            |                        | 7.1                    |                        | mA    |

|                                                      | Stop Mode, DBOR OFF                                      |                        | 100                    |                        | nA    |

|                                                      | DV <sub>DD</sub>                                         | 4.75                   | 5.0                    | 5.25                   | V     |

|                                                      | Normal Mode, f <sub>OSC</sub> = 1MHz                     |                        | 1.2                    |                        | mA    |

|                                                      | Normal Mode, f <sub>OSC</sub> = 8MHz, All Peripherals ON |                        | 9                      |                        | mA    |

|                                                      | Internal Oscillator LF Mode (12.8MHz nominal)            |                        | 15                     |                        | mA    |

|                                                      | Internal Oscillator HF Mode (25.6MHz nominal)            |                        | 29                     |                        | mA    |

|                                                      | Stop Mode, DBOR OFF                                      |                        | 100                    |                        | nA    |

| DIGITAL INPUT/OUTPUT (CMOS)                          |                                                          |                        |                        |                        |       |

| Logic Level: V <sub>IH</sub> (except XIN pin)        |                                                          | 0.6 • DV <sub>DD</sub> |                        | DV <sub>DD</sub>       | V     |

| V <sub>IL</sub> (except XIN pin)                     |                                                          | DGND                   |                        | 0.2 • DV <sub>DD</sub> | V     |

| Ports 1 and 3, Input Leakage Current, Input Mode     | $V_{IH} = DV_{DD}$ or $V_{IH} = 0V$                      |                        | 0                      |                        | μΑ    |

| Pin XIN Input Leakage Current                        |                                                          |                        | 0                      |                        | μΑ    |

| I/O Pin Hysteresis                                   |                                                          |                        | 700                    |                        | mV    |

| V <sub>OL</sub> , Ports 1 and 3, All Output Modes    | $I_{OL} = 1mA$                                           | DGND                   |                        | 0.4                    | V     |

| V <sub>OL</sub> , Ports 1 and 3, All Output Modes    | I <sub>OL</sub> = 30mA, 3V (20mA)                        |                        | 1.5                    |                        | V     |

| V <sub>OH</sub> , Ports 1 and 3, Strong Drive Output | I <sub>OH</sub> = 1mA                                    | $DV_{DD} - 0.4$        |                        | DV <sub>DD</sub>       | V     |

| V <sub>OH</sub> , Ports 1 and 3, Strong Drive Output | $I_{OH} = 30 \text{mA}, 3V (20 \text{mA})$               |                        | DV <sub>DD</sub> – 1.5 |                        | V     |

| Ports 1 and 3 Pull-Up Resistors                      |                                                          |                        | 11                     |                        | kΩ    |

# FLASH MEMORY CHARACTERISTICS: $DV_{DD} = 2.7V$ to 5.25V

$t_{USEC}$  = 1 $\mu$ s,  $t_{MSEC}$  = 1 $\mu$ s

|                             |                             | MSC1200Yx |           | (   |        |

|-----------------------------|-----------------------------|-----------|-----------|-----|--------|

| PARAMETER                   | CONDITION                   | MIN       | TYP       | MAX | UNITS  |

| Flash Memory Endurance      |                             | 100,000   | 1,000,000 |     | cycles |

| Flash Memory Data Retention |                             | 100       |           |     | Years  |

| Mass and Page Erase Time    | Set with FER Value in FTCON | 10        |           |     | ms     |

| Flash Memory Write Time     | Set with FWR Value in FTCON | 30        |           | 40  | μs     |

# AC ELECTRICAL CHARACTERISTICS<sup>(1)</sup>: $DV_{DD} = 2.7V$ to 5.25V

|                                                                                   |                                                                                                                          | MSC1200Yx |                              |     |                         |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------|------------------------------|-----|-------------------------|

| PARAMETER                                                                         | CONDITION                                                                                                                | MIN       | TYP                          | MAX | UNITS                   |

| PHASE LOCK LOOP (PLL) Input Frequency Range PLL LF Mode PLL HF Mode PLL Lock Time | External Crystal/Clock Frequency (f <sub>OSC</sub> ) PLLDIV = 449 (default) PLLDIV = 899 (must be set by user) Within 1% |           | 32.768<br>14.7456<br>29.4912 | 2   | kHz<br>MHz<br>MHz<br>ms |

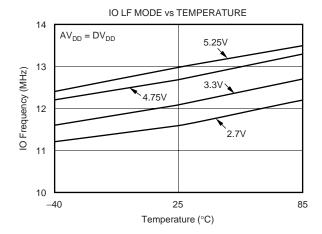

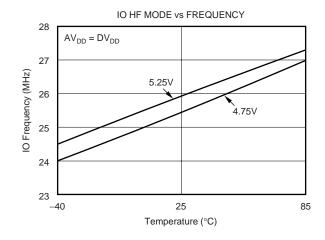

| INTERNAL OSCILLATOR (IO) IO LF Mode IO HF Mode Internal Oscillator Settling Time  | See Typical Characteristics Within 1%                                                                                    |           | 12.8<br>25.6                 | 1   | MHz<br>MHz<br>ms        |

NOTE: (1) Parameters are valid over operating temperature range, unless otherwise specified.

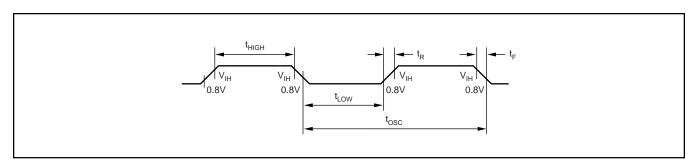

## **EXTERNAL CLOCK DRIVE CLK TIMING**

|                                   |        |                                                          | 2.7V t | o 3.6V | 4.75V t | o 5.25V |       |

|-----------------------------------|--------|----------------------------------------------------------|--------|--------|---------|---------|-------|

| SYMBOL                            | FIGURE | PARAMETER                                                | MIN    | MAX    | MIN     | MAX     | UNITS |

| External Clock Mode               |        |                                                          |        |        |         |         |       |

| f <sub>OSC</sub> <sup>(1)</sup>   | Α      | External Crystal Frequency (f <sub>OSC</sub> )           | 1      | 20     | 1       | 33      | MHz   |

| 1/t <sub>OSC</sub> <sup>(1)</sup> | Α      | External Clock Frequency (f <sub>OSC</sub> )             | 0      | 20     | 0       | 33      | MHz   |

| f <sub>OSC</sub> <sup>(1)</sup>   | Α      | External Ceramic Resonator Frequency (f <sub>OSC</sub> ) | 1      | 12     | 1       | 12      | MHz   |

| t <sub>HIGH</sub>                 | Α      | HIGH Time <sup>(2)</sup>                                 | 15     |        | 10      |         | ns    |

| t <sub>LOW</sub>                  | Α      | LOW Time <sup>(2)</sup>                                  | 15     |        | 10      |         | ns    |

| t <sub>R</sub>                    | Α      | Rise Time <sup>(2)</sup>                                 |        | 5      |         | 5       | ns    |

| t <sub>F</sub>                    | Α      | Fall Time <sup>(2)</sup>                                 |        | 5      |         | 5       | ns    |

NOTES: (1) t<sub>CLK</sub> = 1/f<sub>OSC</sub> = one oscillator clock period for clock divider = 1. (2) These values are characterized but not 100% production tested.

FIGURE A. External Clock Drive CLK.

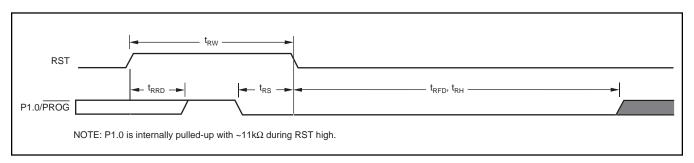

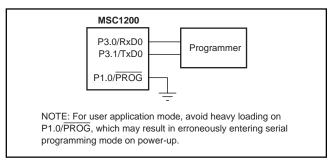

#### **SERIAL FLASH PROGRAMMING TIMING**

| SYMBOL           | FIGURE | PARAMETER                              | MIN                | MAX | UNIT |

|------------------|--------|----------------------------------------|--------------------|-----|------|

| t <sub>RW</sub>  | В      | RST width                              | 2 t <sub>osc</sub> | _   | ns   |

| t <sub>RRD</sub> | В      | RST rise to P1.0 internal pull high    | _                  | 5   | μs   |

| t <sub>RFD</sub> | В      | RST falling to CPU start               | _                  | 18  | ms   |

| t <sub>RS</sub>  | В      | Input signal to RST falling setup time | tosc               | _   | ns   |

| t <sub>RH</sub>  | В      | RST falling to P1.0 hold time          | 18                 | _   | ms   |

FIGURE B. Serial Flash Programming Power-On Timing.

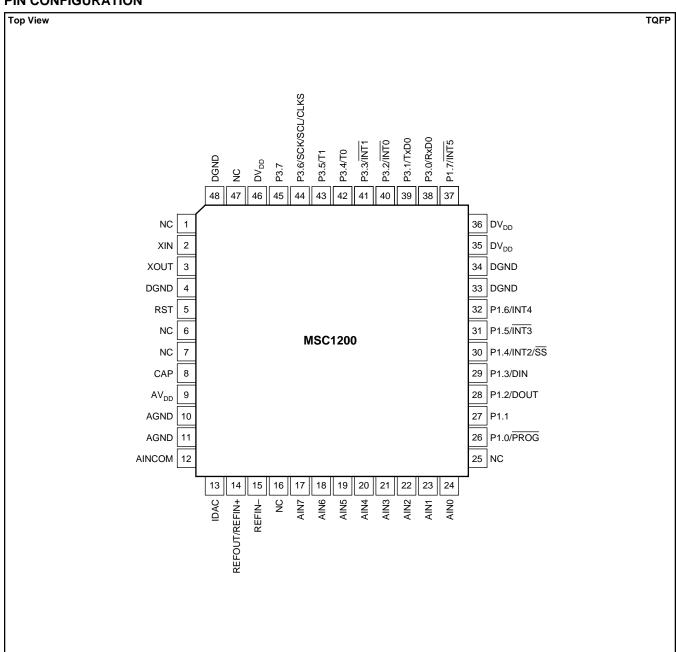

# **PIN CONFIGURATION**

# **PIN DESCRIPTIONS**

| PIN #          | NAME             | DESCRIPTION                                                                                                                                                                                                 |                                                                                         |  |  |  |

|----------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|--|

| 1,6,7,16,25,47 | NC               | No Connection                                                                                                                                                                                               |                                                                                         |  |  |  |

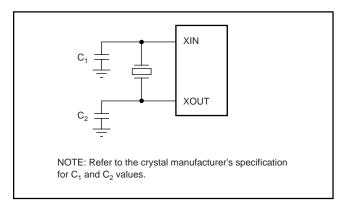

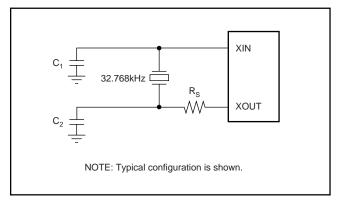

| 2              | XIN              | The crystal oscillator pin XIN supports parallel resonant AT cut fundamental frequency crystals and ceramic resonators. XIN can also be an input if there is an external clock source instead of a crystal. |                                                                                         |  |  |  |

| 3              | XOUT             | The crystal oscillator pin XOUT supports parallel resonant XOUT serves as the output of the crystal amplifier.                                                                                              | AT cut fundamental frequency crystals and ceramic resonators.                           |  |  |  |

| 4, 33, 34, 48  | DGND             | Digital Ground                                                                                                                                                                                              |                                                                                         |  |  |  |

| 5<br>8         | RST<br>CAP       | A HIGH on the reset input for two $t_{\mbox{\scriptsize OSC}}$ periods will reset Capacitor (220pF ceramic)                                                                                                 | he device.                                                                              |  |  |  |

| 9              | AV <sub>DD</sub> | Analog Power Supply                                                                                                                                                                                         |                                                                                         |  |  |  |

| 10, 11         | AGND             | Analog Ground                                                                                                                                                                                               |                                                                                         |  |  |  |

| 12             | AINCOM           | Analog Input (can be analog common for single-ended in                                                                                                                                                      | outs or analog input for differential inputs)                                           |  |  |  |

| 13             | IDAC             | IDAC Output                                                                                                                                                                                                 |                                                                                         |  |  |  |

| 14             | REFOUT/REF IN+   | Internal Voltage Reference Output/Voltage Reference Pos                                                                                                                                                     | itive Input                                                                             |  |  |  |

| 15             | REF IN-          | Voltage Reference Negative Input (tie to AGND for intern                                                                                                                                                    | al voltage reference)                                                                   |  |  |  |

| 17             | AIN7             | Analog Input Channel 7                                                                                                                                                                                      |                                                                                         |  |  |  |

| 18             | AIN6             | Analog Input Channel 6                                                                                                                                                                                      |                                                                                         |  |  |  |

| 19             | AIN5             | Analog Input Channel 5                                                                                                                                                                                      |                                                                                         |  |  |  |

|                | AIN3<br>AIN4     | · .                                                                                                                                                                                                         |                                                                                         |  |  |  |

| 20             |                  | Analog Input Channel 4                                                                                                                                                                                      |                                                                                         |  |  |  |

| 21             | AIN3             | Analog Input Channel 3                                                                                                                                                                                      |                                                                                         |  |  |  |

| 22             | AIN2             | Analog Input Channel 2                                                                                                                                                                                      |                                                                                         |  |  |  |

| 23             | AIN1             | Analog Input Channel 1                                                                                                                                                                                      |                                                                                         |  |  |  |

| 24             | AIN0             | Analog Input Channel 0                                                                                                                                                                                      |                                                                                         |  |  |  |

| 26-32, 37      | P1.0-P1.7        |                                                                                                                                                                                                             | H, and P1DDRH, SFR AFH, for port pin configuration control).                            |  |  |  |

|                |                  | Port 1—Alternate Functions:                                                                                                                                                                                 | 1                                                                                       |  |  |  |

|                |                  | PORT ALTERNATE                                                                                                                                                                                              | MODE                                                                                    |  |  |  |

|                |                  | P1.0 PROG                                                                                                                                                                                                   | Serial Programming Mode                                                                 |  |  |  |

|                |                  | P1.1 N/A                                                                                                                                                                                                    |                                                                                         |  |  |  |

|                |                  | P1.2 DOUT<br>P1.3 DIN                                                                                                                                                                                       | Serial Data Out<br>Serial Data In                                                       |  |  |  |

|                |                  | P1.4 INT2/SS                                                                                                                                                                                                | External Interrupt 2/Slave Select                                                       |  |  |  |

|                |                  | P1.5 INT3                                                                                                                                                                                                   | External Interrupt 3                                                                    |  |  |  |

|                |                  | P1.6 INT4                                                                                                                                                                                                   | External Interrupt 4                                                                    |  |  |  |

|                |                  | P1.7 INT5                                                                                                                                                                                                   | External Interrupt 5                                                                    |  |  |  |

| 38-45          | P3.0-P3.7        | Port 3—Alternate Functions:                                                                                                                                                                                 | 3 <sub>H</sub> , and P3DDRH, SFR B4 <sub>H</sub> , for port pin configuration control). |  |  |  |

|                |                  | PORT ALTERNATE                                                                                                                                                                                              | MODE                                                                                    |  |  |  |

|                |                  | P3.0 RxD0                                                                                                                                                                                                   | Serial Port 0 Input                                                                     |  |  |  |

|                |                  | P3.1 <u>TxD0</u>                                                                                                                                                                                            | Serial Port 0 Output                                                                    |  |  |  |

|                |                  | P3.2 INTO                                                                                                                                                                                                   | External Interrupt 0                                                                    |  |  |  |

|                |                  | P3.3 INT1                                                                                                                                                                                                   | External Interrupt 1                                                                    |  |  |  |

|                |                  | P3.4 T0                                                                                                                                                                                                     | Timer 0 External Input                                                                  |  |  |  |

|                |                  | P3.5 T1                                                                                                                                                                                                     | Timer 1 External Input                                                                  |  |  |  |

|                |                  | P3.6 SCK/SCL/CLKS                                                                                                                                                                                           | SCK/SCL/Various Clocks (refer to PASEL, SFR F2 <sub>H</sub> )                           |  |  |  |

|                |                  | P3.7 N/A                                                                                                                                                                                                    |                                                                                         |  |  |  |

| 35, 36, 46     | DV <sub>DD</sub> | Digital Power Supply                                                                                                                                                                                        |                                                                                         |  |  |  |

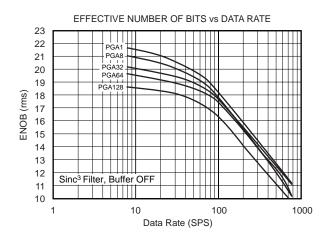

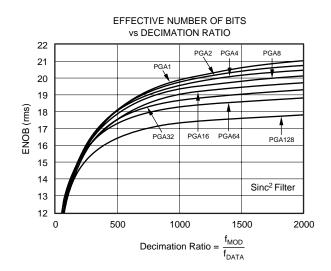

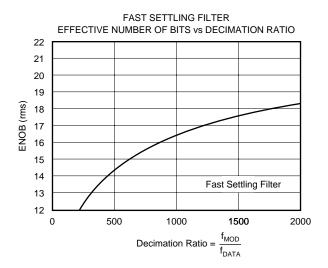

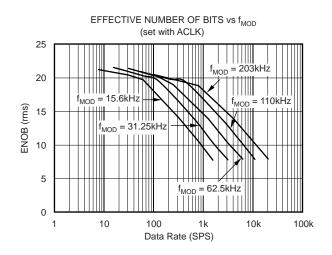

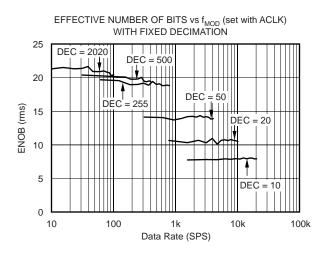

# TYPICAL CHARACTERISTICS

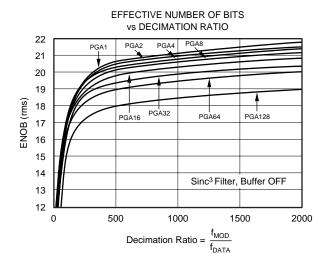

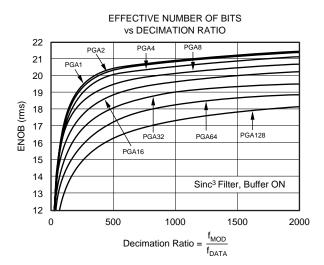

$AV_{DD} = +5V, \ DV_{DD} = +5V, \ f_{OSC} = 8MHz, \ PGA = 1, \ f_{MOD} = 15.625kHz, \ Bipolar, \ Buffer \ ON, \ and \ V_{REF} = (REF \ IN+) - (REF \ IN-) = +2.5V, \ unless \ otherwise \ specified.$

$AV_{DD} = +5V, \ DV_{DD} = +5V, \ f_{OSC} = 8MHz, \ PGA = 1, \ f_{MOD} = 15.625kHz, \ Bipolar, \ Buffer \ ON, \ and \ V_{REF} = (REF \ IN+) - (REF \ IN-) = +2.5V, \ unless \ otherwise \ specified.$

$AV_{DD}$  = +5V,  $DV_{DD}$  = +5V,  $f_{OSC}$  = 8MHz, PGA = 1,  $f_{MOD}$  = 15.625kHz, Bipolar, Buffer ON, and  $V_{REF}$  = (REF IN+) – (REF IN-) = +2.5V, unless otherwise specified.

$\mathsf{AV}_\mathsf{DD} = +5\mathsf{V}, \ \mathsf{DV}_\mathsf{DD} = +5\mathsf{V}, \ \mathsf{f}_\mathsf{OSC} = 8\mathsf{MHz}, \ \mathsf{PGA} = 1, \ \mathsf{f}_\mathsf{MOD} = 15.625\mathsf{kHz}, \ \mathsf{Bipolar}, \ \mathsf{Buffer ON}, \ \mathsf{and} \ \mathsf{V}_\mathsf{REF} \equiv (\mathsf{REF IN+}) - (\mathsf{REF IN-}) = +2.5\mathsf{V}, \ \mathsf{unless otherwise specified}.$

$AV_{DD} = +5V, \ DV_{DD} = +5V, \ f_{OSC} = 8MHz, \ PGA = 1, \ f_{MOD} = 15.625kHz, \ Bipolar, \ Buffer \ ON, \ and \ V_{REF} \equiv (REF \ IN+) - (REF \ IN-) = +2.5V, \ unless \ otherwise \ specified.$

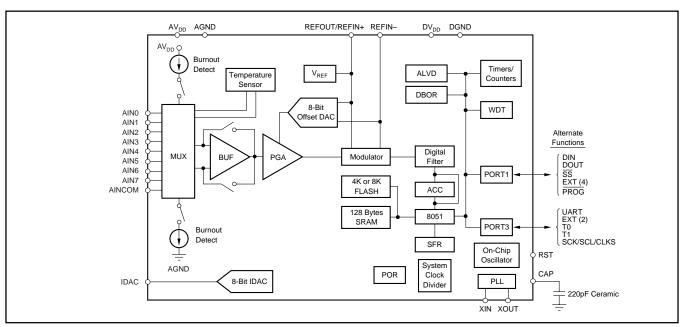

# DESCRIPTION

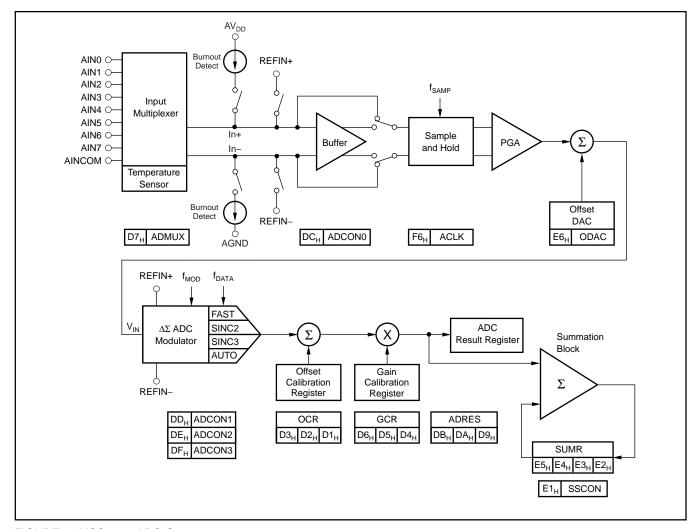

The MSC1200Yx is a completely integrated family of mixedsignal devices incorporating a high-resolution delta-sigma ADC, 8-bit IDAC, 8-channel multiplexer, burnout detect current sources, selectable buffered input, offset DAC, programmable gain amplifier (PGA), temperature sensor, voltage reference, 8-bit microcontroller, Flash Program Memory, Flash Data Memory, and Data SRAM, as shown in Figure 1.

On-chip peripherals include an additional 32-bit accumulator, basic SPI, basic I<sup>2</sup>C, UART, multiple digital input/output ports, watchdog timer, low-voltage detect, on-chip power-on reset, brownout reset, timer/counters, system clock divider, PLL, on-chip oscillator, and external interrupts.

The device accepts low-level differential or single-ended signals directly from a transducer. The ADC provides 24 bits of resolution and 24 bits of no-missing-code performance using a Sinc<sup>3</sup> filter with a programmable sample rate. The ADC also has a selectable filter that allows for high-resolution single-cycle conversion.

The microcontroller core is 8051 instruction set compatible. The microcontroller core is an optimized 8051 core that executes up to three times faster than the standard 8051 core, given the same clock source. This makes it possible to run the device at a lower external clock frequency and achieve the same performance at lower power than the standard 8051 core.

The MSC1200Yx allows the user to uniquely configure the Flash memory map to meet the needs of their application. The Flash is programmable down to 2.7V using serial programming. Flash endurance is typically 1M Erase/Write cycles.

The part has separate analog and digital supplies, which can be independently powered from 2.7V to +5.25V. At +3V operation, the power dissipation for the part is typically less than 4mW. The MSC1200Yx is packaged in a TQFP-48 package.

The MSC1200Yx is designed for high-resolution measurement applications in smart transmitters, industrial process control, weigh scales, chromatography, and portable instrumentation.

#### **ENHANCED 8051 CORE**

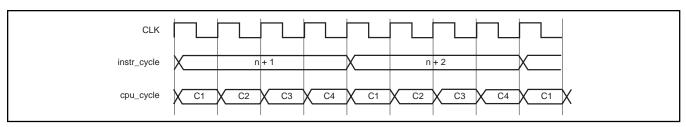

All instructions in the MSC1200 family perform exactly the same functions as they would in a standard 8051. The effect on bits, flags, and registers is the same. However, the timing is different. The MSC1200 family utilizes an efficient 8051 core which results in an improved instruction execution speed of between 1.5 and 3 times faster than the original core for the same external clock speed (4 clock cycles per instruction versus 12 clock cycles per instruction, as shown in Figure 2). This translates into an effective throughput improvement of more than 2.5 times, using the same code and same external clock speed. Therefore, a device frequency of 33MHz for the MSC1200Yx actually performs at an equivalent execution speed of 82.5MHz compared to the

FIGURE 1. Block Diagram.

FIGURE 2. Instruction Cycle Timing.

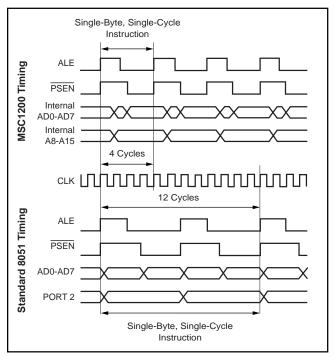

standard 8051 core. This allows the user to run the device at slower clock speeds, which reduces system noise and power consumption, but provides greater throughput. This performance difference can be seen in Figure 3. The timing of software loops will be faster with the MSC1200. However, the timer/counter operation of the MSC1200 may be maintained at 12 clocks per increment or optionally run at 4 clocks per increment.

FIGURE 3. Comparison of MSC1200 Timing to Standard 8051 Timing.

The MSC1200 also provides dual data pointers (DPTRs).

Furthermore, improvements were made to peripheral features that off-load processing from the core and the user, to further improve efficiency. For instance, a 32-bit accumulator was added to significantly reduce the processing overhead for the multiple byte data from the ADC or other sources. This allows for 24-bit addition and shifting to be accomplished in a few instruction cycles, compared to hundreds of instruction cycles through software implementation.

# **Family Device Compatibility**

The hardware functionality and pin configuration across the MSC1200 family is fully compatible. To the user, the only difference between family members is the memory configuration. This makes migration between family members simple. Code written for the MSC1200Y2 can be executed directly on an MSC1200Y3. This gives the user the ability to add or subtract software functions and to freely migrate between family members. Thus, the MSC1200 can become a standard device used across several application platforms.

# **Family Development Tools**

The MSC1200 is fully compatible with the standard 8051 instruction set. This means that the user can develop software for the MSC1200 with existing 8051 development tools. Additionally, a complete, integrated development environment is provided with each demo board, and third-party developers also provide support.

#### **Power Down Modes**

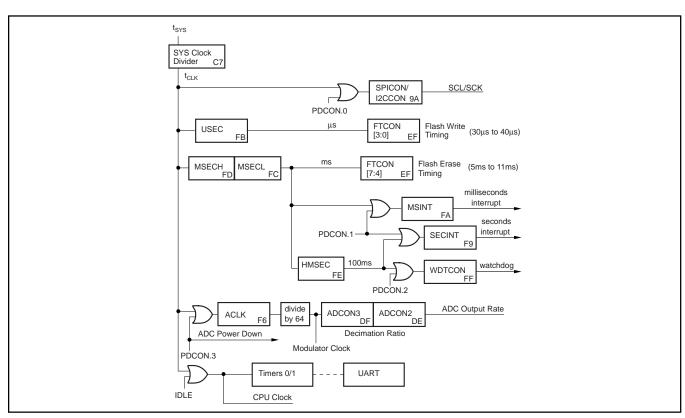

The MSC1200 can power several of the peripherals and put the CPU into IDLE. This is accomplished by shutting off the clocks to those sections, as shown in Figure 4.

FIGURE 4. MSC1200 Timing Chain and Clock Control.

# **OVERVIEW**

The MSC1200 ADC structure is shown in Figure 5. The figure lists the components that make up the ADC, along with the corresponding special function register (SFR) associated with each component.

FIGURE 5. MSC1200 ADC Structure.

#### **INPUT MULTIPLEXER**

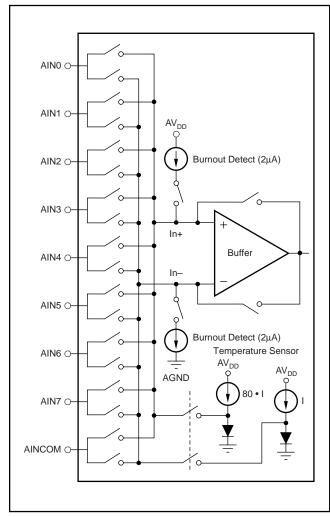

The input multiplexer provides for any combination of differential inputs to be selected as the input channel, as shown in Figure 6. If AINO is selected as the positive differential input channel, any other channel can be selected as the negative differential input channel. With this method, it is possible to have up to eight fully differential input channels. It is also possible to switch the polarity of the differential input pair to negate any offset voltages.

FIGURE 6. Input Multiplexer Configuration.

In addition, current sources are supplied that will source or sink current to detect open or short circuits on the pins.

## **TEMPERATURE SENSOR**

On-chip diodes provide temperature sensing capability. When the configuration register for the input MUX is set to all 1s, the diodes are connected to the input of the ADC. All other channels are open.

#### **BURNOUT DETECT**

When the Burnout Detect (BOD) bit is set in the ADC control configuration register (ADCON0 DC<sub>H</sub>), two current sources are enabled. The current source on the positive input channel sources approximately  $2\mu A$  of current. The current source on the negative input channel sinks approximately  $2\mu A$ . This allows for the detection of an open circuit (full-scale reading) or short circuit (small differential reading) on the selected input differential pair. Enabling the buffer is recommended when BOD is enabled.

#### **INPUT BUFFER**

The analog input impedance is always high, regardless of PGA setting (when the buffer is enabled). With the buffer enabled, the input voltage range is reduced and the analog power-supply current is higher. If the limitation of input voltage range is acceptable, then the buffer is always preferred.

The input impedance of the MSC1200 without the buffer is  $7M\Omega/PGA$ . The buffer is controlled by the state of the BUF bit in the ADC control register (ADCON0 DC<sub>H</sub>).

#### **ANALOG INPUT**

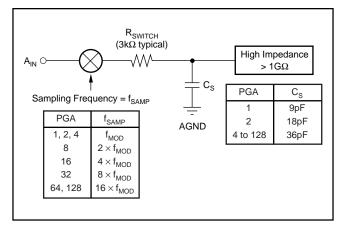

When the buffer is not selected, the input impedance of the analog input changes with ACLK clock frequency (ACLK  $F6_H$ ) and gain (PGA). The relationship is:

$$\begin{split} &A_{IN}\,\text{Impedance}\,(\Omega) = & \left(\frac{1\,\text{MHz}}{\text{ACLK}\,\text{Frequency}}\right) \bullet \left(\frac{7\text{M}\Omega}{\text{PGA}}\right) \\ &\text{where ACLK}\,\,\text{frequency}\,\,(f_{ACLK}) = \frac{f_{CLK}}{\text{ACLK}+1} \\ &\text{and}\,\,f_{MOD} = \frac{f_{ACLK}}{64}. \end{split}$$

Figure 7 shows the basic input structure of the MSC1200.

FIGURE 7. Analog Input Structure (without buffer).

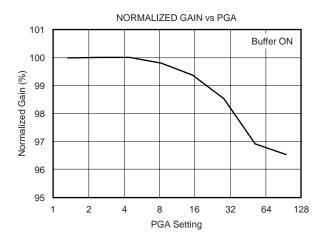

#### **PGA**

The PGA can be set to gains of 1, 2, 4, 8, 16, 32, 64, or 128. Using the PGA can actually improve the effective resolution of the ADC. For instance, with a PGA of 1 on a  $\pm 2.5 \text{V}$  full-scale range, the ADC can resolve to  $1.5 \mu\text{V}$ . With a PGA of 128 on a  $\pm 19 \text{mV}$  full-scale range, the ADC can resolve to 75nV. With a PGA of 1 on a  $\pm 2.5 \text{V}$  full-scale range, it would require a 26-bit ADC to resolve 75nV, as shown in Table I.

| PGA<br>SETTING | FULL-SCALE<br>RANGE<br>(V) | ENOB<br>AT 10Hz<br>(BITS) | RMS<br>MEASUREMENT<br>RESOLUTION<br>(nV) |

|----------------|----------------------------|---------------------------|------------------------------------------|

| 1              | ±2.5                       | 21.7                      | 1468                                     |

| 2              | ±1.25                      | 21.5                      | 843                                      |

| 4              | ±0.625                     | 21.4                      | 452                                      |

| 8              | ±0.313                     | 21.2                      | 259                                      |

| 16             | ±0.156                     | 20.8                      | 171                                      |

| 32             | ±0.0781                    | 20.4                      | 113                                      |

| 64             | ±0.039                     | 20                        | 74.5                                     |

| 128            | ±0.019                     | 19                        | 74.5                                     |

TABLE I. ENOB Versus PGA.

#### **OFFSET DAC**

The analog output from the PGA can be offset by up to half the full-scale input range of the PGA by using the ODAC register (SFR E6 $_{\rm H}$ ). The ODAC (Offset DAC) register is an 8-bit value; the MSB is the sign and the seven LSBs provide the magnitude of the offset. Since the ODAC introduces an analog (instead of digital) offset to the PGA, using the ODAC does not reduce the range of the ADC.

#### **MODULATOR**

The modulator is a single-loop 2nd-order system. The modulator runs at a clock speed ( $f_{MOD}$ ) that is derived from the CLK using the value in the Analog Clock register (ACLK, F6<sub>H</sub>). The data output rate is:

$$\label{eq:Data_Rate} \begin{aligned} \text{Data Rate} &= f_{\text{DATA}} = \frac{f_{\text{MOD}}}{\text{Decimation Ratio}} \\ \text{where } f_{\text{MOD}} &= \frac{f_{\text{CLK}}}{(\text{ACLK}+1) \bullet 64} = \frac{f_{\text{ACLK}}}{64} \end{aligned}$$

#### **CALIBRATION**

The offset and gain errors in the MSC1200, or the complete system, can be reduced with calibration. Calibration is controlled through the ADCON1 register (SFR DD<sub>H</sub>), bits CAL2:CAL0. Each calibration process takes seven  $t_{DATA}$  periods (data conversion time) to complete. Therefore, it takes 14  $t_{DATA}$  periods to complete both an offset and gain calibration.

For system calibration, the appropriate signal must be applied to the inputs. The system offset calibration requires a zero-differential input signal. It then computes an offset value that will nullify offset in the system. The system gain calibration

requires a positive full-scale differential input signal. It then computes a gain value to nullify gain errors in the system. Each of these calibrations will take seven  $t_{\mathsf{DATA}}$  periods to complete.

Calibration should be performed after power on, a change in temperature, power supply, voltage reference, decimation ratio, buffer, or a change of the PGA. Calibration will remove the effects of the Offset DAC; therefore, changes to the Offset DAC register should be done after calibration.

At the completion of calibration, the ADC Interrupt bit goes high, which indicates the calibration is finished and valid data is available.

#### **DIGITAL FILTER**

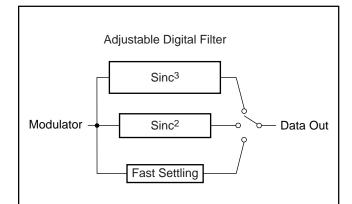

The Digital Filter can use either the Fast Settling, Sinc<sup>2</sup>, or Sinc<sup>3</sup> filter, as shown in Figure 8. In addition, the Auto mode changes the Sinc filter after the input channel or PGA is changed. When switching to a new channel, it will use the Fast Settling filter, for the next two conversions the first of which should be discarded. It will then use the Sinc<sup>2</sup> followed by the Sinc<sup>3</sup> filter to improve noise performance. This combines the low-noise advantage of the Sinc<sup>3</sup> filter with the quick response of the Fast Settling Time filter. The frequency response of each filter is shown in Figure 9.

#### FILTER SETTLING TIME

| FILTER            | SETTLING TIME<br>(Conversion Cycles) |

|-------------------|--------------------------------------|

| Sinc <sup>3</sup> | 3 <sup>(1)</sup>                     |

| Sinc <sup>2</sup> | 2 <sup>(1)</sup>                     |

| Fast              | 1 <sup>(1)</sup>                     |

NOTE: (1) With Synchronized Channel Changes.

#### **AUTO MODE FILTER SELECTION**

| CONVERSION CYCLE |      |                   |                   |  |  |  |

|------------------|------|-------------------|-------------------|--|--|--|

| 1                | 2    | 3                 | 4+                |  |  |  |

| Discard          | Fast | Sinc <sup>2</sup> | Sinc <sup>3</sup> |  |  |  |

FIGURE 8. Filter Step Responses.

FIGURE 9. Filter Frequency Responses.

#### **VOLTAGE REFERENCE**

The voltage reference used for the MSC1200 can either be internal or external. The power-up configuration for the voltage reference is 2.5V internal. The selection for the voltage reference is made through the ADCON0 register (SFR DC<sub>H</sub>).

The internal voltage reference is selectable as either 1.25V (AV<sub>DD</sub> = 2.7V to 5.25V) or 2.5V (AV<sub>DD</sub> = 4.1V to 5.25V). If the internal V<sub>REF</sub> is not used, it should be turned off. The REFOUT/REFIN+ pin should have a  $0.1\mu F$  capacitor to AGND.

The external voltage reference is differential and is represented by the voltage difference between the pins: REFIN+ and REFIN-. The absolute voltage on either pin (REFIN+ and REFIN-) can range from AGND to AV<sub>DD</sub>; however, the differential voltage must not exceed AV<sub>DD</sub>. The differential voltage reference provides easy means of performing ratiometric measurement.

#### **IDAC**

The 8-bit IDAC in the MSC1200 can be used to provide a current source that can be used for ratiometric measurements. The full-scale output current of the IDAC is approximately 1mA. The equation for the IDAC output current is:

IDACOUT = IDAC • 3.8μA

#### **DIGITAL BROWNOUT RESET**

The MSC1200 contains a programmable digital brownout reset (DBOR). When the digital supply drops below the value programmed in HCR1, the device is held in a reset state until the supply rises above this value. Once the supply rises above this value, the device is released from reset and executes a normal POR sequence. The digital supply voltage comparison is performed against an analog reference, and therefore, the analog supply must be within the valid operating range in order to use DBOR.

#### **ANALOG LOW VOLTAGE DETECT**

The MSC1200 contains an analog low-voltage detect. When the analog supply drops below the value programmed in LVDCON (SFR  $E7_H$ ), an interrupt is generated.

#### POWER-UP—SUPPLY VOLTAGE RAMP RATE

The built-in (on-chip) power-on reset circuitry was designed to accommodate analog or digital supply ramp rates as slow as 1V/10ms. To ensure proper operation, the power supply should ramp monotonically at the specified rate. If DBOR is enabled, the ramp rate can be slower.

#### **RESET**

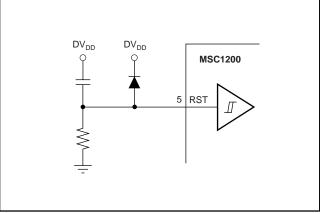

A typical reset circuit is shown in Figure 10.

FIGURE 10. Typical Reset Circuit.

#### **CLOCKS**

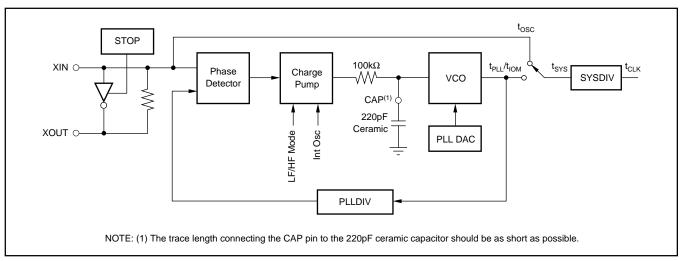

The MSC1200 can operate in three separate clock modes: internal oscillator mode (IOM), external clock mode (ECM), and PLL mode. A block diagram is shown in Figure 11. The clock mode for the MSC1200 is selected via the CLKSEL bits in HCR2. IOM is the default mode for the device.

Serial Flash Programming mode uses IO LF mode (the HCR2 and CLKSEL bits have no effect). Table II shows the active clock mode for the various startup conditions.

#### Internal Oscillator

In IOM, the CPU executes either in LF mode (if HCR2, CLKSEL = 111) or HF mode (if HCR2, CLKSEL = 110).

#### **External Clock**

In ECM (HCR2, CLKSEL = 011), the CPU can execute from an external crystal, external ceramic resonator, external clock, or external oscillator. If an external clock is detected at startup, then the CPU will begin execution in ECM after startup. If an external clock is not detected at startup, then the device will revert to the mode shown in Table II.

#### **PLL**

In Phase Lock Loop (PLL) mode (HCR2, CLKSEL = 101 or HCR2, CLKSEL = 100), the CPU can execute from an external 32.768 kHz crystal. This mode enables the use of a phase-lock loop (PLL) circuit that synthesizes the selected clock frequencies (PLL LF mode or PLL HF mode). If an external clock is detected at startup, then the CPU will begin execution in PLL mode after startup. If an external clock is not detected at startup, then the device will revert to the mode shown in Table II. The status of the PLL can be determined by first writing the PLLLOCK bit (enable) and then reading the PLLLOCK status bit in the PLLH SFR.

The frequency of the PLL is preloaded with default trimmed values. However, the PLL frequency can be fine-tuned by writing to the PLLDIV1 and PLLDIV0 SFRs. The equation for the PLL frequency is:

PLL Frequency =

$$((PLLDIV9:PLLDIV0) + 1) \cdot f_{OSC}$$

where  $f_{OSC} = 32.768kHz$ .

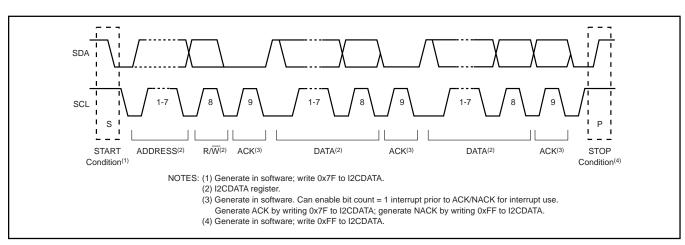

The default value for PLL LF mode is automatically loaded into the PLLDIV SFR. For PLL HF mode, the user must load PLLDIV with the appropriate value (0383<sub>H</sub>).