### SN54LS690, SN54LS691, SN54LS693 SN74LS690, SN74LS691, SN74LS693

Synchronous Counters with Output Registers and Multiplexed 3-State Outputs

These low-power Schottky LSI devices incorporate synchronous counters, four-bit D-type registers, and quadruple two-line to one-line multiplexers with three-state outputs in a single 20-pin package. The counters can be programmed from the data inputs and have enable P inputs and enable T inputs and a ripple-carry output for easy expansion. The register/counter select input,  $R/\overline{C}$ , selects the counter when low or the register when high for the three-state outputs,  $Q_A$ ,  $Q_B$ ,  $Q_C$ , and  $Q_D$ . These outputs are rated 12 and 24 milliamperes (54LS/74LS) for good bus-driving performance.

## Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

#### **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- · Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

#### SN54LS690, SN54LS691, SN54LS693, SN74LS690, SN74LS691, SN74LS693 SYNCHRONOUS COUNTERS WITH OUTPUT REGISTERS AND MULTIPLEXED 3-STATE OUTPUTS

D2423, JANUARY 1981-REVISED MARCH 1988

- 4-Bit Counters/Registers

- Multiplexed Outputs for Counter or Latched Data

- 3-State Outputs Drive Bus Lines Directly

- 'LS690 . . Decade Counter, Direct Clear 'LS691 . . Binary Counter, Direct Clear 'LS693 . . Binary Counter, Synchronous

#### description

These low-power Schottky LSI devices incorporate synchronous counters, four-bit D-type registers, and quadruple two-line to one-line multiplexers with three-state outputs in a single 20-pin package. The counters can be programmed from the data inputs and have enable P inputs and enable T inputs and a ripple-carry output for easy expansion. The register/counter select input, R/C, selects the counter when low or the register when high for the three-state outputs, QA, QB, QC, and QD. These outputs are rated at 12 and 24 milliamperes (54LS/74LS) for good bus-driving performance.

Individual clock and clear inputs are provided for both the counter and the register. Both clock inputs are positive-edge triggered: The clear line is active low and is asynchronous on the 'LS690 and 'LS691, synchronous on the 'LS693. Loading of the counter is accomplished when  $\overline{\text{LOAD}}$  is taken low and a positive-transition occurs on the counter clock CCK.

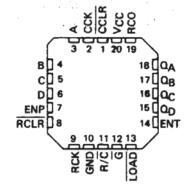

Expansion is easily accomplished by connecting RCO of the first stage to ENT of the second state, etc. All ENP inputs can be tied common and used as master enable or disable control. SN54LS690, SN54LS691, SN54LS693...J PACKAGE SN74LS690, SN74LS691, SN74LS693...DW OR N PACKAGE (TOP VIEW)

SN54LS690, SN54LS691, SN54LS693 . . . FK PACKAGE (TOP VIEW)

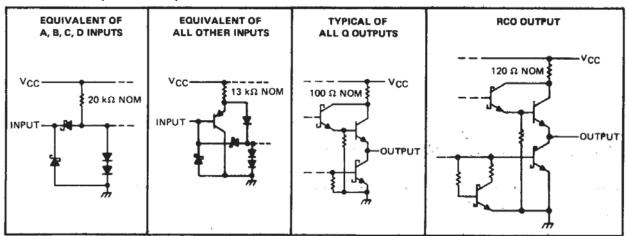

#### schematics of inputs and outputs

PRODUCTION DATA desuments contain information current as of publication data. Products conform to apacifications pur the turns of Toxas instruments standard warranty. Production processing does not necessarily include testing of all persumeters.

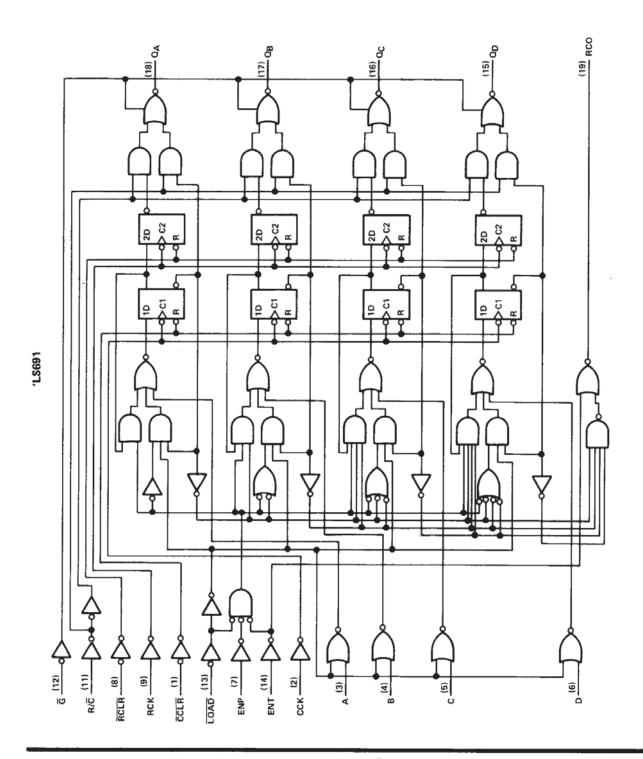

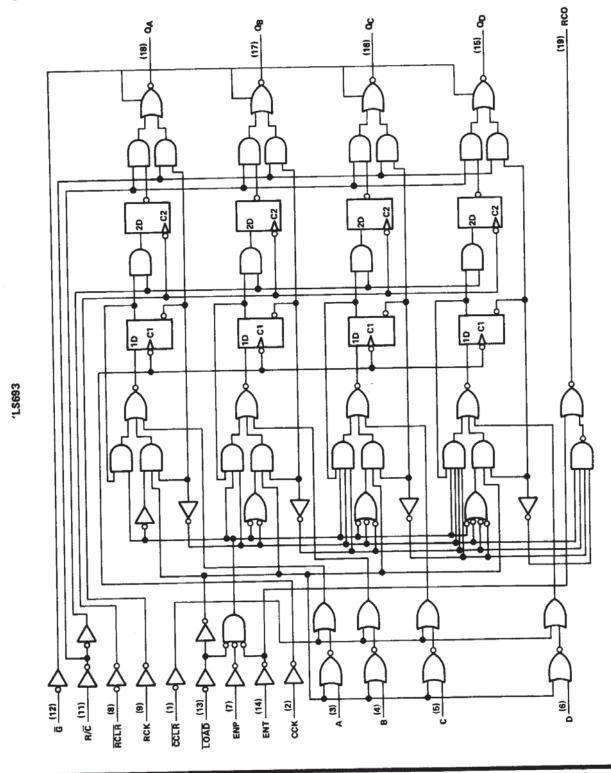

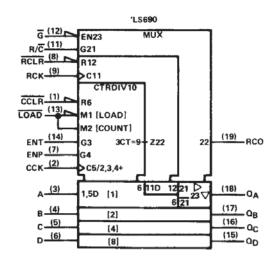

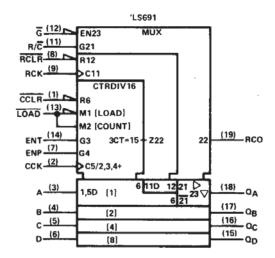

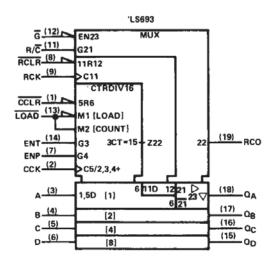

logic diagrams (positive logic) (continued)

#### SN54LS690, SN54LS691, SN54LS693, SN74LS690, SN74LS691, SN74LS693 SYNCHRONOUS COUNTERS WITH OUTPUT REGISTERS AND MULTIPLEXED 3-STATE OUTPUTS

#### logic symbols†

<sup>&</sup>lt;sup>†</sup>These symbols are in accordance with ANSI/IEEE Std. 91-1984 and IEC Publication 617-12.

# SN54LS690, SN54LS691, SN54LS693, SN74LS690, SN74LS691, SN74LS693 SYNCHRONOUS COUNTERS WITH OUTPUT REGISTERS AND MULTIPLEXED 3-STATE OUTPUTS

|                                  | ng free-air temperature range (unless otherwise noted)                                       |

|----------------------------------|----------------------------------------------------------------------------------------------|

| Supply voltage, VCC (See Note 1) |                                                                                              |

| Input voltage                    | 5.5                                                                                          |

| Off-state output voltage         | SN54LS690, SN54LS691, SN54LS693 -55°C to 125<br>SN74LS690, SN74LS691, SN74LS693 -65°C to 150 |

NOTE 1: Voltage values are with respect to network ground terminal.

#### recommended operating conditions

|                    |                                                                      |                   |                    | 1   | SN54LS' |       | SN74LS' |     |       | UNIT |

|--------------------|----------------------------------------------------------------------|-------------------|--------------------|-----|---------|-------|---------|-----|-------|------|

|                    |                                                                      |                   |                    | MIN | NOM     | MAX   | MIN     | NOM | MAX   | ONT  |

| 1                  | Supply voltage                                                       |                   |                    | 4.5 | 5       | 5.5   | 4.75    | 5   | 5.25  | V    |

| vcc_               | High-level input                                                     | . voltage         |                    | 2   |         |       | 2       |     |       | ٧    |

| VIH                |                                                                      |                   |                    |     |         | 0.7   |         |     | 0.8   | V    |

| VIL_               | Low-level input                                                      | voltage           | 0                  |     |         | 1     |         |     | - 2.6 | mA   |

| Іон                | High-level output current  Low-level output current  Clock frequency |                   | BCO                |     |         | - 0.4 |         |     | - 0.4 | mA   |

|                    |                                                                      |                   | Q                  |     |         | 12    |         |     | 24    | mA   |

| OL                 |                                                                      |                   | RCO                |     |         | 4     |         |     | 8     | mA   |

|                    |                                                                      |                   | CCK                | 0   |         | 20    | 0       |     | 20    | MH   |

| f <sub>clock</sub> |                                                                      |                   | RCK                | 0   |         | 20    | 0       |     | 20    | МН   |

| t <sub>w</sub>     | Pulse duration                                                       |                   | CCK high or low    | 25  |         |       | 25.     |     |       | ns   |

|                    |                                                                      |                   | RCK high or low    | 25  |         |       | 25      |     |       |      |

|                    |                                                                      |                   | RCLR low           | 20  |         |       | 20      |     |       |      |

|                    |                                                                      | 'LS690, 'LS691    | CCLR low           | 20  |         |       | 20      |     |       | -    |

| t <sub>su</sub>    | Setup time                                                           |                   | A thru D           | 30  |         |       | 30      |     |       | ns   |

|                    |                                                                      |                   | ENP or ENT         | 30  |         |       | 30      |     |       |      |

|                    |                                                                      |                   | LOAD +             | 30  |         |       | 30      |     |       |      |

|                    | before CCK †                                                         | 'LS693            | CCLR +             | 40  |         |       | 40      |     |       |      |

|                    |                                                                      | 'LS690, 'LS691    | CCLR † inactive    | 25  |         |       | 25      |     |       |      |

|                    |                                                                      |                   | CCK † (see Note 2) | 30  |         |       | 30      |     |       | 4    |

| t <sub>su</sub>    | Setup time<br>before RCK †                                           | 'LS690, 'LS691    | RCLR † inactive    | 25  |         |       | 25      |     |       | ns   |

|                    |                                                                      | 'LS693            | RCLR +             | 20  |         |       | 20      |     |       | -    |

| th                 | Hold time                                                            | Any input from CC | K t or RCK t       | 0   |         |       | 0       |     |       | ns   |

| TA                 | Operating free-air temperature                                       |                   |                    | 55  |         | 125   | 0       |     | 70    | °c   |

NOTE 2: This set up time ensures the register will see stable data from the counter outputs. The clocks may be tied together in which case the register state will be one clock pulse behind the counter.

#### SN54LS690, SN54LS691, SN54LS693, SN74LS690, SN74LS691, SN74LS693 SYNCHRONOUS COUNTERS WITH OUTPUT REGISTERS AND MULTIPLEXED 3-STATE OUTPUTS

switching characteristics,  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$  (see note 6)

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST CONDITIONS                                | 'LS690, 'L | 'LS693 |              |    | UNIT |          |

|------------------|-----------------|----------------|------------------------------------------------|------------|--------|--------------|----|------|----------|

|                  |                 |                |                                                | MIN TYP    | MAX    | MIN T        |    | MAX  |          |

|                  | CCK1            | RCO            | R <sub>L</sub> = 2 kΩ, C <sub>L</sub> = 15 pF  | 23         | 40     |              | 23 | 40   | -I ns    |

| tPLH             |                 |                |                                                | 23         | 40     |              | 23 | 40   |          |

| tPHL             |                 |                |                                                | 13         | 20     |              | 13 | 20   |          |

| tPLH .           | ENT             | RCO            |                                                | 13         | 20     |              | 13 | 20   | ns       |

| †PHL             |                 |                |                                                | 12         |        | <del> </del> | 12 | 20   |          |

| tPLH.            | CCK†            | Q              |                                                | 17         | 25     | -            | 17 | 25   | ns       |

| tPHL             | 7 000           |                |                                                |            |        | <del> </del> |    | 20   | ₩-       |

| tPLH             |                 | a              |                                                | 12         |        | <b>↓</b> —   | 12 |      | ns       |

|                  | - RCK1          |                |                                                | 17         | 25     |              | 17 | 25   |          |

| tPHL             | CCLR↓           | Ω              | 1                                              | 23         | 40     |              |    |      | ns       |

| tPHL             | RCLR            | a              | 1                                              | 20         | 30     |              |    |      | ns       |

| tPHL             | HCLN+           |                | R <sub>L</sub> = 667 Ω, C <sub>L</sub> = 45 pF | 16         | 25     |              | 16 | 25   | -⊢ ns    |

| tPLH             | R/C             |                |                                                | 16         | 25     |              | 16 | 25   |          |

| <b>tPHL</b>      |                 |                |                                                | 19         |        |              | 19 | 30   | <u>,</u> |

| <sup>t</sup> PZH | Ğ↓              | α              |                                                | 19         |        | +            | 19 | 30   | –ì ns    |

| tPZL             | 7 "             |                |                                                |            |        |              | 17 | 30   |          |

| tPHZ             | Ē.              | Gt Q           | R <sub>L</sub> = 667 Ω, C <sub>L</sub> = 5 pF  | 17         |        |              |    | 30   | → ns     |

| tPLZ             | ٠, ١            |                |                                                | 17         | 30     | L            | 17 | 30   |          |

NOTE 6: Load circuits and voltage waveforms are shown in Section 1.

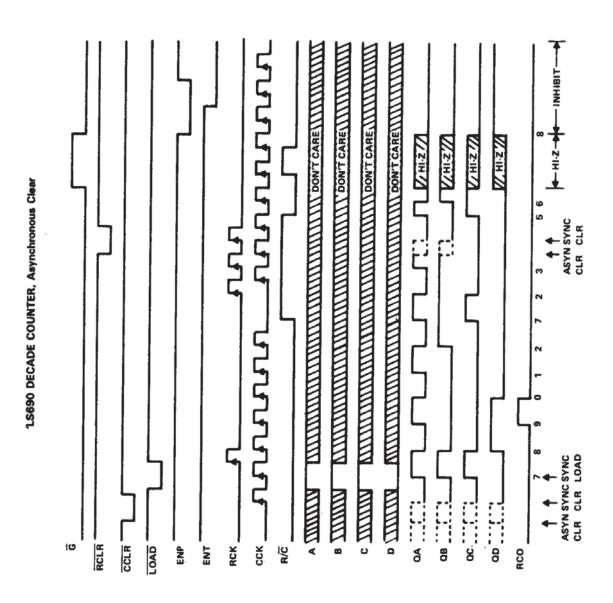

typical operating sequences

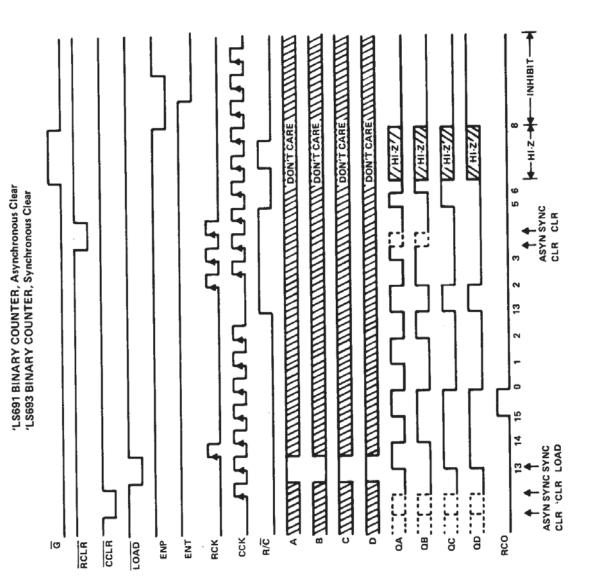

typical operating sequences (continued)

N TTL Devices