SDLS123 - MARCH 1974 - REVISED MARCH 1988

| TYPE          | TYPICAL POWER | TYPICAL<br>DELAY |

|---------------|---------------|------------------|

| 1117          | DISSIPATION   | (4-BIT WORDS)    |

| <b>'85</b>    | 275 mW        | 23 ns            |

| <b>LS85</b>   | 52 mW         | 24 ns            |

| <b>'</b> \$85 | 365 mW        | 11 ns            |

### description

These four-bit magnitude comparators perform comparison of straight binary and straight BCD (8-4-2-1) codes. Three fully decoded decisions about two 4-bit words (A, B) are made and are externally available at three outputs. These devices are fully expandable to any number of bits without external gates. Words of greater length may be compared by connecting comparators in cascade. The A > B, A < B, and A = B outputs of a stage handling less-significant bits are connected to the corresponding A > B, A < B, and A = B inputs of the next stage handling more-significant bits. The stage handling the least-significant bits must have a high-level voltage applied to the A = B input. The cascading paths of the '85, 'LS85, and 'S85 are implemented with only a two-gate-level delay to reduce overall comparison times for long words. An alternate method of cascading which further reduces the comparison time is shown in the typical application data.

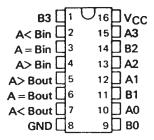

#### SN5485, SN54LS85, SN54S85 . . . J OR W PACKAGE SN7485 : . . N PACKAGE SN74LS85, SN74S85 . . . D OR N PACKAGE (TOP VIEW)

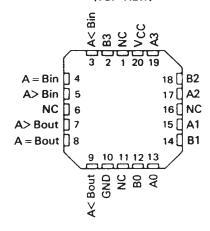

# SN54LS85, SN54S85 . . . FK PACKAGE (TOP VIEW)

NC - No internal connection

#### **FUNCTION TABLE**

|         | COMPARING<br>INPUTS |         |         | CASCADING<br>INPUTS |       |       | OUTPUTS |       |       |  |

|---------|---------------------|---------|---------|---------------------|-------|-------|---------|-------|-------|--|

| A3, B3  | A2, B2              | A1, B1  | A0, B0  | A > B               | A < B | A = B | A > B   | A < B | A = 8 |  |

| A3 > B3 | X                   | ×       | ×       | Х                   | Х     | Х     | Н       | L     | L     |  |

| A3 < B3 | ×                   | ×       | ×       | ×                   | X     | ×     | L       | Н     | L     |  |

| A3 = B3 | A2 > B2             | ×       | ×       | ×                   | X     | ×     | н       | L     | L     |  |

| A3 = B3 | A2 < B2             | ×       | ×       | ×                   | X     | ×     | L       | Н     | L     |  |

| A3 = B2 | A2 = B2             | A1 > B1 | ×       | ×                   | X     | ×     | н       | L     | L     |  |

| A3 = B3 | A2 = B2             | A1 < B1 | ×       | ×                   | X     | ×     | L       | н     | L     |  |

| A2 = B3 | A2 = B2             | A1 = B1 | A0 > B0 | ×                   | X     | ×     | н       | L     | L     |  |

| A3 = B3 | A2 = B2             | A1 = B1 | A0 < 80 | ×                   | X     | ×     | L       | Н     | L     |  |

| A3 = B3 | A2 = B2             | A1 = B1 | A0 = 80 | н                   | L     | L     | Н       | L     | L     |  |

| A3 = B3 | A2 = B2             | A1 = B1 | AO = BO | L                   | Н     | L     | L       | Н     | L     |  |

| A3 = B3 | A2 = B2             | A1 = B1 | A0 = B0 | ×                   | X     | н     | L       | L     | н     |  |

| A3 = B3 | A2 = B2             | A1 = B1 | AO = BO | н                   | н     | Ł     | L       | L     | L     |  |

| A3 = B3 | A2 = B2             | A1 = B1 | A0 = B0 | L                   | L     | L_    | н       | Н     | L     |  |

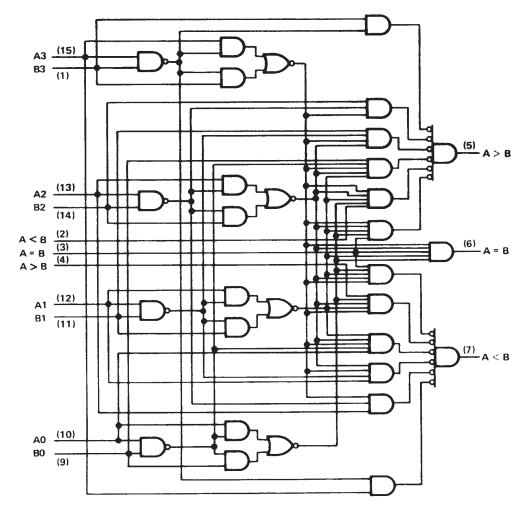

# logic diagrams (positive logic)

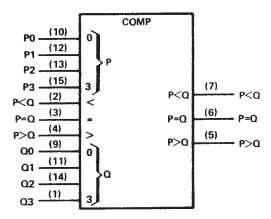

logic symbol†

†This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12. Pin numbers shown are for D, J, N, and W packages.

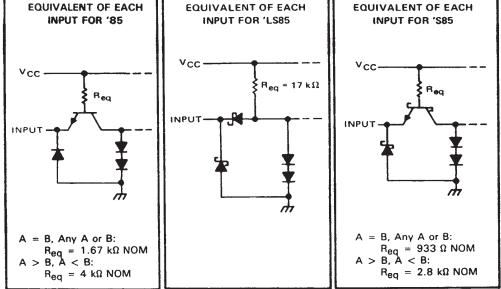

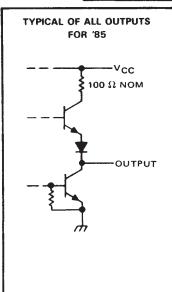

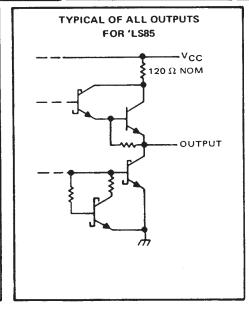

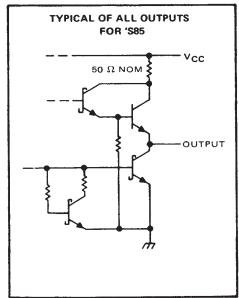

# schematics of inputs and outputs

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

|                                              | SN54'<br>SN54S' | SN54LS'         | SN74'<br>SN74S' | SN74LS' | UNIT |

|----------------------------------------------|-----------------|-----------------|-----------------|---------|------|

| Supply voltage, V <sub>CC</sub> (see Note 1) | 7               | 7               | 7               | 7       | V    |

| Input voltage                                | 5.5             | 7               | 5.5             | 7       | V    |

| Interemitter voltage (see Note 2)            | 5.5             |                 | 5.5             |         | V    |

| Operating free-air temperature range         | - 55            | to 125 -0 to 70 |                 | to 70   | °C   |

| Storage temperature range                    | -65             | - 65 to 150     |                 | to 150  | °C   |

NOTES: 1. Voltage values, except interemitter voltage, are with respect to network ground terminal.

2. This is the voltage between two emitters of a multiple-emitter input transistor. This rating applies to each A input in conjunction with its respective B input of the '85 and 'S85.

# SN5485, SN54LS85, SN54S85 SN7485, SN74LS85, SN74S85 4-BIT MAGNITUDE COMPARATORS

SDLS123 - MARCH 1974 - REVISED MARCH 1988

#### recommended operating conditions

|                                    |     | SN5485 |      |      | SN7485 |      |      |

|------------------------------------|-----|--------|------|------|--------|------|------|

|                                    | MIN | NOM    | MAX  | MIN  | NOM    | MAX  | UNIT |

| Supply voltage, V <sub>CC</sub>    | 4.5 | 5      | 5.5  | 4.75 | 5      | 5.25 | ٧    |

| High-level output current, IOH     |     |        | -400 |      |        | -400 | μΑ   |

| Low-level output current, IOL      |     |        | 16   |      |        | 16   | mA   |

| Operating free-air temperature, TA | -55 |        | 125  | 0    |        | 70   | °C   |

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER                   |                                          |                     | TE                                                 | TEST CONDITIONS† |                                                     |         | MIN | TYP‡ | MAX  | UNIT |  |  |    |  |  |  |  |  |  |        |    |       |  |        |     |  |     |  |

|-----------------------------|------------------------------------------|---------------------|----------------------------------------------------|------------------|-----------------------------------------------------|---------|-----|------|------|------|--|--|----|--|--|--|--|--|--|--------|----|-------|--|--------|-----|--|-----|--|

| ViH                         | V <sub>1H</sub> High-level input voltage |                     |                                                    |                  |                                                     |         | 2   |      |      | V    |  |  |    |  |  |  |  |  |  |        |    |       |  |        |     |  |     |  |

| VIL Low-level input voltage |                                          |                     |                                                    |                  |                                                     |         |     | 0.8  | ٧    |      |  |  |    |  |  |  |  |  |  |        |    |       |  |        |     |  |     |  |

| VIK                         | Input clamp voltage                      |                     | V <sub>CC</sub> = MIN,                             |                  | I <sub>I</sub> = -12 mA                             |         |     |      | -1.5 | V    |  |  |    |  |  |  |  |  |  |        |    |       |  |        |     |  |     |  |

| Vон                         | າພ High-level output voltage 1           |                     | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, |                  | V <sub>IH</sub> = 2 V,<br>t <sub>OH</sub> = -400 μA |         | 2.4 | 3.4  |      | ٧    |  |  |    |  |  |  |  |  |  |        |    |       |  |        |     |  |     |  |

| VOL                         | Low-level output voltage                 |                     | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, |                  | V <sub>IH</sub> = 2 V,<br>I <sub>OL</sub> = 16 mA   |         |     | 0.2  | 0.4  | V    |  |  |    |  |  |  |  |  |  |        |    |       |  |        |     |  |     |  |

| 11                          | Input current at maximum input voltage   |                     | V <sub>CC</sub> = MAX,                             |                  | V <sub>I</sub> = 5.5 V                              |         |     |      | 1    | mA   |  |  |    |  |  |  |  |  |  |        |    |       |  |        |     |  |     |  |

| 1                           | Mich fourt innue course                  | A < B, A > B inputs | V <sub>CC</sub> = MAX, V <sub>I</sub> =            |                  | V <sub>I</sub> = 2.4 V                              |         |     |      | 40   |      |  |  |    |  |  |  |  |  |  |        |    |       |  |        |     |  |     |  |

| ΉΗ                          | High-level input current                 | all other inputs    |                                                    |                  | V  = 2.4                                            | = 2.4 V |     |      | 120  | μΑ   |  |  |    |  |  |  |  |  |  |        |    |       |  |        |     |  |     |  |

| 1                           | Law law Line Annual                      | A < B, A > B inputs | V - MAY                                            | V = 0.4 V        |                                                     |         |     | -1.6 |      |      |  |  |    |  |  |  |  |  |  |        |    |       |  |        |     |  |     |  |

| 11L                         | Low-level input current                  | all other inputs    | V <sub>CC</sub> = MAX,                             |                  | $V_1 = 0.4 V$                                       |         |     | -4.8 |      | mA   |  |  |    |  |  |  |  |  |  |        |    |       |  |        |     |  |     |  |

|                             |                                          |                     | V <sub>CC</sub> = MAX, V <sub>O</sub>              |                  |                                                     | .,      |     |      |      |      |  |  | ., |  |  |  |  |  |  | V 444V | ., | · · · |  | SN5485 | -20 |  | -55 |  |

| los                         | IOS Short-circuit output current §       |                     |                                                    | v0 = 0           | SN7485                                              |         | -18 |      | -55  | mA   |  |  |    |  |  |  |  |  |  |        |    |       |  |        |     |  |     |  |

| 1cc                         | Supply current                           |                     | V <sub>CC</sub> = MAX,                             | See Note 4       |                                                     |         |     | 55   | 88   | mA   |  |  |    |  |  |  |  |  |  |        |    |       |  |        |     |  |     |  |

$<sup>^\</sup>dagger$ For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

NOTE 4:  $I_{CC}$  is measured with outputs open, A = B grounded, and all other inputs at 4.5 V.

# switching characteristics, VCC = 5 V, TA = 25°C

| PARAMETER <sup>¶</sup> | FROM<br>INPUT         | TO OUTPUT      | NUMBER OF GATE LEVELS | TEST CONDITIONS                                       | MIN T | YP MA | רואט x |

|------------------------|-----------------------|----------------|-----------------------|-------------------------------------------------------|-------|-------|--------|

|                        |                       | ·              | 1                     |                                                       |       | 7     |        |

|                        | A A B -               | A < B, $A > B$ | 2                     |                                                       | 1     | 2     |        |

| <sup>t</sup> PLH       | Any A or B data input |                | 3                     | ]                                                     | 1     | 7 26  | ns     |

|                        |                       | A = B          | 4                     | ]                                                     | 2     | 3 35  |        |

|                        |                       |                | 1                     |                                                       | 1     | 1     |        |

|                        |                       | A < B, A > B   | 2                     | C 15 -5                                               | 1     | 5     |        |

| <sup>t</sup> PH L      | Any A or B data input |                | 3                     | $C_L = 15 \text{ pF},$ $R_L = 400 \Omega,$ See Note 5 | 2     | 0 30  | ns     |

|                        |                       | A = B          | 4                     |                                                       | 2     | 0 30  |        |

| <sup>t</sup> PLH       | A < B or A = B        | A > B          | 1                     | See Note 5                                            |       | 7 11  | ns     |

| <sup>t</sup> PHL       | A < B or A = B        | A > B          | 1                     | 1                                                     | 1     | 1 17  | ns     |

| <sup>t</sup> PLH       | A = 8                 | A = B          | 2                     |                                                       | 1     | 3 20  | ns     |

| <sup>t</sup> PHL       | A = B                 | A = B          | 2                     | 1                                                     | 1     | 1 17  | ns     |

| <sup>†</sup> PLH       | A > B or A = B        | A = B A < B 1  |                       |                                                       | 7 11  | ns    |        |

| tPHL.                  | A > B or A = B        | A < B          | 1                     | 1                                                     | 1     | 1 17  | пѕ     |

tpLH = propagation delay time, low-to-high-level output

NOTE 5: Load circuits and voltage waveforms are shown in Section 1.

$<sup>^{\</sup>ddagger}$ All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}$ C.

<sup>§</sup>Not more than one output should be shorted at a time.

tpHL = propagation delay time, high-to-low-level output