- Integrated FETs with Low R<sub>DS-ON</sub> . . .

6 Ω Max

- Current-Controlled Output Drives That Are Proportional to Battery Voltage to Save Power

- Integrated Power-Supply Switches for Power Savings During OFF State . . .

1 μA Max

- Up to 89% Efficiency

- Applications: LCD Display for Cell Phones, PDAs, Palmtops, etc.

NC - No internal connection

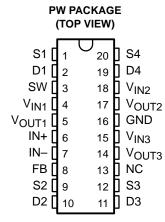

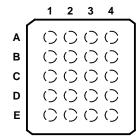

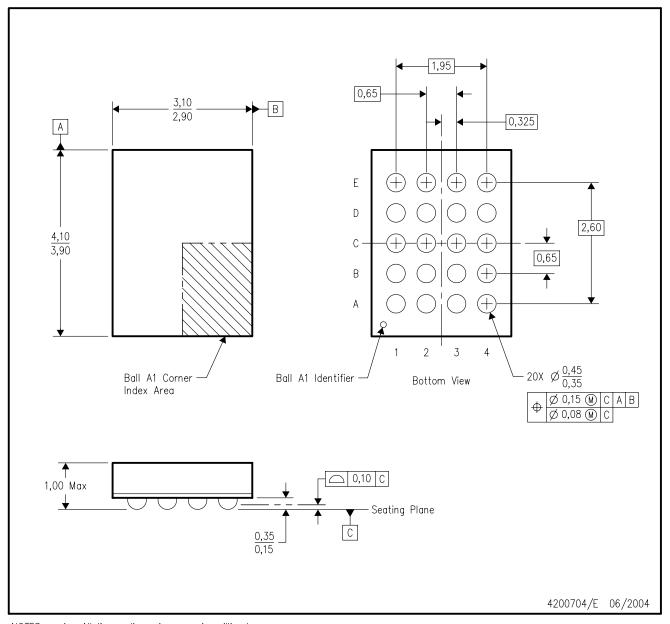

# GQN PACKAGE (TOP VIEW)

## terminal assignments

|   | 1                | 2                 | 3                | 4                 |

|---|------------------|-------------------|------------------|-------------------|

| Α | D1               | S1                | S4               | D4                |

| В | V <sub>IN1</sub> | V <sub>OUT2</sub> | SW               | V <sub>IN2</sub>  |

| С | IN+              | V <sub>OUT1</sub> | V <sub>IN3</sub> | GND               |

| D | FB               | NC                | IN-              | V <sub>OUT3</sub> |

| Ε | D2               | S2                | D3               | S3                |

NC - No internal connection

| TERMINAL            | DESCRIPTION                                                                                                          |

|---------------------|----------------------------------------------------------------------------------------------------------------------|

| D1, D2, D3, D4      | Drain of FETs 1, 2, 3, and 4, respectively                                                                           |

| S1, S2, S3, S4      | Source of FETs 1, 2, 3, and 4, respectively                                                                          |

| VIN1, VIN2, VIN3    | Input of switches 1, 2, and 3, respectively                                                                          |

| VOUT1, VOUT2, VOUT3 | Output of switches 1, 2, and 3, respectively                                                                         |

| SW                  | Operates switches 1, 2, and 3 in unison<br>Low input = switches are closed<br>High input or Open = switches are open |

| IN+                 | Noninverting input to current-control amplifier                                                                      |

| IN-                 | Inverting input to current-control amplifier                                                                         |

| FB                  | Provides feedback connection to IN- of current-control amplifier                                                     |

| GND                 | Device ground                                                                                                        |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SLDS147C - JUNE 2002 - REVISED NOVEMBER 2002

### description/ordering information

The TLED2043 is a four-channel, white LED driver used for backlighting color LCD displays in portable equipment. The device consists of four FET outputs, each of which is used essentially as a current sink to bias a single LED. The gates of the FETs are controlled collectively by a current-control amplifier that automatically monitors the battery voltage. If the battery voltage drops when compared to an externally set reference voltage, the current-control amplifier proportionately lowers all four FETs' output drives to conserve battery power. Additionally, the TLED2043 has internal switches that are programmed to disconnect the power supply and supporting circuitry to the device when LED operation is not needed, offering significant power savings during periods of inactivity.

Offering smaller board space, lower R<sub>DS-ON</sub>, and lower overall cost, the TLED2043 has clear advantages over the use of discrete devices in implementing a white-LED driver solution. Compared to the use of charge pumps and dc-dc converters in similar applications, the TLED2043 again can offer the advantages of smaller board space and lower solution cost because no costly inductors and/or capacitors are required. In addition, it avoids the switching-noise and power-loss issues associated with such devices.

Characterized for operation from –40°C to 85°C, the TLED2043 is offered in 20-pin TSSOP (PW) and MicroStar Jr. BGA (GQN) packages for maximum space savings.

#### ORDERING INFORMATION

| TA            | PACKAGE <sup>†</sup> |              | ORDERABLE<br>PART NUMBER | TOP-SIDE<br>MARKING |

|---------------|----------------------|--------------|--------------------------|---------------------|

|               | TSSOP (PW)           | Tube of 70   | TLED2043IPW              | 20431               |

| –40°C to 85°C | 13301 (1 W)          | Reel of 2000 | TLED2043IPWR             | 20431               |

|               | VFBGA (GQN)          | Reel of 1000 | TLED2043IGQNR            | 20431               |

<sup>†</sup> Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

#### **FUNCTION TABLE**

| TOTOTION TABLE |                          |  |  |  |  |  |

|----------------|--------------------------|--|--|--|--|--|

| SW<br>INPUT    | SWITCH 1, 2, 3<br>STATUS |  |  |  |  |  |

| Н              | All OFF                  |  |  |  |  |  |

| L              | All ON                   |  |  |  |  |  |

| Open           | All OFF                  |  |  |  |  |  |

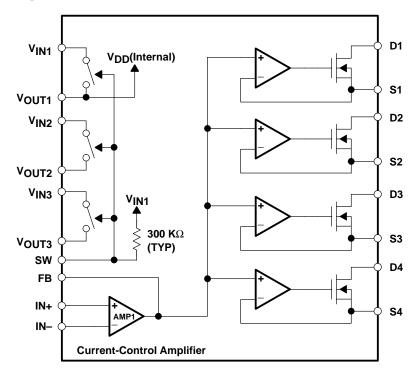

## functional block diagram

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Switch input voltage: V <sub>IN1</sub> , V <sub>IN2</sub> , V <sub>IN3</sub> (see Note 1) | 7 V             |

|-------------------------------------------------------------------------------------------|-----------------|

| Switch output current: I <sub>OUT1</sub> , I <sub>OUT2</sub> , I <sub>OUT3</sub>          |                 |

| Amplifier input voltage, V <sub>I</sub>                                                   | V <sub>DD</sub> |

| Output FET drain-source voltage, V <sub>DS</sub>                                          |                 |

| Output FET drain current, ID                                                              |                 |

| Package thermal impedance, θ <sub>JA</sub> (see Notes 2 and 3): GQN package               | 78°C/W          |

| PW package                                                                                | 83°C/W          |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds                              | 260°C           |

| Storage temperature range, T <sub>stg</sub>                                               |                 |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- NOTES: 1. All voltage values are with respect to the network ground terminal.

- 2. Maximum power dissipation is a function of  $T_J(max)$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any allowable ambient temperature is  $P_D = (T_J(max) T_A)/\theta_{JA}$ . Operating at the absolute maximum  $T_J$  of 150°C can affect reliability.

- 3. The package thermal impedance is calculated in accordance with JESD 51-7.

SLDS147C – JUNE 2002 – REVISED NOVEMBER 2002

## recommended operating conditions

|                   |                                 | MIN | MAX | UNIT |

|-------------------|---------------------------------|-----|-----|------|

| V <sub>IN1</sub>  |                                 | 2.7 | 5.5 |      |

| V <sub>IN2</sub>  | Switch input voltage            | 0   | 5.5 | V    |

| V <sub>IN3</sub>  |                                 | 0   | 5.5 |      |

| Vsw               | Input voltage for SW pin        | 0   | 5.5 | V    |

| I <sub>OUT1</sub> |                                 |     | 3   |      |

| I <sub>OUT2</sub> | Switch output current           |     | 3   | mA   |

| IOUT3             |                                 |     | 3   |      |

| $V_{DS}$          | FET output drain-source voltage |     | 5.5 | V    |

| $I_{D}$           | FET output drain current        |     | 50  | mA   |

| TA                | Operating free-air temperature  | -40 | 85  | °C   |

## electrical characteristics, $T_A = 25^{\circ}C$ (unless otherwise noted)

## supply voltage switch section

| PARAMETER |                                     | TEST CONDITIONS                                   | MIN                  | TYP | MAX                 | UNIT |

|-----------|-------------------------------------|---------------------------------------------------|----------------------|-----|---------------------|------|

| VOUT1     |                                     | V <sub>IN1</sub> = 3.6 V, I <sub>OUT</sub> = 3 mA | V <sub>IN</sub> -0.1 |     |                     |      |

| VOUT2     | Switch output voltage               | V <sub>IN1</sub> = 3.6 V, I <sub>OUT</sub> = 3 mA | V <sub>IN</sub> -0.1 |     |                     | V    |

| VOUT3     |                                     | V <sub>IN1</sub> = 3.6 V, I <sub>OUT</sub> = 3 mA | V <sub>IN</sub> -0.1 |     |                     |      |

| Vou       | High input voltage range for SW OFF | V <sub>IN1</sub> = 2.7 V to 5.5 V (see Note 4)    | $V_{DD} \times 0.7$  |     |                     | ٧    |

| Vsw       | Low input voltage range for SW ON   | V <sub>IN1</sub> = 2.7 V to 5.5 V (see Note 4)    |                      |     | $V_{DD} \times 0.3$ | V    |

| ΙL        | Low input current for SW            | V <sub>IN1</sub> = 3.6 V, V <sub>SW</sub> = 0 V   |                      | 20  | 100                 | μΑ   |

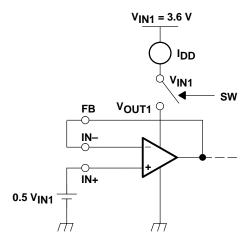

| lon       | Input current (see Figure 1)        | ON state (V <sub>SW</sub> = 0 V)                  |                      |     | 1                   | mA   |

| IDD       | input current (see rigule 1)        | OFF state (V <sub>SW</sub> = OPEN)                |                      |     | 1                   | μΑ   |

NOTE 4: V<sub>DD</sub> = V<sub>OUT1</sub>

## amplifier (AMP1) section, $V_{IN1} = 3.6 \text{ V}$

|                 | PARAMETER TEST CONDITIONS |                                                         | MIN                         | TYP                  | MAX | UNIT                 |      |

|-----------------|---------------------------|---------------------------------------------------------|-----------------------------|----------------------|-----|----------------------|------|

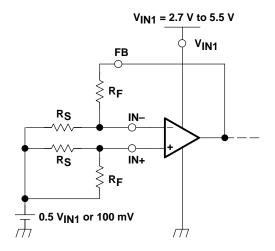

| Via lanut offee | Input offset voltage      | $V_{IC} = 0.5 \times V_{IN} \text{ or } 100 \text{ mV}$ | T <sub>A</sub> = 25°C       |                      | 0.3 | 4                    | mV   |

| VIO             | input onset voltage       |                                                         | T <sub>A</sub> = Full range |                      |     | 5                    | IIIV |

| IIO             | Input offset current      |                                                         |                             |                      | 8   |                      | pА   |

| I <sub>IB</sub> | Input bias current        |                                                         |                             |                      | 45  |                      | pA   |

| VICR            | Common-mode input voltage | V <sub>IN1</sub> = 2.7 V to 5.5 V (see Figure 3)        |                             | 0                    |     | V <sub>DD</sub> -1.5 | V    |

| AVD             | Open-loop voltage gain    |                                                         |                             | 70                   |     |                      | dB   |

| B <sub>1</sub>  | Unity-gain bandwidth      |                                                         |                             |                      | 630 |                      | kHz  |

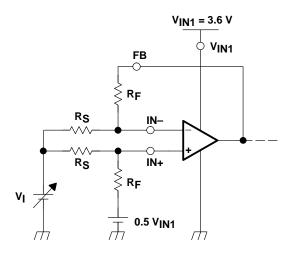

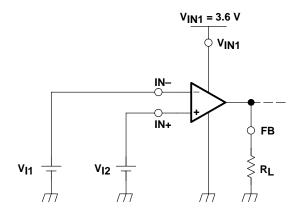

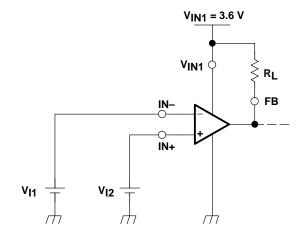

| Vон             | Output voltage (FB)       | R <sub>L</sub> ≥ 100 kΩ (see Figure 4)                  |                             | V <sub>DD</sub> -1.5 |     | ·                    | V    |

| VOL             | Output voltage (FB)       | $R_L \ge 100 \text{ k}\Omega$ (see Figure 5)            |                             |                      |     | 0.1                  | V    |

## constant-current circuit section, AMP + FET

|                      | PARAMETER                  | TEST CONDITIONS                                                                                                      | MIN | TYP | MAX | UNIT |

|----------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| I <sub>D</sub> (OFF) | Drain off-state current    | $V_{IN1}$ = 3.6 V, SW: OFF ( $V_{SW}$ = $V_{DD}$ or OPEN), $V_{DS}$ = 5.5 V                                          |     | 25  | 250 | nA   |

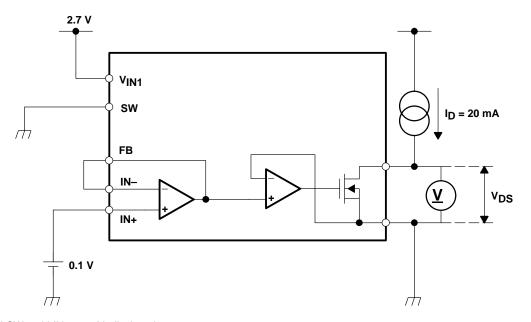

| r <sub>on</sub>      | Drain-source ON resistance | $V_{IN1} = 2.7 \text{ V, IN+} = 0.1 \text{ V, I}_D = 20 \text{ mA (see Figure 6)}$                                   |     |     | 6   | Ω    |

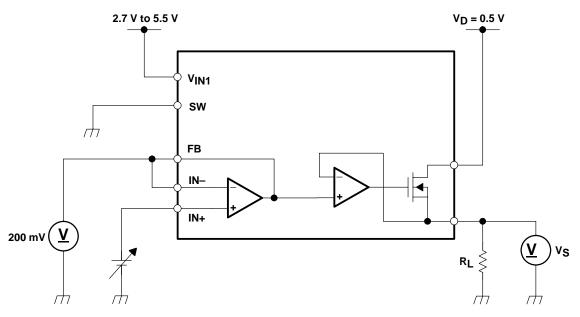

| ٧s                   | Source voltage             | $V_{\mbox{IN1}}$ = 2.7 V to 5.5 V, FB = 200 mV, $V_{\mbox{D}}$ = 0.5 V, R $_{\mbox{L}}$ = 10 $\Omega$ (see Figure 7) | 194 | 199 | 204 | mV   |

NOTE:  $V_{SW} = 0 V$  or open, all other pins open

Figure 1. I<sub>DD</sub> (ON State)

NOTE: SW = 0 V, all other pins open

Figure 2. V<sub>IO</sub>

NOTE: SW = 0 V, all other pins open

Figure 3. V<sub>ICR</sub>

NOTE: SW = 0 V, all other pins open

Figure 4. V<sub>OH</sub>

NOTE: SW = 0 V, all other pins open

Figure 5. V<sub>OL</sub>

NOTE:  $V_{IN1}$  = 2.7 V, SW = 0 V, IN+ = 0.1 V, all other pins open  $r_{on} = V_{DS}/I_{D}$

Figure 6. ron

NOTE:  $~V_{IN1}$  = 2.7 V to 5.5 V, FB = 200 mV,  $V_D$  = 0.5 V,  $R_L$  = 10  $\Omega$

Figure 7. V<sub>S</sub>

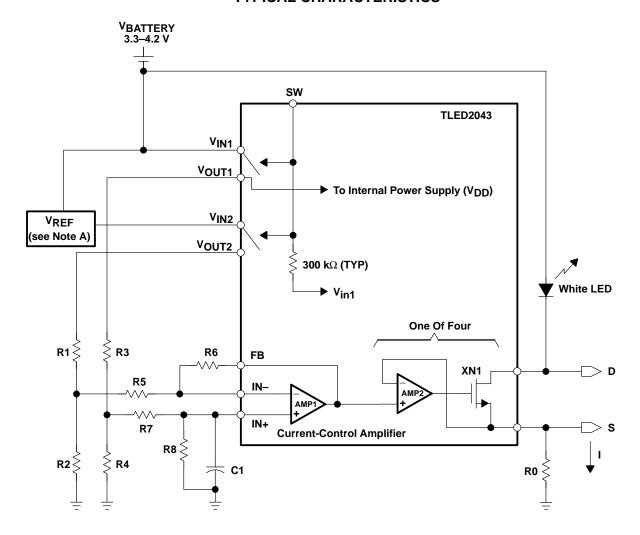

$R0=0.01~k\Omega$

$R1 = 20 \text{ k}\Omega$

$R2 = 1.6 \text{ k}\Omega$

$R3 = 20 \text{ k}\Omega$

$R4 = 2.2 \text{ k}\Omega$

$R5 = 6.8 \text{ k}\Omega$

$R6 = 20 \text{ k}\Omega$

$R7 = 100 \text{ k}\Omega$

$R8 = 100 \text{ k}\Omega$

$C1=1\;\mu F$

V<sub>REF</sub> = 2.8 V

NOTE A: V<sub>REF</sub> and resistor values should be chosen for proper control of LED current, which is adjusted by the current-control amplifier to be directly proportional to the difference between V<sub>BATTERY</sub> and V<sub>REF</sub>. A stable V<sub>REF</sub> can be achieved through a low-power voltage reference (such as the REF29xx), a shunt regulator (such as the TLV431A), or a low-power LDO (such as the TPS770xx or TPS769xx families).

**Figure 8. Typical Application Circuit**

#### **DEVICE OPERATION/APPLICATION HINTS**

Refer to the functional block diagram and typical application circuit (see Figure 8)

White LEDs commonly are used to produce the backlight for small color LCDs found in portable electronics, such as cell phones and PDAs. Because the LED's brightness and chromaticity are dependent on the LED's bias current, precise control of this current is necessary for proper illumination of the LCD. The TLED2043 is, essentially, four voltage-controlled current sinks that are regulated in unison, with each current sink setting the bias current for one white LED. The basic circuitry and operation of the TLED2043 can be divided into three main operating blocks described below.

### output FETs

The TLED2043 has four n-channel MOSFETs to drive four external LEDs. The FETs have a specified maximum  $r_{on}$  of 6  $\Omega$ , while delivering 20 mA of load current. To determine the biasing current for each LED, the gate of each FET is driven by a buffer whose output is controlled by the current-control amplifier.

#### current control amplifier

The output of the Current Control Amplifier simultaneously drives four unity-gain amplifiers connected to the gates of the output FETs. To determine the drain current of each FET (the LED current), the noninverting input (IN+) of this amplifier typically is coupled to the battery voltage via Switch 1, while the inverting input (IN-) typically is coupled to a fixed reference voltage that remains constant as battery voltage changes. Therefore, the output of the Current Control Amplifier and the corresponding LED currents are proportional to the difference between the battery and reference voltages. As battery voltage drops with use, so does the LED current, allowing for lower power consumption to conserve battery power.

#### switch 1, 2, 3

The TLED2042 has three switches that are opened/closed in unison via an active-low switch-enable (SW) pin; the switches are closed with a low input applied and opened with a high input. Each switch has a maximum loss of 0.1 V across it; thus, the output of each switch is specified to be  $(V_{IN} - 0.1 \text{ V}) < V_{OLIT} < V_{IN}$ .

During periods of inactivity when the LEDs are not needed, significant power savings can be achieved (from a maximum of 1 mA to 1  $\mu$ A) by opening the switches. The purpose of each switch is described below:

- Switch 1: used to remove power to the TLED2043 when the LEDs are not needed.

- Switch 2 (or 3): used to remove power to the series voltage reference (V<sub>REF</sub> in the typical application Circuit). Without this switch, V<sub>REF</sub> current flows continuously (through R1 and R2), even when power is removed from the TLED2043. (Note that, if a shunt reference like the TLV431 is used, current still flows through the reference, even if Switch 2 is open).

- Switch 3: Though not used in the typical application circuit here, this switch can be used to connect various external circuitries to the current-control amplifier. One example is to connect an external voltage to either input of the current-control amplifier to implement an analog LED brightness control (see next section).

#### efficiency

Laboratory measurements and calculations have shown that the application circuit in Figure 8 typically has the following efficiency:

- Battery Voltage = 3.6 V: η = 78.8% (I<sub>I FD</sub> = 12.2 mA)

- Battery Voltage = 3.3 V: η = 89% (I<sub>I FD</sub> = 7.8 mA)

- Battery Voltage = 3.1 V: η = 80.4% (I<sub>I FD</sub> = 4.5 mA)

NOTE: Efficiency, as mentioned previously, refers to the efficiency of the **overall solution** and is defined simply as:

$$\eta = P_{LED}/P_{BATTERY}$$

where PBATTERY is the total power delivered by the battery to the entire circuit.

Thus, the efficiency indicates how effectively the TLED2043 delivers power to the LEDs. As such, LED selection can have a significant impact on calculated efficiency. For instance, two different brands of LEDs may have different values of  $V_F$  for the same value of  $I_F$ . According to the equation above, the LED with the larger  $V_F$  will dissipate more power ( $P_{LED} = V_F \times I_F$ ) and thus will achieve higher efficiency. This result simply states how much power is dissipated in the LED, not how well that particular LED converts the electrical power into light—this, of course, solely depends on the LED construction and characteristics.

It should be pointed out that although a lower calculated efficiency is achieved using the LED with the lower  $V_F$  (for the same  $I_F$ ), the benefit of the lower  $V_F$  is that there is now more headroom for LED operation as battery voltage drops.

#### LED brightness control

The brightness of an LED is proportional to its bias current. Since the current control amplifier determines the LED current by sensing the difference between its two inputs, changing the voltage at either IN– or IN+ (or both) affects LED current and brightness. There are several methods to achieve this.

- 1. **Variable V<sub>REF</sub>:** use an adjustable shunt regulator (e.g., TL431/TLV431) and a variable resistor to change voltage applied to IN– of the current-control amplifier.

- V<sub>RFF</sub> ↑, brightness ↓

- 2. External Analog Voltage, VBRIGHT: applied to either IN- or IN+ of the current-control amplifier.

- IN–: V<sub>BRIGHT</sub> ↑, brightness ↓

- IN+: V<sub>BRIGHT</sub> ↑, brightness ↑

NOTE: If using this method,  $V_{BRIGHT}$  should be coupled resistively to the Current Control Amplifier via Switch 3, allowing it to be disconnected from the amplifier when the switches are opened. Doing so prevents wasted current flow from  $V_{BRIGHT}$  to ground when no power is applied to the TLED2043.

3. **Variable Resistors:** use a variable resistor anywhere along the signal path of IN– or IN+ (R1–R8); this allows for adjustment of the voltage at IN– or IN+ (or both).

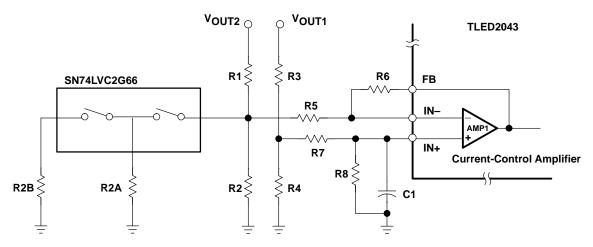

## example of a "digital" brightness control circuit

When using equipment such as cell phones, often it is desirable to adjust the brightness of the LCD display. While variable resistors offer an easy means of adjusting the LED brightness as described above, they are not economical if a digital potentiometer is required. Figure 9 shows a relatively simple and cost-effective means of achieving "digital" control of the LED brightness using standard resistors and signal switches.

Using a simple dual signal switch such as the SN74LVC2G66, resistors R2A and R2B can be individually paralleled to R2 to change the voltage divider being fed by  $V_{REF}$ . Doing so lowers the voltage applied to IN– of the current-control amplifier, resulting in increased LED current and brightness.

Figure 9. Example of a "Digital" Brightness Control

# GQN (R-PBGA-N20)

## PLASTIC BALL GRID ARRAY

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MO-225 variation BC.

- D. This package is tin-lead (SnPb). Refer to the 20 ZQN package (drawing 4204492) for lead-free.

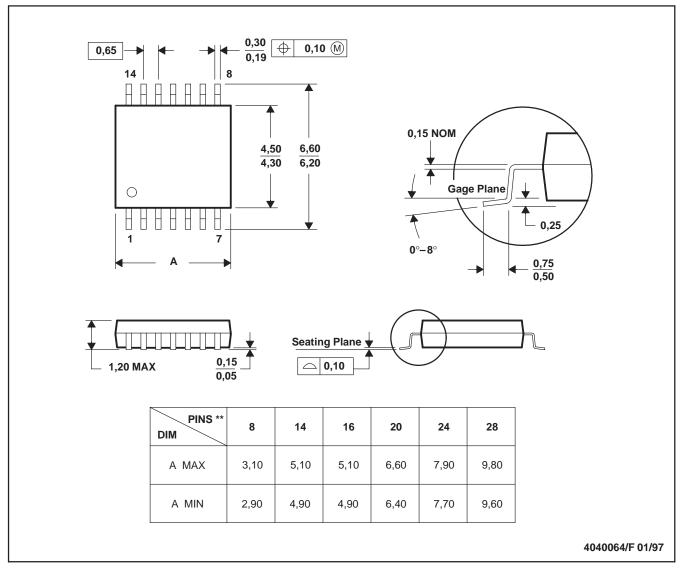

## PW (R-PDSO-G\*\*)

#### 14 PINS SHOWN

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-153

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| e               |

|-----------------|

| d               |

| trol            |

|                 |

| work            |

|                 |

|                 |

|                 |

|                 |

| d<br>trol<br>wo |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2004, Texas Instruments Incorporated