SLVS449A - DECEMBER 2002 - REVISED MAY 2003

# PC CARD™ POWER-INTERFACE SWITCH WITH RESET FOR SERIAL PCMCIA CONTROLLER

#### **FEATURES**

- Fully Integrated V<sub>CC</sub> and V<sub>PP</sub> Switching for Single-Slot or Dual-Slot PC Card™ Interface

- P<sup>2</sup>C<sup>™</sup> 3-Lead Serial Interface Compatible With CardBus<sup>™</sup> Controller

- Meets PC Card Standard

- RESET for System Initialization of PC Cards

- 12-V Supplies Can Be Disabled Except During

12-V Flash Programming

- Short-Circuit and Thermal Protection

- 24-Pin HTSSOP (PWP), 30-Pin SSOP (DB), and 32-Pin TSSOP (DAP) Packages

- Compatible With 3.3-V, 5-V, and 12-V PC Cards

- Low r<sub>DS(on)</sub> (95-mΩ, 5-V V<sub>CC</sub> Switch; 85-mΩ

3.3-V V<sub>CC</sub> Switch)

- Single-Slot Switch: TPS2210A

Dual-Slot Switch: TPS2204A and TPS2206A

- Break-Before-Make Switching

#### **APPLICATIONS**

- Notebook and Desktop Computers

- Set-Top Boxes

- Personal Digital Assistants(PDAs)

- Digital Cameras

- Bar Code Scanners

#### DESCRIPTION

The TPS2204A and TPS2206A PC CardBus<sup>TM</sup> power-interface switches provide an integrated power-management solution for two PC Card<sup>TM</sup> sockets. The TPS2210A is a single-slot option for this family of devices. These devices allow the controlled distribution of 3.3 V, 5 V, and 12 V to each card slot. The current-limiting and thermal-protection features eliminate the need for fuses. Current-limit reporting helps the user isolate a system fault. The switch  $r_{DS(on)}$  and current-limit values are set for the peak and average current requirements stated in the PC Card<sup>TM</sup> specification, and are optimized for cost.

The TPS2206A is pin and/or functionally compatible with the TPS2206, TPS2216, TPS2216A, TPS2226, TPS2226A, and TPS2228 with a few exceptions, as shown in the Available Options table.

#### **AVAILABLE OPTIONS OF THE TPS2206A PIN COMPATABLE SWITCHES**

| DADTAUMBED  | INDEPENDENT               |             |     | INPUT |           |     |                   |

|-------------|---------------------------|-------------|-----|-------|-----------|-----|-------------------|

| PART NUMBER | V <sub>PP</sub> SWITCHING | RESET RESET |     | SHDN  | SHDN MODE |     | VOLTAGES          |

| TPS2206     | No                        | Yes         | Yes | No    | No        | No  | 3.3 V, 5 V, 12 V  |

| TPS2206A    | No                        | Yes         | No  | Yes   | No        | No  | 3.3 V, 5 V, 12 V  |

| TPS2216     | Yes/No(1)                 | Yes         | Yes | No    | Yes       | Yes | 3.3 V, 5 V, 12 V  |

| TPS2216A    | Yes/No(1)                 | Yes         | Yes | No    | Yes       | Yes | 3.3 V, 5 V, 12 V  |

| TPS2226     | Yes                       | Yes         | No  | Yes   | No        | No  | 3.3 V, 5 V, 12 V  |

| TPS2226A    | Yes                       | Yes         | No  | Yes   | No        | No  | 3.3 V, 5 V, 12 V  |

| TPS2228     | Yes                       | Yes         | No  | Yes   | No        | No  | 1.8 V, 3.3 V, 5 V |

<sup>(1)</sup> Selected by MODE pin.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

P<sup>2</sup>C is a trademark of Texas Instruments.

PC Card and CardBus are trademarks of PCMCIA (Personal Computer Memory Card International Association).

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### ORDERING INFORMATION

|               | PACKAGED DEVICES           |                                             |                                             |  |  |  |  |

|---------------|----------------------------|---------------------------------------------|---------------------------------------------|--|--|--|--|

| TA            | PLASTIC SMALL OUTLINE (DB) | POWERPAD™ PLASTIC SMALL<br>OUTLINE (DAP-32) | POWERPAD™ PLASTIC SMALL<br>OUTLINE (PWP-24) |  |  |  |  |

| -40°C to 85°C | TPS2206ADB                 | TPS2206ADAP                                 | TPS2204APWP<br>TPS2210APWP                  |  |  |  |  |

<sup>(1)</sup> The DB, PWP, and DAP packages are available taped and reeled. Add R suffix to device type (e.g., TPS2206ADBR) for taped and reeled.

#### PACKAGE DISSIPATION RATINGS

| PACKAGE(1) | $T_{\mbox{$\mbox{$A$}}} \leq 25^{\circ}\mbox{$\mbox{$C$}}$ POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|------------|-------------------------------------------------------------------------|------------------------------------------------|---------------------------------------|---------------------------------------|

| DB (30)    | 821.46 mW                                                               | 10.95 mW/°C                                    | 328.58 mW                             | 164.29 mW                             |

| DAP (32)   | 3191.4 mW                                                               | 42.55 mW/°C                                    | 1276.5 mW                             | 638.29 mW                             |

| PWP (24)   | 2491.6 mW                                                               | 33.22 mW/°C                                    | 996.67 mW                             | 498.33 mW                             |

<sup>(1)</sup> These devices are mounted on an JEDEC low-k board (2-oz. traces on surface).

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted(1)

|                                      |                              |                          | UNITS |  |  |

|--------------------------------------|------------------------------|--------------------------|-------|--|--|

|                                      | V <sub>I(3.3V)</sub>         | -0.3 V to 5.5            | V     |  |  |

| Input voltage range for card power   | V <sub>I(5V)</sub>           | -0.3 V to 5.5            | V     |  |  |

|                                      | V <sub>I</sub> (12V)         | −0.3 V to 14             | V     |  |  |

| Logic input/output voltage           |                              | -0.3 V to 6              | V     |  |  |

|                                      | VO(xVCC)                     | −0.3 V to 6              | V     |  |  |

| VO(xVP                               | VO(xVPP)                     | −0.3 V to 14             | V     |  |  |

| Continuous total power dissipation   |                              | See Dissipation Rating T | able  |  |  |

|                                      | I <sub>O(xVCC)</sub>         | InternallyLimited        |       |  |  |

| Output current                       | lO(xVPP)                     | InternallyLimited        |       |  |  |

| Operating virtual junction temperatu | re range, T <sub>J</sub>     | -40°C to 100             | °C    |  |  |

| Storage temperature range, TSTG      |                              | −55°C to 150             | °C    |  |  |

| Lead temperature 1,6 mm (1/16 inc    | h) from case for 10 seconds) | 260                      | °C    |  |  |

| OC sink current                      |                              | 10                       | mA    |  |  |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

|                                                                                                                                     |                                                | MIN | MAX  | UNIT |

|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----|------|------|

|                                                                                                                                     | V <sub>I</sub> (3.3V)(1)                       | 3   | 3.6  |      |

| Input voltage, $V_{I(3,3V)}$ is required for all circuit operations. 5 V and 12 V are only required for their respective functions. | V <sub>I</sub> (5V)                            | 3   | 5.5  | V    |

| 12 v are only required for their respective functions.                                                                              | V <sub>I</sub> (12V)                           | 7   | 13.5 |      |

| Outroot comment I                                                                                                                   | I <sub>O(xVCC)</sub> at T <sub>J</sub> = 100°C |     | 1    | Α    |

|                                                                                                                                     | $I_{O(xVPP)}$ at $T_J = 100^{\circ}C$          |     | 100  | mA   |

| Clock frequency, f(clock)                                                                                                           |                                                |     | 2.5  | MHz  |

|                                                                                                                                     | Data                                           | 200 |      |      |

|                                                                                                                                     | Latch                                          | 250 |      |      |

| Pulse duration, t <sub>W</sub>                                                                                                      | Clock                                          | 100 |      | ns   |

|                                                                                                                                     | Reset                                          | 100 |      |      |

| Data-to-clock hold time, th (see Figure 2)                                                                                          |                                                | 100 |      | ns   |

| Data-to-clock setup time, t <sub>SU</sub> (see Figure 2)                                                                            |                                                | 100 |      | ns   |

| Latch delay time, t <sub>d(latch)</sub> (see Figure 2)                                                                              |                                                | 100 |      | ns   |

| Clock delay time, t <sub>d(clock)</sub> (see Figure 2)                                                                              |                                                | 250 |      | ns   |

| Operating virtual junction temperature, T <sub>J</sub> (maximum to be calculate                                                     | ed at worst case PD at 85°C ambient)           | -40 | 100  | °C   |

<sup>(1)</sup> It is understood that for  $V_{I(3.3V)}$ < 3 V, voltages within the absolute maximum ratings applied to pin 5 V or pin 12 V will not damage the IC.

#### **ELECTRICAL CHARACTERISTICS**

$T_J = 25$ °C,  $V_{I(5V)} = 5$  V,  $V_{I(3.3V)} = 3.3$  V,  $V_{I(12V)} = 12$  V, all outputs unloaded (unless otherwise noted)

| POWER   | SWITCH                                                |                        |                                                             |                       |     |     |     |      |

|---------|-------------------------------------------------------|------------------------|-------------------------------------------------------------|-----------------------|-----|-----|-----|------|

|         | PARAME                                                | TER                    | TEST CONDITIONS                                             | ;(1)                  | MIN | TYP | MAX | UNIT |

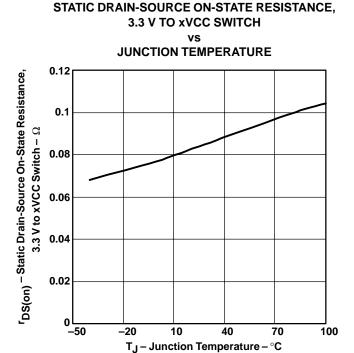

|         |                                                       | 3.3V to xVCC (2)       | I <sub>O</sub> = 750 mA each                                |                       |     | 85  | 110 |      |

|         |                                                       | 3.3V to XVCC (2)       | $I_O = 750 \text{ mA each}, T_J = 100^{\circ} \text{C}$     |                       |     | 110 | 140 | 0    |

|         |                                                       | 5V to xVCC(2)          | I <sub>O</sub> = 500 mA each                                |                       |     | 95  | 130 | mΩ   |

|         | Static drain-                                         |                        | $I_O = 500 \text{ mA each}, T_J = 100^{\circ} \text{C}$     |                       |     | 120 | 160 |      |

| rDS(on) | source on-state resistance                            | 3.3V or 5V to xVPP(2)  | I <sub>O</sub> = 50 mA each                                 |                       |     | 0.8 | 1   |      |

|         |                                                       |                        | $I_O = 50 \text{ mA each},  T_J = 100^{\circ}\text{C}$      |                       |     | 1   | 1.3 | 0    |

|         |                                                       | 12V to xVPP (2)        | I <sub>O</sub> = 50 mA each                                 |                       | 2   | 2.5 | Ω   |      |

|         |                                                       | 12V to XVPP (2)        | $I_O = 50 \text{ mA each},  T_J = 100^{\circ}\text{C}$      |                       |     | 2.5 | 3.4 |      |

|         | Output discharge                                      | Discharge at xVCC      | I <sub>O(disc)</sub> = 1 mA                                 |                       | 0.5 | 0.7 | 1   | kΩ   |

|         | resistance                                            | Discharge at xVPP      | I <sub>O(disc)</sub> = 1 mA                                 |                       | 0.2 | 0.4 | 0.5 | K22  |

|         |                                                       |                        | Limit (steady-state value),<br>output powered into a short  | IOS(xVCC)             | 1   | 1.4 | 2   | Α    |

|         | Chart sinsuit suturet                                 |                        | circuit                                                     | I <sub>OS(xVPP)</sub> | 120 | 200 | 300 | mA   |

| los     | Short-circuit output o                                | current                | Limit (steady-state value),                                 | IOS(xVCC)             | 1   | 1.4 | 2   | Α    |

|         |                                                       |                        | output powered into a short circuit, T <sub>J</sub> = 100°C | I <sub>OS(xVPP)</sub> | 120 | 200 | 300 | mA   |

|         | Thermalshutdown                                       | Thermal trip point, TJ | Risingtemperature                                           |                       |     | 135 |     |      |

|         | temperature <sup>(2)</sup> Hysteresis, T <sub>J</sub> |                        |                                                             |                       |     | 10  |     | °C   |

|         |                                                       | (2)(4)                 | 5V to xVCC = 5 V, with 100-m $\Omega$                       | short to GND          |     | 10  |     |      |

|         | Current-limit respons                                 | se time (3)(4)         | 5V to xVPP = 5 V, with 100-m $\Omega$                       | short to GND          |     | 3   |     | μs   |

<sup>(1)</sup> Pulse-testing techniques maintain junction temperature close to ambient temperature; thermal effects must be taken into account separately. (2) TPS2204A and TPS2206A: two switches on. TPS2210A: one switch on.

<sup>(3)</sup> Specified by design; not tested in production.

(4) From application of short to 110% of final current limit.

#### **ELECTRICAL CHARACTERISTICS Continued**

$T_J = 25$ °C,  $V_{I(5V)} = 5$  V,  $V_{I(3.3V)} = 3.3$  V,  $V_{I(12V)} = 12$  V, all outputs unloaded (unless otherwise noted)

|                  | PARAME           | TER                 |                                                         | TEST CONDITION                 | s                      | MIN | TYP | MAX | UNIT |

|------------------|------------------|---------------------|---------------------------------------------------------|--------------------------------|------------------------|-----|-----|-----|------|

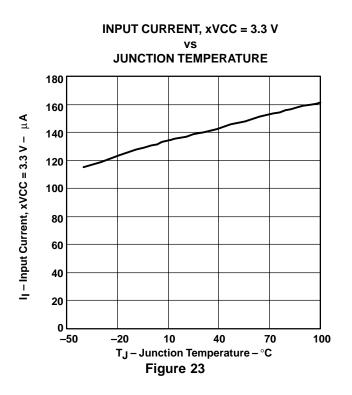

|                  |                  |                     | I <sub>I</sub> (3.3V)                                   |                                |                        | 140 |     | 200 |      |

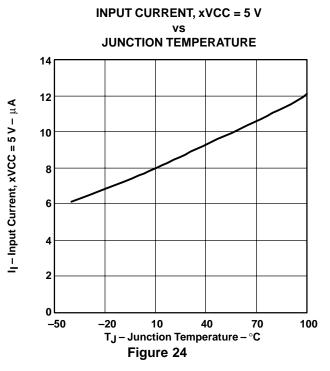

| Input current,   | Normal operation | I <sub>I(5V)</sub>  | $V_O(xVCC) = V_O(xVPP) = 3.3 V$<br>also for RESET = 0 V | and                            |                        | 8   | 12  |     |      |

|                  | operation        | I <sub>I(12V)</sub> | also for REGET = 0 V                                    |                                |                        | 100 | 180 |     |      |

| l II             | quiescent        | Shutdown<br>mode    | I <sub>I(3.3V)</sub>                                    |                                |                        |     | 0.3 | 2   | μΑ   |

|                  |                  |                     | I <sub>I(5V)</sub>                                      | $V_O(xVCC) = V_O(xVPP) = Hi-Z$ |                        | 0.1 | 2   |     |      |

|                  |                  | I <sub>I(12V)</sub> |                                                         |                                |                        |     | 0.3 | 2   |      |

|                  |                  |                     |                                                         | $V_{O(xVCC)} = 5 V$            |                        |     |     | 10  |      |

|                  | Leakage current, | Shutdown mode       | _                                                       | $V_{I(5V)} = V_{I(12V)} = 0 V$ | T <sub>J</sub> = 100°C |     |     | 50  | 4    |

| l <sub>lkg</sub> | output off state |                     | е                                                       | $V_{O(xVPP)} = 12 V$           |                        |     |     | 10  | μΑ   |

|                  |                  |                     |                                                         | $V_{I(5V)} = V_{I(12V)} = 0 V$ | T <sub>J</sub> = 100°C | •   |     | 50  |      |

| LOGIC S             | ECTION (CLOCK, DATA, LA         | TCH, RESET, SHDN, OC)                 |                              |     |      |     |      |

|---------------------|---------------------------------|---------------------------------------|------------------------------|-----|------|-----|------|

|                     | PARAMET                         | TER                                   | TEST CONDITIONS              | MIN | TYP  | MAX | UNIT |

|                     |                                 |                                       | RESET = 5.5 V                | -1  |      | 1   |      |

| 1                   |                                 | I <sub>I</sub> (RESET) <sup>(1)</sup> | RESET = 0 V                  | -30 | -20  | -10 |      |

|                     |                                 | I <sub>I</sub> (SHDN) <sup>(1)</sup>  | SHDN = 5.5 V                 | -1  |      | 1   |      |

| Ц                   | Input current, logic            |                                       | SHDN = 0 V                   | -50 |      | -3  | μА   |

|                     |                                 | I <sub>I(LATCH)</sub> (1)             | LATCH = 5.5 V                |     |      | 50  |      |

|                     |                                 |                                       | LATCH = 0 V                  | -1  |      | 1   |      |

|                     |                                 | I(CLOCK, DATA)                        | 0 V to 5.5 V                 | -1  |      | 1   |      |

| VIH                 | High-level input voltage, logic |                                       |                              | 2   |      |     | V    |

| V <sub>IL</sub>     | Low-level input voltage, logic  |                                       |                              |     |      | 0.8 | V    |

| V <sub>O(sat)</sub> | Output saturation voltage at OC |                                       | $I_O = 2 \text{ mA}$         |     | 0.14 | 0.4 | V    |

| llkg                | Leakage current at OC           |                                       | $V_{O(/OC)} = 5.5 \text{ V}$ |     | 0    | 1   | μΑ   |

<sup>(1)</sup> LATCH has low current pulldown. RESET and SHDN have low-current pullup.

| UVLO AND POR (POWER-ON RESET) |                                          |                                                                                                                                     |     |     |     |      |  |  |

|-------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|--|--|

|                               | PARAMETER                                | TEST CONDITIONS                                                                                                                     | MIN | TYP | MAX | UNIT |  |  |

| V <sub>I(3.3V)</sub>          | Input voltage at 3.3V pin, UVLO          | 3.3-V level below which all switches are Hi-Z                                                                                       | 2.4 | 2.7 | 2.9 | V    |  |  |

| V <sub>hys</sub> (3.3V)       | UVLO hysteresis voltage at VA (1)        |                                                                                                                                     |     | 100 |     | mV   |  |  |

| V <sub>I(5V)</sub>            | Input voltage at 5V pin, UVLO            | 5-V level below which only 5V switches are Hi-Z                                                                                     | 2.3 | 2.5 | 2.9 | V    |  |  |

| V <sub>hys(5V)</sub>          | UVLO hysteresis voltage at 5 V(1)        |                                                                                                                                     |     | 100 |     | mV   |  |  |

| <sup>t</sup> df               | Delay time for falling response, UVLO(1) | Delay from voltage hit (step from 3 V to 2.3 V) to Hi-Z control (90% V <sub>G</sub> to GND)                                         |     | 4   |     | μs   |  |  |

| VI(POR)                       | Input voltage, power-on reset(1)         | 3.3-V voltage below which POR is asserted causing a RESET internally with all line switches open and all discharge switches closed. |     |     | 1.7 | V    |  |  |

<sup>(1)</sup> Specified by design; not tested in production.

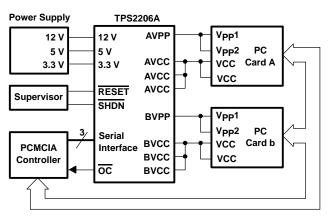

### **SWITCHING CHARACTERISTICS**

$V_{CC} = 5 \text{ V}, T_A = 25^{\circ}\text{C}, V_{I(3.3\text{V})} = 3.3 \text{ V}, V_{I(5\text{V})} = 5 \text{ V}, V_{I(12)} = 12 \text{ V}$  (not applicable for TPS2223A) all outputs unloaded (unless otherwise noted)

|                 | PARAMETER(1)                                                | LOAD CONDITION                                                                                                          | TEST CONDITIONS                                       | 3(2)               | MIN TYP | MAX | UNIT |

|-----------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------|---------|-----|------|

|                 |                                                             | C <sub>L(xVCC)</sub> = 0.1 μF, C <sub>L(xVPP)</sub> = 0.1 μF,                                                           | $V_{O(xVCC)} = 5 V$                                   |                    | 0.9     |     |      |

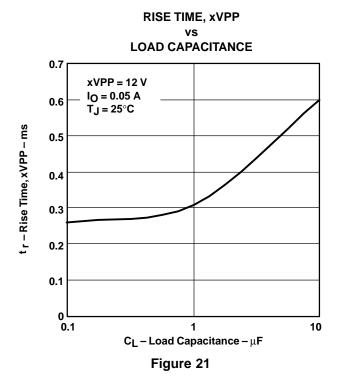

|                 | Output rise times(3)                                        | $I_{O(xVCC)} = 0 \text{ A},  I_{O(xVPP)} = 0 \text{ A}$                                                                 | V <sub>O(xVPP)</sub> = 12 V                           |                    | 0.26    |     | mo   |

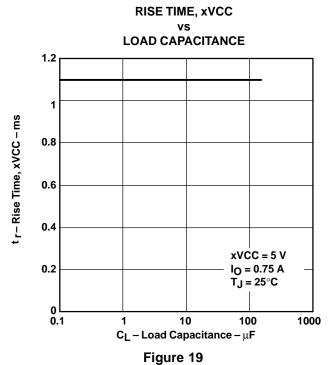

| t <sub>r</sub>  | Output rise times(3)                                        | $C_{L(XVCC)} = 150 \mu\text{F}, \ C_{L(XVPP)} = 10 \mu\text{F},$                                                        | $V_{O(xVCC)} = 5 V$                                   |                    | 1.1     |     | ms   |

|                 |                                                             | $I_{O(xVCC)} = 0.75 \text{ A}, I_{O(xVPP)} = 50 \text{ mA}$                                                             | V <sub>O(xVPP)</sub> = 12 V                           |                    | 0.6     |     |      |

|                 |                                                             | C <sub>L(xVCC)</sub> = 0.1 μF, C <sub>L(xVPP)</sub> = 0.1 μF,                                                           | V <sub>O(xVCC)</sub> = 5 V,<br>Discharge switches ON  |                    | 0.5     |     |      |

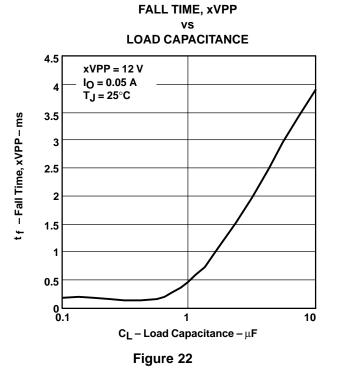

| t <sub>f</sub>  | Output fall times(3)                                        | $I_{O(xVCC)} = 0 A$ , $I_{O(xVPP)} = 0 A$                                                                               | V <sub>O(xVPP)</sub> = 12 V,<br>Discharge switches ON |                    | 0.2     |     | ms   |

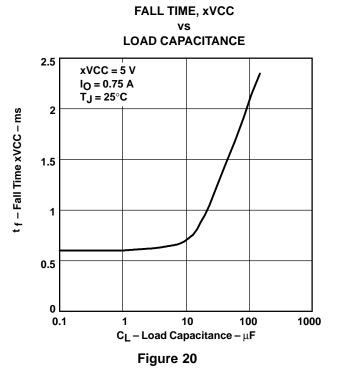

|                 |                                                             | $C_{L(xVCC)} = 150 \mu\text{F}, \ C_{L(xVPP)} = 10 \mu\text{F},$                                                        | V <sub>O(xVCC)</sub> = 5 V                            |                    | 2.35    |     |      |

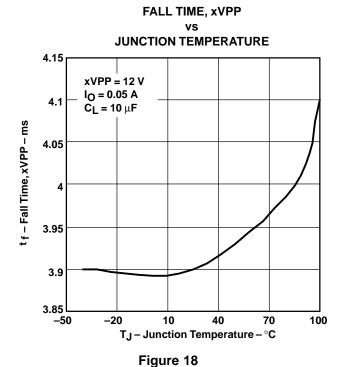

|                 | $I_{O(xVCC)} = 0.75 \text{ A}, I_{O(xVPP)} = 50 \text{ mA}$ | V <sub>O(xVPP)</sub> = 12 V                                                                                             |                                                       | 3.9                |         |     |      |

|                 |                                                             |                                                                                                                         | Latch↑ to xVPP (12 V)                                 | t <sub>pdon</sub>  | 2       |     |      |

|                 |                                                             |                                                                                                                         | Lateri to XVPP (12 V)                                 | tpdoff             | 0.62    |     | ms   |

|                 |                                                             | $C_{L(xVCC)} = 0.1 \mu\text{F}, \ C_{L(xVPP)} = 0.1 \mu\text{F},$ $I_{O(xVCC)} = 0 \text{A},  I_{O(xVPP)} = 0 \text{A}$ | Lotoh to W/DD (F.)()                                  | tpdon              | 0.77    |     |      |

|                 |                                                             |                                                                                                                         | Latch↑ to xVPP (5 V)                                  | tpdoff             | 0.51    |     |      |

|                 |                                                             |                                                                                                                         | Latch↑ to xVPP (3.3 V)                                | tpdon              | 0.75    |     |      |

|                 |                                                             |                                                                                                                         | Lateri to XVIII (0.5 V)                               | <sup>t</sup> pdoff | 0.52    |     |      |

|                 |                                                             |                                                                                                                         | Latch <sup>↑</sup> to xVCC (5 V)                      | tpdon              | 0.3     |     |      |

|                 |                                                             |                                                                                                                         |                                                       | <sup>t</sup> pdoff | 2.5     |     |      |

|                 |                                                             |                                                                                                                         | Latch↑ to xVCC (3.3V)                                 | <sup>t</sup> pdon  | 0.3     |     |      |

|                 | Propagationdelay                                            |                                                                                                                         | Lateri to xvec (5.5v)                                 | <sup>t</sup> pdoff | 2.8     |     |      |

| <sup>t</sup> pd | times(3)                                                    |                                                                                                                         | Latch↑ to xVPP (12 V)                                 | tpdon              | 2.2     |     |      |

|                 |                                                             |                                                                                                                         | Lateri to XVIII (12 V)                                | tpdoff             | 0.8     |     |      |

|                 |                                                             |                                                                                                                         | Latch↑ to xVPP (5 V)                                  | tpdon              | 0.8     |     |      |

|                 |                                                             |                                                                                                                         | Lateri to XVII (5 V)                                  | <sup>t</sup> pdoff | 0.6     |     |      |

|                 |                                                             | $C_{L(XVCC)} = 150 \mu\text{F}, \ C_{L(XVPP)} = 10 \mu\text{F},$                                                        | Latch↑ to xVPP (3.3 V)                                | tpdon              | 0.8     |     | ms   |

|                 |                                                             | $I_{O(xVCC)} = 0.75 \text{ A}, I_{O(xVPP)} = 50 \text{ mA}$                                                             | Lateria to AVI I (0.5 V)                              | <sup>t</sup> pdoff | 0.6     |     |      |

|                 |                                                             |                                                                                                                         | Latch↑ to xVCC (5 V)                                  | tpdon              | 0.6     |     |      |

|                 |                                                             |                                                                                                                         | Ediciti to XVOO (5 V)                                 | tpdoff             | 2.5     |     |      |

|                 |                                                             |                                                                                                                         | Latch↑ to xVCC (3.3V)                                 | tpdon              | 0.5     |     |      |

|                 |                                                             |                                                                                                                         | Laton 10 x V C C (3.3 V)                              | tpdoff             | 2.6     |     |      |

Refer to Parameter Measurement Information in Figure 1.

No card inserted, assumes a 0.1-μF output capacitor (see Figure 1).

<sup>(3)</sup> Specified by design; not tested in production.

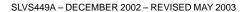

#### PIN ASSIGNMENTS

#### **TERMINAL FUNCTIONS**

|               |                  | TERMINAL         |                        |                             |     |                                                                                                                              |

|---------------|------------------|------------------|------------------------|-----------------------------|-----|------------------------------------------------------------------------------------------------------------------------------|

|               |                  | NUM              | BER                    |                             |     | DECORIDATION                                                                                                                 |

| NAME          | TPS2204A         | TPS2             | 206A                   | TPS2210A                    | 1/0 | DESCRIPTION                                                                                                                  |

|               | PWP              | DB               | DAP                    | PWP                         |     |                                                                                                                              |

| 3.3V          | 13, 14           | 15, 16, 17       | 16, 17, 18             | 13                          | I   | 3.3-V input for card power and chip power                                                                                    |

| 5V            | 1, 2, 24         | 1, 2, 30         | 1, 2, 32               | 1, 2                        | I   | 5-V V <sub>CC</sub> input for card power                                                                                     |

| 12V           | 7, 20            | 7, 24            | 8, 25                  | 7, 20                       | I   | 12-V Vpp input for card power (xVPP). The two 12-V pins must be externally connected.                                        |

| AVCC          | 9, 10            | 9, 10, 11        | 10, 11, 12             | 9, 10                       | 0   | Switchedoutput that delivers 0 V, 3.3 V, 5 V, or high impedance to card.                                                     |

| AVPP          | 8                | 8                | 9                      | 8                           | 0   | Switched output that delivers 0 V, 3.3 V, 5 V, 12 V, or high impedance to card.                                              |

| BVCC          | 17, 18           | 20, 21, 22       | 21, 22, 23             |                             | 0   | Switched output that delivers 0 V, 3.3 V, 5 V, or high impedance.                                                            |

| BVPP          | 19               | 23               | 24                     | _                           | 0   | Switched output that delivers 0 V, 3.3 V, 5 V, 12 V, or high impedance.                                                      |

| CLOCK         | 4                | 4                | 5                      | 4                           | - 1 | Logic-level clock for serial data word                                                                                       |

| DATA          | 3                | 3                | 4                      | 3                           | I   | Logic-level serial data word                                                                                                 |

| GND           | 11               | 12               | 13                     | 11                          |     | Ground                                                                                                                       |

| LATCH         | 5                | 5                | 6                      | 5                           | I   | Logic-level latch for serial data word, internal pulldown                                                                    |

| NC            | 6, 16, 22,<br>23 | 13, 19,<br>26–29 | 3, 7, 15,<br>19, 27–31 | 6, 14,<br>16 – 19,<br>22–24 |     | No internal connection                                                                                                       |

| <del>oc</del> | 15               | 18               | 20                     | 15                          | 0   | Open-drain overcurrent reporting output that goes low when an overcurrent condition exists.  An external pullup is required. |

| SHDN          | 21               | 25               | 26                     | 21                          | ı   | Hi-Z (open) all switches. Identical function to serial D8. Asynchronous active-low command, internal pullup                  |

| RESET         | 12               | 14               | 14                     | 12                          | I   | Logic-level RESET input active low. Do not connect if terminal 6 is used.                                                    |

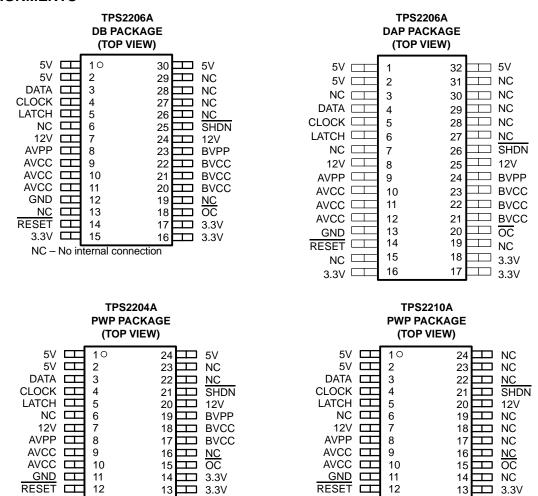

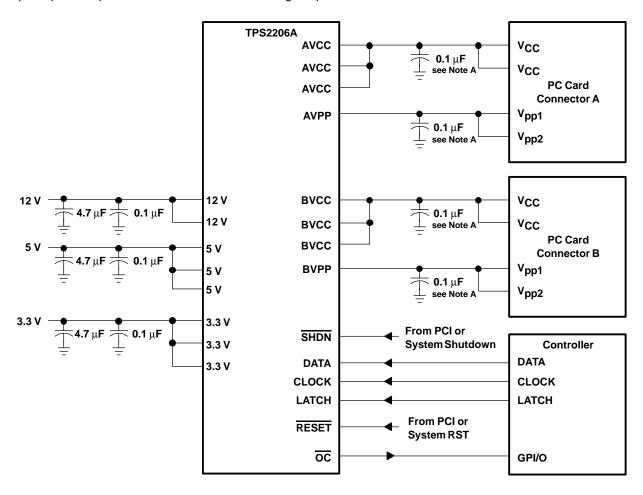

#### TYPICAL PC CARD POWER-DISTRIBUTION APPLICATION

#### PARAMETER MEASUREMENT INFORMATION

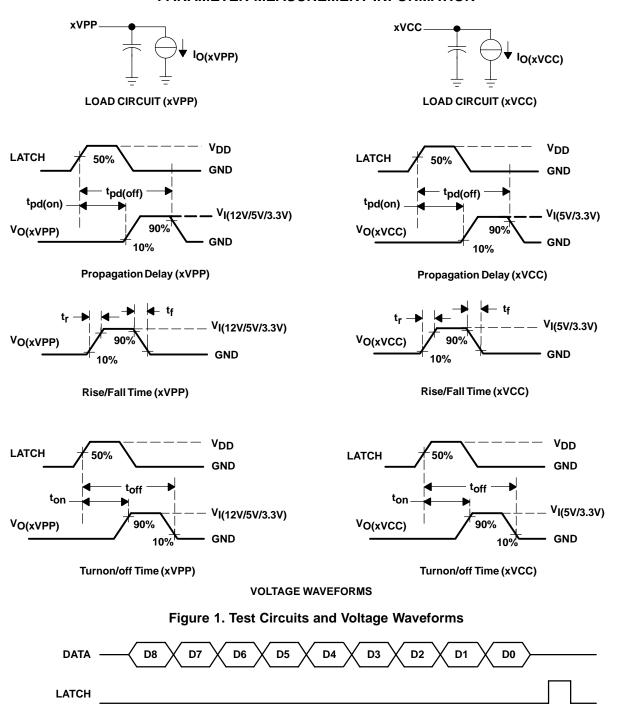

NOTE: Data is clocked in on the positive edge of the clock. The latch should occur before the next positive leading edge of the clock. For definition of D0to D8, see the control logic table.

Figure 2. Serial-Interface Timing for TPS2206A

CLOCK

#### **TABLE OF GRAPHS**

|                                                                             |                         | FIGURE |

|-----------------------------------------------------------------------------|-------------------------|--------|

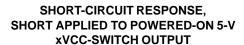

| Short-circuit response, short applied to powered-on 5-V xVCC-switch output  | vs Time                 | 3      |

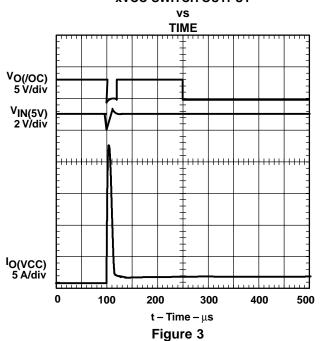

| Short-circuit response, short applied to powered-on 12-V xVPP-switch output | vs Time                 | 4      |

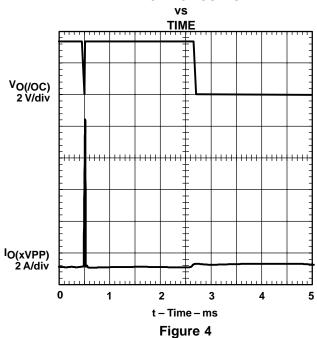

| OC response with ramped overcurrent-limit load on 5-V xVCC-switch output    | vs Time                 | 5      |

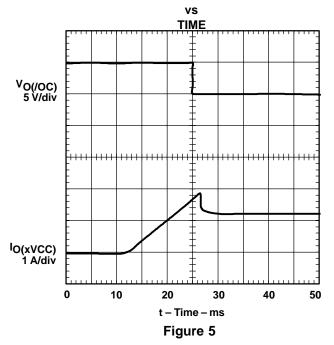

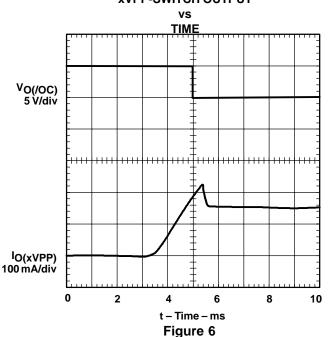

| OC response with ramped overcurrent-limit load on 12-V xVPP-switch output   | vs Time                 | 6      |

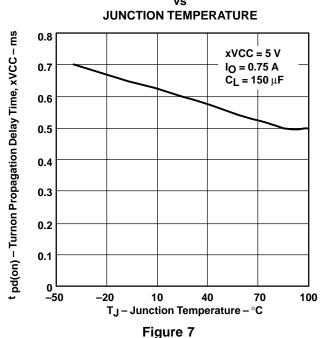

| Turnon propagation delay time, xVCC ( $C_L = 150 \mu F$ )                   | vs Junction temperature | 7      |

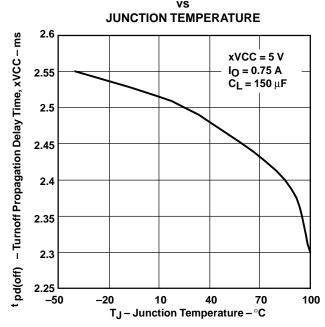

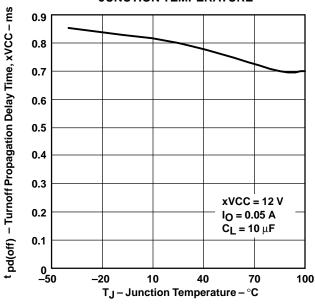

| Turnoff propagation delay time, xVCC ( $C_L = 150 \mu F$ )                  | vs Junction temperature | 8      |

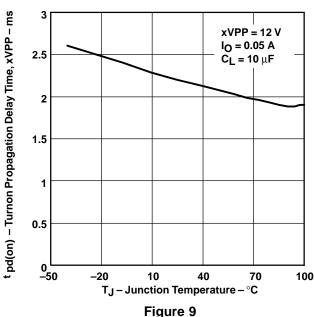

| Turnon propagation delay time, xVPP ( $C_L = 10 \mu F$ )                    | vs Junction temperature | 9      |

| Turnoff propagation delay time, xVPP ( $C_L = 10 \mu F$ )                   | vs Junction temperature | 10     |

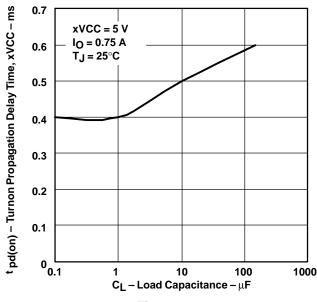

| Turnon propagation delay time, xVCC (T <sub>J</sub> = 25°C)                 | vs Load capacitance     | 11     |

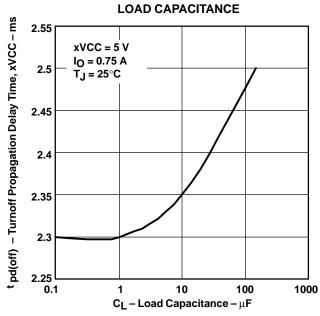

| Turnoff propagation delay time, xVCC (T <sub>J</sub> = 25°C)                | vs Load capacitance     | 12     |

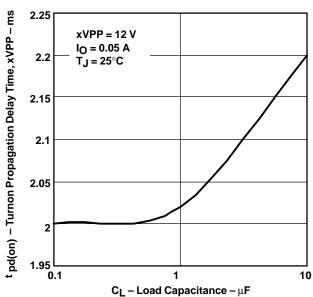

| Turnon propagation delay time, xVPP (T <sub>J</sub> = 25°C)                 | vs Load capacitance     | 13     |

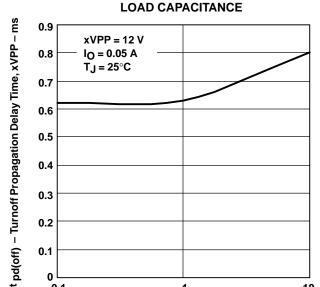

| Turnoff propagation delay time, xVPP (T <sub>J</sub> = 25°C)                | vs Load capacitance     | 14     |

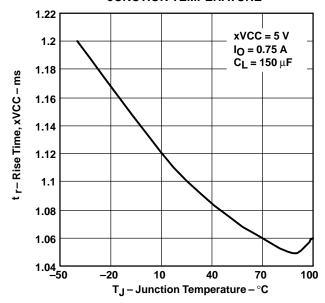

| Rise time, xVCC ( $C_L = 150 \mu F$ )                                       | vs Junction temperature | 15     |

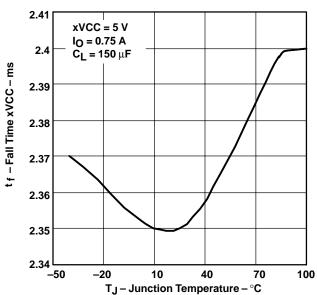

| Fall time, xVCC ( $C_L = 150 \mu F$ )                                       | vs Junction temperature | 16     |

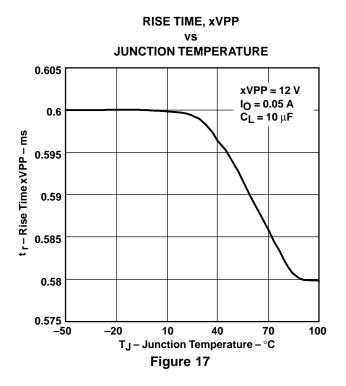

| Rise time, xVPP ( $C_L = 10 \mu F$ )                                        | vs Junction temperature | 17     |

| Fall time, xVPP ( $C_L = 10 \mu F$ )                                        | vs Junction temperature | 18     |

| Rise time, xVCC ( $T_J = 25^{\circ}C$ )                                     | vs Load capacitance     | 19     |

| Fall time, xVCC (T <sub>J</sub> = 25°C)                                     | vs Load capacitance     | 20     |

| Rise time, xVPP ( $T_J = 25^{\circ}C$ )                                     | vs Load capacitance     | 21     |

| Fall time, xVPP ( $T_J = 25^{\circ}C$ )                                     | vs Load capacitance     | 22     |

#### SHORT-CIRCUIT RESPONSE, SHORT APPLIED TO POWERED-ON 12-V xVPP-SWITCH OUTPUT

#### OC RESPONSE WITH RAMPED OVERCURRENT-LIMIT LOAD ON 5-V xVCC-SWITCH OUTPUT

#### OC RESPONSE WITH RAMPED OVERCURRENT-LIMIT LOAD ON 12-V xVPP-SWITCH OUTPUT

# TURNON PROPAGATION DELAY TIME, xVCC

# TURNOFF PROPAGATION DELAY TIME, xVCC

Figure 8

# TURNON PROPAGATION DELAY TIME, xVPP

#### JUNCTION TEMPERATURE

### TURNON PROPAGATION DELAY TIME, xVCC

#### vs LOAD CAPACITANCE

Figure 11

# TURNOFF PROPAGATION DELAY TIME, xVPP

### JUNCTION TEMPERATURE

Figure 10

#### **TURNOFF PROPAGATION DELAY TIME, xVCC**

#### vs

Figure 12

10

# TURNON PROPAGATION DELAY TIME, xVPP

## LOAD CAPACITANCE

Figure 13

# RISE TIME, xVCC

# JUNCTION TEMPERATURE

Figure 15

# TURNOFF PROPAGATION DELAY TIME, xVPP vs

Figure 14

0.1

## FALL TIME, xVCC

$C_L$  – Load Capacitance –  $\mu$ F

#### JUNCTION TEMPERATURE

Figure 16

#### **TYPICAL CHARACTERISTICS**

#### **TABLE OF GRAPHS**

|                |                                                               |                         | FIGURE |

|----------------|---------------------------------------------------------------|-------------------------|--------|

| l <sub>l</sub> | Input current, xVCC = 3.3 V                                   |                         | 23     |

|                | Input current, xVCC = 5 V                                     | vs Junction temperature | 24     |

|                | Input current, xVPP = 12 V                                    |                         | 25     |

| rDS(on)        | Static drain-source on-state resistance, 3.3 V to xVCC switch |                         | 26     |

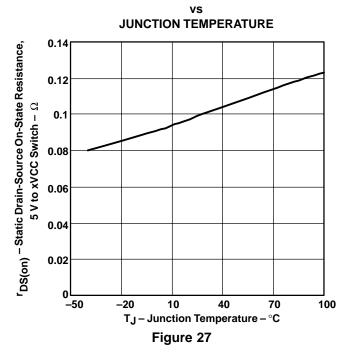

|                | Static drain-source on-state resistance, 5 V to xVCC switch   | vs Junction temperature | 27     |

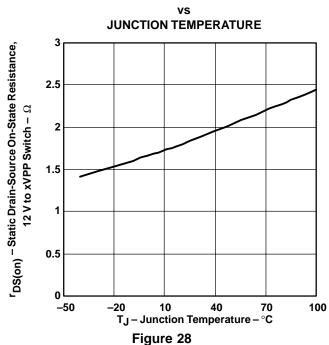

|                | Static drain-source on-state resistance, 12 V to xVPP switch  |                         | 28     |

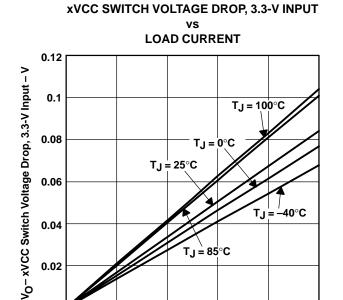

| Vo             | xVCC switch voltage drop, 3.3-V input                         |                         | 29     |

|                | xVCC switch voltage drop, 5-V input vs Load current           |                         | 30     |

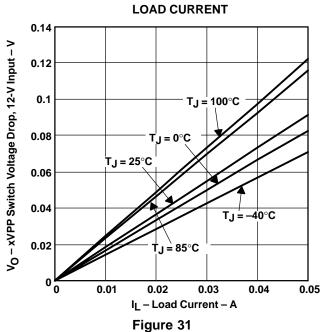

|                | xVPP switch voltage drop, 12-V input                          |                         | 31     |

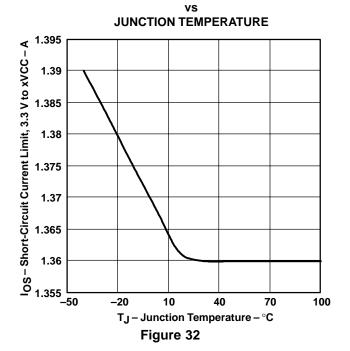

| los            | Short-circuit current limit, 3.3 V to xVCC                    |                         | 32     |

|                | Short-circuit current limit, 5 V to xVCC                      | vs Junction temperature | 33     |

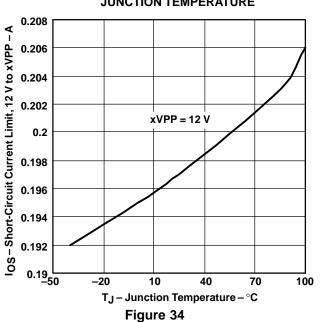

|                | Short-circuit current limit, 12 V to xVPP                     |                         | 34     |

# **INPUT CURRENT, xVPP = 12 V** vs **JUNCTION TEMPERATURE** 120 I<sub>I</sub> – Input Current, xVPP = $12 \text{ V} - \mu \text{A}$ 100 80 60 40 20 0 -50 -20 10 40 100 T.J - Junction Temperature - °C

#### STATIC DRAIN-SOURCE ON-STATE RESISTANCE, **5 V TO xVCC SWITCH**

Figure 25

#### STATIC DRAIN-SOURCE ON-STATE RESISTANCE, 12 V TO xVPP SWITCH

Figure 26

**xVCC SWITCH VOLTAGE DROP, 5-V INPUT**

Figure 29

0.4

0.6

8.0

0.2

### **LOAD CURRENT** 0.14 V<sub>O</sub> - xVCC Switch Voltage Drop, 5-V Input - V 0.12 Tی = 100°C 0.1 TJ = 0°C 0.08 T<sub>J</sub> = 25<sup>o</sup>C 0.06 T<sub>J</sub> = -40°C 0.04 T.ı = 85°C 0.02 0 0.4 0.6 8.0 IL - Load Current - A

Figure 30

# xVPP SWITCH VOLTAGE DROP, 12-V INPUT

IL - Load Current - A

SHORT-CIRCUIT CURRENT LIMIT, 3.3 V TO xVCC

## SHORT-CIRCUIT CURRENT LIMIT, 5 V TO xVCC

#### JUNCTION TEMPERATURE 1.435 IOS - Short-Circuit Current Limit, 5 V to xVCC - A 1.43 1.425 1.42 1.415 1.41 1.405 1.4 1.395 1.39 1.385 40 \_50 -20 10 70 100 $T_J$ – Junction Temperature – $^{\circ}$ C

Figure 33

# SHORT-CIRCUIT CURRENT LIMIT, 12 V TO xVPP vs JUNCTION TEMPERATURE

#### APPLICATION INFORMATION

#### **OVERVIEW**

PC Cards were initially introduced as a means to add flash memory to portable computers. The idea of add-in cards quickly took hold, and modems, wireless LANs, global positioning satellite system (GPS), multimedia, and hard-disk versions were soon available. As the number of PC Card applications grew, the engineering community quickly recognized the need for a standard to ensure compatibility across platforms. To this end, the PCMCIA (Personal Computer Memory Card International Association) was established, comprising members from leading computer, software, PC Card, and semiconductor manufacturers. One key goal was to realize the *plug-and-play* concept, so that cards and hosts from different vendors would be transparently compatible.

#### PC CARD POWER SPECIFICATION

System compatibility also means power compatibility. The most current set of specifications (PC Card Standard) set forth by the PCMCIA committee states that power is to be transferred between the host and the card through eight of the 68 terminals of the PC Card connector. This power interface consists of two  $V_{CC}$ , two  $V_{pp}$ , and four ground terminals. Multiple  $V_{CC}$  and ground terminals minimize connector-terminal and line resistance. The two  $V_{pp}$  terminals were originally specified as separate signals, but are normally tied together in the host to form a single node to minimize voltage losses. Card primary power is supplied through the  $V_{CC}$  terminals; flash-memory programming and erase voltage are supplied through the  $V_{pp}$  terminals.

#### **DESIGNING FOR VOLTAGE REGULATION**

The current PCMCIA specification for output voltage regulation,  $V_{O(reg)}$ , of the 5-V output is 5% (250 mV). In a typical PC power-system design, the power supply has an output-voltage regulation,  $V_{PS(reg)}$ , of 2% (100 mV). Also, a voltage drop from the power supply to the PC Card results from resistive losses,  $V_{PCB}$ , in the PCB traces and the PCMCIA connector. A typical design would limit the total of these resistive losses to less than 1% (50 mV) of the output voltage. Therefore, the allowable voltage drop,  $V_{DS}$ , for the device would be the PCMCIA voltage regulation less the power supply regulation and less the PCB and connector resistive drops:

$$V_{DS} = V_{O(reg)} - V_{PS(reg)} - V_{PCB}$$

Typically, this would leave 100 mV for the allowable voltage drop across the TPS2204A, TPS2206A, or TPS2210A. The voltage drop is the output current multiplied by the switch resistance of the device. Therefore, the maximum output current,  $I_{\rm O}$  max, that can be delivered to the PC Card in regulation is the allowable voltage drop across the device, divided by the output-switch resistance.

$$I_{O}$$

max =  $\frac{V_{DS}}{r_{DS(on)}}$

The xVCC outputs have been designed to deliver the peak and average currents defined by the PC Card specification within regulation over the operating temperature range. The xVPP outputs have been designed to deliver 100 mA continuously.

SLVS449A - DECEMBER 2002 - REVISED MAY 2003

#### OVERCURRENT AND OVERTEMPERATURE PROTECTION

PC Cards are inherently subject to damage that can result from mishandling. Host systems require protection against short-circuited cards that could lead to power-supply or PCB trace damage. Even extremely robust systems could undergo rapid battery discharge into a damaged PC Card, resulting in the rather sudden and unacceptable loss of system power. The reliability of fused systems is poor, in comparison, as blown fuses require troubleshooting and repair, usually by the manufacturer.

The TPS2204A, TPS2206A, and TPS2210A take a two-pronged approach to overcurrent protection. Overcurrent protection is designed to activate if an output is shorted or when an overcurrent condition is present when switches are powered up. First, instead of fuses, sense FETs monitor each of the xVCC and xVPP power outputs. Unlike sense resistors or polyfuses, these FETs do not add to the series resistance of the switch; therefore voltage and power losses are reduced. Overcurrent sensing is applied to each output separately. Excessive current generates an error signal that limits the output current of only the affected output, preventing damage to the host. Each xVCC output overcurrent limits from 1 A to 2.2 A, typically around 1.6 A; the xVPP outputs limit from 100 mA to 250 mA, typically around 200 mA.

Second, when an overcurrent condition is detected, the device asserts an active low  $\overline{OC}$  signal that can be monitored by the microprocessor or controller to initiate diagnostics and/or send the user a warning message. If an overcurrent condition persists, causing the IC to exceed its maximum junction temperature, thermal-protection circuitry activates, shutting down all power outputs until the device cools to within a safe operating region, which is ensured by a thermal shutdown hysteresis. Thermal limiting prevents destruction of the IC from overheating beyond the package power-dissipation ratings.

During power up, the devices control the rise times of the xVCC and xVPP outputs and limit the inrush current into a large load capacitance, faulty card, or connector.

#### 12-V SUPPLY NOT REQUIRED

Some PC Card switches use the externally supplied 12 V to power gate drive and other chip functions, which requires that power be present at all times. The TPS2204A, TPS2206A, and TPS2210A offer considerable power savings by using an internal charge pump to generate the required higher gate drive voltages from the 3.3-V input. Therefore, the external 12-V supply can be disabled except when needed by the PC Card in the slot, thereby extending battery lifetime. A special feature in the 12-V circuitry actually helps to reduce the supply current demanded from the 3.3-V input. When 12 V is supplied and requested at the  $V_{pp}$  output, a voltage selection circuit draws the charge-pump drive current for the 12-V FETs from the 12-V input. This selection is automatic and effectively reduces demand fluctuations on the normal 3.3-V  $V_{CC}$  rail. For proper operation of this feature, a minimum 3.3-V input capacitance of 4.7  $\mu$ F is recommended, and a minimum 12-V input ramp-up rate of 12 V/50 ms (240 V/s) is required. Additional power savings are realized during a software shutdown in which quiescent current drops to a maximum of 1  $\mu$ A.

#### **BACKWARD COMPATIBILITY**

The TPS2206A is backward compatible with the TPS2206 product, with the following considerations. An active low /SHDN is added to provide fast shutdown capability. Also, the TPS2206A does not have the active—high RESET input, which is left as no connect.

3.3-V input is required for device operation of TPS2206A.

#### **VOLTAGE-TRANSITIONING REQUIREMENT**

PC Cards, like portables, are migrating from 5 V to 3.3 V to minimize power consumption, optimize board space, and increase logic speeds. The TPS2204A, TPS2206A, and TPS2210A meet all combinations of power delivery as currently defined in the PCMCIA standard. The latest protocol accommodates mixed 3.3-V/5-V systems by first powering the card with 5 V, then polling it to determine its 3.3-V compatibility. The PCMCIA specification requires that the capacitors on 3.3-V-compatible cards be discharged to below 0.8 V before applying 3.3-V power. This action ensures that sensitive 3.3-V circuitry is not subjected to any residual 5-V charge and functions as a power RESET. PC Card specification requires that V<sub>CC</sub> be discharged within 100 ms. PC Card resistance cannot be relied on to provide a discharge path for voltages stored on PC Card capacitance because of possible high-impedance isolation by power-management schemes. The devices include discharge transistors on all xVCC and xVPP outputs to meet the specification requirement.

#### SHUTDOWN MODE

In the shutdown mode, which can be controlled by  $\overline{\text{SHDN}}$  or bit D8 of the input serial DATA word, each of the xVCC and xVPP outputs is forced to a high-impedance state. In this mode, the chip quiescent current is reduced to 1  $\mu$ A or less to conserve battery power.

#### POWER-SUPPLY CONSIDERATIONS

These switches have multiple pins for each 3.3-V (except for the TPS2210A) and 5-V power input and for the switched xVCC outputs. Any individual pin can conduct the rated input or output current. Unless all pins are connected in parallel, the series resistance is higher than that specified, resulting in increased voltage drops and power loss. It is recommended that all input and output power pins be paralleled for optimum operation.

To increase the noise immunity of the TPS2204A, TPS2206A, and TPS2210A, the power-supply inputs should be bypassed with at least a  $4.7-\mu F$  electrolytic or tantalum capacitor paralleled by a  $0.047-\mu F$  to  $0.1-\mu F$  ceramic capacitor. It is strongly recommended that the switched outputs be bypassed with a  $0.1-\mu F$  (or larger) ceramic capacitor; doing so improves the immunity of the IC to electrostatic discharge (ESD). Care should be taken to minimize the inductance of PCB traces between the devices and the load. High switching currents can produce large negative voltage transients, which forward biases substrate diodes, resulting in unpredictable performance. Similarly, no pin should be taken below -0.3 V.

#### **RESET INPUT**

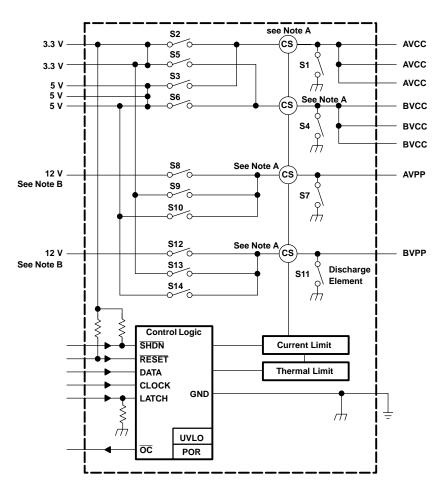

To ensure that cards are in a known state after power brownouts or system initialization, the PC Cards should be reset at the same time as the host by applying low-impedance paths from xVCC and xVPP terminals to ground. A low-impedance output state allows discharging of residual voltage remaining on PC Card filter capacitance, permitting the system (host and PC Cards) to be powered up concurrently. The active low  $\overline{RESET}$  input closes internal ground switches S1, S4, S7, and S11 with all other switches left open. The devices remain in the low-impedance output state until the signal is deasserted and new data is clocked in and latched. The input serial data cannot be latched during reset mode.  $\overline{RESET}$  is provided for direct compatibility with systems that use an active-low reset voltage supervisor. The  $\overline{RESET}$  pin has an internal 150-k $\Omega$  pullup resistor.

#### CALCULATING JUNCTION TEMPERATURE

The switch resistance,  $r_{DS(on)}$ , is dependent on the junction temperature,  $T_J$ , of the die. The junction temperature is dependent on both  $r_{DS(on)}$  and the current through the switch. To calculate  $T_J$ , first find  $r_{DS(on)}$  from Figures 26 through 28, using an initial temperature estimate about 30°C above ambient. Then calculate the power dissipation for each switch, using the formula:

$$P_D = r_{DS(on)} \times I^2$$

Next, sum the power dissipation of all switches and calculate the junction temperature:

$$T_{J} = \left(\sum P_{D} \times R_{\theta JA}\right) + T_{A}, R_{\theta JA} = 108^{\circ}C/W$$

Compare the calculated junction temperature with the initial temperature estimate. If the temperatures are not within a few degrees of each other, recalculate using the calculated temperature as the initial estimate.

#### LOGIC INPUTS AND OUTPUTS

The serial interface consists of the DATA, CLOCK, and LATCH leads. The data is clocked in on the positive edge of the clock (see Figure 2). The 9-bit (D0–D8) serial data word is loaded during the positive edge of the latch signal. The latch signal should occur before the next positive edge of the clock.

The shutdown bit of the data word places all  $V_{CC}$  and  $V_{pp}$  outputs in a high-impedance state and reduces chip quiescent current to 1  $\mu$ A to conserve battery power.

The serial interface is designed to be compatible with serial-interface PCMCIA controllers and current PCMCIA and Japan Electronic Industry Development Association (JEIDA) standards.

An overcurrent output  $(\overline{OC})$  is provided to indicate an overcurrent or overtemperature condition in any of the  $V_{CC}$  and  $V_{PP}$  outputs as previously discussed.

NOTES: A. Current sense

B. The two 12-V pins must be externally connected.

Figure 35. Internal Switching Matrix, TPS2204A and TPS2206A

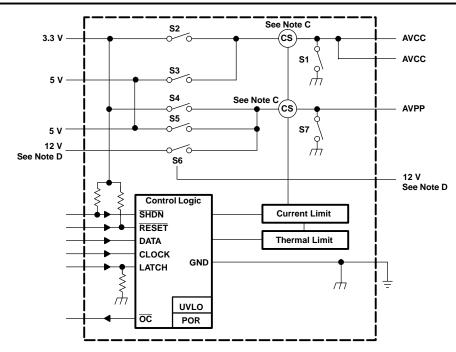

NOTES: C. Current sense

D. The two 12-V pins must be externally connected.

Figure 36. Internal Switching Matrix, TPS2210A

#### **CONTROL LOGIC**

AVPP BVPP

| CONTROL SIGNALS |    | OUTPUT | CONTROL SIGNALS |          |    | OUTPUT |         |

|-----------------|----|--------|-----------------|----------|----|--------|---------|

| D8 (SHDN)       | D0 | D1     | VAVPP           | D8 SHDN) | D4 | D5     | VBVPP   |

| 1               | 0  | 0      | 0 V             | 1        | 0  | 0      | 0 V     |

| 1               | 0  | 1      | AVCC(1)         | 1        | 0  | 1      | BVCC(2) |

| 1               | 1  | 0      | 12 V            | 1        | 1  | 0      | 12 V    |

| 1               | 1  | 1      | Hi–Z            | 1        | 1  | 1      | Hi–Z    |

| 0               | Х  | X      | Hi–Z            | 0        | Х  | X      | Hi–Z    |

<sup>(1)</sup> Output depends on AVCC

AVCC BVCC

| 2.00            |    |    |        |                 |    |    |        |

|-----------------|----|----|--------|-----------------|----|----|--------|

| CONTROL SIGNALS |    |    | OUTPUT | CONTROL SIGNALS |    |    | OUTPUT |

| D8 SHDN)        | D3 | D2 | VAVCC  | D8 SHDN)        | D6 | D7 | VBVCC  |

| 1               | 0  | 0  | 0 V    | 1               | 0  | 0  | 0 V    |

| 1               | 0  | 1  | 3.3 V  | 1               | 0  | 1  | 3.3 V  |

| 1               | 1  | 0  | 5 V    | 1               | 1  | 0  | 5 V    |

| 1               | 1  | 1  | 0 V    | 1               | 1  | 1  | 0 V    |

| 0               | Х  | Х  | Hi–Z   | 0               | Х  | Х  | Hi–Z   |

<sup>(2)</sup> Output depends on BVCC

#### USING THE DEVICES WITH 11-BIT SERIAL DATA INTERFACE CONTROLLERS

Even though the control logic table only shows a 9-bit interface, it can be used with most 11-bit serial data interface controllers. With the use of the latch input, the TPS2204A, TPS2206A, and TPS2210A only latch the last 9 bits from the serial stream. This means that for an 11-bit serial stream, bits 9 and 10 are ignored. 11-bit serial interface controllers use bits 9 and 10 for independent voltage selection of 3.3 V and 5 V between xV<sub>CC</sub> and xV<sub>PP</sub>.

#### **ESD PROTECTIONS (see FIGURE 37)**

All TPS2206A inputs and outputs of these devices incorporate ESD-protection circuitry designed to withstand a 2-kV human-body-model discharge as defined in MIL-STD-883C, Method 3015. The xVCC and xVPP outputs can be exposed to potentially higher discharges from the external environment through the PC Card connector. Bypassing the outputs with 0.1- $\mu$ F capacitors protects the devices from discharges up to 10 kV.

NOTE A: Maximum recommended output capacitance for xVCC is 220  $\mu$ F including card capacitance, and for xVPP is 10  $\mu$ F, without  $\overline{\text{OC}}$  glitch when switches are powered on.

Figure 37. Detailed Interconnections and Capacitor Recommendations

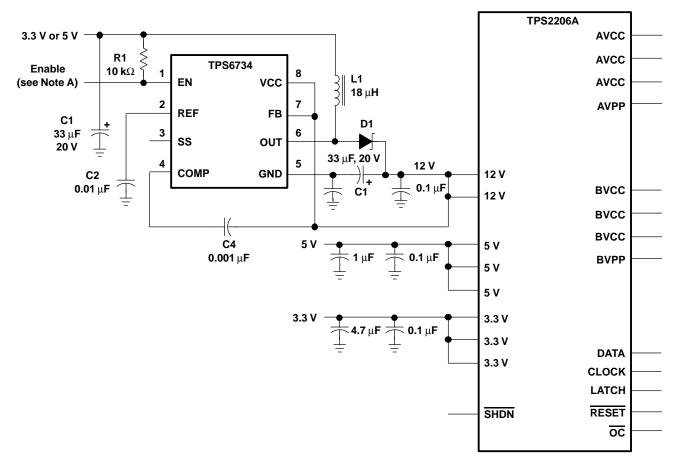

#### 12-V FLASH MEMORY SUPPLY

The TPS6734 is a fixed 12-V output boost converter capable of delivering 120 mA from inputs as low as 2.7 V. The device is pin-for-pin compatible with the MAX734 regulator and offers the following advantages: lower supply current, wider operating input-voltage range, and higher output currents. As shown in Figure 36, the only external components required are: an inductor, a Schottky rectifier, an output filter capacitor, an input filter capacitor, and a small capacitor for loop compensation. The entire converter occupies less than 0.7 in PCB space when implemented with surface-mount components. An enable input is provided to shut the converter down and reduce the supply current to 3  $\mu$ A when 12 V is not needed.

The TPS6734 is a 170-kHz current-mode PWM (pulse-width modulation) controller with an n-channel MOSFET power switch. Gate drive for the switch is derived from the 12-V output after start-up to minimize the die area needed to realize the  $0.7-\Omega$  MOSFET and improve efficiency at input voltages below 5 V. Soft start is accomplished with the addition of one small capacitor. A 1.22-V reference, pin 2 of TPS6734, is brought out for external use. For additional information, see the TPS6734 data sheet (SLVS127).

NOTE A: The enable terminal can be tied to a general-purpose I/O terminal on the PCMCIA controller or tied high.

Figure 38. TPS2206A With TPS6734 12-V, 120-mA Supply

#### PACKAGE OPTION ADDENDUM

.com 6-Dec-2006

#### PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| TPS2204APWP      | ACTIVE                | HTSSOP          | PWP                | 24   | 60             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS2204APWPR     | ACTIVE                | HTSSOP          | PWP                | 24   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS2204APWPRG4   | ACTIVE                | HTSSOP          | PWP                | 24   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS2206ADAP      | ACTIVE                | HTSSOP          | DAP                | 32   | 46             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| TPS2206ADAPR     | ACTIVE                | HTSSOP          | DAP                | 32   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| TPS2206ADAPRG4   | ACTIVE                | HTSSOP          | DAP                | 32   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-3-260C-168 HR          |

| TPS2206ADB       | ACTIVE                | SSOP            | DB                 | 30   | 50             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| TPS2206ADBR      | ACTIVE                | SSOP            | DB                 | 30   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| TPS2206ADBRG4    | ACTIVE                | SSOP            | DB                 | 30   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| TPS2210APWP      | ACTIVE                | HTSSOP          | PWP                | 24   | 60             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS2210APWPR     | ACTIVE                | HTSSOP          | PWP                | 24   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS2210APWPRG4   | ACTIVE                | HTSSOP          | PWP                | 24   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND**: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

**Green (RoHS & no Sb/Br):** TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

## **PACKAGE OPTION ADDENDUM**

6-Dec-2006

| In no event shall TI's liabil | lity arising out of such inform             | nation exceed the total n | urchase price of the TL   | part(s) at issue in this o | document sold by T |

|-------------------------------|---------------------------------------------|---------------------------|---------------------------|----------------------------|--------------------|

| to Customer on an annual      | lity arising out of such inform<br>I basis. | lation exceed the total p | urchase price of the 11 p | oant(s) at issue in this t | occument sold by T |

|                               |                                             |                           |                           |                            |                    |

|                               |                                             |                           |                           |                            |                    |

|                               |                                             |                           |                           |                            |                    |

|                               |                                             |                           |                           |                            |                    |

|                               |                                             |                           |                           |                            |                    |

|                               |                                             |                           |                           |                            |                    |

|                               |                                             |                           |                           |                            |                    |

|                               |                                             |                           |                           |                            |                    |

|                               |                                             |                           |                           |                            |                    |

|                               |                                             |                           |                           |                            |                    |

|                               |                                             |                           |                           |                            |                    |

|                               |                                             |                           |                           |                            |                    |

|                               |                                             |                           |                           |                            |                    |

|                               |                                             |                           |                           |                            |                    |

|                               |                                             |                           |                           |                            |                    |

|                               |                                             |                           |                           |                            |                    |

|                               |                                             |                           |                           |                            |                    |

|                               |                                             |                           |                           |                            |                    |

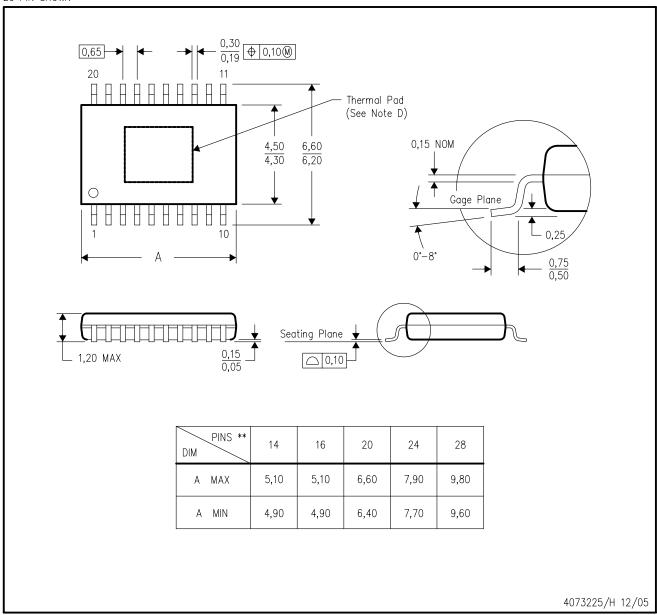

# PWP (R-PDSO-G\*\*)

## PowerPAD™ PLASTIC SMALL-OUTLINE PACKAGE

20 PIN SHOWN

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="https://www.ti.com">www.ti.com</a>.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

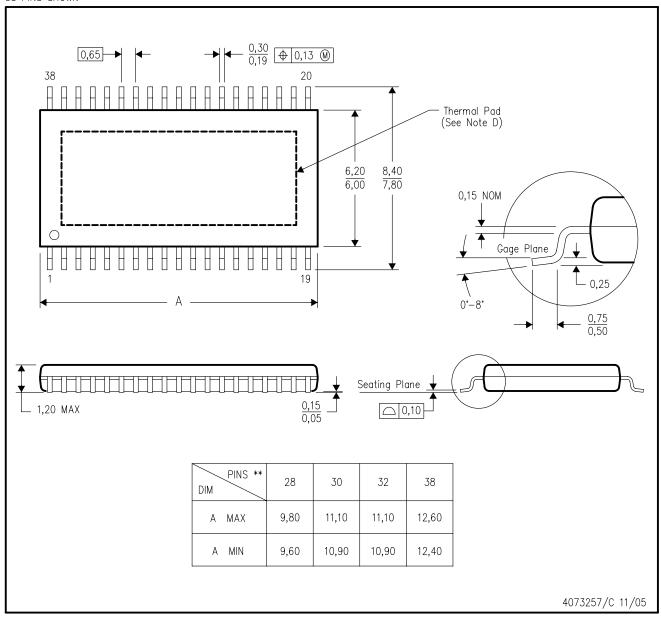

# DAP (R-PDSO-G\*\*)

## PowerPAD™ PLASTIC SMALL-OUTLINE PACKAGE

38 PINS SHOWN

NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.15 per side.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>>.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

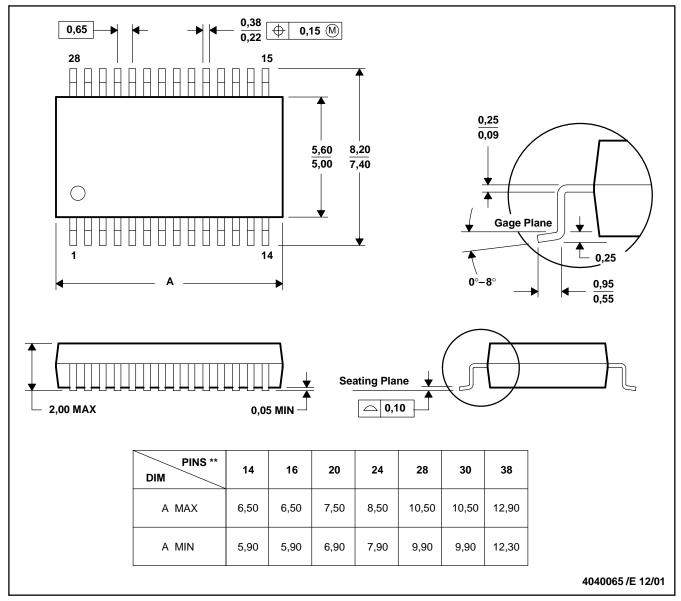

#### DB (R-PDSO-G\*\*)

#### PLASTIC SMALL-OUTLINE

#### **28 PINS SHOWN**

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

D. Falls within JEDEC MO-150

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

|                        | Applications                                                                                      |                                                                                                                                                                                                                                                                         |

|------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| amplifier.ti.com       | Audio                                                                                             | www.ti.com/audio                                                                                                                                                                                                                                                        |

| dataconverter.ti.com   | Automotive                                                                                        | www.ti.com/automotive                                                                                                                                                                                                                                                   |

| dsp.ti.com             | Broadband                                                                                         | www.ti.com/broadband                                                                                                                                                                                                                                                    |

| interface.ti.com       | Digital Control                                                                                   | www.ti.com/digitalcontrol                                                                                                                                                                                                                                               |