# Design Enhancement for the XC18V00 PROMs Manufactured at STMicroelectronics

PCN2004-17 (v1.1) October 25, 2004

Product/Process Change Notice

### **Overview**

This notification describes a design enhancement to the commercial members of the  $XC18V00^{TM}$  family of In-System Programmable Configuration PROMs manufactured at STMicroelectronics in Catania, Italy. This notification does not affect the  $XC18V00^{TM}$  family of In-System Programmable Configuration PROMs manufactured at UMC in Hsin Chu, Taiwan.

## **Description**

This design enhancement addresses the intermittent sync word issue detailed in Customer Advisory <u>CA2003-08</u> and the errata items detailed in <u>DS026-E01</u>. (NOTE: To view errata, you must be a registered user with the Xilinx <u>MySupport</u> web site.)

The new STMicroelectronics offerings are form, fit, and function compatible with the current product.

#### **Products Affected**

This notification only applies to the following part numbers manufactured at STMicroelectronics. Reference the *Traceability* section for further information on identifying these products.

| XC18V512PC20C | XC18V01PC20C | XC18V02PC44C | XC18V04PC44C |

|---------------|--------------|--------------|--------------|

| XC18V512SO20C | XC18V01SO20C | XC18V02VQ44C | XC18V04VQ44C |

| XC18V512VQ44C | XC18V01VQ44C |              |              |

**Table 1: Products Affected**

# **Key Dates**

Xilinx will begin shipping production devices manufactured at STMicroelectronics with this design enhancement starting November 9, 2004. After this date, customers ordering the standard part number may receive product manufactured with or without the design enhancement.

Qualification samples for product manufactured at STMicroelectronics with the design enhancement are now available. Use the sample ordering code ES when placing orders for these sample units. To use sample ordering code ES, append "ES" to the end of the standard ordering part number (e.g., XC18V04VQ44CES). The sample ordering code ES will be marked on the package topmark.

Customers who would like to receive only the enhanced product manufactured at STMicroelectronics beyond the onset of device cross-shipment (November 9, 2004) should use special ordering code SCD0936. To use SCD0936, append "0936" to the end of the standard ordering part number (e.g., XC18V04VQ44C0936). The ordering code 0936 will *not* be marked on the package topmark. Only product manufactured at STMicroelectronics with this design enhancement will be used to fulfill SCD0936 orders.

Customers who need devices without the design enhancement beyond the onset of device cross-shipment (November 9, 2004) may do so on a short-term basis only by using special ordering code SCD0901. To use SCD0901, append "0901" to the end of the standard part ordering number (e.g., XC18V04VQ44C0901). Only

<sup>© 2004</sup> Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>. All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

product manufactured without the design enhancement will be used to fulfill SCD0901 orders. SCD0901 is currently available for use and will be discontinued after March 1, 2005. The ordering code 0901 will *not* be marked on the package topmark.

# **Traceability**

The devices manufactured at STMicroelectronics with the design enhancement can be distinguished both visually and electrically.

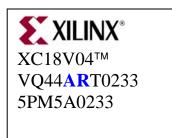

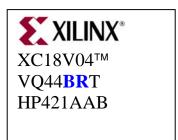

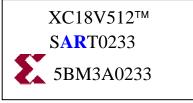

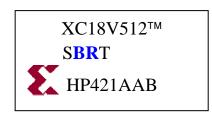

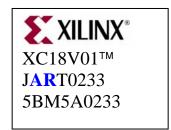

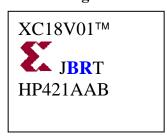

*Visually:* The devices can be distinguished visually by a 3-letter code located on the package topmark after the package/pin code. The first letter in this 3-letter code indicates the Design Circuit Revision and will be a "B" for product manufactured with the design enhancement. The Design Circuit Revision will be an "A" for product manufactured without the design enhancement. The 2<sup>nd</sup> letter of this 3-letter code indicates the fabrication location, and will be an "R" for product manufactured at STMicroelectronics. See the example below.

## Sample Topmark for 44-Pin VQFP and PLCC Packages

Figure 1: Without Design Enhancement

Figure 2: With Design Enhancement

## Sample Topmark for 20-Pin SOIC Package

Figure 4: With Design Enhancement

#### Sample Topmark for 20-Pin PLCC Package

Figure 6: With Design Enhancement

<sup>© 2004</sup> Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

*Electrically:* The devices can be distinguished electrically by the **IDCODE**:

| Device   | STMicroelectronics<br>IDCODE without<br>Design Enhancement | STMicroelectronics<br>IDCODE with<br>Design Enhancement |

|----------|------------------------------------------------------------|---------------------------------------------------------|

| XC18V512 | <b>0</b> 5033093h                                          | <b>F</b> 5033093h                                       |

| XC18V01  | <b>0</b> 5034093h                                          | <b>F</b> 5034093h                                       |

| XC18V02  | <b>0</b> 5035093h                                          | <b>F</b> 5035093h                                       |

| XC18V04  | <b>0</b> 5036093h                                          | <b>F</b> 5036093h                                       |

Table 2: IDCODEs

The current version of the programming algorithm ignores this revision field (1st character in bold above) so customers need not update their programming algorithms.

### **Qualification Data**

| Part    | Test                                                 | Sample | Hours/Cycles | Fails | Status |

|---------|------------------------------------------------------|--------|--------------|-------|--------|

| XC18V04 | HTOL @140°C                                          | 77     | 1000         | 0     | Pass   |

| XC18V04 | Temp Cycle, Condition C<br>-65°C to 150°C            | 76     | 1000         | 0     | Pass   |

| XC18V04 | HTS, 150°C                                           | 77     | 1000         | 0     | Pass   |

| XC18V04 | Temperature/Humidity<br>Bias Test - Hast 130°C/85%RH | 77     | 96           | 0     | Pass   |

| XC18V04 | ESD - HBM JESD22-A-114                               | 12     | 2000 volts   | 0     | Pass   |

| XC18V04 | Latchup – EIA/JESD78                                 | 6      | 200 mA       | 0     | Pass   |

Table 3: Reliability Qualification Data

#### Recommendation

No response is required to this PCN. Contact your <u>Xilinx Sales Representative</u> for assistance in obtaining sample or production devices. For additional information or questions, contact <u>Xilinx Technical Support</u>.

**Important Notice:** Xilinx Customer Notifications (PCN, PDN, and Quality Alerts) can be delivered via e-mail alerts sent by the MySupport website (<a href="http://www.xilinx.com/support">http://www.xilinx.com/support</a>). Register today and personalize your "MyAlerts" to include Customer Notifications. This change provides many benefits, including the ability to receive alerts for new and updated information about specific products, as well as alerts for other publications, such as data sheets, errata, application notes, and so forth. For instructions on how to sign up, refer to <a href="https://xilinx.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.nswer.n

# **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                                    |

|----------|---------|---------------------------------------------|

| 8/9/04   | 1.0     | Initial Xilinx release.                     |

| 10/25/04 | 1.1     | Revised errata URL to reflect new location. |

<sup>© 2004</sup> Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.