**AN1900**

## Transformerless Applications of Microchip's LAN9250/LAN935x Ethernet Controller and Switches

Author: Kansal Mariam Banu Shaick Ibrahim

Microchip Technology Inc.

#### INTRODUCTION

The Microchip LAN9250/LAN935x provides design solutions targeted to support next generation Ethernet switches and a 10/100 Industrial Ethernet MAC/PHY controller. The Ethernet switch products are divided into host bus and MII categories with the host bus version supporting a full featured Ethernet MAC residing behind the switch fabric. The non-host bus versions support various MII, RMII and Turbo MII options with 1 and 2 port options.

The following table lists the various products available.

| Part Number | Description                                                                  |

|-------------|------------------------------------------------------------------------------|

| LAN9250     | 10/100 Industrial Ethernet Controller & PHY                                  |

| LAN9352     | 2-Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface      |

| LAN9353     | 3-Port 10/100 Managed Ethernet Switch with Single MII/Turbo MII or Dual RMII |

| LAN9354     | 3-Port 10/100 Managed Ethernet Switch with Single RMII                       |

| LAN9355     | 3-Port 10/100 Managed Ethernet Switch with Dual MII/RMII/Turbo MII           |

Applications which are sensitive to cost, utilize short distance PCB connections, or even extreme environmental conditions like temperature may benefit from operation without the use of a transformer. A magnetic-less design could be applied anywhere when two known fixed Ethernet devices need to communicate over a known distance.

This application note provides guidelines for connecting two Microchip Ethernet devices together without a transformer.

**Note:** For information on transformerless operation of the LAN9252, refer to the Transformerless Applications of Microchip's LAN9252 EtherCAT® Controller application note.

© 2015 - 2016 Microchip Technology Inc.

#### TYPICAL TRANSFORMER ISOLATION

To appreciate non-typical transformerless application development constraints, it is first necessary to understand physical network services and signaling, and the functions that transformers provide in typical applications.

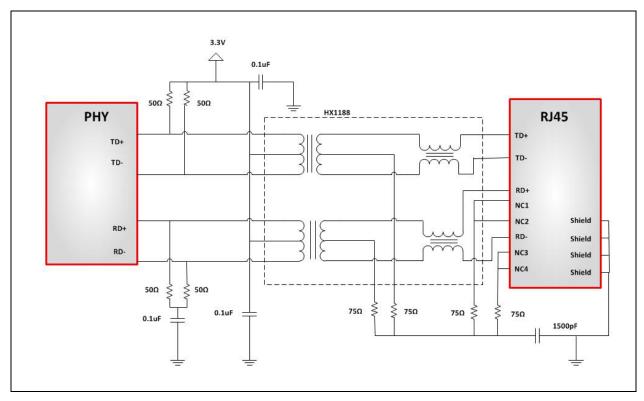

A typical network configuration consists of a point to point connection, through a cable, between two physical layer devices. Figure 1 shows a schematic for a typical transformer interface. The transmitter and the receiver of each node are DC isolated from the network cable by 1:1 transformers.

FIGURE 1: TYPICAL TRANSFORMER ISOLATION

#### TRANSFORMERLESS CONFIGURATION

To meet the operational requirements of non-typical transformerless network applications, physical layer component transmit and receive separation and biasing as well as high voltage DC isolation to meet the specific safety requirements of the application must be implemented.

For non-typical applications, the isolation that the transformer provides in typical configurations can be realized using non-polarized capacitors.

A typical network configuration provides the services of Auto-Negotiation, Auto-MDIX, 10 Mb/s operations and 100 Mb/s operations. Auto-Negotiation and Auto-MDIX must be disabled in a transformerless application because both ends of the link are under local control. The system designer can configure a specific speed and duplex on both devices to ensure proper communication.

The IEEE 802.3–2008 specification requires the TX and RX lines to run in differential mode. The TXP and TXN lines form a differential pair and need to be designed to  $100\Omega$  differential impedance for long distances and  $50\Omega$  differential impedance for short distances. The RXP and RXN lines also form a differential pair and need to be designed to appropriate differential impedance targets.

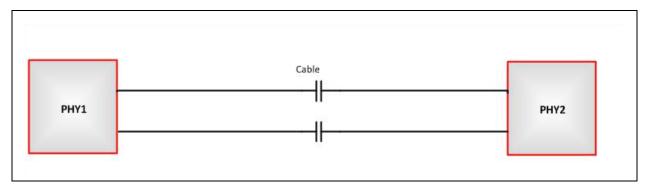

### FIGURE 2: TYPICAL TRANSFORMERLESS ISOLATION - CONNECTING TWO PHYS TOGETHER

#### **AUTO-NEGOTIATION**

The purpose of the Auto-Negotiation function is to automatically configure the transceiver to the optimum link parameters based on the capabilities of its link partner. Auto-Negotiation is a mechanism for exchanging configuration information between two link-partners and automatically selecting the highest performance mode of operation supported by both sides. In transformerless applications, Auto-Negotiation must be disabled in the Microchip device.

The following methods can be used to disable Auto-Negotiation:

- · Disabling Auto-Negotiation via Registers

- · Disabling Auto-Negotiation via Hardware Strapping

**Note:** A lowercase "x" has been appended to the end of each PHY register name in the following sections, where "x" should be replaced with "A" or "B" for the PHY A or PHY B registers respectively. In some instances, a "1" or a "2" may be appropriate instead.

#### **Disabling Auto-Negotiation via Registers**

Auto-Negotiation can be disabled by clearing the Auto-Negotiation Enable (PHY\_AN) bit of the PHY x Basic Control Register (PHY\_BASIC\_CONTROL\_x). The transceiver will then force its speed of operation to reflect the information in the PHY x Basic Control Register (PHY\_BASIC\_CONTROL\_x) Speed Select LSB (PHY\_SPEED\_SEL\_LSB) and Duplex Mode (PHY\_DUPLEX) bits. These bits are ignored when Auto-Negotiation is enabled.

|      | PHY x Basic Control Register (PHY_BASIC_CONTROL_x)                                                                                                                                                                                    |      |                                                                                                                           |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------|--|

| Bits | Description                                                                                                                                                                                                                           | Туре | Default                                                                                                                   |  |

| 13   | Speed Select LSB (PHY SPEED SEL LSB) This bit is used to set the speed of the PHY when the Auto-Negotiation Enable (PHY_AN) bit is disabled. 0: 10 Mbps 1: 100 Mbps                                                                   | R/W  | 1'b1 when in 100BASE-FX mode else 1'b1 when autoneg_strap_X is '1' else defaults to speed_strap_x value                   |  |

| 12   | Auto-Negotiation Enable (PHY AN)  This bit enables/disables Auto-Negotiation. When enabled, the Speed LSB (PHY_SPEED_SEL_LSB) and Duplex Mode (PHY_DUPLEX) are overridden.  0: Auto-Negotiation disabled  1: Auto-Negotiation enabled | R/W  | 1'b0 when in 100BASE-FX mode else defaults to autoneg_strap_X value                                                       |  |

| 8    | Duplex Mode (PHY DUPLEX) This bit is used to set the duplex when the Auto-Negotiation Enable (PHY_AN) bit is disabled. 0: Half Duplex 1: Full Duplex                                                                                  | R/W  | duplex_strap_x value when in 100BASE-FX mode else 1'b0 when autoneg_strap_X is '1' else defaults to duplex_strap_x value. |  |

#### **Disabling Auto-Negotiation via Hardware Strapping**

For LAN9250, autoneg\_strap\_2, duplex\_strap\_2 and speed\_strap\_2 are not valid.

| Strap Name       | Description                                                                                   | Pin/Default Value                                                                                                             |

|------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| autoneg_strap_1  | PHY A Auto Negotiation Enable Strap: '0' Disable Auto negotiation '1' Enable Auto negotiation | LAN9250,LAN9352,LAN9354 : 1'b1 LAN9353,LAN9355 :P1_INTPHY strap value  (Note: P1_INTPHY is a hard strap latched during reset) |

| autoneg_strap_2  | PHY B Auto Negotiation Enable Strap: '0' Disable Auto negotiation '1' Enable Auto negotiation | 1'b1                                                                                                                          |

| duplex_strap_1/2 | PHY x duplex select strap : '1' full duplex '0' Half duplex                                   | 1'b1                                                                                                                          |

| speed_strap_1/2  | PHY x speed select strap '1' 100Mbps '0' 10Mbps                                               | 1'b1                                                                                                                          |

#### **HP AUTO-MDIX**

HP Auto-MDIX facilitates the use of CAT-3 (10BASE-T) or CAT-5 (100BASE-TX) media UTP interconnect cable without consideration of the interface wiring scheme. If a user plugs in either a direct connect LAN cable or a cross-over patch cable, the transceiver is capable of configuring the TXPx/TXNx and RXPx/RXNx (for LAN9250 only single TXP/TXN,RXP/RXN) twisted pair pins for correct transceiver operation.

The internal logic of the device detects the TX and RX pins of the connecting device. Since the RX and TX line pairs are interchangeable, special PCB design considerations are needed to accommodate the symmetrical magnetics and termination of an Auto-MDIX design. For transformerless applications, it is recommended to disable HP Auto-MDIX.

**Note:** The HP Auto-MDIX feature may be useful if the TX and RX lines are accidentally swapped in the transformerless application.

**Note:** A lowercase "x" has been appended to the end of each PHY register name in the following sections, where "x" should be replaced with "A" or "B" for the PHY A or PHY B registers respectively. In some instances, a "1" or a "2" may be appropriate instead.

#### **Disabling Auto-MDIX via Registers**

Software based control of the Auto-MDIX function may be performed using the Auto-MDIX Control (AMDIXCTRL) bit of the PHY x Special Control/Status Indication Register PHY\_SPECIAL\_CONTROL\_STAT\_IND\_x). When AMDIXCTRL is set to 1, the Auto-MDIX capability is determined by the Auto-MDIX Enable (AMDIXEN) and Auto-MDIX State (AMDIX-STATE) bits of the PHY x Special Control/Status Indication Register (PHY\_SPECIAL\_CONTROL\_STAT\_IND\_x).

| PHY x Special Control/Status Indication Register (PHY_SPECIAL_CONTROL_STAT_IND_x) |                                                                                                                                                        |      |         |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| Bits                                                                              | Description                                                                                                                                            | Туре | Default |

|                                                                                   | Auto-MDIX Control (AMDIXCTRL)                                                                                                                          | R/W  |         |

|                                                                                   | This bit is responsible for determining the source of Auto-MDIX control.                                                                               | NASR |         |

| 15                                                                                | When set, Auto-MDIX functions are controlled using the AMDIXEN and AMDIXSTATE bits of this register.                                                   |      | 0       |

|                                                                                   | 0: Port x Auto-MDIX determined by strap inputs 1: Port x Auto-MDIX determined by bits 14 and 13                                                        |      |         |

|                                                                                   | Auto-MDIX Enable (AMDIXEN)                                                                                                                             | R/W  |         |

| 14                                                                                | When the AMDIXCTRL bit of this register is set, this bit is used in conjunction with the AMDIXSTATE bit to control the Port x Auto-MDIX functionality. | NASR | 0       |

|                                                                                   | Auto-MDIX State (AMDIXSTATE)                                                                                                                           | R/W  |         |

| 13                                                                                | When the AMDIXCTRL bit of this register is set, this bit is used in conjunction with the AMDIXEN bit to control the Port x Auto-MDIX functionality.    | NASR | 0       |

| Auto-MDIX Enable | Auto-MDIX State | Mode                             |

|------------------|-----------------|----------------------------------|

| 0                | 0               | Manual mode, no crossover        |

| 0                | 1               | Manual mode, crossover           |

| 1                | 0               | Auto-MDIX mode                   |

| 1                | 1               | RESERVED (do not use this state) |

#### **Disabling Auto-MDIX via Hardware Strapping**

MDIX Strap Functionality is defined as below.

| auto_mdix_strap_x | manual_mdix_strap_x | Mode                      |

|-------------------|---------------------|---------------------------|

| 0                 | 0                   | Manual mode, no crossover |

| 0                 | 1                   | Manual mode, crossover    |

| 1                 | X                   | Auto-MDIX mode            |

#### PHYSICAL CONNECTION

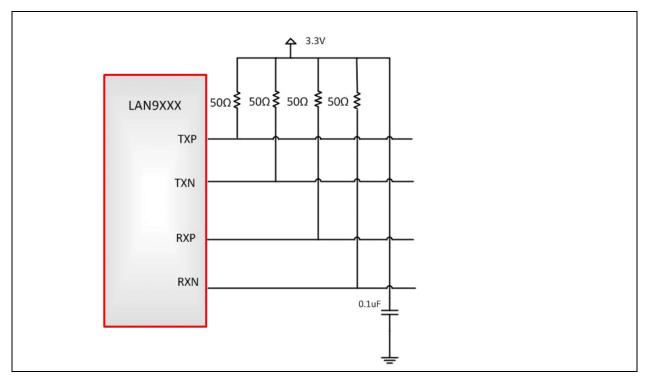

The transmitter output is designed to sink current into a transformer. When the transformer is not used, load resistors must be connected at each device to develop the output voltage as shown in Figure 3.

Note:

RX pins are configured with 50 Ohm to the supply for AMDIX operation where they may be configured as TX pins. If AMDIX is disabled and RX pins are for receive mode only, then the external termination can be tied any way possible as long as there is 100 Ohm differential across the pins.

#### FIGURE 3: LOAD RESISTORS IN TRANSFORMERLESS APPLICATION

#### **DISTANCE CONSIDERATIONS**

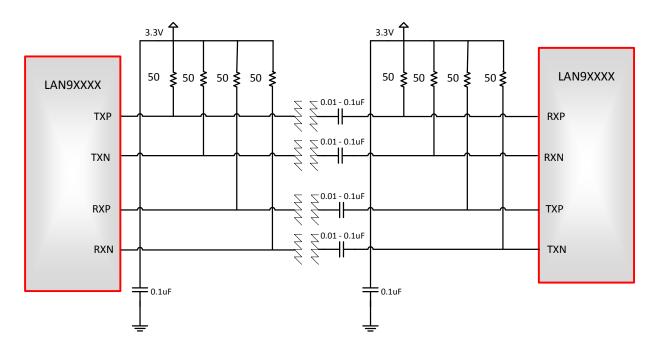

Microchip recommends that both Ethernet devices have terminating resistors on each analog pin. Proper lab validation should be performed to provide optimum resistor placement using the configuration shown in Figure 4.

Cable connections over very long distances without transformers are not encouraged due to the risk for potential high voltage build-up and noise effects.

FIGURE 4: EXAMPLE CONNECTION

**Note:** 50 Ohm termination at each device with no AC coupling capacitance can be used for PCB traces greater than 12", assuming both Microchip devices are sharing the same power domain within the same PCB.

**Note:** AC coupling capacitors are required for any board to board communications using different power domains. Due to the possible shift in power/ground domains between boards, the coupling capacitor is required to minimize DC balancing issues.

#### **SUMMARY**

Microchip Ethernet devices may be configured in non-typical transformerless network applications to transmit and receive reliably. Recommendations include the use of non-polarized capacitors for DC isolation from a network cable, with a minimum DC isolation rating which suits the individual application.

## **AN1900**

#### APPENDIX A: APPLICATION NOTE REVISION HISTORY

TABLE A-1: REVISION HISTORY

| Revision Level & Date  | Section/Figure/Entry                     | Correction                                                                                                                                                                                                                                                                                                                               |

|------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DS00001900B (06-14-16) | All                                      | LAN9252 transformerless applications is now covered in a separate application note and is therefore removed from this application note.                                                                                                                                                                                                  |

|                        | All                                      | Removed "backplane" references.                                                                                                                                                                                                                                                                                                          |

|                        | Transformerless Configuration            | <ul> <li>Removed line from third paragraph: "(except LAN9252 where Auto-Negotiation and Auto-MDIX are always enabled)"</li> <li>In third paragraph, changed "Auto-Negotiation and Auto-MDIX may" to "Auto-Negotiation and Auto-MDIX must"</li> <li>Removed fourth paragraph.</li> </ul>                                                  |

|                        | Auto-Negotiation                         | <ul> <li>Removed sentence: "LAN9XXX has been tested successfully for Auto-Negotiation with the configurations given in the hardware section below." and replaced with information stating Auto-Negotiation must be disabled in transformerless applications.</li> <li>In note, removed "(This is not applicable for LAN9250)"</li> </ul> |

|                        | Disabling Auto-Negotiation via Registers | Removed text from title: "(not applicable for LAN9252, Auto- Negotiation always enabled)"                                                                                                                                                                                                                                                |

|                        | HP Auto-MDIX                             | In note, removed "(This is not applicable for LAN9250)"                                                                                                                                                                                                                                                                                  |

|                        | Distance Considerations                  | Simplified section.                                                                                                                                                                                                                                                                                                                      |

|                        | Typical Transformer Isolation            | Simplified section.                                                                                                                                                                                                                                                                                                                      |

| DS00001900A (02-26-15) | Document Release                         |                                                                                                                                                                                                                                                                                                                                          |

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- · Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, Anyln, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2015 - 2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 9781522407010

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

#### Worldwide Sales and Service

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200

Fax: 480-792-7277 Technical Support:

http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA

Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN

Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor

Tower 6, The Gateway Harbour City, Kowloon

Hong Kong

Tel: 852-2943-5100 Fax: 852-2401-3431

**Australia - Sydney** Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Dongguan** Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829

Fax: 86-24-2334-2829

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300

Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138

Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

**Korea - Seoul** Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

**Malaysia - Kuala Lumpur** Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

**Philippines - Manila** Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Fax: 31-416-690340 Poland - Warsaw

Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

07/14/15