## **APPLICATION NOTE**

### **Two-wire LIN Networking**

**ATAN0049**

#### Introduction

Today's modern automobiles contain hundreds of sensors used to measure and report on parameters such as temperature and pressure. In most instances, these sensors are remotely located within a vehicle far away from the host microcontroller responsible for monitoring and processing the sensor data. These sensors typically do not directly connect to a network (such as CAN or LIN) due to the vehicle wiring overhead associated with connecting to the network. One such method for overcoming this wiring limitation is to convert the standard three-wire LIN network to a two-wire implementation where the LIN slave nodes harvest power directly from the LIN bus master communication wire, thereby eliminating the need for an individual battery supply wire to each slave node.

### **Conceptual Overview**

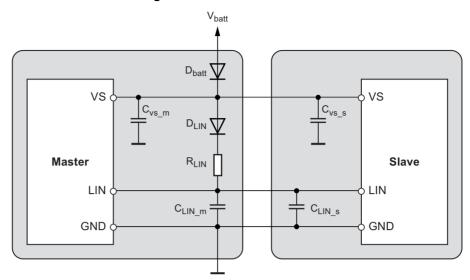

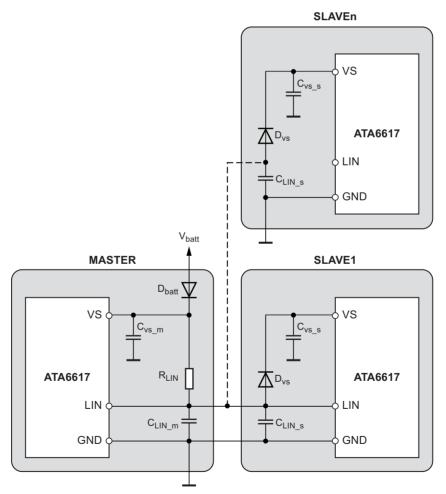

A standard LIN bus consists of a master node and up to 15 slave nodes connected to a single network. The physical LIN network is a three-wire configuration consisting of power (vehicle battery), ground and the LIN bus communication line. A pull-up resistor,  $R_{\text{LIN}}$ , typically  $1k\Omega$ , is required on the master's LIN bus line. Under normal LIN bus operation, this pull-up resistor provides a voltage bias on the LIN bus line to the slave nodes on the LIN network. It does not power the LIN slave nodes. Slave node power is derived from the battery input to the device, as shown in Figure 1.

Figure 1. Standard Three-wire LIN Configuration

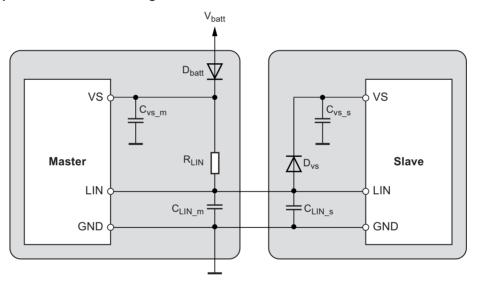

It is possible to use a non-standard LIN network architecture that simplifies to two wires. This approach relies on the harvesting of power by a connected slave node directly from the LIN bus line, thus eliminating the need for an independent slave node battery supply line. This concept is shown in Figure 2.

Figure 2. Proposed Two-wire LIN Configuration

With the battery supply line removed, all that is required to power the slave node is a blocking diode,  $V_{DS}$  and buffer capacitor,  $C_{VS\_S}$ , large enough to sustain the slave node supply voltage during the transmission of LIN data packets, which periodically pulls the LIN signal to ground. This article outlines the implementation of this two-wire approach and identifies the inherent system-level tradeoffs that must be considered to fully realize a functional two-wire LIN network.

### 1. Two-wire LIN Design Considerations

### 1.1 Key Parameters

The key to successfully implementing a two-wire LIN network centers around the power requirements of the connected slave node. The slave node must be supplied with sufficient power to maintain communication at the minimum system operating voltage: typically 9V. If this condition cannot be met, it is unlikely that the two-wire LIN implementation will be a viable solution.

Key parameters that affect the slave node's performance in the two-wire implementation are:

- LIN bus power supply

- 2. Slave node current consumption

- 3. Slave node buffer capacitance

- 4. LIN bus data protocol

### 1.1.1 LIN Bus Power Supply

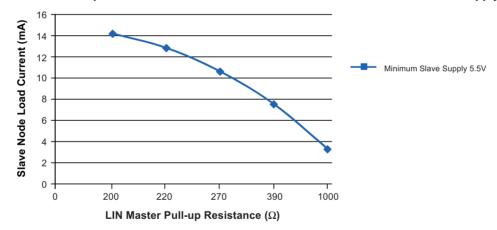

The two-wire LIN network is limited by the power supplied from the master to the slave node over the LIN bus line. The supply to the LIN slave in this configuration will be dictated by the LIN bus master pull-up resistor,  $R_{LIN}$  (Figure 2 on page 2). The slave node has a fixed minimum input voltage operating requirement of 5.5V (reference: the Atmel® ATA6624 LIN transceiver). In order to meet this minimum operating voltage requirement, the load current drawn by the slave node must not cause the voltage drop across the LIN master pull-up resistor to increase to the point at which the input voltage to the slave node drops below 5.5V. This is the minimum operating voltage threshold for slave node voltage regulator operation. Figure 1-1 shows the maximum load current available to the slave node at the minimum supply voltage of 5.5V at different LIN master pull-up resistances.

Figure 1-1. LIN Master Pull-up Resistance versus Maximum Slave Node Load Current at 5.5V Supply

The  $1k\Omega$  master pull-up resistor specified in the LIN standard specification cannot be used in the two-wire configuration. The resistor is too large and, as a result, is unable to properly source the slave node load (slave node current will be discussed in further detail in Section 1.1.2 "Slave Node Current Consumption" on page 4). The pull-up resistor must be reduced in size to the smallest value possible without exceeding the current limitation specification of the LIN driver. In the case of the typical Atmel LIN transceiver, the ATA6624, the recommended minimum pull-up resistor value is  $220\Omega$ . Resistances lower than this could result in excessive current flow through the LIN transceiver when the LIN bus is asserted low.

#### 1.1.2 **Slave Node Current Consumption**

There are several factors which contribute to the overall current consumption of the LIN slave node. They include:

- System clock frequency

- 2. Power management

- a. Sleep mode

- LIN scheduling

- Sensor load requirements

- a. Current consumption and "ON" time

### 1.1.2.1 System Clock Frequency

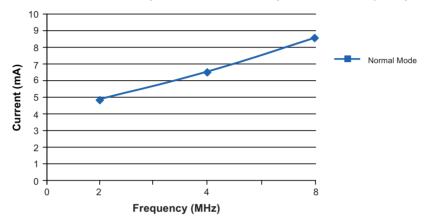

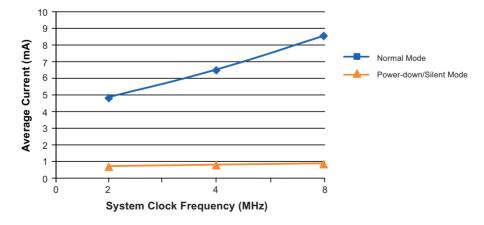

The system clock frequency of the microcontroller has the most significant effect on the slave node current consumption. The slave node current consumption is directly proportional to the clock frequency. This effect is shown in Figure 1-2.

Figure 1-2. Typical Normal Mode Atmel ATtiny167 Current versus System Clock Frequency

Clearly, one should attempt to use the lowest clock frequency that enables the application to meet functional design requirements.

#### 1.1.2.2 Power Management — Sleep Mode

The overall current consumption of the two-wire LIN slave node can be further reduced by duty-cycling between low and high current operating modes, e.g. power-down/normal mode for the microcontroller and silent/normal mode for the LIN transceiver in between LIN data frames. Figure 1-3 demonstrates this point.

Figure 1-3. Typical Current versus System Clock Frequency

2MHz system clock, 8-bit response, no load, 1s LIN schedule table period for the Power-down/Silent Mode Note: measurement case.

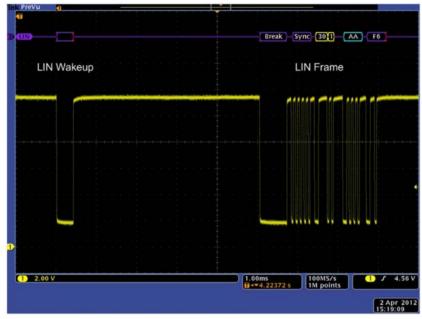

Atmel<sup>®</sup> AVR<sup>®</sup> microcontrollers provide various sleep modes, allowing the user to tailor power consumption to the application's requirements. In the case of the two-wire LIN application, the power-down mode provides the greatest current reduction when used in conjunction with the silent mode of the LIN transceiver. In this mode, all generated clocks are shut down, allowing operation of asynchronous modules only (external interrupts, USI and watchdog). To wake up the microcontroller from power-down, the LIN master must first generate a LIN wake-up request followed by a LIN frame header. This process is shown in Figure 1-4.

Figure 1-4. LIN Wake-up and LIN Frame

Upon wake-up, the microcontroller enters the normal mode and switches the EN pin (LIN transceiver enable) to HIGH at the start of each newly received LIN wake-up/frame packet. During LIN data frames, the slave node microcontroller remains in normal mode and is able to provide an immediate data response upon receipt of the sync-break and message ID. At the end of the LIN data frame, the slave node returns to the power-down mode.

Note: Operating the device in this manner will significantly reduce the average current consumption of the slave node.

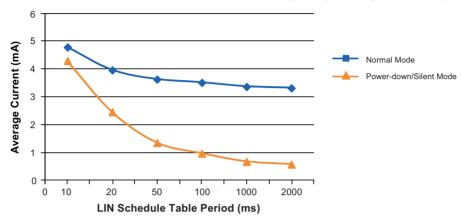

#### 1.1.2.3 Power Management — LIN Scheduling

The time between LIN frames, also known as the schedule table period, and the duration of the LIN frame define the power duty cycle of the slave node. This duty cycle affects the average current consumption of the two-wire LIN slave node. A typical LIN network operating at 19.2kbaud with a single frame, 8-bit message response has an average frame length of 2.95ms each. Figure 1-5 shows the effect of varying the schedule table period while connected to a slave node that is power duty cycling between power-down/silent and normal modes under these conditions.

Figure 1-5. Effect of LIN Schedule Periods versus Current Consumption (2MHz System Clock)

Clearly, lengthening the schedule table period reduces the slave node's average current consumption. However, this benefit is bounded by the power-down/silent mode current and offers minimal benefit for schedule periods greater than one second.

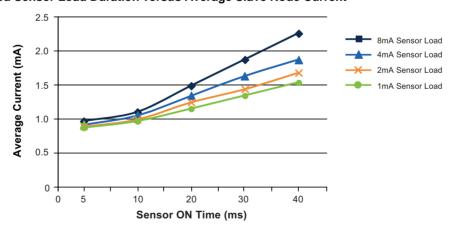

#### 1.1.2.4 Sensor Load Current

The current consumption and the active or "ON" time of the remote LIN slave sensor node are application specific parameters. The effect of different duty cycled sensor loads on the slave node can be seen in Figure 1-6 on page 6. Steady state sensor load currents are modeled using a resistive load connected between an I/O pin (5V nominal) and ground. The sensor load is pulsed "ON" for a duration of 2ms to 40ms following the slave node frame response. Once completed, the simulated load is deactivated and the slave node is placed into power-down/silent mode between message bursts of the 1s LIN frame schedule period.

Figure 1-6. Pulsed Sensor Load Duration versus Average Slave Node Current

Note: 9V supply, 2MHz slave node system clock, power-down/silent mode, 1s schedule period, 8-bit slave response, 100µF slave node buffer capacitor.

The graph shown in Figure 1-6 characterizes several load possibilities that could be used in a potential two-wire LIN network.

Of course, other possibilities exist, but the designer must keep in mind that the goal should be to limit the load size and slave node "ON" time duration as much as possible between LIN message frames to minimized the overall slave node load placed upon the two-wire LIN network supply voltage. The slave node supply is current limited by the LIN master pull-up resistance and as such an infinite number of nodes supplied by this source is not possible.

#### 1.1.3 Slave Node Buffer Capacitance

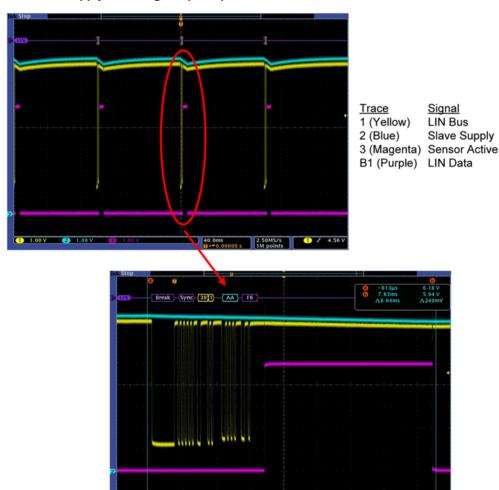

While an important piece of the two-wire LIN equation, sizing of the slave node buffer capacitor, C<sub>VS, S</sub>, is not a dominant factor. The capacitor must provide sufficient charge reserve to power the slave node during a LIN frame data packet (LIN signal is periodically asserted low) and also receive a full charge between LIN frame data transmissions (the LIN signal is pulled up to system supply voltage). In practice, bench tests indicate that a buffer capacitor of 47µF to 100µF is sufficient to maintain power to the slave node for a network operating at a data rate of 19.2kbaud with a 100ms delay (or greater) between LIN data frames and a 9V minimum operating battery voltage. Figure 1-7 provides a visualization of one such case using a 100µF buffer capacitor.

Figure 1-7. Slave Node Supply Buffering, 100µF Capacitor

9V supply,2MHz system clock, Power-down/Silent Mode, 100ms schedule period, 100µF Slave Node buffer Note: capacitor, 2mA sensor load, 5ms sensor load duration.

The slave node shown in Figure 1-7 is configured to operate in power-down/silent mode between LIN frames. The attached sensor load was modeled as a  $2.5 \mathrm{k}\Omega$  resistor. This creates a steady state slave node current draw of 2mA with a 5V regulated supply. The sensor load was then pulsed "ON" for 5ms in duration at the end of each transmitted LIN slave frame response to simulate sensor loading during data acquisition mode. As can be seen from the expanded screen capture of the plot, the voltage on the slave node power supply only drops by 240mV between the beginning of the frame transmission and the deactivation of the simulated sensor load.

#### 1.1.4 LIN Bus Data Protocol

The format of the LIN bus data protocol will affect the charge/discharge rate of the slave node supply line buffer capacitor. Three factors affect the data format:

- Rate of data transfer

- 2. Quantity of data transferred

- 3. LIN data schedule table period

The LIN bus data rate should be kept high, i.e., a maximum baud rate of 19.2kHz or higher to maximize the speed at which the data can be transferred. The quantity of data (number of bits) should be kept as low as possible in order to minimize the duration of the dominant state (logic level low) on the LIN bus line. And finally, the LIN schedule table period should be long enough in duration to allow the LIN bus powered slave node time to fully recharge the buffer capacitor,  $C_{VS\_S}$ , between LIN message frames.

Note: Most Atmel<sup>®</sup> LIN transceivers are capable of baud rates in excess of the LIN specification (please refer to the specific device data sheet for more information).

### 1.2 Multi-Slave Evaluation Network

The multi-slave two-wire LIN network used for test and characterization purposes is shown in Figure 1-8. The two-wire LIN network total node count is limited only by the LIN master pull-up resistor's ability to source the required current to the attached slave nodes to maintain normal operation (slave node  $V_S$  greater than 5.5V).

Figure 1-8. Two-wire LIN Multi-slave Network

Each node has been realized using the Atmel<sup>®</sup> ATA6617-EK<sup>(1)</sup> evaluation board and configured using the settings shown in Table 1-1. This configuration provides one possible operating scenario and, as such, will most likely need to be modified to accommodate the end user's application.

Note:

1. The Atmel ATA6617-EK is an Atmel LIN system in package (SiP) evaluation board which consists of an Atmel AVR<sup>®</sup> microcontroller, the ATtiny167, and the Atmel LIN system basis chip (SBC), the ATA6624. For more detailed information, please refer to the product data sheets for the respective devices.

Table 1-1. Multi-Slave Network Configuration

| LIN Frame  | Baud rate: 19.2kbaud              |

|------------|-----------------------------------|

|            | Message payload: 8-bits           |

|            | Schedule table: 1s                |

| LIN Master | Operating voltage: 9V             |

|            | Pull-up resistance: 220Ω          |

|            | System clock: 8MHz                |

|            | Blocking diode: removed           |

| MCU        | Operating voltage: 5V             |

|            | Power cycling: Yes                |

|            | System clock: 2MHz                |

|            | LIN slave buffer capacitor: 100µF |

|            | Sensor load: 4mA/8ms              |

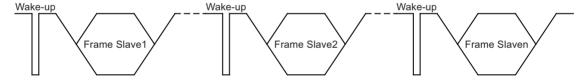

The network utilizes the standard LIN protocol and does not deviate from the LIN2.x standard in any manner. The schedule table has been optimized for the two-wire LIN application where a LIN wake-up frame is followed by a single slave node frame, Figure 1-9.

Figure 1-9. Multi-slave LIN Frame Schedule

Standard LIN protocol dictates that each node must process every incoming frame ID message on the bus. This forces each slave node to wake-up on every incoming message, regardless of ownership. Sending a wake-up frame followed by a single slave node frame minimizes the time that each slave node is powered "ON". The alternate approach of sending a wake-up frame followed by a sequential burst of all the slave frames will cause slave nodes to remain awake longer than necessary. The end result is an overall increase in system load current — a scenario that should be avoided.

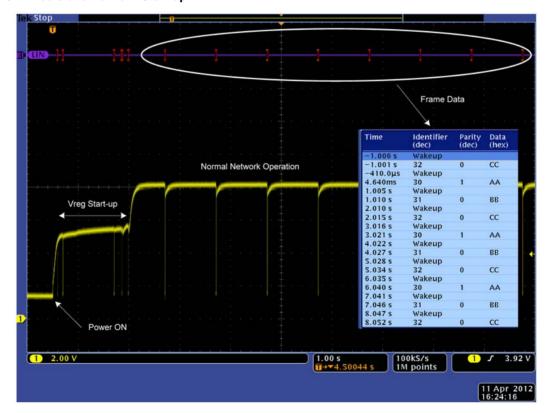

#### 1.2.1 Network Start-up and the Voltage Regulator

A multi-slave, two-wire LIN network can be implemented so long as the supply voltage to the slave node does not drop below the 5.5V minimum input voltage requirement of the Atmel® ATA6617 voltage regulator. In this regard, extensive testing has shown that the network as currently configured cannot support more than three slave nodes at any one time. The effective load placed upon the LIN master pull-up resistor simply cannot source enough current to meet the minimum input voltage requirement under all operating conditions.

Ultimately, the network is limited by the voltage drop across the LIN master pull-up resistor and the cumulative load induced by the multiple slave nodes. Adding slave nodes to the network will increase the effective load placed upon LIN master pull-up resistor. The load placed upon  $V_{batt}$  results in an increased voltage drop across the master pull-up resistor,  $R_{LIN}$ , thus decreasing the input supply voltage to the slave nodes. If the input voltage falls below 5.5V, the minimum input voltage required for Atmel ATA6617 voltage regulator operation, the output will become unregulated and the slave node(s) will be rendered inoperable. In this mode of operation, the voltage regulator pass transistor behaves as a switch and the input voltage flows directly through to the regulator output. Voltage regulator current in this region is unstable and can be upwards of 3mA in excess of the normally regulated current. Operation in this unstable region will lead to non-linear increases in the voltage drop across the LIN master pull-up resistor,  $R_{LIN}$ .

Increasing the number of slave nodes on the network greatly raises the risk that an "unregulated" voltage regulator condition will occur. This is due to the brief, but instantaneous spike in the load current of each slave node when power is initially supplied to the network at start-up. Extra current is required to kick-start the voltage regulator of each slave node. Even though the average current consumption in the multi-slave network is approximately 0.8mA per slave node, an extra 2mA to 3mA of current must be factored into the overall current consumption of each node at start-up.

### 1.2.1.1 Four-node Network (1 Master, 3 Slaves)

Figure 1-10 shows the effect that the load has upon the LIN bus line at network power-on when three slave nodes are connected to the network. The plot clearly shows that slave node start-up briefly places an extra load on the network not seen during normal operation. At start-up, the LIN bus supply voltage hovers around 5.5V. Eventually, the slave node voltage regulators stabilize and the supply voltage settles to 8.2V. Network communication begins at this point.

Figure 1-10. Three-slave Network Start-up

### 1.2.1.2 Five-node Network (1 Master, 4 Slaves)

Figure 1-11 shows the start-up behavior when a fourth slave node is added to the network. In this case, the LIN bus supply voltage is never able to recover from the start-up load condition and hovers at 5V (0.5V below the minimum operating voltage of the voltage regulator). The measured voltage drop across the LIN master pull-up resistor in this case is 3.3V.

Frame Data Identifier (dec) Master Frame Requests, No Slave Response 420.0us Wakeup Heavily Loaded Network, No Slave Communication Wakeup 1.004 s 1.009 Wakeup 2.014 Wakeup Wakeup Wakeup .024 Wakeup Wakeup Wakeup 1 2.00 V 100kS/s 1M points

Figure 1-11. Four-slave Network Sequential, Start-up

The load current through the 220  $\!\Omega$  LIN master pull-up resistor under these conditions is calculated by:

$$I_{RLIN} = V_{RLIN} / R_{LIN} = 3.3 / 220 = 15 mA$$

Referencing the plot from Figure 1-1 on page 3, one can see that the maximum load current supported by the  $220\Omega$  LIN master pull-up resistor is approximately 13mA at 5.5V. The 15mA load caused by the addition of the fourth slave node is 2mA greater than the two-wire LIN network can handle. As a result, the slave nodes fail to respond to the master frame requests.

To mitigate this effect, consider the scenario where the slave nodes are started sequentially (one node after the other, not all at once). In this case, network communication will occur as shown in Figure 1-12 on page 12. Staggering the start-up of the individual slave nodes greatly reduces the current load on the network at reset, in effect increasing the node handling capabilities of the two-wire network.

Frame Data Identifier (dec) RR wakeup CC Wakeup DD Wakeun AA Wakeup BB vakeup CC DD Wakeup wakeup RR Wakeup CC (1) 2.00 V 100kS/s 1M points

Figure 1-12. Four-slave Network, Serial Start-up

A network using this implementation could potentially run up to 12 slave nodes under the same network conditions; a) current per slave node is 0.8mA and b) 3mA voltage regulator start-up transient is limited to one slave node at a time.

Then,

$I_{Slave\_total}$  = number of slaves  $\times$   $I_{Slave}$  = 12  $\times$  0.8 = 9.6mA

and.

$$I_{Network} = I_{Slave\_total} + I_{Vreg\_start} = 9.6 + 3 = 12.6 mA$$

The calculated current of 12.6mA is slightly below the 13mA maximum supply current that the LIN master is capable of supporting with a pull-up resistance of  $220\Omega$ . In theory, this network should be possible.

### 2. Conclusion

The analysis and measurements here have shown that the existing LIN networking topology (three wires, battery, ground and LIN) can be easily transformed to a two-wire implementation (LIN and ground) with very little effort. All that is required is a thorough understanding of the system supply/load requirements and several hardware modifications to enable the slave node to harvest power from the master LIN bus line in between LIN data frame transmissions. The two-wire LIN network is best suited for low-node count networks where the system is limited to one master and no more than three slaves where all nodes are powered on simultaneously. The number of slave nodes could potentially be increased if the system designer is able to implement a power-on scheme where the slave nodes are activated serially to limit the surge current at network start-up.

## 3. Appendix

### 3.1 Node Schematics

#### 3.1.1 LIN Master

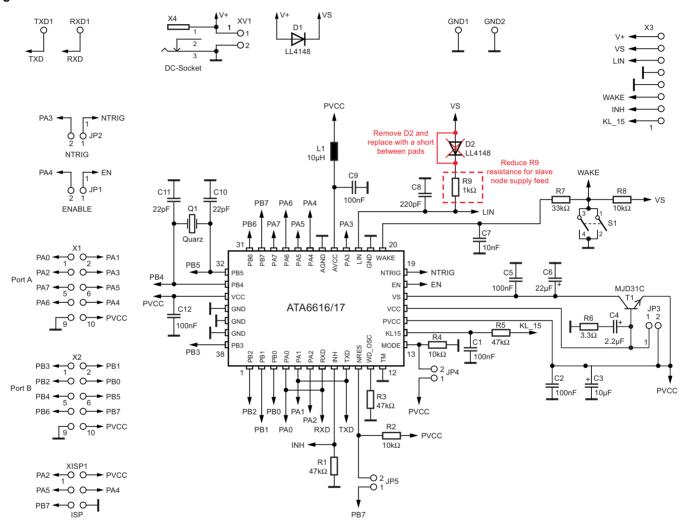

The LIN master node was realized using the Atmel® ATA6617-EK evaluation board. It must be modified as shown in Figure 3-1.

Figure 3-1. Atmel ATA6617 Two-wire LIN Master

The master pull-up diode,  $D_2$ , is not needed and should be removed. This has the added benefit of increasing the minimum operating voltage of the slave node by approximately 0.7V. Additionally, the pull-up resistor,  $R_9$ , must be decreased from the LIN standard  $1k\Omega$  to  $220\Omega$  to improve the charging characteristics of the slave node buffer capacitor.

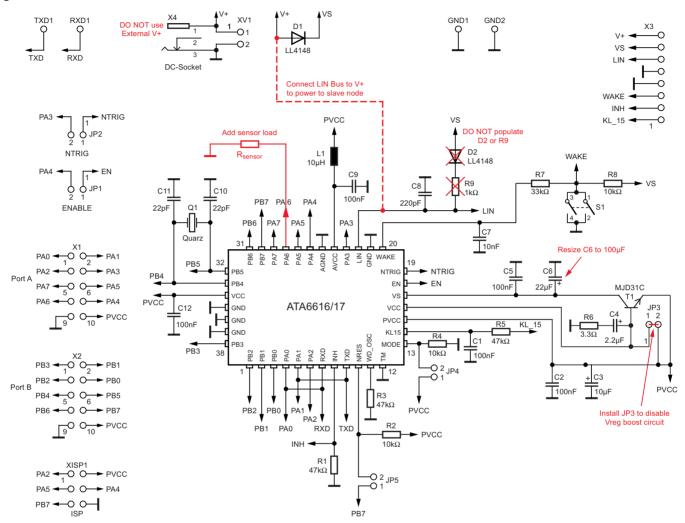

#### 3.1.2 LIN Slave

Similar to the LIN master, the slave node was also realized using the Atmel<sup>®</sup> ATA6617-EK evaluation board. It must be modified for the application as shown in Figure 3-2.

Figure 3-2. Atmel ATA6617 Two-wire LIN Slave

The external power supply input on the module is not used. To receive power, the anode of diode,  $D_1$ , must be connected to the LIN bus line as shown. The supply buffer capacitor,  $C_6$ , should also be increased from the standard  $22\mu F$  to  $100\mu F$ . The resistive sensor load is optional and only used for simulation purposes.

# 4. Revision History

Please note that the following page numbers referred to in this section refer to the specific revision mentioned, not to this document.

| Revision No.     | History                             |

|------------------|-------------------------------------|

| 9281B-AUTO-04/15 | Put document in the latest template |

1600 Technology Drive, San Jose, CA 95110 USA

T: (+1)(408) 441.0311

F: (+1)(408) 436.4200

www.atmel.com

© 2015 Atmel Corporation. / Rev.: 9281B-AUTO-04/15

**Atmel Corporation**

Atmel®, Atmel logo and combinations thereof, Enabling Unlimited Possibilities®, AVR®, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. Other terms and product names may be trademarks of others.

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.