### **HIGHLIGHTS**

This section of the manual contains the following major topics:

| 1.0  | Introduction                              | 2  |

|------|-------------------------------------------|----|

| 2.0  | CPU Clocking                              | 6  |

| 3.0  | Oscillator Configuration Registers        | 7  |

| 4.0  | Special Function Registers                | 13 |

| 5.0  | Primary Oscillator (POSC)                 | 39 |

| 6.0  | Internal Fast RC (FRC) Oscillator         | 45 |

| 7.0  | Low-Power RC (LPRC) Oscillator            | 46 |

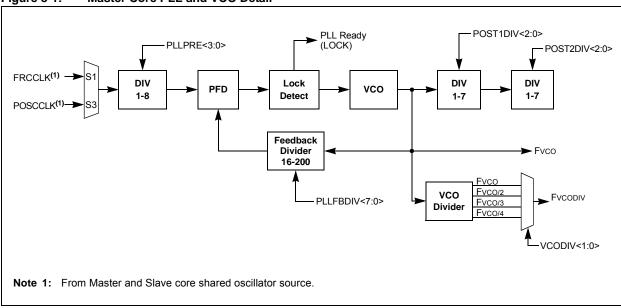

| 8.0  | Master Phase-Locked Loop (PLL)            | 47 |

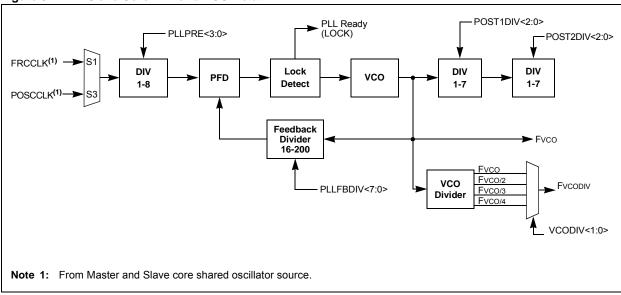

| 9.0  | Slave Phase-Locked Loop (PLL)             | 53 |

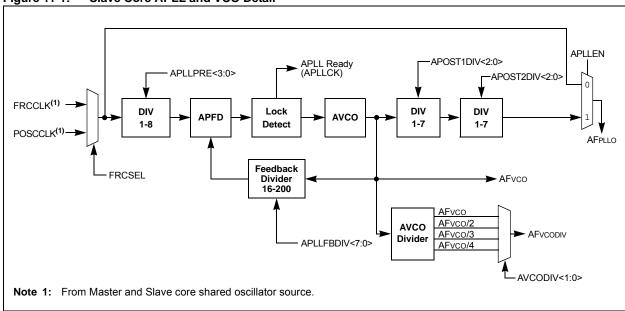

| 10.0 | Master Auxiliary Phase-Locked Loop (APLL) | 59 |

| 11.0 | Slave Auxiliary Phase-Locked Loop (APLL)  | 61 |

| 12.0 | Fail-Safe Clock Monitor (FSCM)            | 63 |

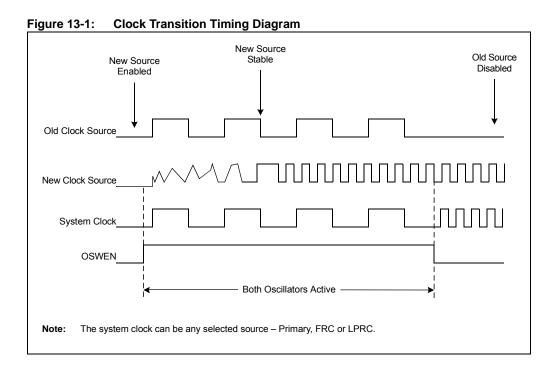

| 13.0 | Clock Switching.                          | 64 |

| 14.0 | Two-Speed Start-up                        | 68 |

| 15.0 | Reference Clock Output                    | 68 |

| 16.0 | Register Maps                             | 69 |

| 17.0 | Related Application Notes                 | 71 |

| 18.0 | Revision History                          | 72 |

#### Note:

This family reference manual section is meant to serve as a complement to device data sheets. This document applies to all dsPIC33/PIC24 devices. Some dsPIC33/PIC24 devices are dual core and contain both a Master and Slave CPU core. For single core dsPIC33/PIC24 devices, disregard any Slave-specific references.

Please consult the note at the beginning of the "Oscillator Configuration" chapter in the current device data sheet to check whether this document supports the device you are using.

Device data sheets and family reference manual sections are available for download from the Microchip Worldwide Web site at: http://www.microchip.com.

### 1.0 INTRODUCTION

The Oscillator Module with High-Speed PLL includes these characteristics:

- · Master and Slave Core Subsystems

- · Internal and External Oscillator Sources Shared between Master and Slave Cores

- Master and Slave Independent On-Chip Phase-Locked Loop (PLL) to Boost Internal Operating Frequency on Select Internal and External Oscillator Sources

- Master and Slave Independent Auxiliary PLL (APLL) Clock Generator to Boost Operating Frequency for Peripherals.

- Master and Slave Independent Doze mode for System Power Savings

- Master and Slave Independent Scalable Reference Clock Output (REFCLKO)

- On-the-Fly Clock Switching between Various Clock Sources

- Fail-Safe Clock Monitoring (FSCM) that Detects Clock Failure and Permits Safe Application Recovery or Shutdown

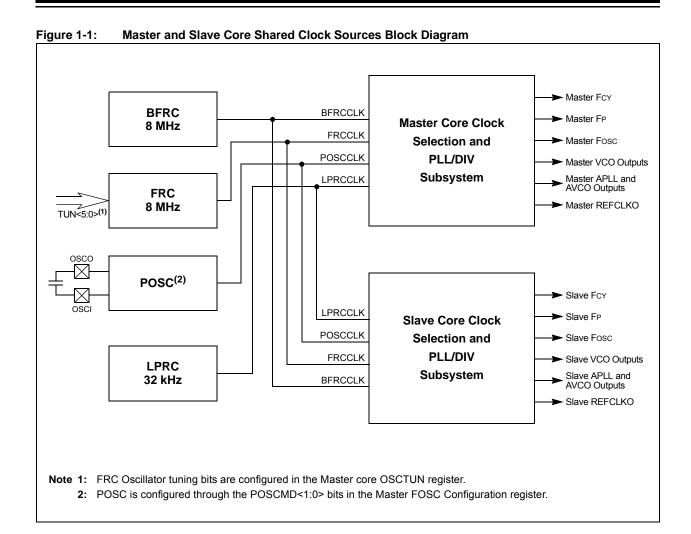

A block diagram of the dsPIC33/PIC24 shared core oscillator system is shown in Figure 1-1.

© 2016-2017 Microchip Technology Inc.

DS70005255B-page 4

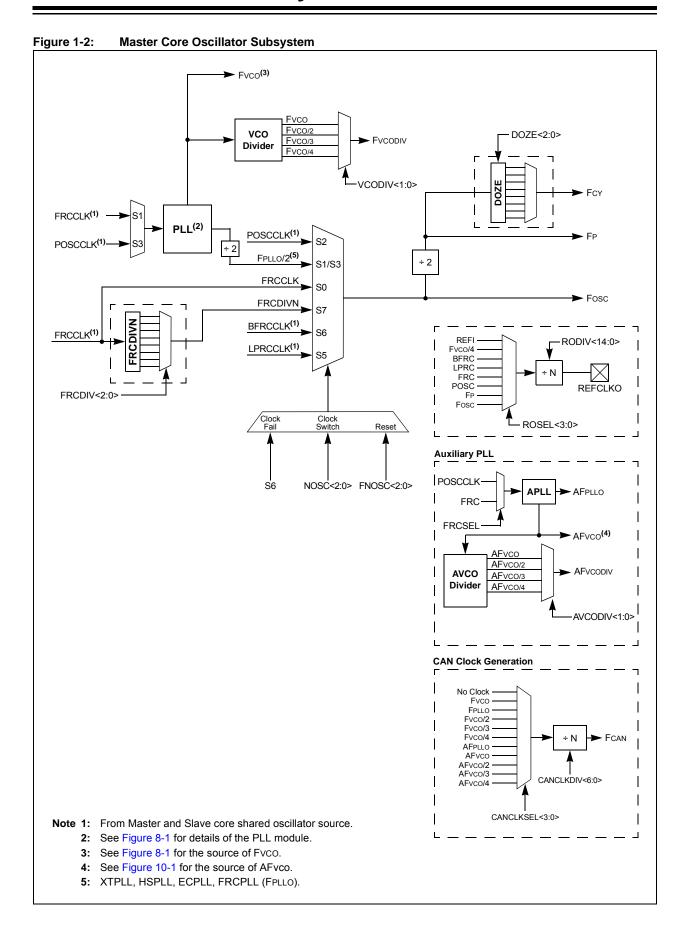

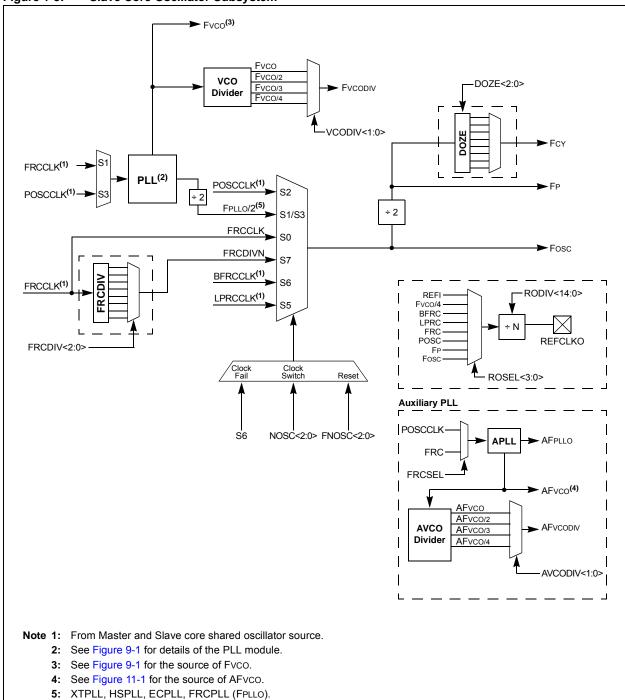

Figure 1-3: Slave Core Oscillator Subsystem

### 2.0 CPU CLOCKING

While the Master and Slave subsystems share access to a single set of oscillator sources, all other clocking logic is implemented individually. The Master and Slave core can be configured independently to use any of the following clock configurations:

- · Primary Oscillator (POSC) on the OSC1 and OSC2 pins

- · Internal Fast RC Oscillator (FRC) with optional clock divider

- Internal Low-Power RC Oscillator (LPRC)

- · Primary Oscillator with PLL

- Internal Fast RC Oscillator with PLL (FRCPLL)

- · Backup Internal Fast RC Oscillator (BFRC)

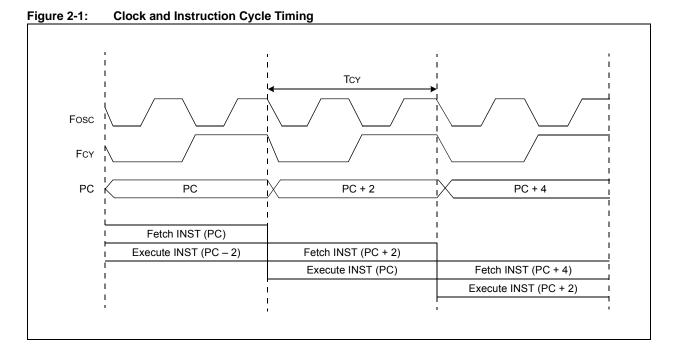

Each core's system clock source is divided by two to produce the internal instruction cycle clock. In this document, the instruction cycle clock is denoted by Fcy. The timing diagram in Figure 2-1 illustrates the relationship between the system clock (Fosc), the instruction cycle clock (Fcy) and the Program Counter (PC).

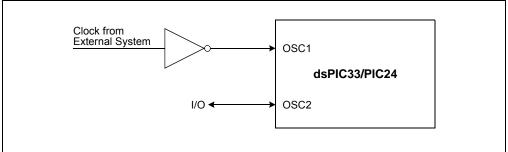

The internal instruction cycle clock (FcY) can be output on the OSC2 I/O pin if the Primary Oscillator mode or the HS mode is not selected as the clock source. For more information, see **Section 5.0 "Primary Oscillator (POSC)"**.

### 3.0 OSCILLATOR CONFIGURATION REGISTERS

### 3.1 Master Oscillator Configuration Registers

• FOSCSEL: Master Oscillator Source Selection Register

FOSCSEL selects the Master core's initial oscillator source and start-up option. FOSCSEL contains the following Configuration bits:

- The FNOSC<2:0> Configuration bits in the Master Oscillator Source Selection register (FOSCSEL<2:0>) determine the clock source that is used at a Power-on Reset (POR).

Thereafter, the clock source can be changed between permissible clock sources with clock switching.

- The Internal FRC Oscillator with Postscaler (FRCDIVN) is the default (unprogrammed) selection.

#### FOSC: Master Oscillator Configuration Register

FOSC configures the Primary Oscillator mode, OSC2 pin function, Peripheral Pin Select (PPS) and the Fail-Safe and Clock Switching modes. FOSC contains the following Configuration bits:

- The POSCMD<1:0> (FOSC<1:0>) Configuration bits select the operation mode of the POSC that is available to both the Master and Slave cores.

- The OSCIOFNC (FOSC<2>) Configuration bit selects the OSC2 pin function, except in High-Speed or Medium Speed Oscillator (XT) mode.

If OSCIOFNC is unprogrammed ('1'), the Master FCY clock is output on the OSC2 pin. If OSCIOFNC is programmed ('0'), the OSC2 pin becomes a general purpose I/O pin.

Table 3-1 lists the configuration settings that select the device's Master core oscillator source and operating mode at a POR.

| Oscillator<br>Source | Oscillator Mode                               | FNOSC<2:0><br>Value | POSCMD<1:0> <sup>(3)</sup><br>Value | Notes |

|----------------------|-----------------------------------------------|---------------------|-------------------------------------|-------|

| S0                   | Fast RC Oscillator (FRC)                      | 000                 | xx                                  | 1     |

| S1                   | Fast RC Oscillator with PLL (FRCPLL)          | 001                 | xx                                  | 1     |

| S2                   | Primary Oscillator (EC)                       | 010                 | 00                                  | 1     |

| S2                   | Primary Oscillator (XT)                       | 010                 | 01                                  |       |

| S2                   | Primary Oscillator (HS)                       | 010                 | 10                                  |       |

| S3                   | Primary Oscillator with PLL (ECPLL)           | 011                 | 00                                  | 1     |

| S3                   | Primary Oscillator with PLL (XTPLL)           | 011                 | 01                                  |       |

| S3                   | Primary Oscillator with PLL (HSPLL)           | 011                 | 10                                  |       |

| S4                   | Reserved                                      | 100                 | xx                                  |       |

| S5                   | Low-Power RC Oscillator (LPRC)                | 101                 | xx                                  | 1     |

| S6                   | Backup FRC (BFRC)                             | 110                 | xx                                  | 1     |

| S7                   | Fast RC Oscillator with ÷ N Divider (FRCDIVN) | 111                 | xx                                  | 1, 2  |

- Note 1: The OSC2 pin function is determined by the OSCIOFNC Configuration bit.

- 2: This is the default oscillator mode for an unprogrammed (erased) device.

- **3:** The POSCMD<1:0> bits are only available in the Master Oscillator Configuration register, FOSC.

#### Register 3-1: FOSCSEL: Master Oscillator Source Selection Register

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1           | U-1 | U-1 |  |  |  |  |  |  |  |

|--------|-----|-----|-----|-----|---------------|-----|-----|--|--|--|--|--|--|--|

| _      | _   | _   | _   | _   | _             | _   | _   |  |  |  |  |  |  |  |

| bit 23 |     |     |     |     | bit 23 bit 16 |     |     |  |  |  |  |  |  |  |

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/PO-1 | U-1         | U-1 | U-1 | U-1 | R/PO-1 | R/PO-1 | R/PO-1 |  |  |

|--------|-------------|-----|-----|-----|--------|--------|--------|--|--|

| IESO   | _           | _   | _   | _   | FNOSC2 | FNOSC1 | FNOSC0 |  |  |

| bit 7  | bit 7 bit 0 |     |     |     |        |        |        |  |  |

**Legend:** PO = Program Once bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '1'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 23-8 Unimplemented: Read as '1'

bit 7 **IESO:** Internal External Start-up Option bit

1 = Starts up device with the Internal FRC Oscillator, then automatically switches to the user-selected oscillator source when ready

0 = Starts up device with the user-selected oscillator source

bit 6-3 Unimplemented: Read as '1'

bit 2-0 FNOSC<2:0>: Initial Oscillator Source Selection bits

111 = Fast RC Oscillator with Divide-by-N (FRCDIVN)

110 = Backup FRC Oscillator (BFRC)

101 = Low-Power RC Oscillator (LPRC)

100 = Reserved

011 = Primary Oscillator with PLL (XTPLL, HSPLL, ECPLL)

010 = Primary Oscillator (XT, HS, EC)

001 = Fast RC Oscillator with PLL (FRCPLL)

000 = Fast RC Oscillator (FRC)

#### Register 3-2: FOSC: Master Oscillator Configuration Register

| U-1    | U-1           | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 |  |  |  |

|--------|---------------|-----|-----|-----|-----|-----|-----|--|--|--|

| _      | _             | _   | _   | _   | _   | _   | _   |  |  |  |

| bit 23 | bit 23 bit 16 |     |     |     |     |     |     |  |  |  |

| U-1    | U-1 | U-1 | R/PO-1 | R/PO-1 | R/PO-1 | U-1 | R/PO-1 |

|--------|-----|-----|--------|--------|--------|-----|--------|

| _      | _   | _   | XTBST  | XTCFG1 | XTCFG0 | _   | PLLKEN |

| bit 15 |     |     |        |        |        |     | bit 8  |

| R/PO-1 | R/PO-1 | U-1 | U-1 | U-1 | R/PO-1                  | R/PO-1                 | R/PO-1                 |

|--------|--------|-----|-----|-----|-------------------------|------------------------|------------------------|

| FCKSM1 | FCKSM0 | _   | _   | _   | OSCIOFNC <sup>(1)</sup> | POSCMD1 <sup>(2)</sup> | POSCMD0 <sup>(2)</sup> |

| bit 7  |        |     |     |     |                         |                        | bit 0                  |

**Legend:** PO = Program Once bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '1'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 23-13 Unimplemented: Read as '1'

bit 12 XTBST: Kick-Starter Programmability for Oscillator bit

1 = Boosts the kick-start

0 = Default kick-start

bit 11-10 XTCFG<1:0>: Crystal Oscillator Drive Select bits

Current gain programmability for oscillator (output drive).

11 = Gain3 (use for 24-32 MHz crystals)

10 = Gain2 (use for 16-24 MHz crystals)

11 = Gain1 (use for 8-16 MHz crystals)

11 = Gain0 (use for 4-8 MHz crystals)

bit 9 **Unimplemented:** Read as '1'

bit 8 PLLKEN: PLL Lock Enable bit

1 = Source for PLL lock signal is the lock detect

0 = Source for PLL lock signal is the PLL enable signal

bit 7-6 **FCKSM<1:0>:** Clock Switching Mode bits

1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled

01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled

00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled

bit 5-3 **Unimplemented:** Read as '1'

bit 2 OSCIOFNC: OSC2 Pin Function bit (except in XT and HS modes)<sup>(1)</sup>

1 = OSC2 is the clock output and the Master core instruction cycle (Master FcY) clock is output on the

0002 piii

0 = OSC2 is a general purpose digital I/O pin

bit 1-0 **POSCMD<1:0>:** Primary Oscillator Mode Selection bits<sup>(2)</sup>

11 = Primary Oscillator is disabled

10 = HS Crystal Oscillator mode (10 MHz to 32 MHz)

01 = XT Crystal Oscillator mode (3.5 MHz to 10 MHz)

00 = EC (External Clock) mode (0 MHz to 64 MHz)

**Note 1:** If both the Master core OSCIOFNC and Slave core S1OSCIOFNC bits are set, the Master core OSCIOFNC bit has priority.

2: The POSCMD<1:0> bits are only available in the Master Oscillator Configuration register, FOSC. This setting configures the Primary Oscillator for use by either core.

### 3.2 Slave Oscillator Configuration Registers

• FS10SCSEL: Slave Oscillator Source Selection Register

FS1OSCSEL selects the initial oscillator source and start-up option. FS1OSCSEL contains the following Configuration bits:

- The S1FNOSC<2:0> Configuration bits in the Slave Oscillator Source Selection register (FS1OSCSEL<2:0>) determine the clock source that is used at a Power-on Reset (POR). Thereafter, the clock source can be changed between permissible clock sources with clock switching.

- The Internal FRC Oscillator with Postscaler (FRCDIVN) is the default (unprogrammed) selection.

- FS1OSC: Slave Oscillator Configuration Register

FS1OSC configures the Primary Oscillator mode, OSC2 pin function, Peripheral Pin Select (PPS), and the Fail-Safe and Clock Switching modes.

Table 3-2 lists the configuration settings that select the device's Slave core oscillator source and operating mode at a POR.

Table 3-2: Configuration Bit Values for Clock Selection

| Oscillator<br>Source | Oscillator Mode                               | S1FNOSC<2:0><br>Value | POSCMD<1:0> <sup>(3)</sup><br>Value | Notes |

|----------------------|-----------------------------------------------|-----------------------|-------------------------------------|-------|

| S0                   | Fast RC Oscillator (FRC)                      | 000                   | xx                                  | 1     |

| S1                   | Fast RC Oscillator with PLL (FRCPLL)          | 001                   | xx                                  | 1     |

| S2                   | Primary Oscillator (EC)                       | 010                   | 00                                  | 1     |

| S2                   | Primary Oscillator (XT)                       | 010                   | 01                                  |       |

| S2                   | Primary Oscillator (HS)                       | 010                   | 10                                  |       |

| S3                   | Primary Oscillator with PLL (ECPLL)           | 011                   | 00                                  | 1     |

| S3                   | Primary Oscillator with PLL (XTPLL)           | 011                   | 01                                  |       |

| S3                   | Primary Oscillator with PLL (HSPLL)           | 011                   | 10                                  |       |

| S4                   | Reserved                                      | 100                   | xx                                  | 1     |

| S5                   | Low-Power RC Oscillator (LPRC)                | 101                   | xx                                  | 1     |

| S6                   | Backup FRC Oscillator (BFRC)                  | 110                   | xx                                  | 1     |

| S7                   | Fast RC Oscillator with ÷ N Divider (FRCDIVN) | 111                   | xx                                  | 1, 2  |

- Note 1: The OSC2 pin function is determined by the S1OSCIOFNC Configuration bit. If both the Master core OSCIOFNC and Slave core S1OSCIOFNC bits are set, the Master core OSCIOFNC bit has priority.

- 2: This is the default oscillator mode for an unprogrammed (erased) device.

- **3:** The POSCMD<1:0> bits are only available in the Master Oscillator Configuration register, FOSC. This setting configures the Primary Oscillator for use by either core.

#### Register 3-3: FS1OSCSEL: Slave Oscillator Source Selection Register

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| _      | _   | _   | _   | _   | _   | _   | _      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| U1     | U-1   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/PO-1 | U-1 | U-1 | U-1 | U-1 | R/PO-1   | R/PO-1   | R/PO-1   |

|--------|-----|-----|-----|-----|----------|----------|----------|

| S1IESO | _   | _   | _   | _   | S1FNOSC2 | S1FNOSC1 | S1FNOSC0 |

| bit 7  | •   |     |     |     |          |          | bit 0    |

**Legend:** PO = Program Once bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '1'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 23-8 **Unimplemented:** Read as '1'

bit 7 S1IESO: Internal External Start-up Option bit

1 = Starts up device with the Internal FRC Oscillator, then automatically switches to the user-selected oscillator source when ready

0 = Starts up device with the user-selected oscillator source

bit 6-3 **Unimplemented:** Read as '1'

bit 2-0 **S1FNOSC<2:0>:** Initial Oscillator Source Selection bits

111 = Fast RC Oscillator with Divide-by-N (FRCDIVN)

110 = Backup FRC Oscillator (BFRC)

101 = Low-Power RC Oscillator (LPRC)

100 = Reserved

011 = Primary Oscillator with PLL (XTPLL, HSPLL, ECPLL)

010 = Primary Oscillator (XT, HS, EC)

001 = Fast RC Oscillator with PLL (FRCPLL)

000 = Fast RC Oscillator (FRC)

#### Register 3-4: FS1OSC: Slave Oscillator Configuration Register

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| _      | _   | _   | _   | _   | _   | _   | _      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | R/PO-1   |

|--------|-----|-----|-----|-----|-----|-----|----------|

| _      | _   | _   | _   | _   | _   | _   | S1PLLKEN |

| bit 15 |     |     |     |     |     |     | bit 8    |

| R/PO-1   | R/PO-1   | U-1 | U-1 | U-1 | R/PO-1                    | U-1 | U-1   |

|----------|----------|-----|-----|-----|---------------------------|-----|-------|

| S1FCKSM1 | S1FCKSM0 | _   | _   | _   | S10SCI0FNC <sup>(1)</sup> | _   | _     |

| bit 7    |          |     |     |     |                           |     | bit 0 |

**Legend:** PO = Program Once bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '1'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 23-9 Unimplemented: Read as '1'

bit 8 S1PLLKEN: PLL Lock Enable bit

1 = Clock switches will wait for PLL lock signal

0 = Source for PLL lock signal is the PLL enable signal

bit 7-6 **S1FCKSM<1:0>:** Clock Switching Mode bits

1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled

01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled

00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled

bit 5-3 **Unimplemented:** Read as '1'

bit 2 **S10SCIOFNC:** OSC2 Pin Function bit (except in XT and HS modes)<sup>(1)</sup>

1 = OSC2 is the clock output and the Slave core instruction cycle (Slave FcY) clock is output on the OSC2

nin

0 = OSC2 is a general purpose digital I/O pin

bit 1-0 **Unimplemented:** Read as '1'

**Note 1:** If both the Master core OSCIOFNC and Slave core S1OSCIOFNC bits are set, the Master core OSCIOFNC bit has priority.

### 4.0 SPECIAL FUNCTION REGISTERS

### 4.1 Master Special Function Registers

These Special Function Registers provide run-time control and status of the Master core's oscillator system:

OSCCON: Oscillator Control Register<sup>(1)</sup>

This register controls clock switching and provides status information that allows the current clock source, PLL lock and clock fail conditions to be monitored.

· CLKDIV: Clock Divider Register

This register controls Doze mode, the FRC divider and PLL prescaler.

PLLFBD: PLL Feedback Divider Register

This register selects the PLL feedback divider.

OSCTUN: FRC Oscillator Tuning Register

This register is available to the Master core only and provides the ability to tune the Internal FRC Oscillator frequency in software.

PLLDIV: PLL Output Divider Register

This register controls the VCO divider and both PLL post-dividers.

ACLKCON1: Auxiliary Clock Control Register

This register is used to configure and enable the Auxiliary PLL. APLL clock source selection, APLL prescaler setting and APLL lock status are all contained in this register.

APLLFBD1: APLL Feedback Divider Register

This register controls the APLL feedback divider.

APLLDIV1: APLL Output Divider Register

This register controls the AVCO divider and both APLL post-dividers.

CANCLKCON: CAN Clock Control Register<sup>(4)</sup>

This register controls the CAN clock source and divider selection.

• REFOCONL: Reference Clock Control Low Register

This register is used to configure and enable the Reference Clock output.

REFOCONH: Reference Clock Control High Register

This register controls the Reference Clock output divider selection.

#### Register 4-1: OSCCON: Oscillator Control Register<sup>(1)</sup>

| U-0    | R-0   | R-0   | R-0   | U-0 | R/W-y                | R/W-y                | R/W-y                |

|--------|-------|-------|-------|-----|----------------------|----------------------|----------------------|

| _      | COSC2 | COSC1 | COSC0 | _   | NOSC2 <sup>(2)</sup> | NOSC1 <sup>(2)</sup> | NOSC0 <sup>(2)</sup> |

| bit 15 |       |       |       |     |                      |                      | bit 8                |

| R/W-0   | U-0 | R-0  | U-0 | R/W-0             | U-0 | U-0 | R/W-0 |

|---------|-----|------|-----|-------------------|-----|-----|-------|

| CLKLOCK | _   | LOCK | _   | CF <sup>(3)</sup> | _   | _   | OSWEN |

| bit 7   |     |      |     |                   |     |     | bit 0 |

| Legend:           | y = Value Set from Configuration bits on POR |                                    |                    |  |  |  |

|-------------------|----------------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                             | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                             | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 15 **Unimplemented:** Read as '0'

bit 14-12 **COSC<2:0>:** Current Oscillator Selection bits (read-only)

111 = Fast RC Oscillator (FRC) with Divide-by-N (FRCDIVN)

110 = Backup FRC Oscillator (BFRC)

101 = Low-Power RC Oscillator (LPRC)

100 = Reserved

011 = Primary Oscillator (XT, HS, EC) with PLL (XTPLL, HSPLL, ECPLL)

010 = Primary Oscillator (XT, HS, EC)

001 = Fast RC Oscillator (FRC) with PLL (FRCPLL)

000 = Fast RC Oscillator (FRC)

bit 11 **Unimplemented:** Read as '0'

bit 10-8 NOSC<2:0>: New Oscillator Selection bits<sup>(2)</sup>

111 = Fast RC Oscillator (FRC) with Divide-by-N (FRCDIVN)

110 = Backup FRC Oscillator (BFRC)

101 = Low-Power RC Oscillator (LPRC)

100 = Reserved

011 = Primary Oscillator (XT, HS, EC) with PLL (XTPLL, HSPLL, ECPLL)

010 = Primary Oscillator (XT, HS, EC)

001 = Fast RC Oscillator (FRC) with PLL (FRCPLL)

000 = Fast RC Oscillator (FRC)

bit 7 CLKLOCK: Clock Lock Enable bit

1 = If (FCKSM0 = 1), then the clock and PLL configurations are locked; if (FCKSM0 = 0), then the clock and PLL configurations may be modified

0 = Clock and PLL selections are not locked, configurations may be modified

bit 6 **Unimplemented:** Read as '0'

bit 5 LOCK: PLL Lock Status bit (read-only)

1 = Indicates that PLL is in lock or the PLL start-up timer is satisfied

0 = Indicates that PLL is out of lock, the start-up timer is in progress or PLL is disabled

bit 4 Unimplemented: Read as '0'

bit 3 **CF**: Clock Fail Detect bit<sup>(3)</sup>

1 = FSCM has detected a clock failure

0 = FSCM has not detected a clock failure

**Note 1:** Writes to this register require an unlock sequence.

2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL modes are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

3: This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and will trigger an oscillator failure trap.

### Register 4-1: OSCCON: Oscillator Control Register<sup>(1)</sup> (Continued)

bit 2-1 Unimplemented: Read as '0'

bit 0 **OSWEN:** Oscillator Switch Enable bit

1 = Requests oscillator switch to the selection specified by the NOSC<2:0> bits

0 = Oscillator switch is complete

**Note 1:** Writes to this register require an unlock sequence.

- 2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL modes are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- 3: This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and will trigger an oscillator failure trap.

#### Register 4-2: CLKDIV: Clock Divider Register

| R/W-0  | R/W-0                | R/W-1                | R/W-1                | R/W-0                  | R/W-0   | R/W-0   | R/W-0   |

|--------|----------------------|----------------------|----------------------|------------------------|---------|---------|---------|

| ROI    | DOZE2 <sup>(1)</sup> | DOZE1 <sup>(1)</sup> | DOZE0 <sup>(1)</sup> | DOZEN <sup>(2,3)</sup> | FRCDIV2 | FRCDIV1 | FRCDIV0 |

| bit 15 | •                    |                      |                      |                        |         |         | bit 8   |

| U-0   | U-0 | r-0 | r-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-1                  |

|-------|-----|-----|-----|------------------------|------------------------|------------------------|------------------------|

| _     | _   | _   | _   | PLLPRE3 <sup>(4)</sup> | PLLPRE2 <sup>(4)</sup> | PLLPRE1 <sup>(4)</sup> | PLLPRE0 <sup>(4)</sup> |

| bit 7 |     |     |     |                        |                        |                        | bit 0                  |

| Legend:           | r = Reserved bit |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

- bit 15 ROI: Recover on Interrupt bit

- 1 = Interrupts will clear the DOZEN bit and the processor clock, and the peripheral clock ratio is set to 1:1

- 0 = Interrupts have no effect on the DOZEN bit

- bit 14-12 **DOZE<2:0>:** Processor Clock Reduction Select bits<sup>(1)</sup>

- 111 = Fcy divided by 128

- 110 = FCY divided by 64

- 101 = Fcy divided by 32

- 100 = Fcy divided by 16

- 011 = Fcy divided by 8 (default)

- 010 = Fcy divided by 4

- 001 = Fcy divided by 2

- 000 = Fcy divided by 1

- bit 11 **DOZEN:** Doze Mode Enable bit<sup>(2,3)</sup>

- 1 = DOZE<2:0> bits field specifies the ratio between the peripheral clocks and the processor clocks

- 0 = Processor clock and peripheral clock ratio is forced to 1:1

- bit 10-8 FRCDIV<2:0>: Internal Fast RC Oscillator Postscaler bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2

- 000 = FRC divided by 1 (default)

- bit 7-6 **Unimplemented:** Read as '0'

- bit 5-4 **Reserved:** Read as '0'

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- 2: This bit is cleared when the ROI bit is set and an interrupt occurs.

- 3: The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

- 4: PLLPRE<3:0> bits may be updated while the PLL is operating, but the VCO may overshoot.

#### Register 4-2: CLKDIV: Clock Divider Register (Continued)

```

bit 3-0

PLLPRE<3:0>: PLL Phase Detector Input Divider Select bits (also denoted as 'N1', PLL prescaler)

1111 = Reserved

1001 = Reserved

1000 = Input divided by 8

0111 = Input divided by 7

0110 = Input divided by 6

0101 = Input divided by 5

0100 = Input divided by 4

0011 = Input divided by 3

0010 = Input divided by 2

0001 = Input divided by 1 (power-on default selection)

0000 = Invalid selection

```

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- 2: This bit is cleared when the ROI bit is set and an interrupt occurs.

- 3: The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

- 4: PLLPRE<3:0> bits may be updated while the PLL is operating, but the VCO may overshoot.

### Register 4-3: PLLFBD: PLL Feedback Divider Register

| U-0    | U-0 | U-0 | U-0 | r-0 | r-0 | r-0 | r-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-1         | R/W-0 | R/W-0 | R/W-1 | R/W-0 | R/W-1 | R/W-1 | R/W-0 |  |

|---------------|-------|-------|-------|-------|-------|-------|-------|--|

| PLLFBDIV<7:0> |       |       |       |       |       |       |       |  |

| bit 7         |       |       |       |       |       |       |       |  |

| Legend:           | r = Reserved bit |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

Note 1: The allowed range is 16-200 (decimal). The rest of the values are reserved and should be avoided. The power on the default feedback divider is 150 (decimal) with an 8 MHz FRC input clock. The VCO frequency is 1.2 GHz.

### Register 4-4: OSCTUN: FRC Oscillator Tuning Register

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | _   |       |       | TUN   | <5:0> |       |       |

| bit 7 |     |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-6 **Unimplemented:** Read as '0'

bit 5-0 **TUN<5:0>:** FRC Oscillator Tuning bits

011111 = Maximum frequency deviation of 1.74% (8.139 MHz)

011110 = Center frequency + 1.693% (8.135 MHz)

. . .

000001 = Center frequency + 0.047% (8.038 MHz)

000000 = Center frequency (8.00 MHz nominal)

111111 = Center frequency – 0.047% (7.962 MHz)

• • •

100001 = Center frequency – 1.693% (7.865 MHz)

100000 = Minimum frequency deviation of -1.74% (7.861 MHz)

#### Register 4-5: PLLDIV: PLL Output Divider Register

| U-0    | U-0          | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0  |  |

|--------|--------------|-----|-----|-----|-----|-------|--------|--|

| _      | _            | _   | _   | _   | _   | VCODI | V<1:0> |  |

| bit 15 | bit 15 bit 8 |     |     |     |     |       |        |  |

| U-0   | R/W-1                          | R/W-0 | R/W-0 | U-0 | R/W-0              | R/W-0 | R/W-1 |  |

|-------|--------------------------------|-------|-------|-----|--------------------|-------|-------|--|

| _     | POST1DIV<2:0> <sup>(1,2)</sup> |       |       | _   | POST2DIV<2:0>(1,2) |       |       |  |

| bit 7 |                                |       |       |     |                    |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-10 Unimplemented: Read as '0'

bit 9-8 VCODIV<1:0>: PLL VCO Output Divider Select bits

11 = VCO clock 10 = VCO/2 clock 01 = VCO/3 clock 00 = VCO/4 clock

bit 7 **Unimplemented:** Read as '0'

bit 6-4 **POST1DIV<2:0>:** PLL Output Divider #1 Ratio bits<sup>(1,2)</sup>

POST1DIV<2:0> bits can have a valid value from 1 to 7 (POST1DIVx value should be greater than or equal to the POST2DIVx value). The POST1DIVx divider is designed to operate at higher clock rates

than the POST2DIVx divider.

bit 3 Unimplemented: Read as '0'

bit 2-0 **POST2DIV<2:0>:** PLL Output Divider #2 Ratio bits<sup>(1,2)</sup>

POST2DIV<2:0> bits can have a valid value from 1 to 7 (POST2DIVx value should be less than or equal to the POST1DIVx value). The POST1DIVx divider is designed to operate at higher clock rates than the POST2DIVx divider.

Note 1: The POST1DIVx and POST2DIVx divider values must not be changed while the PLL is operating.

2: The default values for POST1DIVx and POST2DIVx are 4 and 1, respectively, yielding a 150 MHz Master PLL output.

### Register 4-6: ACLKCON1: Auxiliary Clock Control Register

| R/W-0                 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |  |

|-----------------------|--------|-----|-----|-----|-----|-----|--------|--|

| APLLEN <sup>(1)</sup> | APLLCK | _   | _   | _   | _   | _   | FRCSEL |  |

| bit 15 bit 8          |        |     |     |     |     |     |        |  |

| U-0   | U-0 | r-0 | r-0 | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|-------|-----|-----|-----|----------|----------|----------|----------|

| _     | _   | _   | _   | APLLPRE3 | APLLPRE2 | APLLPRE1 | APLLPRE0 |

| bit 7 |     |     |     |          |          |          | bit 0    |

| Legend:           | r = Reserved bit |                                      |                    |  |  |

|-------------------|------------------|--------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | t U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                 | x = Bit is unknown |  |  |

**APLLEN:** Auxiliary PLL Enable/Bypass Select bit(1) bit 15 1 = AFPLLO is connected to the APLL post-divider output (bypass disabled) 0 = AFPLLO is connected to the APLL input clock (bypass enabled) bit 14 APLLCK: APLL Phase-Locked Loop State Status bit 1 = Auxiliary PLL is in lock 0 = Auxiliary PLL is not in lock bit 13-9 Unimplemented: Read as '0' bit 8 FRCSEL: FRC Clock Source Select bit 1 = FRC is the clock source for APLL 0 = Primary Oscillator is the clock source for APLL bit 7-6 Unimplemented: Read as '0' bit 5-4 Reserved: Read as '0' APLLPRE<3:0>: Auxiliary PLL Phase Detector Input Divider Select bits bit 3-0 1111 = Reserved 1001 = Reserved 1000 = Input divided by 8 0111 = Input divided by 7 0110 = Input divided by 6 0101 = Input divided by 5 0100 = Input divided by 4 0011 = Input divided by 3

0001 = Input divided by 1 (power-on default selection)

Note 1: Even with the APLLEN bit set, another peripheral must generate a clock request before the APLL will start.

0010 = Input divided by 2

0000 = Invalid selection

### Register 4-7: APLLFBD1: APLL Feedback Divider Register

| U-0    | U-0 | U-0 | U-0 | r-0 | r-0 | r-0 | r-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-1          | R/W-0 | R/W-0 | R/W-1 | R/W-0 | R/W-1 | R/W-1 | R/W-0 |  |

|----------------|-------|-------|-------|-------|-------|-------|-------|--|

| APLLFBDIV<7:0> |       |       |       |       |       |       |       |  |

| bit 7 bit      |       |       |       |       |       |       |       |  |

| Legend:           | r = Reserved bit |                        |                                    |  |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |  |

**Note 1:** The allowed range is 16-200 (decimal). The rest of the values are reserved and should be avoided. The power-on default feedback divider is 150 (decimal) with an 8 MHz FRC input clock; the VCO frequency is 1.2 GHz.

#### Register 4-8: APLLDIV1: APLL Output Divider Register

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0        | R/W-0 |

|--------|-----|-----|-----|-----|-----|--------------|-------|

| _      | _   | _   | _   | _   | _   | AVCODIV<1:0> |       |

| bit 15 |     |     |     |     |     |              | bit 8 |

| U-0   | R/W-1               | R/W-0 | R/W-0 | U-0 | R/W-0               | R/W-0 | R/W-1 |  |

|-------|---------------------|-------|-------|-----|---------------------|-------|-------|--|

| _     | APOST1DIV<2:0>(1,2) |       |       | _   | APOST2DIV<2:0>(1,2) |       |       |  |

| bit 7 |                     |       |       |     |                     |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-10 **Unimplemented:** Read as '0'

bit 9-8 AVCODIV<1:0>: APLL VCO Output Divider Select bits

11 = VCO clock 10 = VCO/2 clock 01 = VCO/3 clock

00 = VCO/4 clock bit 7 **Unimplemented:** Read as '0'

bit 6-4 **APOST1DIV<2:0>:** APLL Output Divider #1 Ratio bits<sup>(1,2)</sup>

APOST1DIV<2:0> bits can have a valid value from 1 to 7 (the APOST1DIVx value should be greater than or equal to the APOST2DIVx value). The APOST1DIVx divider is designed to operate at higher clock rates than the APOST2DIVx divider.

bit 3 Unimplemented: Read as '0'

bit 2-0 APOST2DIV<2:0>: APLL Output Divider #2 Ratio bits<sup>(1,2)</sup>

APOST2DIV<2:0> bits can have a valid value from 1 to 7 (the APOST2DIVx value should be less than or equal to the APOST1DIVx value). The APOST1DIVx divider is designed to operate at higher clock rates than the APOST2DIVx divider.

Note 1: The APOST1DIVx and APOST2DIVx values must not be changed while the PLL is operating.

2: The default values for APOST1DIVx and APOST2DIVx are 4 and 1, respectively, yielding a 150 MHz Master APLL output.

### Register 4-9: CANCLKCON: CAN Clock Control Register (4)

| R/W-0    | U-0 | U-0 | U-0 | R/W-0 | R/W-0   | R/W-0                  | R/W-0 |

|----------|-----|-----|-----|-------|---------|------------------------|-------|

| CANCLKEN | _   | _   | _   |       | CANCLKS | EL<3:0> <sup>(1)</sup> |       |

| bit 15   |     |     |     |       |         |                        | bit 8 |

| U-0   | R/W-0 | R/W-0               | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-1 |  |  |  |

|-------|-------|---------------------|-------|-------|-------|-------|-------|--|--|--|

|       |       | CANCLKDIV<6:0>(2,3) |       |       |       |       |       |  |  |  |

| bit 7 |       |                     |       |       |       |       | bit 0 |  |  |  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

```

bit 15

CANCLKEN: Enables the CAN Clock Generator

1 = CAN clock generation circuitry is enabled

0 = CAN clock generation circuitry is disabled

bit 14-12

Unimplemented: Read as '0'

CANCLKSEL<3:0>: CAN Clock Source Select bits<sup>(1)</sup>

bit 11-8

1011-1111 = Reserved (no clock selected)

1010 = AFvco/4

1001 = AFvco/3

1000 = AFvco/2

0111 = AFVCO

0110 = AFPLLO

0101 = Fvco/4

0100 = Fvco/3

0011 = Fvco/2

0010 = FPLLO

0001 = Fvco

0000 = 0 (no clock selected)

bit 7

Unimplemented: Read as '0'

CANCLKDIV<6:0>: CAN Clock Divider Select bits(2,3)

bit 6-0

1111111 = Divide-by-128

0000010 = Divide-by-3

0000001 = Divide-by-2

0000000 = Divide-by-1

```

- Note 1: The user must ensure the input clock source is 640 MHz or less.

- 2: The CANCLKDIVx divider value must not be changed during CAN module operation.

- 3: The user must ensure the maximum clock output frequency of the divider is 80 MHz or less.

- **4:** CAN is not implemented in all devices. Refer to the device-specific data sheet to check if CAN is included in your device.

#### Register 4-10: REFOCONL: Reference Clock Control Low Register

| R/W-0  | U-0 | R/W-0  | R/W-0 | R/W-0 | U-0 | R/W-0, HC | R-0, HSC |

|--------|-----|--------|-------|-------|-----|-----------|----------|

| ROEN   | _   | ROSIDL | ROOUT | ROSLP | _   | ROSWEN    | ROACTIV  |

| bit 15 |     |        |       |       |     |           | bit 8    |

| U-0   | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|-----|--------|--------|--------|--------|

| _     | _   | _   | _   | ROSEL3 | ROSEL2 | ROSEL1 | ROSEL0 |

| bit 7 |     |     |     |        |        |        | bit 0  |

| Legend:           | HC = Hardware Clearable bit | rable bit HSC = Hardware Settable/Clearable bit |                    |  |

|-------------------|-----------------------------|-------------------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0'              |                    |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared                            | x = Bit is unknown |  |

bit 15 ROEN: Reference Clock Enable bit

1 = Reference Oscillator is enabled on the REFO pin

0 = Reference Oscillator is disabled

bit 14 Unimplemented: Read as '0'

bit 13 ROSIDL: Reference Clock Stop in Idle bit

1 = Reference Oscillator is disabled in Idle mode

0 = Reference Oscillator continues to run in Idle mode

bit 12 ROOUT: Reference Clock Output Enable bit

1 = Reference Clock external output is enabled and available on the REFO pin

0 = Reference Clock external output is disabled

bit 11 ROSLP: Reference Clock Stop in Sleep bit

1 = Reference Oscillator continues to run in Sleep modes

0 = Reference Oscillator is disabled in Sleep modes

bit 10 **Unimplemented:** Read as '0'

bit 9 ROSWEN: Reference Clock Output Enable bit

1 = Clock divider change is requested or is in progress (set in software, cleared by hardware upon completion)

0 = Clock divider change has completed or is not pending

bit 8 ROACTIV: Reference Clock Status bit

1 = Reference Clock is active; do not change clock source

0 = Reference Clock is stopped; clock source and configuration may be safely changed

bit 7-4 **Unimplemented:** Read as '0'

bit 3-0 ROSEL<3:0>: Reference Clock Source Select bits

1111 = Reserved

··· = Reserved

1000 = Reserved

0111 = REFI pin

0110 = Fvco/4

0101 = BFRC

0100 = LPRC

0011 **= FRC**

0010 = Primary Oscillator

0001 = Fosc/2 (FP)

0000 = Fosc

#### Register 4-11: REFOCONH: Reference Clock Control High Register

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------------|-------|-------|-------|

| _      |       |       |       | RODIV<14:8> | •     |       |       |

| bit 15 |       |       |       |             |       |       | bit 8 |

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| RODIV<7:0> |       |       |       |       |       |       |       |  |  |

| bit 7      |       |       |       |       |       |       |       |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-0 RODIV<14:0>: Reference Clock Integer Divider Select bits

Divider for the selected input clock source is two times the selected value.

111 1111 1111 1111 = Base clock value divided by 65,534 (2 \* 7FFFh)

111 1111 1111 1110 = Base clock value divided by 65,532 (2 \* 7FFEh)

111 1111 1111 1101 = Base clock value divided by 65,530 (2 \* 7FFDh)

• • •

000 0000 0000 0010 = Base clock value divided by 4 (2 \* 2)

000 0000 0000 0001 = Base clock value divided by 2 (2 \* 1)

000 0000 0000 0000 = Base clock value

### 4.2 Slave Special Function Registers

These Special Function Registers provide run-time control and status of the Slave core's oscillator system:

OSCCON: Oscillator Control Register<sup>(1)</sup>

This register controls clock switching and provides status information that allows the current clock source, PLL lock and clock fail conditions to be monitored.

· CLKDIV: Clock Divider Register

This register controls the Doze mode, FRC divider and PLL prescaler.

PLLFBD: PLL Feedback Divider Register

This register selects the PLL feedback divider.

• PLLDIV: PLL Output Divider Register

This register controls the VCO divider and both PLL post-dividers.

ACLKCON1: Auxiliary Clock Control Register

This register is used to configure and enable the Auxiliary PLL. APLL clock source selection, APLL prescaler setting and APLL lock status are all contained in this register.

APLLFBD1: APLL Feedback Divider Register

This register controls the APLL feedback divider.

APLLDIV1: APLL Output Divider Register

This register controls the AVCO divider and both APLL post-dividers.

• REFOCONL: Reference Clock Control Low Register

This register is used to configure and enable the Reference Clock output.

REFOCONH: Reference Clock Control High Register

This register controls the Reference Clock output divider selection.

### Register 4-12: OSCCON: Oscillator Control Register<sup>(1)</sup>

| U-0    | R-0   | R-0   | R-0   | U-0 | R/W-y                | R/W-y                | R/W-y                |

|--------|-------|-------|-------|-----|----------------------|----------------------|----------------------|

| _      | COSC2 | COSC1 | COSC0 | _   | NOSC2 <sup>(2)</sup> | NOSC1 <sup>(2)</sup> | NOSC0 <sup>(2)</sup> |

| bit 15 |       |       |       |     |                      |                      | bit 8                |

| R/W-0   | U-0 | R-0  | U-0 | R/W-0             | U-0 | U-0 | R/W-0 |

|---------|-----|------|-----|-------------------|-----|-----|-------|

| CLKLOCK | _   | LOCK | _   | CF <sup>(3)</sup> | _   | _   | OSWEN |

| bit 7   |     |      |     |                   |     |     | bit 0 |

Legend:y = Value Set from Configuration bits on PORR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-12 COSC<2:0>: Current Oscillator Selection bits (read-only)

111 = Fast RC Oscillator (FRC) with Divide-by-N (FRCDIVN)

110 = Backup FRC Oscillator (BFRC)

101 = Low-Power RC Oscillator (LPRC)

100 = Reserved

011 = Primary Oscillator (XT, HS, EC) with PLL (XTPLL, HSPLL, ECPLL)

010 = Primary Oscillator (XT, HS, EC)

001 = Fast RC Oscillator (FRC) with PLL (FRCPLL)

000 = Fast RC Oscillator (FRC)

bit 11 **Unimplemented:** Read as '0'

bit 10-8 NOSC<2:0>: New Oscillator Selection bits<sup>(2)</sup>

111 = Fast RC Oscillator (FRC) with Divide-by-N (FRCDIVN)

110 = Backup FRC Oscillator (BFRC)

101 = Low-Power RC Oscillator (LPRC)

100 = Reserved

011 = Primary Oscillator (XT, HS, EC) with PLL (XTPLL, HSPLL, ECPLL)

010 = Primary Oscillator (XT, HS, EC)

001 = Fast RC Oscillator (FRC) with PLL (FRCPLL)

000 = Fast RC Oscillator (FRC)

bit 7 CLKLOCK: Clock Lock Enable bit

1 = If (FCKSM0 = 1), then clock and PLL configurations are locked; if (FCKSM0 = 0), then clock and PLL configurations may be modified

0 = Clock and PLL selections are not locked, configurations may be modified

bit 6 Unimplemented: Read as '0'

bit 5 LOCK: PLL Lock Status bit (read-only)

1 = Indicates that PLL is in lock or PLL start-up timer is satisfied

0 = Indicates that PLL is out of lock, start-up timer is in progress or PLL is disabled

bit 4 Unimplemented: Read as '0'

bit 3 **CF:** Clock Fail Detect bit<sup>(3)</sup>

1 = FSCM has detected a clock failure

0 = FSCM has not detected a clock failure

Note 1: Writes to this register require an unlock sequence.

2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

3: This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and will trigger an oscillator failure trap.

### Register 4-12: OSCCON: Oscillator Control Register<sup>(1)</sup> (Continued)

bit 2-1 Unimplemented: Read as '0'

bit 0 **OSWEN:** Oscillator Switch Enable bit

1 = Requests oscillator switch to the selection specified by the NOSC<2:0> bits

0 = Oscillator switch is complete

**Note 1:** Writes to this register require an unlock sequence.

- 2: Direct clock switches between any Primary Oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- 3: This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and will trigger an oscillator failure trap.

#### Register 4-13: CLKDIV: Clock Divider Register

| R/W-0  | R/W-0                | R/W-1                | R/W-1                | R/W-0                  | R/W-0   | R/W-0   | R/W-0   |

|--------|----------------------|----------------------|----------------------|------------------------|---------|---------|---------|

| ROI    | DOZE2 <sup>(1)</sup> | DOZE1 <sup>(1)</sup> | DOZE0 <sup>(1)</sup> | DOZEN <sup>(2,3)</sup> | FRCDIV2 | FRCDIV1 | FRCDIV0 |

| bit 15 | •                    |                      |                      |                        |         |         | bit 8   |

| U-0   | U-0 | r-0 | r-0 | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-------|-----|-----|-----|------------------------|------------------------|------------------------|------------------------|

| _     | _   | _   | _   | PLLPRE3 <sup>(4)</sup> | PLLPRE2 <sup>(4)</sup> | PLLPRE1 <sup>(4)</sup> | PLLPRE0 <sup>(4)</sup> |

| bit 7 |     |     |     |                        |                        |                        | bit 0                  |

| Legend:           | r = Reserved bit |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

- bit 15 ROI: Recover on Interrupt bit

- 1 = Interrupts will clear the DOZEN bit and the processor clock, and the peripheral clock ratio is set to 1:1

- 0 = Interrupts have no effect on the DOZEN bit

- bit 14-12 **DOZE<2:0>:** Processor Clock Reduction Select bits<sup>(1)</sup>

- 111 = Fcy divided by 128

- 110 = FcY divided by 64

- 101 = Fcy divided by 32

- 100 = Fcy divided by 16

- 011 = Fcy divided by 8 (default)

- 010 = Fcy divided by 4

- 001 = Fcy divided by 2

- 000 = Fcy divided by 1

- bit 11 **DOZEN:** Doze Mode Enable bit<sup>(2,3)</sup>

- 1 = DOZE<2:0> bits field specifies the ratio between the peripheral clocks and the processor clocks

- 0 = Processor clock and peripheral clock ratio is forced to 1:1

- bit 10-8 FRCDIV<2:0>: Internal Fast RC Oscillator Postscaler bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2

- 000 = FRC divided by 1 (default)

- bit 7-6 **Unimplemented:** Read as '0'

- bit 5-4 **Reserved:** Read as '0'

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- 2: This bit is cleared when the ROI bit is set and an interrupt occurs.

- 3: The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

- 4: PLLPRE<3:0> may be updated while the PLL is operating, but the VCO may overshoot.

#### Register 4-13: CLKDIV: Clock Divider Register (Continued)

```

bit 3-0

PLLPRE<3:0>: PLL Phase Detector Input Divider Select bits (also denoted as 'N1', PLL prescaler)

1111 = Reserved

1001 = Reserved

1000 = Input divided by 8

0111 = Input divided by 7

0110 = Input divided by 6

0101 = Input divided by 5

0100 = Input divided by 4

0011 = Input divided by 3

0010 = Input divided by 2

0001 = Input divided by 1 (power-on default selection)

0000 = Invalid selection

```

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- 2: This bit is cleared when the ROI bit is set and an interrupt occurs.

- 3: The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

- 4: PLLPRE<3:0> may be updated while the PLL is operating, but the VCO may overshoot.

### Register 4-14: PLLFBD: PLL Feedback Divider Register

| U-0    | U-0 | U-0 | U-0 | r-0 | r-0 | r-0 | r-0 |

|--------|-----|-----|-----|-----|-----|-----|-----|

| _      | _   | _   | _   | _   | _   | _   | _   |

| bit 15 |     |     |     |     |     |     |     |

| R/W-1         | R/W-0 | R/W-0 | R/W-1 | R/W-0 | R/W-1 | R/W-1 | R/W-0 |

|---------------|-------|-------|-------|-------|-------|-------|-------|

| PLLFBDIV<7:0> |       |       |       |       |       |       |       |

| bit 7         |       |       |       |       |       |       | bit 0 |

| Legend:           | r = Reserved bit |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

Note 1: The allowed range is 16-200 (decimal). The rest of the values are reserved and should be avoided. The power on the default feedback divider is 150 (decimal) with an 8 MHz FRC input clock. The VCO frequency is 1.2 GHz.

#### Register 4-15: PLLDIV: PLL Output Divider Register

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0       | R/W-0 |

|--------|-----|-----|-----|-----|-----|-------------|-------|

| _      | _   | _   | _   | _   | _   | VCODIV<1:0> |       |

| bit 15 |     |     |     |     |     | bit 8       |       |

| U-0   | R/W-1                          | R/W-0 | R/W-0 | U-0 | R/W-0              | R/W-0 | R/W-1 |

|-------|--------------------------------|-------|-------|-----|--------------------|-------|-------|

| _     | POST1DIV<2:0> <sup>(1,2)</sup> |       |       | _   | POST2DIV<2:0>(1,2) |       |       |

| bit 7 |                                |       |       |     |                    |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-10 **Unimplemented:** Read as '0'

bit 9-8 VCODIV<1:0>: PLL VCO Output Divider Select bits

11 = VCO clock 10 = VCO/2 clock 01 = VCO/3 clock 00 = VCO/4 clock

bit 7 **Unimplemented:** Read as '0'

bit 6-4 **POST1DIV<2:0>:** PLL Output Divider #1 Ratio bits<sup>(1,2)</sup>

POST1DIV<2:0> bits can have a valid value from 1 to 7 (POST1DIVx value should be greater than or equal to the POST2DIVx value). The POST1DIVx divider is designed to operate at higher clock rates

than the POST2DIVx divider.

bit 3 Unimplemented: Read as '0'

bit 2-0 **POST2DIV<2:0>:** PLL Output Divider #2 Ratio bits<sup>(1,2)</sup>

POST2DIV<2:0> bits can have a valid value from 1 to 7 (POST2DIVx value should be less than or equal to the POST1DIVx value). The POST1DIVx divider is designed to operate at higher clock rates

than the POST2DIVx divider.

Note 1: The POST1DIVx and POST2DIVx divider values must not be changed while the PLL is operating.

2: The default values for POST1DIVx and POST2DIVx are 4 and 1, respectively, yielding a 150 MHz Slave PLL output.

#### Register 4-16: ACLKCON1: Auxiliary Clock Control Register

| R/W-0                 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|-----------------------|--------|-----|-----|-----|-----|-----|--------|

| APLLEN <sup>(1)</sup> | APLLCK | _   | _   | _   | _   | _   | FRCSEL |

| bit 15                |        |     |     |     |     |     |        |

| U-0   | U-0 | r-0 | r-0 | R/W-0    | R/W-0    | R/W-0    | R/W-1    |

|-------|-----|-----|-----|----------|----------|----------|----------|

| _     | _   | _   | _   | APLLPRE3 | APLLPRE2 | APLLPRE1 | APLLPRE0 |

| bit 7 |     |     |     |          |          |          | bit 0    |

| Legend:           | r = Reserved bit |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15 APLLEN: Auxiliary PLL Enable/Bypass Select bit (1)

1 = AFPLLO is connected to the APLL post-divider output (bypass disabled)

0 = AFPLLO is connected to the APLL input clock (bypass enabled)

bit 14 APLLCK: APLL Phase-Locked State Status bit

1 = Auxiliary PLL is in lock0 = Auxiliary PLL is not in lock

bit 13-9 Unimplemented: Read as '0'

bit 8 FRCSEL: FRC Clock Source Select bit

1 = FRC is the clock source for APLL

0 = Primary Oscillator is the clock source for APLL

bit 7-6 **Unimplemented:** Read as '0'

bit 5-4 Reserved: Read as '0'

bit 3-0 APLLPRE<3:0>: Auxiliary PLL Phase Detector Input Divider bits

1111 = Reserved

• • •

1001 = Reserved

1000 = Input divided by 8

0111 = Input divided by 7

0110 = Input divided by 6

0101 = Input divided by 5

0100 = Input divided by 4

0011 = Input divided by 3

0010 = Input divided by 2

0001 = Input divided by 1 (power-on default selection)

0000 = Invalid selection

Note 1: Even with the APLLEN bit set, another peripheral must generate a clock request before the APLL will start.

### Register 4-17: APLLFBD1: APLL Feedback Divider Register

| U-0        | U-0 | U-0 | U-0 | r-0 | r-0 | r-0 | r-0 |  |

|------------|-----|-----|-----|-----|-----|-----|-----|--|

| _          | _   | _   | _   | _   | _   | _   | _   |  |

| bit 15 bit |     |     |     |     |     |     |     |  |

| R/W-1          | R/W-0 | R/W-0 | R/W-1 | R/W-0 | R/W-1 | R/W-1 | R/W-0 |  |

|----------------|-------|-------|-------|-------|-------|-------|-------|--|

| APLLFBDIV<7:0> |       |       |       |       |       |       |       |  |

| bit 7          |       |       |       |       |       |       | bit 0 |  |

Legend:r = Reserved bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-12 **Unimplemented:** Read as '0'

bit 11-8 **Reserved:** Read as '0'

bit 7-0 APLLFBDIV<7:0>: APLL Feedback Divider bits

11111111 = Reserved

• • •

11001000 = 200 Maximum<sup>(1)</sup>

. . .

10010110 = **150** (Default)

. . .

00010000 = 16 Minimum<sup>(1)</sup>

• • •

00000010 = Reserved

00000001 = Reserved

00000000 = Reserved

**Note 1:** The allowed range is 16-200 (decimal). The rest of the values are reserved and should be avoided. The power on the default feedback divider is 150 (decimal) with an 8 MHz FRC input clock; the VCO frequency is 1.2 GHz.

#### Register 4-18: APLLDIV1: APLL Output Divider Register

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0        | R/W-0 |

|--------|-----|-----|-----|-----|-----|--------------|-------|

| _      | _   | _   | _   | _   | _   | AVCODIV<1:0> |       |

| bit 15 |     |     |     |     |     |              | bit 8 |

| U-0   | R/W-1                           | R/W-0 | R/W-0 | U-0 | R/W-0                           | R/W-0 | R/W-1 |  |

|-------|---------------------------------|-------|-------|-----|---------------------------------|-------|-------|--|

| _     | APOST1DIV<2:0> <sup>(1,2)</sup> |       |       | _   | APOST2DIV<2:0> <sup>(1,2)</sup> |       |       |  |

| bit 7 | _                               |       | _     |     | _                               | _     | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-10 Unimplemented: Read as '0'

bit 9-8 AVCODIV<1:0>: APLL VCO Output Divider Select bits

11 = VCO clock 10 = VCO/2 clock 01 = VCO/3clock 00 = VCO/4 clock

bit 7 **Unimplemented:** Read as '0'

bit 6-4 APOST1DIV<2:0>: APLL Output Divider #1 Ratio bits<sup>(1,2)</sup>

APOST1DIV<2:0> bits can have a valid value from 1 to 7 (the APOST1DIVx value should be greater than or equal to the APOST2DIVx value). The APOST1DIVx divider is designed to operate at higher clock rates than the APOST2DIVx divider.

bit 3 Unimplemented: Read as '0'

bit 2-0 APOST2DIV<2:0>: APLL Output Divider #2 Ratio bits<sup>(1,2)</sup>

APOST2DIV<2:0> bits can have a valid value from 1 to 7 (the APOST2DIVx value should be less than or equal to the APOST1DIVx value). The APOST1DIVx divider is designed to operate at higher clock rates than the APOST2DIVx divider.

Note 1: The APOST1DIVx and APOST2DIVx divider values must not be changed while the PLL is operating.

2: The default values for APOST1DIVx and APOST2DIVx are 4 and 1, respectively, yielding a 150 MHz Slave APLL output.

#### Register 4-19: REFOCONL: Reference Clock Control Low Register

| R/W-0  | U-0 | R/W-0  | R/W-0 | R/W-0 | U-0 | R/W-0, HC | R-0, HSC |

|--------|-----|--------|-------|-------|-----|-----------|----------|

| ROEN   | _   | ROSIDL | ROOUT | ROSLP | _   | ROSWEN    | ROACTIV  |

| bit 15 |     |        |       |       |     |           | bit 8    |

| U-0   | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|-----|--------|--------|--------|--------|

| _     | _   | _   | _   | ROSEL3 | ROSEL2 | ROSEL1 | ROSEL0 |

| bit 7 |     |     |     |        |        |        | bit 0  |

| Legend: HC = Hardware Clearable bit |                  | HSC = Hardware Settable/Clearable bit |                    |  |

|-------------------------------------|------------------|---------------------------------------|--------------------|--|

| R = Readable bit                    | W = Writable bit | U = Unimplemented bit, re             | ead as '0'         |  |

| -n = Value at POR                   | '1' = Bit is set | '0' = Bit is cleared                  | x = Bit is unknown |  |

bit 15 ROEN: Reference Clock Enable bit

1 = Reference Oscillator is enabled on the REFO pin

0 = Reference Oscillator is disabled

bit 14 Unimplemented: Read as '0'

bit 13 ROSIDL: Reference Clock Stop in Idle bit

1 = Reference Oscillator is disabled in Idle mode

0 = Reference Oscillator continues to run in Idle mode

bit 12 ROOUT: Reference Clock Output Enable bit

1 = Reference Clock external output is enabled and available on the REFO pin

0 = Reference Clock external output is disabled

bit 11 ROSLP: Reference Clock Stop in Sleep bit

1 = Reference Oscillator continues to run in Sleep modes

0 = Reference Oscillator is disabled in Sleep modes

bit 10 **Unimplemented:** Read as '0'

bit 9 ROSWEN: Reference Clock Output Enable bit

1 = Clock divider change is requested or is in progress (set in software, cleared by hardware upon completion)

0 = Clock divider change has completed or is not pending

bit 8 ROACTIV: Reference Clock Status bit

1 = Reference Clock is active; do not change clock source

0 = Reference Clock is stopped; clock source and configuration may be safely changed

bit 7-4 **Unimplemented:** Read as '0'

bit 3-0 ROSEL<3:0>: Reference Clock Source Select bits

1111 = Reserved

· · · = Reserved

1000 = Reserved

0111 = **REFI** pin

0110 = Fvco/4

0101 = BFRC Oscillator

0100 = LPRC Oscillator

0011 = FRC Oscillator

0010 = Primary Oscillator

0001 = Fosc/2 (FP)

0000 = Fosc

#### Register 4-20: **REFOCONH: Reference Clock Control High Register**

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------------|-------|-------|-------|

| _      |       |       |       | RODIV<14:8> | •     |       |       |

| bit 15 |       |       |       |             |       |       | bit 8 |

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|------------|-------|-------|-------|-------|-------|-------|-------|

| RODIV<7:0> |       |       |       |       |       |       |       |

| bit 7      |       |       |       |       |       | bit 0 |       |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15 Unimplemented: Read as '0'

bit 14-0 RODIV<14:0>: Reference Clock Integer Divider Select bits

Divider for the selected input clock source is two times the selected value.

111 1111 1111 = Base clock value divided by 65,534 (2 \* 7FFFh) 111 1111 1111 1110 = Base clock value divided by 65,532 (2 \* 7FFEh)

111 1111 1111 1101 = Base clock value divided by 65,530 (2 \* 7FFDh)

000 0000 0000 0010 = Base clock value divided by 4 (2 \* 2)

000 0000 0000 0001 = Base clock value divided by 2 (2 \* 1)

000 0000 0000 0000 = Base clock value

### 5.0 PRIMARY OSCILLATOR (POSC)

The dsPIC33/PIC24 devices contain one instance of the Primary Oscillator (POSC), which is available to both the Master and Slave clock subsystems. The Primary Oscillator is available on the OSC1 and OSC2 pins of the dsPIC33/PIC24 devices. This connection enables an external crystal (or ceramic resonator) to provide the clock to the device. The Primary Oscillator provides three modes of operation:

### Medium Speed Oscillator (XT Mode)

The XT mode is a Medium Gain, Medium Frequency mode used to work with crystal frequencies of 3.5 MHz to 10 MHz.

#### • High-Speed Oscillator (HS Mode)

- The HS mode is a High Gain, High-Frequency mode used to work with crystal frequencies of 10 MHz to 32 MHz.

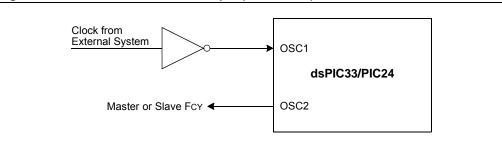

### • External Clock Source Operation (EC Mode)

If the on-chip oscillator is not used, the EC mode allows the internal oscillator to be bypassed. The device clocks are generated from an external source (from 0 MHz to up to 64 MHz) and input on the OSC1 pin.

The FNOSC<2:0> and S1FNOSC<2:0> Configuration bits in the Master and Slave Oscillator Source Selection registers (FOSCSEL<2:0>, FS1OSCSEL<2:0>) specify the system clock source at Power-on Reset.

The POSCMD<1:0> Configuration bits in the Oscillator Configuration register (FOSC<1:0>) specify the Primary Oscillator mode. Table 5-1 provides the options selected by specific bit configurations, which are programmed at the time of device programming.

Table 5-1: Primary Oscillator Clock Source Options

| FNOSC<2:0><br>S1FNOSC<2:0><br>Value | POSCMD<1:0><br>Value | Primary Oscillator Source and Mode                         |

|-------------------------------------|----------------------|------------------------------------------------------------|

| 010                                 | 00                   | Primary Oscillator: External Clock Mode (EC)               |

| 010                                 | 01                   | Primary Oscillator: Medium Frequency Mode (XT)             |

| 010                                 | 10                   | Primary Oscillator: High-Frequency Mode (HS)               |

| 011                                 | 00                   | Primary Oscillator with PLL: External Clock Mode (ECPLL)   |

| 011                                 | 01                   | Primary Oscillator with PLL: Medium Frequency Mode (XTPLL) |

| 011                                 | 10                   | Primary Oscillator with PLL: High-Frequency Mode (HSPLL)   |

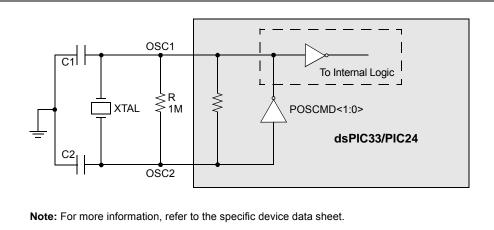

Figure 5-1 is a recommended crystal oscillator circuit diagram for the dsPIC33/PIC24 devices. Capacitors, C1 and C2, form the Load Capacitance (CL) for the crystal. The optimum Load Capacitance for a given crystal is specified by the crystal manufacturer. Load Capacitance can be calculated as shown in Equation 5-1.

Figure 5-1: Crystal or Ceramic Resonator Operation (XT or HS Oscillator Mode)

### Equation 5-1: Crystal Load Capacitance

$$CL = CS + \frac{C1 \times C2}{C1 + C2}$$

**Note:** Where *Cs* is the stray capacitance.

Assuming C1 = C2, Equation 5-2 gives the capacitor value (C1, C2) for a given load and stray capacitance.

Equation 5-2: External Capacitor for Crystal

$$C1 = C2 = 2 \times (CL - Cs)$$

For more information on crystal oscillators and their operation, refer to **Section 17.0 "Related Application Notes"**.

#### 5.1 **Oscillator Start-up Time**

As the device voltage increases from Vss, the oscillator will start its oscillations. The time required for the oscillator to start oscillating depends on these factors:

- Crystal and resonator frequency

- Capacitor values used (C1 and C2 in Figure 5-1)

- · Device VDD rise time

- · System temperature

- · Series resistor value and type if used

- Oscillator mode selection of device (selects the gain of the internal oscillator inverter)

- · Crystal quality

- Oscillator circuit layout

- · System noise

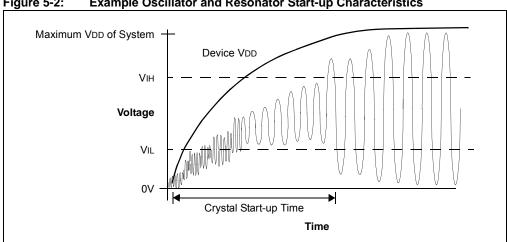

Figure 5-2 illustrates a plot of a typical oscillator and resonator start-up.

Figure 5-2: **Example Oscillator and Resonator Start-up Characteristics**

To ensure that a crystal oscillator (or ceramic resonator) has started and stabilized, an Oscillator Start-up Timer (OST) is provided with the Primary Oscillator (POSC). The OST is a simple, 10-bit counter that counts 1024 cycles before releasing the oscillator clock to the rest of the system. This time-out period is denoted as TOST.

The amplitude of the oscillator signal must reach the VIL and VIH thresholds for the oscillator pins before the OST can begin to count cycles. The TosT interval is required every time the oscillator restarts (that is, on POR, BOR and wake-up from Sleep mode) when XT or HS mode is selected in the Configuration Words. The Tost timer does not exist when EC mode is selected.

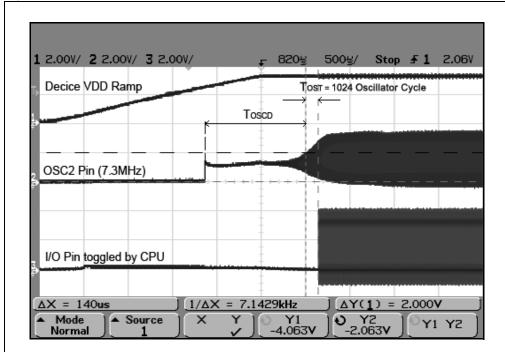

After the Primary Oscillator is enabled, it takes a finite amount of time to start oscillating. This delay is denoted as Tosco. After Tosco, the OST timer takes 1024 clock cycles (Tost) to release the clock. The total delay for the clock to be ready is: TOSCD + TOST. If the PLL is used, an additional delay is required for the PLL to lock. For more information, see Section 8.0 "Master Phase-Locked Loop (PLL)".

Primary Oscillator start-up behavior is illustrated in Figure 5-3, where the CPU begins toggling an I/O pin when it starts execution after the Tosco + Tost interval.

Figure 5-3: Oscillator Start-up Characteristics

### 5.2 Primary Oscillator Pin Functionality

The Primary Oscillator pins (OSC1 and OSC2) can be used for other functions when the oscillator is not being used. The POSCMD<1:0> Configuration bits in the Oscillator Configuration register (FOSC<1:0>) determine the oscillator pin function. The OSCIOFNC bit (FOSC<2>) determines the OSC2 pin function.

#### POSCMD<1:0>: Primary Oscillator Mode Selection bits:

- 11 = Primary Oscillator mode is disabled

- 10 = HS Oscillator mode is selected

- 01 = XT Oscillator mode is selected

- 00 = External Clock mode is selected

#### OSCIOFNC: OSC2 Pin Function bit (except in XT and HS modes):

- 1 = OSC2 is the clock output and the Master instruction cycle (Master FcY) clock is output on the OCS2 pin (see Figure 5-4)

- 0 = OSC2 is a general purpose digital I/O pin (see Figure 5-5)

#### S10SCIOFNC: OSC2 Pin Function bit (except in XT and HS modes):

- 1 = OSC2 is the clock output and the Slave instruction cycle (Slave FcY) clock is output on the OCS2 pin (see Figure 5-4)

- 0 = OSC2 is a general purpose digital I/O pin (see Figure 5-5)

The oscillator pin functions are provided in Table 5-2.

Table 5-2: Clock Pin Function Selection

| Oscillator Source              | OSCIOFNC<br>Value | S1OSCIOFNC<br>Value | POSCMD<1:0><br>Value | OSC1<br>Pin Function <sup>(1)</sup> | OSC2<br>Pin Function <sup>(2)</sup> |

|--------------------------------|-------------------|---------------------|----------------------|-------------------------------------|-------------------------------------|

| Primary Oscillator<br>Disabled | 1                 | х                   | 11                   | Digital I/O                         | Master Clock Output (FcY)           |

| Primary Oscillator<br>Disabled | 0                 | 1                   | 11                   | Digital I/O                         | Slave Clock Output<br>(Slave Fcy)   |

| Primary Oscillator<br>Disabled | 0                 | 0                   | 11                   | Digital I/O                         | Digital I/O                         |

| HS                             | х                 | х                   | 10                   | OSC1                                | OSC2                                |

| XT                             | х                 | х                   | 01                   | OSC1                                | OSC2                                |