# ENT-AN1276 Application Note VSC8489 Device Family Bring-up and Troubleshooting

September 2018

## **Contents**

| 1 | Revision F | History                               | 1  |

|---|------------|---------------------------------------|----|

|   | 1.1 Revis  | sion 1.0                              | 1  |

| 2 | Bring-up a | and Troubleshooting                   | 2  |

|   | 2.1 Regis  | ster Access                           | 2  |

|   | 2.2 PLL L  | Lock Status                           | 3  |

|   | 2.3 Gene   | eral Status Settings                  | 3  |

|   | 2.3.1      | 10G I/O Settings per Channel          |    |

|   | 2.3.2      | Line-Side 10G Input Registers for APC | 5  |

|   | 2.3.3      | XAUI/RXAUI I/O Settings Per Channel   | 6  |

|   | 2.3.4      | 1G Debugging                          | 7  |

|   | 2.4 Relat  | ted Registers                         | 8  |

|   | 2.4.1      | 10G Line Side                         | 8  |

|   | 2.4.2      | 1G Line Side                          | 9  |

|   | 2.4.3      | 10G Host Side                         | 11 |

|   | 2.4.4      | 1G Host Side                          | 15 |

|   | 2.4.5      | Miscellaneous                         | 17 |

|   | 2.5 Traci  | ing Faults                            | 17 |

|   | 2.6 Loop   | backs                                 | 18 |

|   | 2.6.1      | Facility Loopbacks                    | 18 |

|   | 2.6.2      | Equipment Loopbacks                   | 19 |

|   | 2.7 BIST   |                                       | 19 |

|   | 2.7.1      | Packet BIST                           | 20 |

|   | 2.7.2      | Non-Packet BIST                       | 24 |

|   | 2.8 VSco   | ppe                                   | 30 |

## 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

## **1.1** Revision **1.0**

Revision 1.0 was published in September 2018. It was the first publication of this document.

## 2 Bring-up and Troubleshooting

Use this information to bring up boards containing devices within the VSC8489 family (that also includes the VSC8490 and VSC8491), starting with the following checks.

- Check that the different power supplies have the correct voltage

- Check the frequency, amplitude, and jitter for the reference clocks

- Confirm that the input control pin states are stable and accurate (especially the MODE[1:0] pins)

- Confirm that the hardware reset duration is correct and that it occurs after the power supplies and reference clock inputs are stable

There are two amplitude settings for the clock inputs and each one requires a different register setting. After checking that the register accesses are correct, check line-side register 1Ex8208 (L\_PLL5G\_CFG4A) and host-side register 1Ex 8108 (H\_PLL5G\_CFG4A). Set bit 9 of both registers to 0 to select a larger reference clock swing input (from 1100 mV to 2400 mV) and set it to 1 to select a smaller swing input (from 200 mV to 1200 mV).

## 2.1 Register Access

Registers are accessible with a loosely defined clock frequency, and it is generally acceptable to configure the reference clock input amplitude register even if the starting register value and the actual clock input amplitude do not match.

Both 16-bit and 32-bit registers are accessed in the same way when using 32-bit SPI. However, if MDIO is used to access the registers, accessing 32-bit registers requires a specific sequence of 16-bit operations. In the case of a read operation, the MDIO read-increment command must be used (see Register Access Sequence).

To accommodate access to the 32-bit registers through 32-bit SPI and 16-bit MDIO, the addresses for the 32-bit registers are different when using SPI and MDIO. The API manages the differences if the management bus is ported correctly.

The global device 0x1E registers can only be accessed through the physical port 0 of the PHY. Read the chip ID through 1Ex0000, which should return 0x8489/0x8490/8491, depending on the PHY used. The version of the chip is then read back through 1Ex0001 to return the value 0x0000 for rev A/B and 0x0001 for rev C/D. To differentiate rev C and rev D die, please read the global\_spare\_cfg\_stat.spare\_rw1 register at 1Ex01d4. When the register= 1, it is revision D.

Use the registers listed in the following sections to check the status and I/O settings. The addresses given are for the 16-bit MDIO address scheme. If 32-bit SPI is used, addresses for some registers need to be adjusted.

Use the following access sequence under the given conditions for the listed registers.

**Table 1 • Register Access Sequence**

| 16-bit MDIO Read to 32-bit Register                                     | 16-bit MDIO Write to 32-bit Register            |

|-------------------------------------------------------------------------|-------------------------------------------------|

| Set up the lower 16-bit register address by MDIO ADDR                   | Set up the higher 16-bit register address by    |

|                                                                         | MDIO ADDR                                       |

| Read the lower 16-bit register content by MDIO READ INC                 | Write the higher 16-bit register content by     |

|                                                                         | MDIO WRITE                                      |

| The address for the higher 16-bit register will increment automatically | Set up the lower 16-bit register address by     |

| after the read                                                          | MDIO ADDR                                       |

| Read the higher 16-bit register content by regular MDIO READ            | Write the lower 16-bit register content by MDIO |

|                                                                         | WRITE                                           |

## 2.2 PLL Lock Status

When the PHY is powered up but does not pass traffic, use the following checks to ensure the different PLLs are up and running.

Table 2 • PLL Status Check

| PLL                         | Check                                                                                          |

|-----------------------------|------------------------------------------------------------------------------------------------|

| LineLCPLL                   | 1Ex8211.3:1 (6= locked, all others= unlocked)                                                  |

| HostLCPLL                   | 1Ex810E.3:1 (6= locked, all others= unlocked)                                                  |

| Host Rx RCPLL (per channel) | 4xE634 is for channel 0. 4xE63B, 4xE642, and 4xE649 are for channel 1, 2, and 3, respectively. |

| Chamery                     | Bit 12: Calibration. 0= Not complete, 1= Complete.                                             |

|                             | Bit 11: Calibration result. 0= Good, 1= Error.                                                 |

|                             | Bit 10: PLL range. 0= Good, 1= Error.                                                          |

|                             | A properly configured lane should read back bits 15:08 as 0x10.                                |

| Line Rx RCPLL (per channel) | 1xF268.3:0 being 0xd means locked, all others mean unlocked.                                   |

|                             | For 32-bit SPI, 1xF134.3:0                                                                     |

| Line Tx RCPLL (per channel) | 1xF2C8.3:0 (13= locked, all others= unlocked).                                                 |

|                             | For 32-bit SPI, 1xF164.3:0                                                                     |

When the PLLs are functional, program the RXCLKOUT or TXCLKOUT to generate a line rate/64 clock (161 MHz) and use a scope to measure if the frequency is correct.

Table 3 • PLL Accuracy Check

| RXCLKOUT                                                                                                                                           | TXCLKOUT                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Set 1xA000 to 0x0009 to generate a recovered clock from 10G data input in 161 MHz                                                                  | Set 1xA001 to 0x000b to generate a recovered clock from 10G data input in 161 MHz                                                                  |

| Set 1xA000 to 0x000b to generate a 161 MHz clock from the 10G Tx transmit clock, which is based on the internal PLL derived from the XREFCLK input | Set 1xA000 to 0x0009 to generate a 161 MHz clock from the 10G Tx transmit clock, which is based on the internal PLL derived from the XREFCLK input |

## 2.3 General Status Settings

If the PLLs are working correctly but the link is still down or there are CRC errors registered in the link partner, check the following PCS block and XAUI block registers to determine if the problem is at the PMA side or the XAUI side.

## Table 4 • PCS Block Status for 10G Rx Input

| Value  | Status                                                                                                                                                                                                                                                  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3x0008 | Bit 11 indicates Tx fault and bit 10 indicates Rx fault.                                                                                                                                                                                                |

|        | These two bits are latched bits. In order to get the current status, they should be read twice as the first read will clear the residual value and the second read will provide the current value. When these bits are high, it means there is a fault. |

|        | This bit is affected by register 3xE600.                                                                                                                                                                                                                |

|        | When 3xE600= 1, Rx fault depends on block lock (= 1) or high BER (= 1).                                                                                                                                                                                 |

|        | When 3xE600= 0, Rx fault depends on block lock= 1 only.                                                                                                                                                                                                 |

| 3x0021 | Bit 15 indicates block lock.                                                                                                                                                                                                                            |

|        | Bit 14 indicates high BER is reported.                                                                                                                                                                                                                  |

|        | Bit 13:8 is the BER counter.                                                                                                                                                                                                                            |

|        | Bit 7:0 are counts for error blocks (read to clear).                                                                                                                                                                                                    |

| 3x8010 | PCS_TX_Sequencing_Error_Count (read to clear)                                                                                                                                                                                                           |

| 3x8011 | PCS_RX_Sequencing_Error_Count (read to clear)                                                                                                                                                                                                           |

| 3x8012 | PCS_TX_Block_Encode_Error_Count (read to clear)                                                                                                                                                                                                         |

| 3x8013 | PCS_RX_Block_Decode_Error_Count (read to clear)                                                                                                                                                                                                         |

| 3x8014 | PCS_TX_Char_Encode_Error_Count (read to clear)                                                                                                                                                                                                          |

| 3x8015 | PCS_RX_Char_Decode_Error_Count (read to clear)                                                                                                                                                                                                          |

## Table 5 • XAUI Block Status for XAUI Input Data

| Value  | Status                                                                                                                                      |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------|

| 4x0008 | Bit 11 indicates Tx fault, which most likely is caused by the XAUI input.                                                                   |

|        | Bit 10 reflects similar information as in 3x0008.10 (latched bit, so read twice).                                                           |

| 4xF020 | Bit 12 indicates the current alignment status.                                                                                              |

|        | Bit 3:0 indicates the current sync status of lane 3, lane 2, lane 1, and lane 0, respectively.                                              |

| 4xF021 | Bit 4 indicates the current link status.                                                                                                    |

|        | Bit 3:0 indicates the current signal detection status of lane 3, lane 1, and lane 0, respectively.                                          |

| 4xF022 | This is a sticky register. Write 0xFFFF to clear the bits first.                                                                            |

|        | Bit 15:12 indicates sticky bit for local fault status for lane 3–lane 0.                                                                    |

|        | Bit 3:0 indicates change was detected on sync status change for lane 3–lane 0.                                                              |

|        | Other bit definitions are listed in the register descriptions that follow.                                                                  |

| 4xF023 | This is a sticky register. Write 0xFFFF to clear the bits first.                                                                            |

|        | Bit 4 indicates sticky bit for alignment lost for lane 3–lane 0.                                                                            |

|        | Bit 3:0 indicates change was detected on sync lost status for lane 3–lane 0.                                                                |

|        | Other bit definitions are listed in register descriptions that follow.                                                                      |

| 4xF026 | This register is read if 4xF023 bit 6 is 1 because this register being 1 means remote fault and 0 means local fault.                        |

| 4xF042 | In normal mode, Rx FIFO overflow error counter for the rate adaptation FIFO from 10G recovered clock domain to local XAUI Tx clock domain.  |

| 4xF043 | In normal mode, Rx FIFO underflow error counter for the rate adaptation FIFO from 10G recovered clock domain to local XAUI Tx clock domain. |

If the problem is on the line-side PMA input, check the APC at the 10G input data path and the KR output (d filter register) settings that control the 10G Tx output.

#### 2.3.1 10G I/O Settings per Channel

Adjust the KR output setting to compensate for line-side output channel loss on the PCB. The error detection is assumed at the link partner Rx status. So, by adjusting the KR output of the local VSC8489 family PHY, the link partner Rx status should be monitored to see if the CRC error count drops down to zero.

Attached is the spreadsheet for converting C-1, C0, and C+1 into a hex value put into the d-filter register controlling the 10G output. The address of the KR output setting (d\_filter register) is at 1xF225/1xF224 (bit 23:0) [1xF112 for SPI 32-bit address].

#### 2.3.2 Line-Side 10G Input Registers for APC

Use the following tips to troubleshoot line-side 10G issues.

- If 1xF001.19:16 is not at 0x8 and 1xF001.2:0 is not at 0x2, then the APC is not initialized properly.

Either the input reference clock is bad or there is some register programming issue (such as the wait state not implementing correctly) that results in insufficient wait. Check the PLL status to make sure the PLLs are locked.

- If there is no block lock or lots of block errors and bit errors, it could be a signal integrity issue and the APC parameters need to be checked thoroughly. Also, check if the Rx\_LOS is asserted. If any of the APC parameters do not seem correct, try resetting the APC by toggling 1xF001.11 (32-bit SPI address—MDIO address is 1xF002 bit 11) from 0x0 to 0x1 and back to 0x0 while 1xF001.10= 0 and 1xF001.9= 1.

- If there is no block lock at all, the link might be physically broken. Again, also check the Rx\_LOS from the optical transceiver.

- If there is block lock but lots of block errors only (that is, 3x0021 being 0x80FF), the link connection should be fine but the link partner is sending out traffic with error blocks. Check the link partner.

- If APC parameters are not in a good range and stay the same after executing APC\_reset, there could be a cable problem or layout issue.

- If APC parameters are in a good range but still have BER error or block lock issues, check if the

polarity of the signal is inverted.

**Table 6 • Line-Side 10G Input Registers**

| Control                    | Setting                                                                                                                                   |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Common config register     | 1xF003/1xF002 (bit 19:16 is expected to be 0x8, bit 11 to be 0, and 2:0 to be 2). [1xF001 for SPI 32-bit address]                         |

| L of input equalizer       | 1xF031/1xF030 (bit 25:16 is expected to have a ratio AGC:L:C to be 8:2:1 if media_type_SC is not used). [1xF016 for SPI 32-bit address]   |

| Offset of input equalizer  | 1xF025/1xF024 (bit 25:16 is expected to be around 0x200). [1xF010 for SPI 32-bit address]                                                 |

| C of input equalizer       | 1xF02B/1xF02A (bit 25:16 is expected to have a ratio AGC:L:C to be 8:2:1 if media_type_SC is not used). [1xF013 for SPI 32-bit address]   |

| AGC of input equalizer     | 1xF037/1xF036 (bit 25:16 is expected to have a ratio AGC:L:C to be 8:2:1 if media _type_SC is not used).  [1xF019 for SPI 32-bit address] |

| Gain of input<br>equalizer | 1xF019/1xF018 (bit 15:6—the actual gain is expected to be less than 0x2xx; bit 5:0 level detect set).  [1xF00C for SPI 32-bit address]    |

| DFE1 of input equalizer    | 1xF03D/1xF03C (bit 25:16 is expected to be around 0x40). [1xF01E for SPI 32-bit address]                                                  |

| Control                    | Setting                                                                                  |

|----------------------------|------------------------------------------------------------------------------------------|

| DFE2 of input equalizer    | 1xF043/1xF042 (bit 25:16 is expected to be around 0x20). [1xF021 for SPI 32-bit address] |

| DFE3 of input equalizer    | 1xF049/1xF048 (bit 25:16 is expected to be around 0x10). [1xF024 for SPI 32-bit address] |

| DFE4 of input<br>equalizer | 1xF04F/1xF04E (bit 25:16 is expected to be around 0x10). [1xF027 for SPI 32-bit address] |

#### 2.3.3 XAUI/RXAUI I/O Settings Per Channel

Use the following tips to troubleshoot XAUI/RXAUI I/O settings issues.

- If no amplitude signal is detected when 4xF021 is read back, there might not be signals coming from the MAC chip to the PHY.

- If there is no sync or no link but amplitude is detected when 4xF020 and 4xF021 are read back, there might be a signal integrity issue and the registers for the host PLL at 4xE634, 4xE63B, 4xE642, and 4xE649 should be checked. The polarity of the signal should be checked. The status of the high-pass gain, mid-pass gain, low-pass gain, and offset should be checked.

- Adjust the 4xE61A.9:8 among 00, 01, 10, 11 to see if there is any improvement on bit error rate. The

preset 0x0 for bit 9:8 is for regular trace length (within ~24" FR4 material). A higher value could be

used for longer trace length.

- If there is sync and link up but traffic cannot be passed through, then check if local fault or remote fault is received by checking the fault status at 4xF023 bit 6 is 1. If there is a fault, then read 4xF026 to see if it is 0x1 (remote fault) or 0x0 (local fault).

- Check the FIFO overflow/underflow at 4xF042/4xF043.

- If the error is seen at the MAC chip's Rx input, then try to adjust the pre-cursor, post-cursor, amplitude, slew rate, and so on of the XAUI/RXAUI output buffer to see if the bit error registered at MAC chip's Rx input is eliminated.

The host input buffer calibrated parameter status values should fall between the minimum and maximum values configured through the following registers.

**Table 7 ● Input Buffer Min/Max Values**

|      | High-Pass Gain | Mid-Pass Gain | Low-Pass Gain | Offset     |

|------|----------------|---------------|---------------|------------|

| Min. | 4xE623.13:8    | 4xE623.5:0    | 4xE624.13:8   | 4xE623.5:0 |

| Max. | 4xE621.13:8    | 4xE621.5:0    | 4xE622.13:8   | 4xE622.5:0 |

4xE61A.9:8 sets the pattern detection for offset. In general, 0 is good for all lengths (particularly for short trace). If longer trace is needed, set it to 2.

**Table 8 • Host Input Buffer Calibrated Parameter Status**

| Calibration           | Input Buffer High-Pass<br>Gain | Input Buffer Mid-Pass<br>Gain | Input Buffer Low-Pass<br>Gain | Input Buffer<br>Offset |

|-----------------------|--------------------------------|-------------------------------|-------------------------------|------------------------|

| 4xE630.8= 1<br>Lane 0 | 4xE631.13:8                    | 4xE631.5:0                    | 4xE632.13:8                   | 4xE632.5:0             |

| 4xE637.8= 1<br>Lane 1 | 4xE638.13:8                    | 4xE638.5:0                    | 4xE639.13:8                   | 4xE639.5:0             |

| 4xE63E.8= 1<br>Lane 2 | 4xE63F.13:8                    | 4xE63F.5:0                    | 4xE640.13:8                   | 4xE640.5:0             |

| 4xE645.8= 1<br>Lane 3 | 4xE646.13:8                    | 4xE646.5:0                    | 4xE647.13:8                   | 4xE647.5:0             |

## **Table 9 ● Host Output Buffer Calibrated Parameter Status**

| Setting      | Description                                                                        |

|--------------|------------------------------------------------------------------------------------|

| 4xE625.15= 1 | Squelch the XAUI/RXAUI outputs on all four lanes                                   |

| 4xE625.13= 1 | Invert the XAUI/RXAUI outputs' polarity on all four lanes                          |

| 4xE625.12:7  | Pre-cursor Pre-cursor                                                              |

| 4xE625.6:2   | Post-cursor                                                                        |

| 4xE626.15:11 | Second post-cursor                                                                 |

| 4xE626.8= 0  | Slew rate <60 ps                                                                   |

| 4xE626.8= 1  | Slew rate >60 ps                                                                   |

| 4xE626.7:4   | If 4xE626.8= 0: fine adjustment of slew with 30 ps to 60 ps                        |

|              | If 4xE626.8= 1, 60 ps to 140 ps                                                    |

| 4xE627.5:0   | Defines the XAUI/RXAUI output amplitude (with 0 being lowest and 63 being highest) |

## 2.3.4 1G Debugging

## **Table 10 ● 1G Host-Side Debugging**

| Register                    | Description                                                              |  |

|-----------------------------|--------------------------------------------------------------------------|--|

| 3xE002                      | Bit 8: 1= Signal detection enable                                        |  |

|                             | Bit 4: 1= Signal-detect pin is used to determine if a signal is detected |  |

| 3xE003                      | Bit 0: 1= Auto-negotiation enabled                                       |  |

|                             | Auto-negotiation should be disabled for host side.                       |  |

| 3xE00D Bit 8: Signal detect |                                                                          |  |

|                             | Bit 4: Link status                                                       |  |

|                             | Bit 0: Sync status                                                       |  |

|                             | <b>Note:</b> For a good link, these three bits should all be 1.          |  |

## Table 11 • 1G Line-Side Debugging

| Register | Description                                                                                                                                               |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3xE102   | Bit 8: 1= Signal detection enable                                                                                                                         |

|          | Bit 4: 1= Signal-detect pin is used to determine if a signal is detected                                                                                  |

| 3xE103   | Bit 0: 1= Auto-negotiation enabled                                                                                                                        |

| 3xE104   | Bit 5:4 has to be set to 0x2 if auto-negotiation is enabled.                                                                                              |

|          | For debugging simplicity, disable auto-negotiation at the PHY and at the module. When it works with autoneg, then try to add back the autoneg and retest. |

| 3xE10D   | Bit 8: Signal detect                                                                                                                                      |

|          | Bit 4: Link status                                                                                                                                        |

|          | Bit 0: Sync status                                                                                                                                        |

|          | Note: For a good link, these three bits should all be 1.                                                                                                  |

# 2.4 Related Registers

The following tables list the related registers.

## 2.4.1 10G Line Side

Read this register twice to get the latest status.

#### Table 12 • 3x0008.11:10

| Bit | Name           | Access | Description                                                                                                | Default |

|-----|----------------|--------|------------------------------------------------------------------------------------------------------------|---------|

| 11  | Transmit_fault | R/O    | This is a sticky bit that latches the high state. The latch-high bit is cleared when the register is read. | 0x0     |

|     |                |        | 0: No fault condition on transmit path                                                                     |         |

|     |                |        | 1: Fault condition on transmit path                                                                        |         |

| 10  | Receive_fault  | R/O    | This is a sticky bit that latches the high state. The latch-high bit is cleared when the register is read. | 0x0     |

|     |                |        | O: No fault condition on receive path 1: Fault condition on receive path                                   |         |

#### Table 13 • 3x0020

| Bit | Name                             | Access | Description                                                                                                                                                            | Default |

|-----|----------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 12  | is_10GBASE_R_receive_lock_status | R/O    | 0: 10GBASE-R PCS receive link down BLOCK_LOCK (3x0020.0)= 0 or BER_HI (3x0020.1)= 1 1: 10GBASE-R PCS receive link up BLOCK_LOCK (3x0020.0)= 1 and BER_HI (3x0020.1)= 0 | 0x0     |

| 1   | is_10GBASE_R_PCS_high_BER        | R/O    | 0: 10GBASE-R PCS not reporting a high BER<br>1: 10GBASE-R PCS reporting a high BER                                                                                     | 0x0     |

| 0   | is_10GBASE_R_PCS_block_lock      | R/O    | 0: 10GBASE-R PCS is not locked to receive blocks<br>1: 10GBASE-R PCS is locked to receive blocks                                                                       | 0x0     |

#### Table 14 • 3x0021

| Bit  | Name               | Access | Description                                                                                                                         | Default |

|------|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------|---------|

| 15   | BLOCK_LOCK         | R/O    | This is a sticky bit that latches the low state. The latch-low bit is cleared when the register is read.                            | 0x1     |

|      |                    |        | 0: 10GBASE-R PCS does not have block lock 1: 10GBASE-R PCS has block lock                                                           |         |

| 14   | PCS_HIGHBER        | R/O    | This is a sticky bit that latches the high state. The latch-high bit is cleared when the register is read.                          | 0x0     |

|      |                    |        | 0: 10GBASE-R PCS has not reported a high BER<br>1: 10GBASE-R PCS has reported a high BER                                            |         |

| 13:8 | BER                | R/O    | BER counter. The counter saturates when the maximum value is exceeded. The counter is cleared when the register is read.            | 0x00    |

| 7:0  | PCS_ERRORED_BLOCKS | R/O    | Errored blocks counter. The counter saturates when the maximum value is exceeded. The counter is cleared when the register is read. | 0x00    |

## **2.4.2 1G Line Side**

#### Table 15 • 3xE100

| Bit | Name             | Access | Description                                                                                                                                                              | Default |

|-----|------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 4   | LINK_STATUS_TYPE | R/W    | Set type of link_status indication at CPU system.  0: Sync_status (from PCS synchronization state machine)  1: Bit 15 of PCS1G_ANEG_STATUS.lp_adv_ability (Link up/down) | 0x0     |

| 1   | Reserved         | R/W    | Factory use                                                                                                                                                              | 0x0     |

| 0   | PCS_ENA          | R/W    | PCS enable. 0: Disable PCS 1: Enable PCS                                                                                                                                 | 0x0     |

#### Table 16 • 3xE101

| Bit | Name            | Access | Description                                                        | Default |

|-----|-----------------|--------|--------------------------------------------------------------------|---------|

| 4   | UNIDIR_MODE_ENA | R/W    | Unidirectional mode enable.                                        | 0x0     |

|     |                 |        | Implementation of 802.3, Clause 66. When asserted, this enables    |         |

|     |                 |        | MAC to transmit data independent of the state of the receive link. |         |

|     |                 |        | 0: Unidirectional mode disabled                                    |         |

|     |                 |        | 1: Unidirectional mode enabled                                     |         |

| 0   | SGMII_MODE_ENA  | R/w    | Selection of PCS operation.                                        | 0x1     |

|     |                 |        | 0: PCS is used in SerDes mode                                      |         |

|     |                 |        | 1: PCS is used in SGMII mode. Configuration bit PCS1G_ANEG_CFG.    |         |

|     |                 |        | SW_RESOLVE_ENA must be set additionally.                           |         |

#### Table 17 • 3xE102

| Bit | Name   | Access | Description                                                                                                           | Default |

|-----|--------|--------|-----------------------------------------------------------------------------------------------------------------------|---------|

| 8   | SD_SEL | R/W    | Signal-detect selection (select input for internal signal_detect line).                                               | 0x0     |

|     |        |        | 0: Select signal_detect line from hard macro                                                                          |         |

|     |        |        | 1: Select external signal_detect line                                                                                 |         |

| 4   | SD_POL | R/W    | Signal-detect polarity.                                                                                               | 0x1     |

|     |        |        | The signal level on signal_detect input pin must be equal to SD_POL to indicate signal detection (SD_ENA must be set) |         |

|     |        |        | 0: The signal-detect input pin must be "0" to indicate a signal detection                                             |         |

|     |        |        | 1: The signal-detect input pin must be "1" to indicate a signal detection                                             |         |

| 0   | SD_ENA | R/W    | Signal-detect enable.                                                                                                 | 0x1     |

|     |        |        | 0: The signal-detect input pin is ignored. The PCS assumes an active signal detect at all times.                      |         |

|     |        |        | 1: The signal-detect input pin is used to determine if a signal is detected                                           |         |

#### Table 18 • 3xE103

| Bit | Name                  | Access | Description                                                   | Default |

|-----|-----------------------|--------|---------------------------------------------------------------|---------|

| 8   | SW_RESOLVE_ENA        | R/W    | Software resolve abilities.                                   | 0x0     |

|     |                       |        | 0: If auto-negotiation fails (no matching HD or FD            |         |

|     |                       |        | capabilities), the link is disabled                           |         |

|     |                       |        | 1: The result of an auto-negotiation is ignored (the link can |         |

|     |                       |        | be set up through software). This bit must be set in SGMII    |         |

|     |                       |        | mode.                                                         |         |

| 1   | ANEG_RESTART_ONE_SHOT | One-   | Auto-negotiation restart.                                     | 0x0     |

|     |                       | shot   |                                                               |         |

|     |                       |        | 0: No action                                                  |         |

|     |                       |        | 1: Restart auto-negotiation                                   |         |

| 0   | ANEG_ENA              | R/W    | Auto-negotiation enable.                                      | 0x0     |

|     |                       |        | 0: Auto-negotiation disabled                                  |         |

|     |                       |        | 1: Auto-negotiation enabled                                   |         |

#### Table 19 • 3xE104

| Bit  | Name        | Access | Description                                                                               | Default |

|------|-------------|--------|-------------------------------------------------------------------------------------------|---------|

| 15:0 | ADV_ABILITY | R/W    | Advertised ability register.                                                              | 0x0000  |

|      |             |        | Holds the capabilities of the device as described IEEE 802.3, Clause 37.                  |         |

|      |             |        | If SGMII mode is selected (PCS1G_MODE_CFG.SGMII_MODE_ENA= 1), SW_RESOLVE_ENA must be set. |         |

#### **Table 20 • 3xE10D**

| Bit | Name          | Access | Description                                                                 | Default |

|-----|---------------|--------|-----------------------------------------------------------------------------|---------|

| 8   | SIGNAL_DETECT | R/O    | Indicates whether or not the selected signal detect input line is asserted. | 0x0     |

|     |               |        | 0: No signal detected                                                       |         |

|     |               |        | 1: Signal detected                                                          |         |

| 4   | LINK_STATUS   | R/O    | Indicates whether the link is up or down (a link is up when ANEG state      | 0x0     |

|     |               |        | machine is in state LINK_OK or AN_DISABLE_LINK_OK).                         |         |

|     |               |        | 0: Link down                                                                |         |

|     |               |        | 1: Link up                                                                  |         |

| 0   | SYNC_STATUS   | R/O    | Indicates if PCS has successfully synchronized.                             | 0x0     |

|     |               |        | 0: PCS is out of sync                                                       |         |

|     |               |        | 1: PCS has synchronized                                                     |         |

#### **Table 21 • 3xE10E**

| Bit | Name          | Access | Description                                                                                                                                              | Default |

|-----|---------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7:0 | LINK_DOWN_CNT | R/W    | Link down counter.                                                                                                                                       | 0x00    |

|     |               |        | A counter that counts the number of times a link has been down. The counter does not saturate at 255 and is only cleared when writing 0 to the register. |         |

#### **Table 22 • 3xE00F**

| Bit | Name               | Access | Description                                                                                                                                                                                                                                                        | Default |

|-----|--------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 4   | LINK_DOWN_STICKY   | Sticky | The sticky bit is set when the link has been down (that is, if the ANEG state machine has not been in the AN_DISABLE_LINK_OK or LINK_OK state for one or more clock cycles). This occurs if, for example, ANEG is restarted or if signal-detect or synchronization | 0x0     |

|     |                    |        | has been lost for more than 10 ms (1.6 ms in SGMII mode).                                                                                                                                                                                                          |         |

|     |                    |        | 0: Link is up                                                                                                                                                                                                                                                      |         |

|     |                    |        | 1: Link has been down                                                                                                                                                                                                                                              |         |

|     |                    |        | Bit is cleared by writing a 1 to this position.                                                                                                                                                                                                                    |         |

| 0   | OUT_OF_SYNC_STICKY | Sticky | Sticky bit indicating if PCS synchronization has been lost.                                                                                                                                                                                                        | 0x0     |

|     |                    |        | 0: Synchronization has not been lost at any time                                                                                                                                                                                                                   |         |

|     |                    |        | 1: Synchronization has been lost for one or more clock cycles                                                                                                                                                                                                      |         |

|     |                    |        | Bit is cleared by writing a 1 to this position.                                                                                                                                                                                                                    |         |

## 2.4.3 10G Host Side

#### Table 23 • 4xF020

| Bit | Name             | Access | Description                                                           | Default |

|-----|------------------|--------|-----------------------------------------------------------------------|---------|

| 12  | ALIGNMENT_STATUS | R/O    | Status of lane alignment.                                             | 0x0     |

|     |                  |        | 0= No alignment reached                                               |         |

|     |                  |        | 1= All lanes are aligned                                              |         |

| 3:0 | SYNC_STATUS      | R/O    | Status of code group alignment (lane independent), one bit for        | 0x0     |

|     |                  |        | each lane.                                                            |         |

|     |                  |        | The order of the bits is:                                             |         |

|     |                  |        | <lane_3><lane_2><lane_1><lane_0>.</lane_0></lane_1></lane_2></lane_3> |         |

|     |                  |        | 1111: All lanes in sync                                               |         |

|     |                  |        | 0001: Lane 0 is in sync                                               |         |

|     |                  |        |                                                                       |         |

#### Table 24 • 4xF021

| Bit | Name          | Access | Description                                                              | Default |

|-----|---------------|--------|--------------------------------------------------------------------------|---------|

| 4   | LINK_STATE    | R/O    | Status of the link.                                                      | 0x0     |

|     |               |        | 0= Link is not in LINK_OK state                                          |         |

|     |               |        | 1= Link is in LINK_OK state                                              |         |

| 3:0 | SIGNAL_DETECT | R/O    | Current status of selected signal_detect input lines. For each lane, the | 0x0     |

|     |               |        | bit will be "1" if a valid signal is detected.                           |         |

|     |               |        | The order of the bits is:                                                |         |

|     |               |        | <lane_3><lane_2><lane_1><lane_0>.</lane_0></lane_1></lane_2></lane_3>    |         |

|     |               |        | 0= No valid signal detected                                              |         |

|     |               |        | 1= Valid signal detected                                                 |         |

Table 25 • 4xF022

| Bit   | Name                        | Access | Description                                                                                      | Default |

|-------|-----------------------------|--------|--------------------------------------------------------------------------------------------------|---------|

| 15:12 | LOCAL_FAULT_STICKY          | Sticky | Local fault status (one or more sync/align/fifo_of /fifo_uf/8b10b error), one bit for each lane. | 0x0     |

|       |                             |        | The order of the bits is:                                                                        |         |

|       |                             |        | <lane_3><lane_2><lane_1><lane_0>.</lane_0></lane_1></lane_2></lane_3>                            |         |

|       |                             |        | 1= A fault occurred                                                                              |         |

|       |                             |        | 0= No fault detected                                                                             |         |

|       |                             |        | Bit is cleared by writing a 1 to this position.                                                  |         |

| 11    | RX_OSET_FIFO_FULL_STICKY    | Sticky | Interrupt indicating that the ordered set FIFO is full.                                          | 0x0     |

|       |                             |        | 0= Overhead FIFO not full                                                                        |         |

|       |                             |        | 1= Overhead FIFO full                                                                            |         |

| 10    | RX_OSET_STICKY              | Sticky | Interrupt indicating that an ordered set was received and captured in the FIFO.                  | 0x0     |

|       |                             |        | 0= No ordered set captured<br>1= Ordered set captured in FIFO                                    |         |

| 9     | LINK_CHANGE_STICKY          | Sticky | This bit is asserted when the PCS enters or leaves the LINK_OK state.                            | 0x0     |

|       |                             |        | 0= No change                                                                                     |         |

|       |                             |        | 1= Link has changed into or out of the LINK_OK                                                   |         |

|       |                             |        | state                                                                                            |         |

| 8     | ALIGNMENT_CHANGE_STICKY     | Sticky | A change was detected in ALIGNMENT_STATUS.                                                       | 0x0     |

|       |                             |        | 0= No change                                                                                     |         |

|       |                             |        | 1= A change was detected (rising or falling)                                                     |         |

| 7:4   | SIGNAL_DETECT_CHANGE_STICKY | Sticky | A change was detected in the SIGNAL_DETECT status.                                               | 0x0     |

|       |                             |        | One bit per lane:                                                                                |         |

|       |                             |        | <lane_3><lane_2><lane_1><lane_0>.</lane_0></lane_1></lane_2></lane_3>                            |         |

|       |                             |        | 0= No change                                                                                     |         |

|       |                             |        | 1= A change was detected (rising or falling)                                                     |         |

| 3:0   | SYNC_CHANGE_STICKY          | Sticky | A change was detected in SYNC_STATUS.                                                            | 0x0     |

|       |                             |        | One bit is asserted per lane:                                                                    |         |

|       |                             |        | <lane_3><lane_2><lane_1><lane_0>.</lane_0></lane_1></lane_2></lane_3>                            |         |

|       |                             |        | 0= No change                                                                                     |         |

|       |                             |        | 1= A change was detected (rising or falling)                                                     |         |

Write OxFFFF and read it back. Expect it to be 0x0, meaning no sticky bit interrupts.

Table 26 • 4xF023

| Bit | Name                     | Access | Description                                                    | Default |

|-----|--------------------------|--------|----------------------------------------------------------------|---------|

| 9   | RX_FSET_FIFO_FULL_STICKY | Sticky | Interrupt indicating that the signal ordered set FIFO is full. | 0x0     |

|     |                          |        | 0= Overhead FIFO not full                                      |         |

|     |                          |        | 1= Overhead FIFO full                                          |         |

| Bit | Name                   | Access | Description                                                           | Default |

|-----|------------------------|--------|-----------------------------------------------------------------------|---------|

| 8   | RX_FSET_STICKY         | Sticky | Interrupt indicating that an signal ordered set was                   | 0x0     |

|     |                        |        | received and captured in the FIFO.                                    |         |

|     |                        |        | 0= No signal ordered set captured                                     |         |

|     |                        |        | 1= Signal ordered set captured in FIFO                                |         |

| 7   | RX_FSIG_CHANGED_STICKY | Sticky | Received   Fsig   code changed.                                       | 0x0     |

|     |                        |        | 1= New   Fsig   has been received                                     |         |

|     |                        |        | 0= No new   Fsig   since last read                                    |         |

|     |                        |        | Bit is cleared by writing a 1 to this position.                       |         |

| 6   | RX_Q_CHANGED_STICKY    | Sticky | Received   Q   code changed.                                          | 0x0     |

|     |                        |        | 1= New   Q   has been received                                        |         |

|     |                        |        | 0= No new   Q   since last read                                       |         |

|     |                        |        | Bit is cleared by writing a 1 to this position.                       |         |

| 5   | C8B10B_ERR_STICKY      | Sticky | Coding error detected in received 8B/10B encoded data.                | 0x0     |

|     |                        |        | 0= No error found                                                     |         |

|     |                        |        | 1= Coding error detected                                              |         |

|     |                        |        | Bit is cleared by writing a 1 to this position.                       |         |

| 4   | ALIGNMENT_LOST_STICKY  | Sticky | Alignment lost in de-skew logic.                                      | 0x0     |

|     |                        |        | 0= No misalignment occurred                                           |         |

|     |                        |        | 1= A (temporary) misalignment has been detected                       |         |

|     |                        |        | Bit is cleared by writing a 1 to this position.                       |         |

| 3:0 | SYNC_LOST_STICKY       | Sticky | Synchronization lost in lane $\dot{i}$ (i= 03, one bit per lane).     | 0x0     |

|     |                        |        | The order of the bits is:                                             |         |

|     |                        |        | <lane_3><lane_2><lane_1><lane_0>.</lane_0></lane_1></lane_2></lane_3> |         |

|     |                        |        | 0= No sync lost occurred                                              |         |

|     |                        |        | 1= Synchronization lost in lane $i$ (temporarily)                     |         |

|     |                        |        | Bit is cleared by writing a 1 to this position.                       |         |

Write 0xFFFF and read it back. Expect it to be 0x0, meaning no sticky bit interrupts.

#### Table 27 • 4xF026

| Bit  | Name | Access | Description                                                                          | Default |

|------|------|--------|--------------------------------------------------------------------------------------|---------|

| 15:0 | RX_Q | R/O    | Received   Q   code (sequence information, that is, the lower 24 bits of a sequence) | 0x0000  |

#### Table 28 • 4xF042

| Bit  | Name               | Access | Description                                                         | Default |

|------|--------------------|--------|---------------------------------------------------------------------|---------|

| 15:0 | ERR_CNT_FIFO_OF_L0 | R/W    | Number of detected FIFO overflow errors/number of errors in lane 0. | 0x0000  |

|      |                    |        | This counter will saturate at 0xffff.                               |         |

#### Table 29 • 4xF043

| Bit  | Name               | Access | Description                                                          | Default |

|------|--------------------|--------|----------------------------------------------------------------------|---------|

| 15:0 | ERR_CNT_FIFO_UF_L1 | R/W    | Number of detected FIFO underflow errors/number of errors in lane 1. | 0x0000  |

|      |                    |        | This counter will saturate at 0xffff.                                |         |

#### Table 30 • 4xE625 XAUI/RXAUI Output CFG0

| Bit  | Name     | Access | Description                                      | Default |

|------|----------|--------|--------------------------------------------------|---------|

| 15   | OB_IDLE  | R/W    | 1: Force to 0 V differential                     | 0x0     |

|      |          |        | 0: Normal mode                                   |         |

| 14   | Reserved | R/W    | Factory use                                      | 0x1     |

| 13   | OB_POL   | R/W    | Polarity of output signal.                       | 0x1     |

|      |          |        | 0: Normal                                        |         |

|      |          |        | 1: Inverted                                      |         |

| 12:7 | OB_POST0 | R/W    | Coefficients for first post-cursor (MSB is sign) | 0x00    |

| 6:2  | OB_PREC  | R/W    | Coefficients for pre-cursor (MSB is sign)        | 0x00    |

| 1    | Reserved | R/W    | Factory use                                      | 0x0     |

| 0    | Reserved | R/W    | Factory use                                      | 0x0     |

#### Table 31 • 4xE626 XAUI/RXAUI Output CFG1

| Bit   | Name     | Access | Description                                           | Default |

|-------|----------|--------|-------------------------------------------------------|---------|

| 15:11 | OB_POST1 | R/W    | Coefficients for second post-cursor (MSB is sign)     | 0x00    |

| 10    | Reserved | R/W    | Factory use                                           | 0x0     |

| 9     | Reserved | R/W    | Factory use                                           | 0x0     |

| 8     | OB_SR_H  | R/W    | Half the pre-driver speed, use for slew rate control. | 0x1     |

|       |          |        | 0: Disable—slew rate < 60 ps                          |         |

|       |          |        | 1: Enable—slew rate > 60 ps                           |         |

| 7:4   | OB_SR    | R/W    | Driver speed, fine adjustment of slew rate.           | 0x7     |

|       |          |        | If OB_SR_H= 0: 30 ps-60 ps                            |         |

|       |          |        | If OB_SR_H= 1: 60 ps-140 ps                           |         |

| 3:0   | Reserved | R/W    | Factory use                                           | 0x1     |

#### Table 32 • 4xE627 XAUI/RXAUI Output CFG2

| Bit | Name       | Access | Description                                         | Default |

|-----|------------|--------|-----------------------------------------------------|---------|

| 8:6 | OB_ENA_CAS | R/W    | Output skew, used for skew adjustment in SGMII mode | 0x1     |

| 5:0 | OB_LEV     | R/W    | Level of output amplitude.                          | 0x30    |

|     |            |        | 0: Lowest level<br>63: Highest level                |         |

## **2.4.4 1G Host Side**

#### Table 33 • 3xE000

| Bit | Name             | Access | Description                                                                                                                                                              | Default |

|-----|------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 4   | LINK_STATUS_TYPE | R/W    | Set type of link_status indication at CPU system.  0: Sync_status (from PCS synchronization state machine)  1: Bit 15 of PCS1G_ANEG_STATUS.lp_adv_ability (link up/down) | 0x0     |

| 1   | Reserved         | R/W    | Factory use                                                                                                                                                              | 0x0     |

| 0   | PCS_ENA          | R/W    | PCS enable. 0: Disable PCS 1: Enable PCS                                                                                                                                 | 0x0     |

#### Table 34 • 3xE001

| Bit | Name            | Access | Description                                                      | Default |

|-----|-----------------|--------|------------------------------------------------------------------|---------|

| 4   | UNIDIR_MODE_ENA | R/W    | Unidirectional mode enable.                                      | 0x0     |

|     |                 |        | Implementation of 802.3, Clause 66. When asserted, this enables  |         |

|     |                 |        | the MAC to transmit data independent of the state of the receive |         |

|     |                 |        | link.                                                            |         |

|     |                 |        | 0: Unidirectional mode disabled                                  |         |

|     |                 |        | 1: Unidirectional mode enabled                                   |         |

| 0   | SGMII_MODE_ENA  | R/W    | Selection of PCS operation.                                      | 0x1     |

|     |                 |        | 0: PCS is used in SerDes mode                                    |         |

|     |                 |        | 1: PCS is used in SGMII mode. Configuration bit PCS1G_ANEG_CFG.  |         |

|     |                 |        | SW_RESOLVE_ENA must be set additionally.                         |         |

#### Table 35 • 3xE002

| Bit | Name   | Access | Description                                                                                                                                 | Default |

|-----|--------|--------|---------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 8   | SD_SEL | R/W    | Signal detect selection (select input for internal signal_detect line).                                                                     | 0x0     |

|     |        |        | 0: Select signal_detect line from hard macro                                                                                                |         |

|     |        |        | 1: Select external signal_detect line                                                                                                       |         |

| 4   | SD_POL | R/W    | Signal detect polarity.                                                                                                                     | 0x1     |

|     |        |        | The signal level on signal_detect input pin must be equal to SD_POL to indicate signal detection (SD_ENA must be set).                      |         |

|     |        |        | 0: Signal detect input pin must be "0" to indicate a signal detection 1: Signal detect input pin must be "1" to indicate a signal detection |         |

| 0   | SD_ENA | R/W    | Signal detect enable.                                                                                                                       | 0x1     |

|     |        |        | 0: The signal detect input pin is ignored (the PCS assumes an active signal detect at all times)                                            |         |

|     |        |        | 1: The signal detect input pin is used to determine if a signal is detected                                                                 |         |

#### Table 36 • 3xE003

| Bit | Name                  | Access       | Description                                                   | Default |

|-----|-----------------------|--------------|---------------------------------------------------------------|---------|

| 8   | SW_RESOLVE_ENA        | R/W          | Software resolve abilities.                                   | 0x0     |

|     |                       |              | 0: If auto-negotiation fails (no matching HD or FD            |         |

|     |                       |              | capabilities), the link is disabled                           |         |

|     |                       |              | 1: The result of an auto-negotiation is ignored (the link can |         |

|     |                       |              | be set up through software)                                   |         |

|     |                       |              | This bit must be set in SGMII mode.                           |         |

| 1   | ANEG_RESTART_ONE_SHOT | One-<br>shot | Auto-negotiation restart.                                     | 0x0     |

|     |                       | 31100        | 0: No action                                                  |         |

|     |                       |              | 1: Restart auto-negotiation                                   |         |

| 0   | ANEG_ENA              | R/W          | Auto-negotiation enable.                                      | 0x0     |

|     |                       |              | 0: Auto-negotiation disabled                                  |         |

|     |                       |              | 1: Auto-negotiation enabled                                   |         |

## **Table 37 • 3xE00D**

| Bit | Name          | Access | Description                                                                 | Default |

|-----|---------------|--------|-----------------------------------------------------------------------------|---------|

| 8   | SIGNAL_DETECT | R/O    | Indicates whether or not the selected signal detect input line is asserted. | 0x0     |

|     |               |        | 0: No signal detected                                                       |         |

|     |               |        | 1: Signal detected                                                          |         |

| 4   | LINK_STATUS   | R/O    | Indicates whether the link is up or down. A link is up when ANEG state      | 0x0     |

|     |               |        | machine is in state LINK_OK or AN_DISABLE_LINK_OK.                          |         |

|     |               |        | 0: Link down                                                                |         |

|     |               |        | 1: Link up                                                                  |         |

| 0   | SYNC_STATUS   | R/O    | Indicates if PCS has successfully synchronized.                             | 0x0     |

|     |               |        | 0: PCS is out of sync                                                       |         |

|     |               |        | 1: PCS has synchronized                                                     |         |

#### **Table 38 • 3xE00E**

| Bit | Name          | Access | Description                                                                                                      | Default |

|-----|---------------|--------|------------------------------------------------------------------------------------------------------------------|---------|

| 7:0 | LINK_DOWN_CNT | R/W    | Link down counter.                                                                                               | 0x00    |

|     |               |        | A counter that counts the number of times a link has been down. The counter does not saturate at 255 and is only |         |

|     |               |        | cleared when writing 0 to the register.                                                                          |         |

**Table 39 • 3xE00F**

| Bit | Name               | Access | Description                                                                                                                                                                                                                                                                                                                  | Default |

|-----|--------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 4   | LINK_DOWN_STICKY   | Sticky | The sticky bit is set when the link has been down (that is, if the ANEG state machine has not been in the AN_DISABLE_LINK_OK or LINK_OK state for one or more clock cycles). This occurs if, for example, ANEG is restarted or if signal-detect or synchronization has been lost for more than 10 ms (1.6 ms in SGMII mode). | 0x0     |

|     |                    |        | 0: Link is up                                                                                                                                                                                                                                                                                                                |         |

|     |                    |        | 1: Link has been down                                                                                                                                                                                                                                                                                                        |         |

|     |                    |        | Bit is cleared by writing a 1 to this position.                                                                                                                                                                                                                                                                              |         |

| 0   | OUT_OF_SYNC_STICKY | Sticky | Sticky bit indicating if PCS synchronization has been lost.                                                                                                                                                                                                                                                                  | 0x0     |

|     |                    |        | 0: Synchronization has not been lost at any time                                                                                                                                                                                                                                                                             |         |

|     |                    |        | 1: Synchronization has been lost for one or more clock cycles                                                                                                                                                                                                                                                                |         |

|     |                    |        | Bit is cleared by writing a 1 to this position.                                                                                                                                                                                                                                                                              |         |

#### 2.4.5 Miscellaneous

The following table lists the host mode register information for operation mode.

Table 40 • 4xE806.2:0

| Bit | Name    | Access | Description             | Default |

|-----|---------|--------|-------------------------|---------|

| 2:0 | OP_MODE | R/O    | Current operation mode. | 0x0     |

|     |         |        | 0: XAUI                 |         |

|     |         |        | 1: RXAUI                |         |

|     |         |        | 2: SGMII on lane 0      |         |

|     |         |        | 3: SGMII on lane 3      |         |

|     |         |        | 4–7: Reserved           |         |

The following table lists the sync control configuration register information.

Table 41 • 1xB700

| Bit | Name          | Access | Description                                | Default |

|-----|---------------|--------|--------------------------------------------|---------|

| 4   | CLR_SYNC_STAT | R/W    | Clear sync control status register.        | 0x0     |

|     |               |        | 0: Idle                                    |         |

|     |               |        | 1: Clear                                   |         |

| 1:0 | LANE_SYNC_SRC | R/W    | Source selection for lane synchronization. | 0x3     |

|     |               |        | 0: Select DES_0                            |         |

|     |               |        | 1: Select DES_1                            |         |

|     |               |        | 2: Select F to delta F                     |         |

|     |               |        | 3: Synchronization disabled                |         |

## 2.5 Tracing Faults

Debugging can sometimes be difficult because of the interactions between the local MAC/PHY and link partner MAC/PHY.

When the cable is unplugged, the local PHY will detect no data or just noise coming in at 10G Rx input. When this happens, the PHY will generate a local fault to the MAC chip at the host side. When host-side MAC receives a local fault, it will respond with a remote fault. If only the optical cable of Rx is unplugged but the Tx cable is still on, then this remote fault will be sent from the local PHY to the link partner's PHY, which will pass the frame to the link partner's MAC chip. When the link partner's MAC chip receives a remote fault, it will respond with IDLEs back to the PHY to the non-terminated cable.

The described state remains until the Rx cable is re-plugged to the local PHY. When this happens, the local PHY passes the IDLE instead of a local fault to the local PHY at host side. The MAC chip at the host side will respond by removing the generation of the remote fault and start sending IDLE or traffic to the link partner. When these IDLEs or traffic reach the link partner MAC, the link partner MAC chip will respond with data packets and so the link will come up and pass traffic between the two sides.

In debugging, if faults are seen in both MAC chips, try to find out where the local fault originates. The readings in 4xF022/4xF023/4xF026 may be useful in determining the flow of local fault versus remote fault.

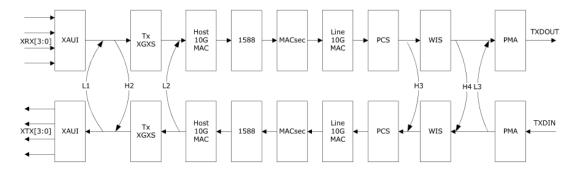

### 2.6 Loopbacks

Loopbacks are very useful in narrowing down the problematic area. There are three facility (line) loopbacks and three (host) equipment loopbacks.

Figure 1 • Loopbacks

#### 2.6.1 Facility Loopbacks