# ENT-AN0061 Application Note Transmitter Testing of 10/100/1000BASE-T

June 2018

# **Contents**

| 1 | Revision History                                    |                                          |                                                       | 1   |

|---|-----------------------------------------------------|------------------------------------------|-------------------------------------------------------|-----|

|   | 1.1                                                 | Revis                                    | ion 1.1                                               | 1   |

|   | 1.2                                                 | Revis                                    | ion 1.0                                               | 1   |

| 2 | Tran                                                | Transmitter Testing of 10/100/1000BASE-T |                                                       |     |

| _ |                                                     | Overview                                 |                                                       |     |

|   |                                                     | Compliance Individual Tests              |                                                       |     |

|   |                                                     | 2.2.1                                    | 1000BASE-T PMA Output Voltage/Droop/Template Tests    |     |

|   |                                                     | 2.2.2                                    | 1000BASE-T PMA Transmitter Timing Jitter              |     |

|   |                                                     | 2.2.3                                    | 1000BASE-T PMA Transmitter Distortion                 |     |

|   |                                                     | 2.2.4                                    | 1000BASE-T PMA Common-Mode Output Voltage             | . 4 |

|   |                                                     | 2.2.5                                    | 100BASE-TX PMD Active Output Interface Template Tests | . 4 |

|   |                                                     | 2.2.6                                    | 10BASE-T MAU Peak Differential Output Voltage Test    | . 5 |

|   |                                                     | 2.2.7                                    | 10BASE-T MAU Transmitter Waveform for Start of TP_IDL | . 5 |

|   |                                                     | 2.2.8                                    | 10BASE-T MAU TD Return Loss                           | . 6 |

|   | 2.3                                                 | Equip                                    | ment Needed                                           | 6   |

|   | 2.4                                                 | Confi                                    | guring the Test Equipment                             | 6   |

|   |                                                     | 2.4.1                                    | Scope, Probe, and Application Calibration             | . 7 |

|   |                                                     | 2.4.2                                    | Verify Probe Calibration                              | . 7 |

|   |                                                     | 2.4.3                                    | Tips For Proper Testing                               | . 7 |

|   | 2.5 Configuring the DUT for Analog Compliance Tests |                                          |                                                       | 7   |

|   |                                                     | 2.5.1                                    | 10BASE-T Amplitude Testing                            | . 7 |

|   |                                                     | 2.5.2                                    | 100BT Amplitude Testing                               | . 7 |

|   |                                                     | 2.5.3                                    | 1000BT Amplitude Testing                              | . 8 |

|   | 2.6                                                 | 1000                                     | BASE-T PMA Testing with Disturbing Signal             | 8   |

|   | 2.7                                                 | Board                                    | d/Magnetic Considerations                             | 9   |

|   | 2.8                                                 | Conc                                     | lusion                                                | 9   |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

# 1.1 **Revision 1.1**

Revision 1.1 of this document was published in June 2018. The following is a summary of the changes:

- The document scope was expanded to also cover 10M and 100M, as well as existing 1G compliance tests.

- Existing test suggestions were updated and ones for PMD and MAU were added. For more information, see Compliance Individual Tests.

- Equipment gain and bandwidth recommendations were added. For more information, see Equipment Needed.

- Vendor-specific procedures for calibrating Ethernet compliance software were added. For more information, see Scope, Probe, and Application Calibration.

- Speed-specific instructions for configuring the PHY were added. For more information, see Configuring the DUT for Analog Compliance Tests.

- PMA disturbing signal information was added. For more information, see 1000BASE-T PMA Testing with Disturbing Signal.

- The board/magnetic considerations were updated. For more information, see Board/Magnetic Considerations.

# 1.2 Revision 1.0

Revision 1.0 was published in November 2007. It was the first publication of this document.

# 2 Transmitter Testing of 10/100/1000BASE-T

IEEE 802.3 specifies the standard for the operation of the medium attachment interface of the PHY (referred to in various IEEE 802.3 clauses as the PMA, PMD, or MAU). Several methods can be employed to verify that a semiconductor vendor's device and the circuit board design conforms to this standard. A customer can apply to become part of the University of New Hampshire (UNH)'s Interoperability Lab (IOL)'s Gigabit Ethernet Consortium. This lab provides test suites for integrated circuit and board-level products that seek to conform to the IEEE 802.3 standard. Upon completion of their testing, a report is generated. This UNH report is considered by many in the industry as an unbiased third-party certification of a product's conformance. As an alternative, the customer can request a copy of the UNH test report from the silicon vendor, which is a cost-effective option.

Another method is for a customer to acquire equipment and perform the conformance testing in their own laboratory environment. Tektronix, for example, offers a software add-on package to many of their oscilloscopes that a customer could use to perform testing like the IOL. However, one of the pitfalls of this method is that there must be strict adherence to proper calibration, compliant test apparatus, test measurement procedures, and interpretation of results in order for it to be useful.

For more information, reference the IEEE 802.3 CSMA/CD Access Method (clauses 14, 25, and 40) Physical Layer Specification and the latest UNH IOL Ethernet Consortium Test Suites for the same IEEE clauses.

# 2.1 Overview

Microsemi's SimpliPHY™ and integrated switch/PHY products incorporate self-terminated, low-power, low-EMI line drivers that leverage industry-standard, low-cost magnetics. Conformance testing can be influenced by calibration factors, test fixture impedance, and probe parameters. Time spent in optimizing the production testing can translate into faster time-to-market.

# 2.2 Compliance Individual Tests

Within the UNH IOL's PMA, PMD, and MAU test suites, there are several tests in which careful test technique should be considered. Examples follow of particular test cases that require proper calibration, measurement, and interpretation of their results are highlighted here. For a more general discussion of test equipment setup and reference guides, see Equipment Needed.

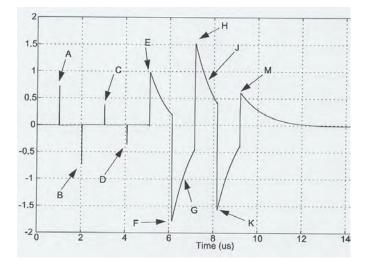

## 2.2.1 1000BASE-T PMA Output Voltage/Droop/Template Tests

The purpose of PMA Tests 40.1.1 through 40.1.3 are to verify correct transmitter output levels and shape. These tests are typically straightforward to pass. However, depending on the scope vendor's Ethernet compliance software package, some manual shifting of the template may be required (instead of relying on auto-fitting, which has been known to fail on certain scope vendor/firmware combinations). It is very important for the test engineer to visually inspect the Test Mode 1 waveform from the DUT to confirm polarity matches the following waveform.

Figure 1 • IEEE Template Testing Waveform

Depending on the scope, it may not invalidate the test result if the probe has incorrect polarity.

The margins required for board-level testing may differ from those required for integrated circuit device-level testing, due to the introduction of variations in magnetic components. However, testing accuracy is important in both cases to insure the conformance and reliability of the system.

# 2.2.2 1000BASE-T PMA Transmitter Timing Jitter

PMA test 40.1.5 includes a test to measure the filtered TX\_TCLK (transmit clock) jitter for the case where the DUT is operating in MASTER mode. In order to perform this test, an attempt is made to subtract out an estimated "unjittered reference" from the DUT's observed TX\_TCLK, and calculate the time difference between those observed zero-crossings versus the "unjittered" ideal zero-crossing times estimated by the scope.

Based on historical data from multiple scope vendors' Ethernet compliance software, Microsemi recommends sanity-checking any failing result. A simple means of sanity-checking the result is to capture the DUT Test Mode 2 (MDI) output into the 100  $\Omega$  loaded (TC2) test fixture. By applying a 1-second persistence filter to the TM2 waveform and cursor-measure the zero-crossing width, the unfiltered (worst-case), peak–peak jitter can be directly measured.

Microsemi has found on multiple occasions that failure was reported in the TM2 filtered, peak–peak value of test 40.1.5, yet the unfiltered, peak–peak value measurement at TC2 is within the allowable range. Clearly, the filtered reported value should not be greater than the unfiltered TC2 measurement (which includes the extra jitter generation term TX\_TCLK -> MDI).

#### 2.2.3 1000BASE-T PMA Transmitter Distortion

PMA test 40.1.6 measures the Test Mode 4 waveform of the DUT and finds its least mean-squared error. Then, the peak error between the ideal reference after partial response filtering and observed symbols is reported as the peak transmitter distortion (in milliVolts).

The 1000BASE-T transmitter distortion test accuracy requirement exceeds the limits of time-domain measurement that can be metrologically guaranteed on digital oscilloscope (DO) technology commonly available today. The criteria for failure involves measured errors exceeding 1% of the reference signal; that is, errors exceeding 10 mV of the 1 V Test Mode 4 transmitter signal. Yet, the industry-standard differential probe linearity specification applicable to this test has an error of 2% of the measured amplitude and so industry-standard input probes used in this test do not guarantee less the than 1% error that the test should require. As a result, the accuracy limits of standard DO equipment should be considered before drawing conclusions about conformance of this test.

Concerning the significance of test failures, Microsemi has evaluated failing systems and found no evidence indicating that a 0%-passing transmitter distortion test (that is, total test failure) affects bit error rate. For a detailed background and context of the 1000BASE-T transmitter distortion test, request the 1000BASE-T Transmitter Distortion Behavior Application Note.

#### 2.2.4 1000BASE-T PMA Common-Mode Output Voltage

PMA test 40.1.8 requires that the common-mode output voltage magnitude, Ecm\_out, be less than 50 mV peak-to-peak when transmitting data. However, the test fixture and signal trigger that are provided by scope vendors today does not give an accurate picture of the DUT's common-mode output.

**Note:** This test is not a common-mode noise test. As it is defined in IEEE 802.3, this measurement intends to capture the generated common-mode signal from the DUT transmitter. As a result, it should be acquired similarly to the Test Mode 4 acquisition in the 1000BASE-T transmitter distortion test; namely, an averaged acquisition that is triggered based on a unique location in the Test Mode 4 pattern. However, today's scopes simply use an asynchronous edge-based trigger for this test, which makes the results very sensitive to environmental noise present at the test site.

In order to mitigate the acquisition inaccuracy inherent in vendors' implementation of this test, environmental noise can be minimized by using additional grounds routed to the test fixture. An example showing a blue wire that ties the TC4 fixture location common to the DUT (digital board) ground is shown in the following.

Figure 2 • PMA Common-Mode Output Voltage Grounding

It is a requirement for running this test that a low-impedance ground be routed from a nearby DUT VSS point to the J4 point on the fixture, as shown. Keeping this wire short and wide (for example, a flat copper braid) ensures as low as possible AC impedance path.

## 2.2.5 100BASE-TX PMD Active Output Interface Template Tests

As part of the Active Output Interface Test Group, an MLT-3 eye pattern for the DUT is captured. The captured pattern is shown along with the eye mask specified in ANSI-X3.263, Annex J. However, the eye mask is considered informative by ANSI-X3.263, and no part of the eye pattern or mask is used for generating numerical results during the transmit jitter test. Margin may be improved by changing 100BASE-TX edge rate settings as described in the device datasheet, but this test may still fail and trying to improve it will cause more problems than benefits. Microsemi believes the DUT's default 100BASE-TX transmitter output waveform provides the best compromise for EMI performance without sacrificing link performance. Overall, the AOI eye mask is intended to serve as a "feel good" measure to show signal shape, but is not a useful indicator of link performance.

## 2.2.6 10BASE-T MAU Peak Differential Output Voltage Test

MAU test 14.1.3 requires that the 10BASE-T peak differential output of the DUT is greater than 2.2 V. For a pure voltage-mode line driver topology, this is a significant challenge with a 2.5 V voltage supply rail.

This test may fail, depending on the user configuration of 10BASE-T signal amplitude trim (as described in device datasheet) or other factors external to the device (such as the actual input voltage to VDD25A of the device). However, Microsemi has found no issue interoperating with other link partners when the DUT output is insufficient to pass the MAU test. That observation is documented in the Design Consideration "10BASE-T Signal Amplitude" of the device datasheet.

Another recommendation related to MAU test 14.1.3 is to use as long a test packet as possible for correct pattern acquisition. The Ethernet packet generator of the device supports both 1518 and 10,000 byte packets (the 1518-byte is sufficient, but 10,000-byte gives the most margin). It is acceptable to use this packet length for other MAU tests where a transmitted frame is required from the DUT.

# 2.2.7 10BASE-T MAU Transmitter Waveform for Start of TP\_IDL

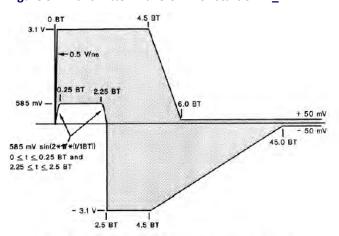

MAU test 14.1.7 requires that the 10BASE-T voltage template is met as in IEEE 802.3 figure 14-11, duplicated here.

Figure 3 • Transmitter Waveform for Start of TP\_IDL

Figure 14-11—Transmitter waveform for start of TP\_IDL

As shown, the MAU voltage and TP\_IDL templates collapse to zero at the origin. When making a measurement in real life, any small perturbation—which can include the measurement setup—may cause the test to fail when measured against the templates.

This shortcoming of the standard is recognized in the industry and the widely accepted solution is to ignore the templates for the first 50 mV on both the high and low portions of the template. Such a solution is standard in scope vendor's software in the TP\_IDL test so that the signal meets the intent of the IEEE standard but can be practically measured.

However, the UNH IOL measures compliance as specified in the standard and does not provide any tolerance at the zero-crossing of these templates. As a result, it is possible for the device to pass compliance testing with industry-standard test equipment, but fail the tests in the UNH IOL report. Microsemi believes strict adherence to this standard is not practical, and the approach adopted by the industry to ignore violations close to the zero-crossing is acceptable.

#### 2.2.8 10BASE-T MAU TD Return Loss

MAU test 14.1.8 requires a differential output impedance of the 10BASE-T line driver while the DUT is transmitting pseudorandom data. However, the technique of injecting data transmission while measuring return loss using an industry-standard network analyzer (NA) is problematic, as the NA stimulus signal may force its circuit into a non-linear operating region when superimposed on the DUT transmitter signal. This will not provide a true measure of the TD differential output impedance from the DUT.

Microsemi has two recommendations for ensuring true measurement of the TD differential output impedance of the DUT.

- Do not transmit frame data while performing 10BASE-T return loss measurement. Doing so allows

the NA technique to be applied where the output stage of the line driver is still operating within its

designed operating range while a stimulus from the NA is superimposed on the circuit output. This

provides an accurate measure of the output impedance and return loss of the 10BASE-T/10BASE-Te

line driver.

- Calibrate the NA output by measuring its amplitude when connected through a balun into an ideal  $100~\Omega$  load (for instance, TC2 of the Gigabit Ethernet test fixture). The peak–peak sine wave from the NA should measure 1 V (peak–peak). Do not rely on the power output values reported from the (unloaded) NA to infer a particular peak–peak voltage output. It is best to calibrate the NA output power setting using the  $100~\Omega$  load present on the TC2 fixture.

**Note**: UNH continues to test with the DUT transmitting frame data. UNH test reports may therefore indicate failures of this test due to inaccuracies in the superimposed sum of NA and DUT signals as previously described.

#### References

- IEEE Std 802.3-2015, subclause 40.6.1.1.2: Test modes

- Ibid., Figure 40–20: Example of transmitter test mode 1 waveform

- Ibid., sub-clause 40.6.1.1.3: Test fixtures

- Ibid., sub-clause 40.6.1.2.1-40.6.1.2.5: PMA transmitter electrical specifications

- Ibid., sub-clause 25.4.8: TP-PMD jitter

- Ibid., sub-clause 14.3.1.2: MAU transmitter specifications

# 2.3 Equipment Needed

For reliable conformance testing in a production test environment, high bit-resolution test equipment is recommended. Test fixtures, probe calibration, and cable connections can greatly influence the accuracy of test results.

The following is an example of a recommended test setup for amplitude testing. The bandwidth limitations help reject spurious, out-of-band noise present on the test system.

- Oscilloscope: Tektronix TDS7104 DPO with Ethernet compliance test app installed (or equivalent: ±1% DC vertical gain accuracy and 1 GHz maximum analog bandwidth recommended)

- Differential probe: Tektronix P6248 (or equivalent: 1.5 GHz maximum bandwidth recommended)

- Calibration fixture: Tektronix 067-0405-00 CAL/DESKEW FIXTURE

- BNC cable: maximum length= 10 inches

- RJ45 to differential/single-ended probe adapter— calibration is strongly recommended for both scope chassis and probe + adapter

# 2.4 Configuring the Test Equipment

The verification steps in the following sub-sections assume that the equipment used is what was listed in the previous section. However, the following averaging technique to verify calibration can be adopted to any scope vendor that provides an Ethernet compliance application.

## 2.4.1 Scope, Probe, and Application Calibration

Proper measurement requires calibration of both the oscilloscope and the probe used for the measurements referenced in this document. It also requires careful attention to the connection steps detailed in the user guide for each Ethernet compliance vendors' software application.

As the calibration method can vary significantly per scope model, please see the calibration and application instructions for both Tektronix and Keysight. Follow the probe de-skew steps in addition to the usual amplitude compensation steps. Timing-sensitive tests such as jitter, distortion, and disturbing signal tests require good timing accuracy in addition to amplitude accuracy.

# 2.4.2 Verify Probe Calibration

The averaging technique that follows is for Tektronix scopes, but the technique to verify calibration can be adopted to any scope vendor that provides an Ethernet compliance application.

- 1. On the oscilloscope, select Acquisition Setup -> Select Average, and set this to 10,000 samples.

- 2. Now, select Measure -> Amplitude.

- 3. Set **Measure** -> **Statistics**. It should read exactly 1.0 V for the TDS7104. If the value is 1.0 V, the probe is calibrated. An average other than 1.0 V indicates out-of-tolerance scope equipment.

## 2.4.3 Tips For Proper Testing

The RJ45 to differential probe adapter must be as short as possible between the oscilloscope probes and the device under test (DUT). The original test cable supplied by Tektronix (AMP) or Keysight (Keysight) are recommended, as they ensure insertion loss and other AC parametrics are unimpaired.

**Note:** The differential probe should be perpendicular to any signal cables or power supply cables. It is not recommended to run a power supply cable in parallel with the measurement probe cable due to the measurement levels involved.

Ensure that the test configuration pop-up within the Ethernet Compliance app is set to **Configure** -> **Avg** = to at least 256 (acquisitions). That provides a reasonable compromise between environmental noise-cancellation and test time.

# 2.5 Configuring the DUT for Analog Compliance Tests

Programming the copper PHY transmitter using the factory-qualified "init\_script" before evaluating the PHY is a requirement. The factory-supplied software stack (for example, depending on the device: Unified API, API Lite, or Microsemi driver) already includes the proper script sequence that applies factory-recommended settings.

#### 2.5.1 10BASE-T Amplitude Testing

To have the PHY transmit packets for the appropriate MAU tests (where transmissions are necessary), complete the following steps:

- 1. For dual-media devices only, ensure the media operating mode is copper-only by reading back register 23 bits 10:8 and confirming value 0x0. See the device datasheet.

- 2. Force speed mode to 10BASE-T by writing register 0 with the value 0x0100.

- 3. Force 10BASE-T link up by setting register 22, bit 15.

- 4. Force a transmitter pair (either A or B) using the force MDI crossover register selection (usually register 19 on extended page 1 registers, see the device datasheet).

- 5. Enable the Ethernet packet generator (EPG) following the device datasheet instructions.

# 2.5.2 100BT Amplitude Testing

To have the PHY transmit the scrambled idles waveform, complete the following steps:

- 1. For dual-media devices only, ensure the media operating mode is copper-only (register 23 bits 10:8 read back hardware defaults 0x0). See the device datasheet.

- 2. Force speed mode to 100BASE-TX by writing register 0 with the value 0x2100.

3. Force a transmitter pair (either A or B) using the force MDI crossover register selection (usually register 19 on extended page 1 registers, see the device datasheet).

## 2.5.3 1000BT Amplitude Testing

To have the PHY transmit the Test Mode 1 waveform, complete the following steps:

- 1. For dual-media devices only, ensure the media operating mode is copper-only (register 23 bits 10:8 read back hardware defaults 0x0). See the device datasheet.

- 2. Turn on the appropriate test mode signal. For example, Test Mode 1 for amplitude testing, by writing bit 15:13 in MII register 9 to 001. Also ensure that register 0 contains the default value, 0x1040.

In addition, it is helpful for noise reduction to soft power-down the other ports not under test using register 0 bit 11 of other ports on the same PCB.

# 2.6 1000BASE-T PMA Testing with Disturbing Signal

For certain 1000BASE-T PMA tests, the DUT is directly connected to a signal generator, referred to as the disturbing signal or Vd. The purpose of Vd is to simulate the presence of a remote transmitter, as would be the case on an operational 1000BASE-T link.

Microsemi does not recommend performing tests using the disturber for the following reasons:

- When an end-user is evaluating the PMA compliance, the objective is knowing whether the external components (those outside of the PHY device, such as magnetics and PCB construction) are compliant with IEEE 802.3 specifications. The PHY silicon itself and its behavior in the presence of an active transmitted signal is qualified at the factory. In fact, the silicon behavior is re-checked by UNH IOL when conducting their PMA test suite.

- The external components (such as magnetics and PCB signal paths) are invariant with respect to the disturbing signal's presence (or its absence). Thus, disturbing signal measurements on end-user equipment are comprised of a triply-redundant test effort. That is, the primary testing is performed at each PHY vendor and a secondary check is performed at UNH IOL, which leaves the end-user test as a third re-check.

- The disturber setup adds many test and measurement variables to the analog compliance tests that are difficult to control in end-customer test environments. Those additional variables greatly increase the challenge of running a valid PMA test. These challenges include the following:

- In order to match functional operation, the AWG "proxy" for the 1000BASE-T link partner would need to be phase-locked to the DUT's transmitter clock, but scope vendor compliance software has been buggy when TX\_TCLK used in these measurements, when it is even available. For example, TDSET3 displays the input option for certain tests, but does not always use it. The UNH PMA Test Suite uses a proprietary method to include TX\_TCLK for these measurements, but TX\_TCLK is frequently unavailable to use as an input in scope vendor solutions.

- Full-scale voltage with disturber more than doubles the quantization error in order to fit the composite signal (4.7 Vd-pp instead of 2 Vd-pp). The way around that quantization problem is to use two matched single-ended input signal paths and compute their differential sum in DPO post-acquisition. However, only Keysight offers such a two-channel single-ended solution, and even then, Keysight amplitude matching between the two SE scope channels is still missing. Other scope vendors pass through the added quantization penalty without adjustment, which degrades the test result.

- Vd adds uncompensated transmit jitter to the test mode signal acquisition due to an asynchronous amplitude fluctuation on the composite signal. The scope typically does not not recover/sync with the disturber AWG output. Especially for Test Mode 4, acquisition for the start of the 2047-symbol test pattern is obfuscated by Vd because the scope trigger is, in practice, a simple width-based trigger on a unique portion of the Test Mode 4 pattern. Frequently, the Vd source sufficiently perturbs the amplitude so as to falsely trigger the 2047-symbol start; the result is still displayed by the compliance app as valid, in spite of a "false start" in the Test Mode 4 pattern acquisition.

- The disturber test specification requires a highly linear AWG to synthesize the disturber voltage (see the –40 dBc criteria in the UNH PMA Test Suite Appendix). Microsemi has typically found low-frequency AWG solutions (such as the popular Agilent 33250A) fall short of that linearity requirement.

# 2.7 Board/Magnetic Considerations

As indicated previously, voltage accuracy is paramount to successful amplitude/template testing of the transmitter output. In order to provide as much voltage reference margin as possible within the DUT for the purpose of passing these tests, it is highly recommended to populate the board with a 0.1%-toleranced voltage-bandgap resistor. For the proper connection, reference the REF\_REXT\_A pin name in the PHY datasheet.

In addition, magnetics and magnetic modules directly impact amplitude measurements, so well-considered selection of magnetics is important to achieve first-pass success with analog compliance measurements. For detailed magnetic guidance, please refer to ENT-AN0098 Magnetics Guide.

# 2.8 Conclusion

Transmitter testing is highly dependent on the test setup, calibration, techniques, and quality of components such as magnetics on the printed circuit board. Following the best practices referenced in this document—starting with components of the board design and finishing with a carefully-executed transmitter test procedure—averts erroneous and inconsistent readings.

#### Microsemi Headquarters

One Enterprise, Aliso Viejo,

CA 92656 USA

Within the USA: +1 (800) 713-4113

Outside the USA: +1 (949) 380-6100

Sales: +1 (949) 380-6136

Fax: +1 (949) 215-4996

Email: sales.support@microsemi.com

© 2007–2018 Microsemi. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www microsemi.com.

VPPD-02009