## **ANTC206**

#### **Differential Clock Translation**

Author: Microchip Engineering Staff

Microchip Technology Inc.

#### INTRODUCTION

Considering that each available clock logic type (LVPECL, HCSL, CML, and LVDS) operates with a different common-mode voltage and swing level than the next (see Table 1), it is necessary to design clock logic translation between the driver side and receiver side for any given system design. This application note details how to translate one differential clock into other types of differential logics by adding attenuation resistors and bias circuits between them to attenuate the swing level and re-bias the common-mode for the input of the receiver.

TABLE 1: COMMON-MODE VOLTAGE

AND SWING LEVELS OF

DIFFERENT CLOCK LOGIC

TYPES

| Spec.                 | LVPECL                    | LVDS    | CML <sup>(1)</sup>          | HCSL   |

|-----------------------|---------------------------|---------|-----------------------------|--------|

| V <sub>CM</sub>       | V <sub>CC</sub> -<br>1.4V | 1.2V    | V <sub>CC</sub> -<br>0.2V   | 350 mV |

| V <sub>SWING_SE</sub> | 800 mV                    | 325 mV  | 400 mV                      | 700 mV |

| V <sub>OH</sub>       | V <sub>CC</sub> -1V       | 1.3625V | $V_{CC}$                    | 700 mV |

| V <sub>OL</sub>       | V <sub>CC</sub> -<br>1.8V | 1.0375V | V <sub>CC</sub> -<br>0.400V | 0V     |

| Reference             | V <sub>CC</sub>           | Ground  | V <sub>CC</sub>             | Ground |

**Note 1:** Terminated  $50\Omega$  to  $V_{CC}$ .

## INPUT/OUTPUT STRUCTURE OF EACH DIFFERENTIAL CLOCK LOGIC

Prior to designing the logic translation circuit, an examination of the input/output structures of each logic type — LVPECL, HCSL, CML, and LVDS — is required as each logic type features a different common-mode voltage and swing level.

### Low-Voltage, Positive-Reference, Emitter-Coupled Logic (LVPECL)

Low-voltage, positive-referenced, emitter-coupled logic (LVPECL) originates from emitter-coupled logic (ECL), adopting a positive power supply.

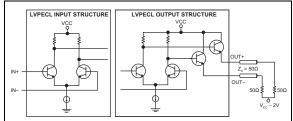

The LVPECL input is a current-switching differential pair with high input impedance (see Figure 1). The input common-mode voltage should be approximately  $V_{\rm CC}-1.3V$  for the purpose of having operating headroom, either from internal self-biasing or external biasing.

The LVPECL output consists of a differential pair amplifier which drives a pair of emitter followers (or open emitters) as illustrated in Figure 1. The output emitter followers should operate in the "active" region with DC current at all times. The output pins of OUT+ and OUT– are typically connected to differential transmission lines  $(Z_0$  = 100 $\Omega)$  or a single-ended transmission line  $(Z_0$  =  $50\Omega)$  for impedance matching. The proper termination for LVPECL output is  $50\Omega$  to  $V_{CC}$  – 2V and OUT+/OUT– will typically be  $V_{CC}$  – 1.3V, resulting in an approximate DC current flow of 14 mA.

Another way to terminate LVPECL output is to apply  $142\Omega$  to GND, which provides a DC-biasing for LVPECL output and a DC current path to GND. Because the LVPECL output common-mode is at V<sub>CC</sub> – 1.3V, the DC-biasing resistor can be selected by assuming a DC current of 14 mA (R = V<sub>CC</sub> – 1.3V / 14 mA), resulting in R =  $142\Omega$  ( $150\Omega$  also works) for V<sub>CC</sub> – 3.3V.

FIGURE 1: LVPECL Input/Output Structure.

#### Low-Voltage Differential Signaling (LVDS)

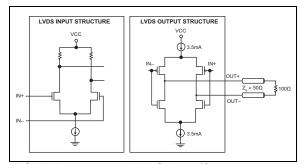

Low-voltage differential signaling (LVDS) input requires a  $100\Omega$  termination resistor across the pins of IN+ and IN– with a common-mode voltage of approximately 1.2V (see Figure 2). If the  $100\Omega$  termination is not included on-chip, it must be included on the printed circuit board (PCB).

The LVDS output driver consists of a 3.5 mA current source which is connected to differential outputs through a switching network. The output pins of OUT+ and OUT- are typically connecting to differential trans-

mission lines ( $Z_0 = 100\Omega$ ) or a single-ended transmission line  $(Z_0 = 50\Omega)$  for impedance matching, which are terminated with a  $100\Omega$  resistor across the receiver inputs, resulting in 350 mV swing for LVDS logic (Figure 2).

FIGURE 2:

LVDS Input/Output

Structure.

#### **Current-Mode Logic (CML)**

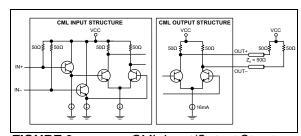

Most current-mode logic (CML) input structures have a  $50\Omega$  resistor to  $V_{CC}$  on-chip (see Figure 3). If not, then one must be applied to V<sub>DD</sub> on both inputs of IN+ and IN- on the PCB. The input transistors are emitter followers which drive a differential-pair amplifier.

The CML output consists of a differential pair of common-emitter transistors with  $50\Omega$  collector resistors as the CML output structure illustrated in Figure 3 shows. The outputs of OUT+ and OUT- are typically connecting to differential transmission lines ( $Z_0 = 100\Omega$ ) or a single-ended transmission line ( $Z_0 = 50\Omega$ ) for impedance matching (Figure 3). The signal swing is provided by switching the current in a common-emitter differential BJT. Assuming the current source is 16 mA (typical) and the CML output is loaded with a  $50\Omega$  resistor that is pulled-up to V<sub>CC</sub>, this will result in an output voltage swing from  $V_{CC}$  to  $V_{CC}$  – 0.4V with a common-mode voltage ( $V_{CC} - 0.2V$ ).

FIGURE 3:

CML Input/Output Structure.

#### **High-Speed Current-Steering Logic** (HCSL)

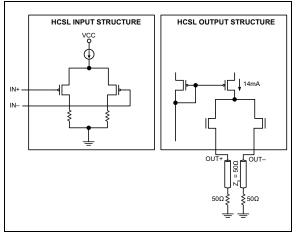

The high-speed current-steering logic (HCSL) input requires the single-ended swing of 700 mV on both input pins of IN+ and IN- with a common-mode voltage of approximately 350 mV (see Figure 4).

A typical HCSL driver is a differential logic with opensource outputs, where each of the output pins switches between 0 and 14 mA. When one output pin is low (0), the other is high (driving 14 mA). The output pins of OUT+ and OUT- are typically connecting to differential transmission lines ( $Z_0 = 100\Omega$ ) or a single-ended transmission line ( $Z_0 = 50\Omega$ ), which requires an external termination resistor (50Ω to GND), resulting in a 700 mV swing level for HCSL input structures (Figure 4).

FIGURE 4: Structure.

HCSL Input/Output

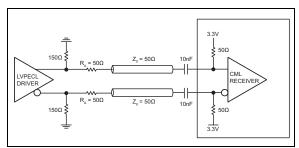

#### LVPECL-TO-CML TRANSLATION

As shown in Figure 5, placing a  $150\Omega$  resistor to GND at LVPECL driver output is essential for the open emitter to provide the DC-biasing as well as a DC current path to GND. In order to attenuate the 800 mV LVPECL swing to 400 mV CML swing, place a 50Ω attenuating resistor ( $R_A$ ) after the 150 $\Omega$  resistor to attenuate half of the LVPECL swing level. Additionally, self-biasing inside the CML receiver input must be confirmed. If the self-biasing at the input of CML is not present, a  $50\Omega$ termination resistor to V<sub>CC</sub> must be placed on the PCB for CML biasing and transmission line termination.

Microchip's ultra-low-jitter crystal oscillators and clock generators (i.e., MX55, MX57, SM802xxx, SM803xxx, MX85xxx) can provide <0.3 ps RMS phase jitter with any type of output logics, except CML logic. With the below translation circuit, it is easy to achieve CML output from LVPECL logic.

FIGURE 5:

LVPECL-to-CML

Translation.

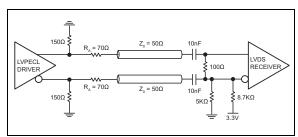

#### LVPECL-TO-LVDS TRANSLATION

Placing a 150Ω resistor to GND at LVPECL driver output is essential for the open emitter to provide the DCbiasing as well as a DC current path to GND (Figure 6). In order to attenuate the 800 mV LVPECL swing to a 325 mV LVDS swing, a 70Ω attenuating resistor must be applied after the  $150\Omega$  resistor. A 10 nF AC-coupled capacitor should be placed in front of the LVDS receiver to block DC level coming from the LVPECL driver. After the AC-coupled capacitor, re-biasing is required for the LVDS input and can be done by placing 8.7 k $\Omega$  resistor to 3.3V and 5 k $\Omega$  resistor to GND to achieve 1.2V DC level for the input common-mode of LVDS receiver. If the LVDS receiver already has integrated a 100Ω resistor across the differential input pins, the external  $100\Omega$ resistor is not required.

When Microchip's LVPECL fanout buffers (i.e., SY89831) have been qualified and adopted by customers-but some of the outputs require LVDS logics for the following receivers—this LVPECL-to-LVDS translation circuit is very helpful to achieve the target.

FIGURE 6:

LVPECL-to-LVDS

Translation.

#### LVPECL-TO-HCSL TRANSLATION

As shown in Figure 7, placing a  $150\Omega$  resistor to GND at LVPECL driver output is essential for the open emitter to provide the DC-biasing as well as a DC current path to GND. In order to attenuate an 800 mV LVPECL swing to a 700 mV HCSL swing, an attenuating resistor  $(R_A = 8\Omega)$  must be placed after the 150 $\Omega$  resistor. A 10 nF AC-coupled capacitor should be placed in front of the HCSL receiver to block DC level coming from the LVPECL driver. After the AC-coupled capacitor is

placed, re-biasing is required for the HCSL input and can be done by placing  $470\Omega$  resistor to 3.3V and  $56\Omega$ resistor to GND to achieve 350 mV DC level for the input common-mode of HCSL receiver.

When Microchip's LVPECL fanout buffers (i.e., SY89831) have been qualified and adopted by customers-but some of the outputs require HCSL logics for the following receivers—this LVPECL-to-HCSL translation circuit is very helpful to achieve the target.

FIGURE 7:

LVPECL-to-HCSL

Translation.

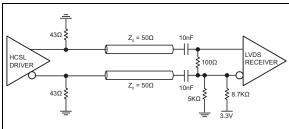

#### **HCSL-TO-LVDS TRANSLATION**

In Figure 8, each of HCSL output pins switches between 0 and 14 mA. When one output pin is low (0), the other is high (driving 14 mA). The equivalent loading for HCSL driver is  $48\Omega$  parallel to  $50\Omega$ , which equates  $23.11\Omega$ . The swing level on the LVDS input is 14 mA  $\times$  23.11 $\Omega$  = 323 mV. A 10 nF AC-coupled capacitor should be placed in front of the LVDS receiver to block DC level coming from the HCSL driver. After the AC-coupled capacitor is placed, re-biasing is required for the LVDS input and can be done by placing 8.7 k $\Omega$ resistor to 3.3V and 5 k $\Omega$  resistor to GND to achieve 1.2V DC level for the input common-mode of LVDS Receiver. If the LVDS receiver already has integrated a  $100\Omega$  resistor across the differential input pins, the external  $100\Omega$  resistor is not required.

Microchip's HCSL fanout buffers When SY75576L, SY75578L) have been qualified and adopted by customers-but some of the outputs require LVDS logics for the following receivers—this HCSL-to-LVDS translation circuit is very helpful to achieve the target.

FIGURE 8:

HCSL-to-LVDS Translation.

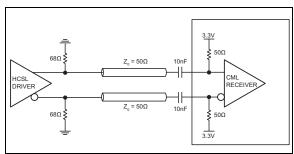

#### **HCSL-TO-CML TRANSLATION**

In Figure 9, each of HCSL output pins switches between 0 and 14 mA. When one output pin is low (0), the other is high (driving 14 mA). The equivalent loading for HCSL driver is  $68\Omega$  parallel to  $50\Omega$ , which equates  $28.81\Omega$ . The swing level on the CML input is 14 mA  $\times$   $28.81\Omega$  = 403 mV. A 10 nF AC-coupled capacitor should be placed in front of the CML receiver to block DC level coming from the HCSL driver. Additionally, self-biasing inside the CML receiver input must be confirmed. If the self-biasing at the input of CML is not present, a  $50\Omega$  termination resistor to  $V_{CC}$  must be placed on the PCB for CML biasing and transmission line termination.

Microchip's ultra-low-jitter crystal oscillators and clock generators (i.e., MX55, MX57, SM802xxx, SM803xxx, MX85xxx) can provide <0.3 ps RMS phase jitter with any type of output logics, except CML logic. With the translation circuit below, it is easy to achieve CML output from HCSL logic.

FIGURE 9: HCSL-to-CML Translation.

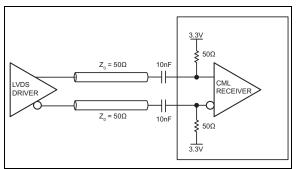

#### LVDS-TO-CML TRANSLATION

LVDS output drives a  $\pm 3.5$  mA current through the termination of  $100\Omega$  resistor, resulting in a 350 mV swing level in front of the CML receiver (Figure 10). Confirmation that the CML receivers are capable of receiving a 350 mV swing is required because the standard swing of CML is 400 mV. Additionally, self-biasing inside the CML receiver input must also be confirmed. If the self-biasing at the input of CML is not present, a  $50\Omega$  termination resistor to  $V_{CC}$  must be placed on the PCB for CML biasing and transmission line termination.

Microchip's ultra-low-jitter crystal oscillators and clock generators (i.e., MX55, MX57, SM802xxx, SM803xxx, MX85xxx) can provide <0.3 ps RMS phase jitter with any type of output logics, except CML logic. With the below translation circuit, it is easy to achieve CML output from LVDS logic.

FIGURE 10: LVDS-to-CML Translation.

#### SUMMARY

This application note presents how to translate different clock logics. With the proper signal level attenuation and self-biasing circuit in front of the receiver side, a translation circuit can be easily achieved with fewer external components.

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### **Trademarks**

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0718-8

#### Worldwide Sales and Service

#### **AMERICAS**

**Corporate Office** 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200

Fax: 480-792-7277 **Technical Support:**

http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323

Fax: 317-773-5453

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

Canada - Toronto Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office** Suites 3707-14, 37th Floor Tower 6, The Gateway

Hong Kong

Tel: 852-2943-5100 Fax: 852-2401-3431

Harbour City, Kowloon

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR Tel: 852-2943-5100 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

China - Wuhan Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

China - Xiamen Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

Japan - Tokyo Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Dusseldorf** Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

Germany - Munich Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

Spain - Madrid Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

06/17/16