# Section 20. Serial Peripheral Interface (SPI)

# **HIGHLIGHTS**

This section of the manual contains the following major topics:

| 20.2       Status and Control Registers       20-4         20.3       Modes of Operation       20-7         20.4       SPI Master Mode Clock Frequency       20-19         20.5       Operation in Power-Saving Modes       20-20         20.6       Register Maps       20-22         20.7       Related Application Notes       20-23         20.8       Revision History       20-24 | 20.1 | Introduction                    | 20-2  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------------------|-------|

| 20.4       SPI Master Mode Clock Frequency       20-19         20.5       Operation in Power-Saving Modes       20-20         20.6       Register Maps       20-22         20.7       Related Application Notes       20-23                                                                                                                                                             | 20.2 | Status and Control Registers    | 20-4  |

| 20.5 Operation in Power-Saving Modes 20-20 20.6 Register Maps 20-22 20.7 Related Application Notes 20-23                                                                                                                                                                                                                                                                                | 20.3 | Modes of Operation              | 20-7  |

| 20.6       Register Maps       20-22         20.7       Related Application Notes       20-23                                                                                                                                                                                                                                                                                           | 20.4 | SPI Master Mode Clock Frequency | 20-19 |

| 20.7 Related Application Notes                                                                                                                                                                                                                                                                                                                                                          | 20.5 | Operation in Power-Saving Modes | 20-20 |

| • •                                                                                                                                                                                                                                                                                                                                                                                     | 20.6 | Register Maps                   | 20-22 |

| 20.8 Revision History                                                                                                                                                                                                                                                                                                                                                                   | 20.7 | Related Application Notes       | 20-23 |

|                                                                                                                                                                                                                                                                                                                                                                                         | 20.8 | Revision History                | 20-24 |

Note:

This family reference manual section is meant to serve as a complement to device data sheets. Depending on the device variant, this manual section may not apply to all dsPIC30F devices.

Please consult the note at the beginning of the "Serial Peripheral Interface (SPI)" chapter in the current device data sheet to check whether this document supports the device you are using.

Device data sheets and family reference manual sections are available for download from the Microchip Worldwide Web site at: http://www.microchip.com

#### 20.1 Introduction

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be Serial EEPROMs, shift registers, display drivers, A/D converters, etc. The SPI module is compatible with Motorola's SPI and SIOP interfaces.

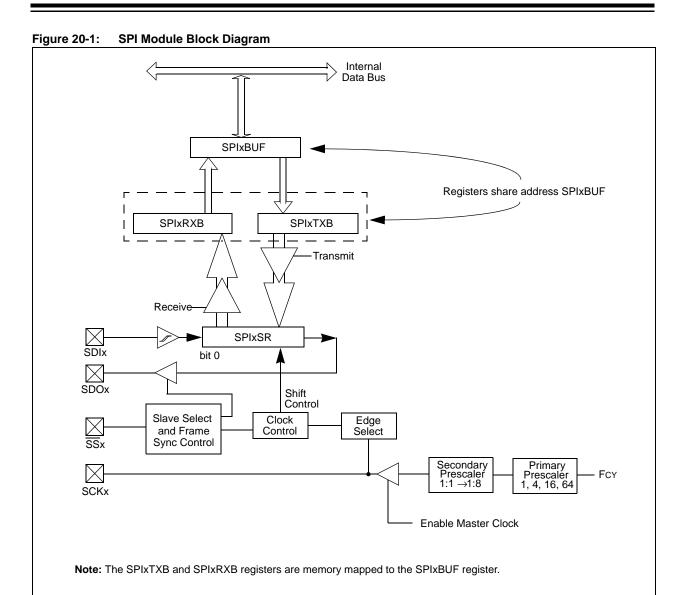

Figure 20-1 illustrates the block diagram of the SPI module.

Depending on the variant, the dsPIC30F family offers one or two SPI modules on a single device. SPI1 and SPI2 are functionally identical. The SPI2 module is available in many of the higher pin count packages (64-pin and higher), while the SPI1 module is available on all devices.

Note:

In this section, the SPI modules are referred together as SPIx or separately as SPI1 and SPI2. Special Function registers (SFRs) will follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 or SPI2 module.

The SPI serial port consists of the following Special Function Registers (SFRs):

- SPIxBUF: Address in SFR space that is used to buffer data to be transmitted and data that is received. This address is shared by the SPIxTXB and SPIxRXB registers.

- SPIxCON: A control register that configures the module for various modes of operation.

- SPIxSTAT: A status register that indicates various status conditions.

In addition, there is a 16-bit shift register, SPIxSR, that is not memory mapped. It is used for shifting data in and out of the SPI port.

The memory mapped SFR, SPIxBUF, is the SPI Data Receive/Transmit register. Internally, the SPIxBUF register actually consists of two separate registers - SPIxTXB and SPIxRXB. The Receive Buffer register, SPIxRXB, and the Transmit Buffer register, SPIxTXB, are two unidirectional 16-bit registers. These registers share the SFR address named SPIxBUF. If a user writes data to be transmitted to the SPIxBUF address, internally the data gets written to the SPIxTXB register. Similarly, when the user reads the received data from SPIxBUF, internally the data is read from the SPIxRXB register. This double-buffering of transmit and receive operations allows continuous data transfers in the background. Transmission and reception occur simultaneously.

**Note:** The user cannot write to the SPIxTXB register or read from the SPIxRXB register directly. All reads and writes are performed on the SPIxBUF register.

The SPI serial interface consists of the following four pins:

- · SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx: Active low slave select or frame synchronization I/O pulse

# 20.2 Status and Control Registers

#### Register 20-1: SPIxSTAT: SPI Status and Control Register

| Upper Byte | e:  |         |     |     |     |     |       |

|------------|-----|---------|-----|-----|-----|-----|-------|

| R/W-0      | U-0 | R/W-0   | U-0 | U-0 | U-0 | U-0 | U-0   |

| SPIEN      | _   | SPISIDL | _   | _   | _   | _   | _     |

| bit 15     |     |         |     |     |     |     | bit 8 |

| Lower Byte | e:          |     |     |     |     |        |        |

|------------|-------------|-----|-----|-----|-----|--------|--------|

| U-0        | R/W-0<br>HS | U-0 | U-0 | U-0 | U-0 | R-0    | R-0    |

| _          | SPIROV      | _   | _   | _   | 1   | SPITBF | SPIRBF |

| bit 7      |             |     |     |     |     |        | bit 0  |

bit 15 SPIEN: SPI Enable bit

1 = Enables module and configures SCKx, SDOx, SDIx and SSx as serial port pins

0 = Disables module

bit 14 **Unimplemented:** Read as '0' bit 13 **SPISIDL:** Stop in Idle Mode bit

1 = Discontinue module operation when device enters Idle mode

0 = Continue module operation in Idle mode

bit 12-7 **Unimplemented:** Read as '0' **SPIROV:** Receive Overflow Flag bit

1 = A new byte/word is completely received and discarded. The user software has not read the previous data in the SPIxBUF register

0 = No overflow has occurred

bit 5-2 Unimplemented: Read as '0'

bit 1 SPITBF: SPI Transmit Buffer Full Status bit

$\texttt{1} = \mathsf{Transmit} \ \mathsf{not} \ \mathsf{yet} \ \mathsf{started}, \ \mathsf{SPIxTXB} \ \mathsf{is} \ \mathsf{full}$

0 = Transmit started, SPIxTXB is empty

Automatically set in hardware when CPU writes SPIxBUF location, loading SPIxTXB.

Automatically cleared in hardware when SPIx module transfers data from SPIxTXB to SPIxSR.

bit 0 SPIRBF: SPI Receive Buffer Full Status bit

1 = Receive complete, SPIxRXB is full

0 = Receive is not complete, SPIxRXB is empty

Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB.

Automatically cleared in hardware when core reads SPIxBUF location, reading SPIxRXB.

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

HC = Cleared by Hardware HS = Set by Hardware

-n = Value at Reset '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

# Register 20-2: SPIxCON: SPIx Control Register

| Upper Byte | e:    |        |     |        |        |       |       |

|------------|-------|--------|-----|--------|--------|-------|-------|

| U-0        | R/W-0 | R/W-0  | U-0 | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

| _          | FRMEN | SPIFSD | 1   | DISSDO | MODE16 | SMP   | CKE   |

| bit 15     |       |        |     | •      |        | •     | bit 8 |

| Lower Byte | e:    |       |       |           |       |       |       |

|------------|-------|-------|-------|-----------|-------|-------|-------|

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

| SSEN       | CKP   | MSTEN | ;     | SPRE<2:0> |       | PPRE  | <1:0> |

| bit 7      |       |       |       |           |       |       | bit 0 |

- bit 15 **Unimplemented:** Read as '0'

- bit 14 FRMEN: Framed SPI Support bit

- 1 = Framed SPI support enabled

- 0 = Framed SPI support disabled

- bit 13 SPIFSD: Frame Sync Pulse Direction Control on SSx pin bit

- 1 = Frame sync pulse input (slave)

- 0 = Frame sync pulse output (master)

- bit 12 Unimplemented: Read as '0'

- bit 11 DISSDO: Disable SDOx pin bit

- 1 = SDOx pin is not used by module. Pin is controlled by associated port register

- 0 = SDOx pin is controlled by the module

- bit 10 MODE16: Word/Byte Communication Select bit

- 1 = Communication is word-wide (16 bits)

- 0 = Communication is byte-wide (8 bits)

- bit 9 SMP: SPI Data Input Sample Phase bit

#### Master mode:

- 1 = Input data sampled at end of data output time

- 0 = Input data sampled at middle of data output time

#### Slave mode:

SMP must be cleared when SPI is used in Slave mode.

- bit 8 CKE: SPI Clock Edge Select bit

- 1 = Serial output data changes on transition from active clock state to Idle clock state (see bit 6)

- 0 = Serial output data changes on transition from Idle clock state to active clock state (see bit 6)

**Note:** The CKE bit is not used in the Framed SPI modes. The user should program this bit to '0' for the Framed SPI modes (FRMEN = 1).

- bit 7 SSEN: Slave Select Enable (Slave mode) bit

- $1 = \overline{SS}$  pin used for Slave mode

- $0 = \overline{SS}$  pin not used by module. Pin controlled by port function

- bit 6 **CKP:** Clock Polarity Select bit

- 1 = Idle state for clock is a high level; active state is a low level

- 0 = Idle state for clock is a low level; active state is a high level

- bit 5 MSTEN: Master Mode Enable bit

- 1 = Master mode

- 0 = Slave mode

20

# dsPIC30F Family Reference Manual

# Register 20-2: SPIxCON: SPIx Control Register (Continued)

bit 4-2 **SPRE<2:0>:** Secondary Prescale (Master Mode) bits (Supported settings: 1:1, 2:1 through 8:1, all inclusive)

111 = Secondary prescale 1:1

110 = Secondary prescale 2:1

•

000 = Secondary prescale 8:1

bit 1-0 PPRE<1:0>: Primary Prescale (Master Mode) bits

11 = Primary prescale 1:1

10 = Primary prescale 4:1

01 = Primary prescale 16:1

00 = Primary prescale 64:1

# Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

# 20.3 Modes of Operation

The SPI module has flexible operating modes which are discussed in the following subsections:

- 8-bit and 16-bit Data Transmission/Reception

- · Master and Slave Modes

- · Framed SPI Modes

# 20.3.1 8-bit vs. 16-bit Operation

MODE16 control bit (SPIxCON<10>), allows the module to communicate in either 8-bit or 16-bit modes. The functionality will be the same for each mode except the number of bits that are received and transmitted. Additionally, the following should be noted in this context:

- The module resets when the value of the MODE16 bit (SPIxCON<10>) is changed.

Consequently, the bit should not be changed during normal operation.

- Data is transmitted from bit 7 of the SPIxSR for 8-bit operation while it is transmitted from bit 15 of the SPIxSR for 16-bit operation. In both modes, data is shifted into bit '0' of the SPIxSR.

- Eight clock pulses at the SCKx pin are required to shift in/out data in the 8-bit mode, while 16 clock pulses are required in the 16-bit mode.

## 20.3.2 Master and Slave Modes

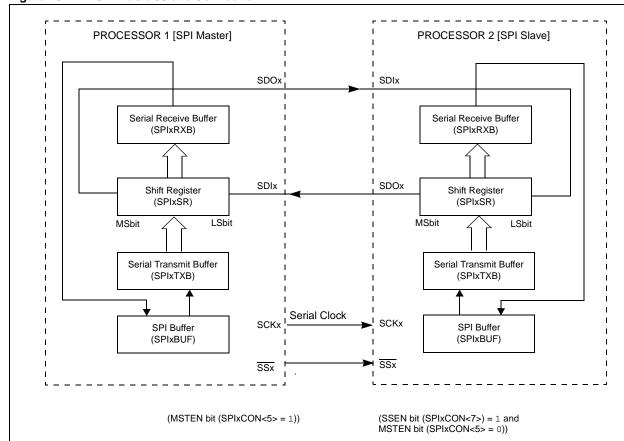

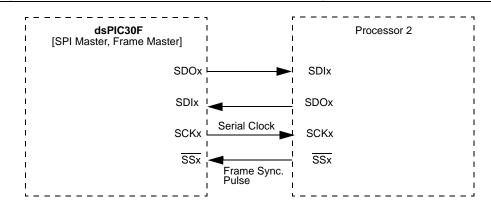

This section describes the SPI Master and Slave modes of operation. Figure 20-2 illustrates the SPI Master/Slave connection.

Figure 20-2: SPI Master/Slave Connection

- **Note 1:** Using the  $\overline{SSx}$  pin in Slave mode of operation is optional.

- 2: User must write transmit data to or read received data from SPIxBUF. The SPIxTXB and SPIxRXB registers are memory mapped to SPIxBUF.

#### 20.3.2.1 Master Mode

The following steps should be taken to set up the SPI module for the Master mode of operation:

- 1. If using interrupts:

- · Clear the SPIxIF bit in the respective IFSn register

- · Set the SPIxIE bit in the respective IECn register

- Write the SPIxIP bits in the respective IPCn register

- Write the desired settings to the SPIxCON register with MSTEN bit (SPIxCON<5>) = 1.

- 3. Clear the SPIROV bit (SPIxSTAT<6>).

- 4. Enable SPI operation by setting the SPIEN bit (SPIxSTAT<15>).

- 5. Write the data to be transmitted to the SPIxBUF register. Transmission(and Reception) starts as soon as data is written to the SPIxBUF register.

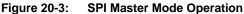

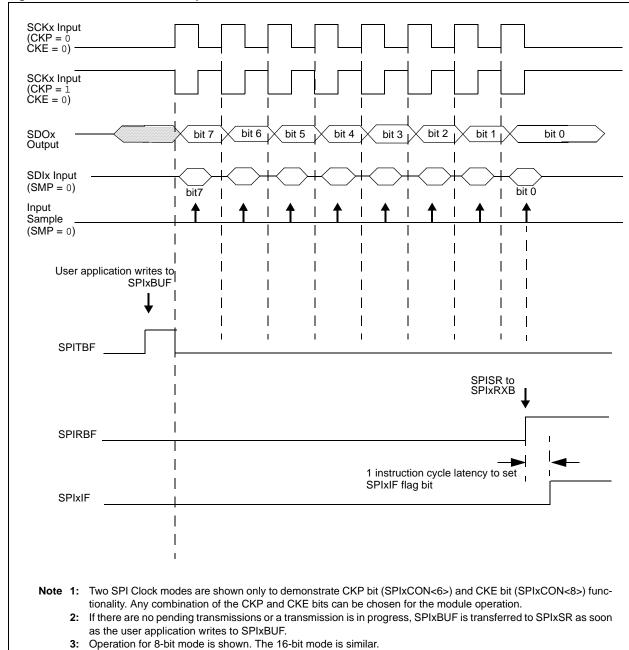

Figure 20-3 illustrates the SPI Master mode of operation. In Master mode, the system clock is prescaled and then used as the serial clock. The prescaling is based on the settings in the PPRE<1:0> bits (SPIxCON<1:0>) and SPRE<2:0> bits (SPIxCON<4:2>). The serial clock is output via the SCKx pin to slave devices. Clock pulses are only generated when there is data to be transmitted. For further information, refer to **20.4** "SPI Master Mode Clock Frequency".

The CKP and CKE bits determine on which edge of the clock, data transmission occurs.

Both data to be transmitted and data that is received are respectively written into or read from the SPIxBUF register.

The following steps describe the SPI module operation in Master mode:

- Once the module is set up for the Master mode of operation and enabled, data to be transmitted is written to the SPIxBUF register. The SPITBF bit (SPIxSTAT<1>) is set.

- 2. The contents of SPIxTXB are moved to the shift register, SPIxSR, and the SPITBF bit is cleared by the module.

- A series of 8/16 clock pulses shifts out 8/16 bits of transmit data from the SPIxSR to the SDOx pin and simultaneously shifts in the data at the SDIx pin into the SPIxSR.

- 4. When the transfer is complete, the following events occurs:

- The interrupt flag bit, SPIxIF, is set. SPI interrupts can be enabled by setting the interrupt enable bit SPIxIE. The SPIxIF flag is not cleared automatically by the hardware.

- Also, when the ongoing transmit and receive operation is completed, the contents of the SPIxSR are moved to the SPIxRXB register.

- The SPIRBF bit (SPIxSTAT<0>) is set by the module, indicating that the receive buffer is full. Once the SPIxBUF register is read by the user application, the hardware clears the SPIRBF bit.

- If the SPIRBF bit is set (receive buffer is full) when the SPI module needs to transfer data from SPIxSR to SPIxRXB, the module will set the SPIROV bit (SPIxSTAT<6>), indicating an overflow condition.

- Data to be transmitted can be written to SPIxBUF by the user software at any time as long

as the SPITBF bit (SPIxSTAT<1>) is clear. The write can occur while SPIxSR is shifting

out the previously written data, allowing continuous transmission.

**Note:** The SPIxSR register cannot be written into directly by the user. All writes to the SPIxSR register are performed through the SPIxBUF register.

- only. Only one of the four modes can be chosen for operation.

- 2: SDI and input samples are shown for two different values of the SMP bit (SPIxCON<9>), for demonstration purposes only. Only one of the two configurations of the SMP bit can be chosen during operation.

- 3: If there are no pending transmissions, SPIxTXB is transferred to SPIxSR as soon as the user application writes to SPIxBUF.

- 4: Operation for 8-bit mode is shown. The 16-bit mode is similar.

#### 20.3.2.2 Slave Mode

The following steps should be taken to set up the SPI module for the Slave mode of operation:

- 1. Clear the SPIxBUF register.

- 2. If using interrupts:

- · Clear the SPIxIF bit in the respective IFSn register

- Set the SPIxIE bit in the respective IECn register

- · Write the SPIxIP bits in the respective IPCn register

- 3. Write the desired settings to the SPIxCON register with MSTEN bit (SPIxCON<5>) = 0.

- 4. Clear the SMP bit.

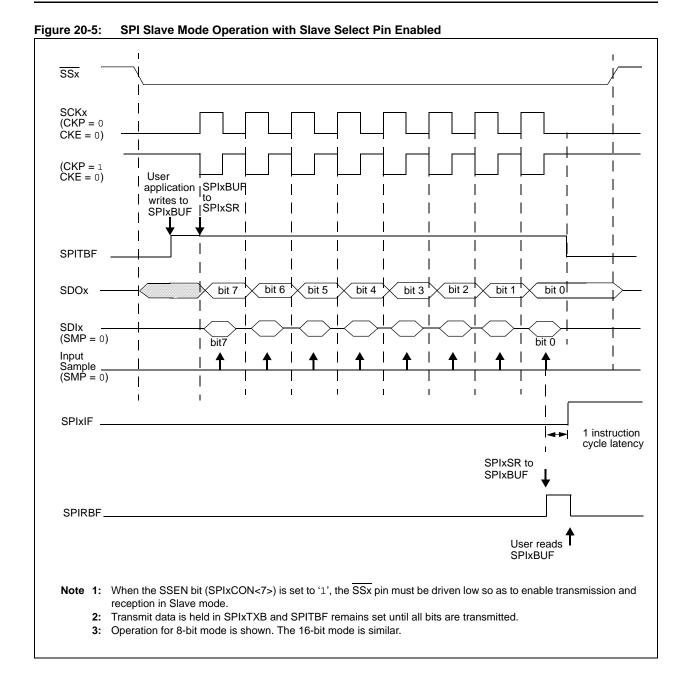

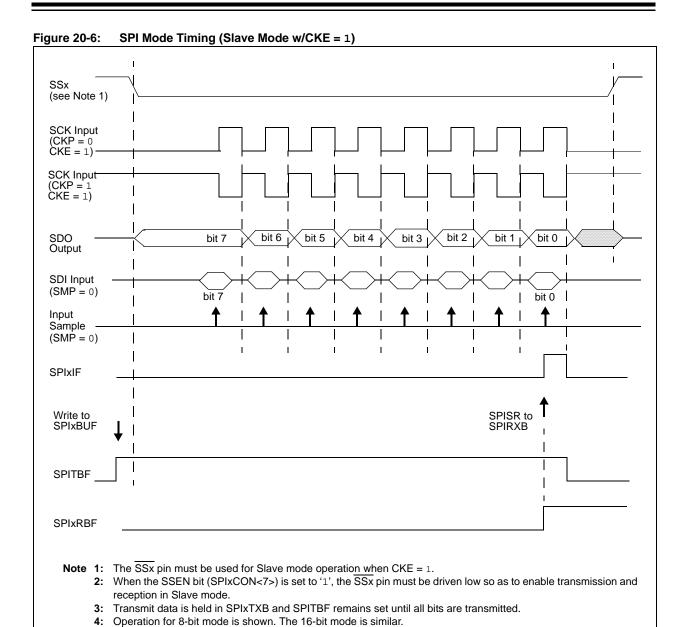

- 5. If the CKE bit is set, then the SSEN bit must be set, thus enabling the SSx pin.

- 6. Clear the SPIROV bit (SPIxSTAT<6>) and,

- 7. Enable SPI operation by setting the SPIEN bit (SPIxSTAT<15>).

In Slave mode, data is transmitted and received as external clock pulses appears on the SCKx pin. The CKP bit (SPIxCON<6>) and CKE bit (SPIxCON<8>) determine on which edge of the clock data transmission occurs.

Data to be transmitted and data that is received are respectively written into or read from the SPIxBUF register.

The remaining operation of the module is identical to that in the Master mode. A few additional features provided in the Slave mode are:

Slave Select Synchronization: The SSx pin allows a Synchronous Slave mode. If the SSEN bit (SPIxCON<7>) is set, transmission and reception is enabled in Slave mode only if the SSx pin is driven to a low state. The port output or other peripheral outputs must not be driven in order to allow the SSx pin to function as an input. If the SSEN bit is set and the SSx pin is driven high, the SDOx pin is no longer driven and will tri-state even if the module is in the middle of a transmission. An aborted transmission will be retried the next time the SSx pin is driven low using the data held in the SPIxTXB register. If the SSEN bit is not set, the SSx pin does not affect the module operation in Slave mode.

**SPITBF Status Flag Operation:** The function of the SPITBF bit (SPIxSTAT<1>) is different in the Slave mode of operation. The following steps describes the function of the SPITBF for various settings of the Slave mode of operation:

- If SSEN bit (SPIxCON<7>) is cleared, the SPITBF bit is set when the SPIxBUF is loaded by the user code. It is cleared when the module transfers SPIxTXB to SPIxSR. This is similar to the SPITBF bit function in Master mode.

- 2. If SSEN bit (SPIxCON<7>) is set, the SPITBF bit is set when the SPIxBUF is loaded by the user code. However, it is cleared only when the SPIx module completes data transmission. A transmission will be aborted when the SSx pin goes high and may be retried at a later time. Each data word is held in SPIxTXB until all bits are transmitted to the receiver.

**Note:** To meet module timing requirements, the  $\overline{SSx}$  pin must be enabled in Slave mode when CKE = 1. Refer to Figure 20-6 for more details.

Figure 20-4: SPI Slave Mode Operation with Slave Select Pin Disabled

DS70067E-page 20-12

© 2010 Microchip Technology Inc.

# 20.3.3 SPI Error Handling

When a new data word has been shifted into SPIxSR and the previous contents of SPIxRXB have not been read by the user software, the SPIROV bit (SPIxSTAT<6>) will be set. The module will not transfer the received data from SPIxSR to SPIxRXB. Further data reception is disabled until the SPIROV bit is cleared. The SPIROV bit is not cleared automatically by the module and must be cleared by the user software.

# 20.3.4 SPI Receive Only Operation

Setting the DISSDO control bit (SPIxCON<11>), disables the transmission at the SDOx pin. This allows the SPIx module to be configured for a receive-only mode of operation. The SDOx pin will be controlled by the respective port function if the DISSDO bit is set.

The DISSDO function is applicable to all SPI operating modes.

#### 20.3.5 Framed SPI Modes

The module supports a very basic framed SPI protocol while operating in either Master mode or Slave mode. The following features are provided in the SPI module to support Framed SPI modes:

- The FRMEN control bit (SPIxCON<14>), enables Framed SPI modes and causes the SSx pin to be used as a frame synchronization pulse input or output pin. The state of the SSEN bit (SPIxCON<7>) is ignored.

- The SPIFSD control bit (SPIxCON<13>), determines whether the SSx pin is an input or an output (i.e., whether the module receives or generates the frame synchronization pulse).

- The frame synchronization pulse is an active high pulse for a single SPI clock cycle.

The following two Framed SPI modes are supported by the SPI module:

- Frame Master Mode: The SPI module gen<u>erates</u> the frame synchronization pulse and provides this pulse to other devices at the SSx pin.

- Frame Slave Mode: The SPI module uses a frame synchronization pulse received at the SSx pin.

The Framed SPI modes are supported in conjunction with the Master and Slave modes. Therefore, the following four framed SPI configurations are available to the user:

- SPI Master mode and Frame Master mode

- SPI Master mode and Frame Slave mode

- · SPI Slave mode and Frame Master mode

- · SPI Slave mode and Frame Slave mode

These four modes determine whether or not the SPIx module generates the serial clock and the frame synchronization pulse.

dsPIC30F [SPI Master, Frame Master] Processor 2 **SDOx** SDIx Serial Receive Buffer Serial Receive Buffer (SPIxRXB) (SPIxRXB) **SDIx** SDOx Shift Register Shift Register (SPIxŠR) (SPIxŠR) **MSbit** LSbit **MSbit** Serial Transmit Buffer Serial Transmit Buffer (SPIxTXB) (SPIxTXB) Serial Clock SPI Buffer **SCKx** SPI Buffer **SCKx** (SPIxBUF) (SPIxBUF) SSx SSx Frame Sync. Note 1: In Framed SPI modes, the SSx pin is used to transmit/receive the frame synchronization pulse. 2: Framed SPI modes require the use of all four pins (i.e., using the SSx pin is not optional). 3: The SPIxTXB and SPIxRXB registers are memory mapped to the SPIxBUF register.

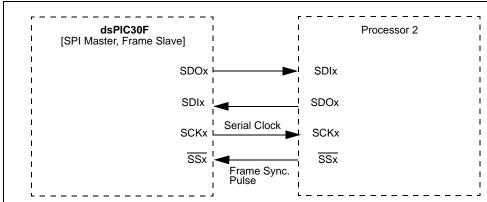

Figure 20-7: SPI Master, Frame Master Connection Diagram

### 20.3.5.1 SCKx in Framed SPI Modes

When FRMEN bit (SPIxCON<14>) = 1 and MSTEN bit (SPIxCON<5>) = 1, the SCKx pin becomes an output and the SPI clock at SCKx becomes a free running clock.

When FRMEN = 1 and MSTEN = 0, the SCKx pin becomes an input. The source clock provided to the SCKx pin is assumed to be a free running clock.

The polarity of the clock is selected by the CKP bit (SPIxCON<6>). The CKE bit (SPIxCON<8>) is not used for the Framed SPI modes and should be programmed to '0' by the user software.

When CKP = 0, the frame sync pulse output and the SDOx data output change on the rising edge of the clock pulses at the SCKx pin. Input data is sampled at the SDIx input pin on the falling edge of the serial clock.

When CKP = 1, the frame sync pulse output and the SDOx data output change on the falling edge of the clock pulses at the SCKx pin. Input data is sampled at the SDIx input pin on the rising edge of the serial clock.

#### 20.3.5.2 SPIx Buffers in Framed SPI Modes

When SPIFSD bit (SPIxCON<13>) = 0, the SPIx module is in the Frame Master mode of operation. In this mode, the frame sync pulse is initiated by the module when the user software writes the transmit data to SPIxBUF location (thus writing the SPIxTXB register with transmit data). At the end of the frame sync pulse, the SPIxTXB register is transferred to the SPIxSR register and data transmission/reception begins.

When SPIFSD bit (SPIxCON<13>) = 1, the module is in the Frame Slave mode. In this mode, the frame sync pulse is generated by an external source. When the module samples the frame sync pulse, it will transfer the contents of the SPIxTXB register to the SPIxSR register and data transmission/reception begins. The user must make sure that the correct data is loaded into the SPIxBUF register for transmission before the frame sync pulse is received.

**Note:** Receiving a frame sync pulse starts a transmission, regardless of whether data was written to SPIxBUF. If no write was performed, the old contents of SPIxTXB are transmitted.

#### 20.3.5.3 SPI Master Mode and Frame Master Mode

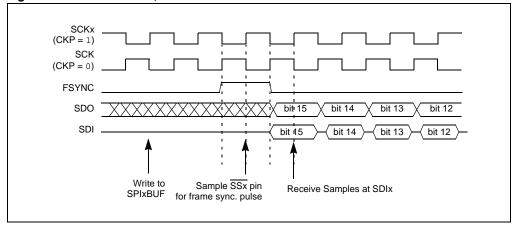

This Framed SPI mode is enabled by setting the MSTEN bit (SPIxCON<5>) and FRMEN bit (SPIxCON<14>) to '1' and the SPIFSD bit (SPIxCON<13>) to '0'. In this mode, the serial clock will be output continuously at the SCKx pin, regardless of whether the module is transmitting. When the SPIxBUF register is written, the SSx pin will be driven high on the next transmit edge of the SCKx clock. The SSx pin will be high for one SCKx clock cycle. The module will start transmitting data on the next transmit edge of the SCKx, as shown in Figure 20-8. A connection diagram indicating signal directions for this operating mode is shown in Figure 20-7.

- **Note 1:** In Framed SPI modes, the  $\overline{SSx}$  pin is used to transmit/receive the frame synchronization pulse.

- 2: Framed SPI modes require the use of all four pins (i.e., Using the SSx pin is not optional).

# Serial F Interfa

#### 20.3.5.4 SPI Master Mode and Frame Slave Mode

This <u>Framed SPI</u> mode is enabled by setting the MSTEN, FRMEN and the SPIFSD bits to '1'. The <u>SSx</u> pin is an input, and it is sampled on the sample edge of the SPI clock. When it is sampled high, data will be transmitted on the subsequent transmit edge of the SPI clock, as shown in Figure 20-9. The interrupt flag, SPIxIF, is set when the transmission is complete. The user must make sure that the correct data is loaded into the SPIxBUF register for transmission before the signal is received at the <u>SSx</u> pin. A connection diagram indicating signal directions for this operating mode is shown in Figure 20-10.

Figure 20-9: SPI Master, Frame Slave

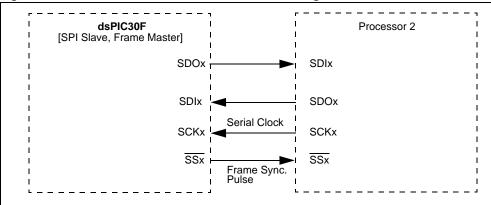

Figure 20-10: SPI Master, Frame Slave Connection Diagram

- Note 1: In Framed SPI modes, the SSx pin is used to transmit/receive the frame synchronization pulse.

- 2: Framed SPI modes require the use of all four pins (i.e., Using the SSx pin is not optional).

#### 20.3.5.5 SPI Slave Mode and Frame Master Mode

This Framed SPI mode is enabled by setting the MSTEN bit (SPIxCON<5>) to '0', the FRMEN bit (SPIxCON<14>) to '1' and the SPIFSD bit (SPIxCON<13>) to '0'. The input SPI clock will be continuous in the Slave mode. The SSx pin will be an output when the SPIFSD bit is low. Therefore, when the SPIBUF is written, the module will drive the SSx pin high on the next transmit edge of the SPI clock. The SSx pin will be driven high for one SPI clock cycle. Data will start transmitting on the next SPI clock transmit edge. A connection diagram indicating signal directions for this operating mode is shown in Figure 20-11.

Figure 20-11: SPI Slave Frame Master Connection Diagram

- **Note 1:** In Framed SPI modes, the  $\overline{SSx}$  pin is used to transmit/receive the frame synchronization pulse.

- 2: Framed SPI modes require the use of all four pins (i.e., Using the SSx pin is not optional).

# 20.3.5.6 SPI Slave Mode and Frame Slave Mode

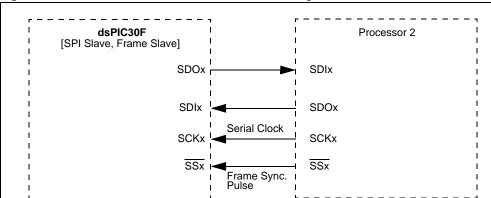

This Framed SPI mode is enabled by setting the MSTEN bit (SPIxCON<5>) to '0', the FRMEN bit (SPIxCON<14>) to '1' and the SPIFSD bit (SPIxCON<13>) to '1'. Therefore, both the SCKx and SSx pins will be inputs. The SSx pin will be sampled on the sample edge of the SPI clock. When SSx is sampled high, data will be transmitted on the next transmit edge of SCKx. A connection diagram indicating signal directions for this operating mode is shown in Figure 20-12.

Figure 20-12: SPI Slave Frame Slave Connection Diagram

Note 1: In Framed SPI modes, the SSx pin is used to transmit/receive the frame synchronization pulse.

2: Framed SPI modes require the use of all four pins (i.e., Using the SSx pin is not optional).

In the Master mode, the clock provided to the SPI module is the instruction cycle (TcY). This clock will then be prescaled by the primary prescaler (specified by PPRE<1:0> bits (SPIxCON<1:0>)), and the secondary prescaler (specified by SPRE<2:0> bits (SPIxCON<4:2>)). The prescaled instruction clock becomes the serial clock and is provided to external devices via the SCKx pin.

**Note:** The SCKx signal clock is not free running for normal SPI modes. It will only run for eight or 16 pulses when the SPIxBUF is loaded with data. It will however, be continuous for Framed modes.

Equation 20-1 can be used to calculate the SCKx clock frequency as a function of the primary and secondary prescaler settings.

## Equation 20-1:

$$FSCK = \frac{FCY}{Primary Prescaler \bullet Secondary Prescaler}$$

Some sample SPI clock frequencies (in kHz) are shown in the table below:

Table 20-1: Sample SCKx Frequencies

| Fcy = 30 MHz               |      |       | Secondar | ry Prescale | r Settings |      |

|----------------------------|------|-------|----------|-------------|------------|------|

| 1 C1 = 30 WI12             |      | 1:1   | 2:1      | 4:1         | 6:1        | 8:1  |

| Primary Prescaler Settings | 1:1  | 30000 | 15000    | 7500        | 5000       | 3750 |

|                            | 4:1  | 7500  | 3750     | 1875        | 1250       | 938  |

|                            | 16:1 | 1875  | 938      | 469         | 313        | 234  |

|                            | 64:1 | 469   | 234      | 117         | 78         | 59   |

| FCY = 5 MHz                |      |       |          |             |            |      |

| Primary Prescaler Settings | 1:1  | 5000  | 2500     | 1250        | 833        | 625  |

|                            | 4:1  | 1250  | 625      | 313         | 208        | 156  |

|                            | 16:1 | 313   | 156      | 78          | 52         | 39   |

|                            | 64:1 | 78    | 39       | 20          | 13         | 10   |

Note: SCKx frequencies are shown in kHz.

**Note:** Not all clock rates are supported. For further information, refer to the SPI timing specifications in the specific device data sheet.

**20**

Serial Periphera Interface (SPI)

# 20.5 Operation in Power-Saving Modes

The dsPIC30F family of devices has three Power modes, one operational mode and two power-saving modes invoked by the PWRSAV instruction. Depending on the SPIx mode selected, entry into a Power-Saving mode may also affect the operation of the module.

- Operational mode: The core and peripherals are running

- Power-saving modes: There are two power-saving modes supported in the dsPIC30F family of devices

- Sleep mode: Device clock source and entire device is shut down. Example 20-1 illustrates the code sequence for achieving the Sleep mode.

# Example 20-1: Code Sequence for Sleep Mode

```

;include p30fxxxx.inc device file

PWRSAV #SLEEP_MODE

```

- Idle mode: Device clock is operational, CPU and selected peripherals are shut down. Example 20-2 illustrates the code sequence for achieving the Idle mode.

#### Example 20-2: Code Sequence for Idle Mode.

```

;include p30fxxxx.inc device file

PWRSAV #IDLE_MODE

```

## 20.5.1 Sleep Mode

When the device enters Sleep mode, the system clock is disabled.

#### 20.5.1.1 Master Mode Operation

The following are consequences of entering the Sleep mode when the SPIx module is configured for Master mode of operation:

- The baud rate generator in the SPIx module stops and resets.

- If the SPIx module enters the Sleep mode in the middle of a transmission/reception, the transmission/reception is aborted. Since there is no automatic way to prevent an entry into Sleep mode if a transmission or reception is pending, the user software must synchronize entry into Sleep with SPI module operation, to avoid aborted transmissions.

- The transmitter and receiver will stop in Sleep. The transmitter or receiver does not continue with a partially completed transmission at wake-up.

## 20.5.1.2 Slave Mode Operation

Since the clock pulses at SCKx are externally provided for the Slave mode, the module will continue to function in Sleep mode. It will complete any transactions during the transition into Sleep. On completion of a transaction, the SPIRBF flag is set. Consequently, the SPIxIF bit will be set. If SPI interrupts are enabled (SPIxIE = 1), the device will wake from Sleep. If the SPI interrupt priority level is greater than the present CPU priority level, code execution will resume at the SPIx interrupt vector location. Otherwise, code execution will continue with the instruction following the PWRSAV instruction that previously invoked Sleep mode. The module is not reset on entering Sleep mode if it is operating as a slave device.

Register contents are not affected when the SPIx module is going into or coming out of Sleep mode.

#### 20.5.2 Idle Mode

When the device enters the Idle mode, the system clock sources remain functional. The SPISIDL bit (SPIxSTAT<13>) selects whether the module will stop or continue functioning on Idle.

- If SPISIDL = 1, the SPI module will stop communication on entering Idle mode. It will

operate in the same manner as it does in Sleep mode.

- If SPISID = 0 (default selection), the module will continue operation in Idle mode.

20

Table 20-2: Pins Associated with the SPI Modules

| Pin Name   | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                                                                                                          |

|------------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCK1       | I/O         | CMOS           | SPI1 module Clock Input or Output                                                                                                                                                                                                                                                    |

| SCK2       | I/O         | CMOS           | SPI2 module Clock Input or Output                                                                                                                                                                                                                                                    |

| SDI1       | I           | CMOS           | SPI1 module Data Receive pin                                                                                                                                                                                                                                                         |

| SDI2       | I           | CMOS           | SPI2 module Data Receive pin                                                                                                                                                                                                                                                         |

| SDO1       | 0           | CMOS           | SPI1 module Data Transmit pin                                                                                                                                                                                                                                                        |

| SDO2       | 0           | CMOS           | SPI2 module Data Transmit pin                                                                                                                                                                                                                                                        |

| SS1        | I/O         | CMOS           | SPI1 module Slave Select Control pin:  • Used to enable transmit/receive in Slave mode, if SSEN bit (SPI1CON<7>) has been set to '1'                                                                                                                                                 |

|            |             |                | Used as Frame Sync I/O Pulse when FRMEN and<br>SPIFSD bits (SPI1CON<14:13>) are set to '11' or '10'                                                                                                                                                                                  |

| <u>SS2</u> | I/O         | CMOS           | <ul> <li>SPI2 module Slave Select Control pin:</li> <li>Used to enable transmit/receive in Slave mode, if SSEN bit (SPI2CON&lt;7&gt;) has been set to '1'</li> <li>Used as Frame Sync I/O Pulse when FRMEN and SPIFSD bits (SPI2CON&lt;14:13&gt;) are set to '11' or '10'</li> </ul> |

# 20.6 Register Maps

Table 20-3, Table 20-4 and Table 20-5 maps the bit function for the SFRs associated with the SPI modules.

# Table 20-3: SPI1 Register Map

| SFR<br>Name | Bit 15 | Bit 14                                                                      | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0               | Reset State         |

|-------------|--------|-----------------------------------------------------------------------------|---------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|-------|--------|---------------------|---------------------|

| SPI1STAT    | SPIEN  | _                                                                           | SPISIDL | _      | _      | _      | _     |       | _     | SPIROV |       | _     | _     |       | SPITBF | SPIRBF              | 0000 0000 0000 0000 |

| SPI1CON     | _      | FRMEN                                                                       | SPIFSD  | _      | DISSDO | MODE16 | SMP   | CKE   | SSEN  | CKP    | MSTEN | SPRE2 | SPRE1 | SPRE0 | PPRE1  | PPRE0               | 0000 0000 0000 0000 |

| SPI1BUF     |        | Transmit and Receive Buffer Address shared by SPI1TXB and SPI1RXB registers |         |        |        |        |       |       |       |        |       |       |       |       |        | 0000 0000 0000 0000 |                     |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# Table 20-4: SPI2 Register Map

| SFR<br>Name | Bit 15 | Bit 14                                                                      | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2               | Bit 1  | Bit 0  | Reset State         |

|-------------|--------|-----------------------------------------------------------------------------|---------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-------|---------------------|--------|--------|---------------------|

|             |        |                                                                             |         |        |        |        |       |       |       |        |       |       |       |                     |        |        |                     |

| SPI2STAT    | SPIEN  | _                                                                           | SPISIDL | _      | _      | _      | _     | 1     | I     | SPIROV | 1     | _     | _     | _                   | SPITBF | SPIRBF | 0000 0000 0000 0000 |

| SPI2CON     | 1      | FRMEN                                                                       | SPIFSD  | _      | DISSDO | MODE16 | SMP   | CKE   | SSEN  | CKP    | MSTEN | SPRE2 | SPRE1 | SPRE0               | PPRE1  | PPRE0  | 0000 0000 0000 0000 |

| SPI2BUF     |        | Transmit and Receive Buffer Address shared by SPI2TXB and SPI2RXB registers |         |        |        |        |       |       |       |        |       |       |       | 0000 0000 0000 0000 |        |        |                     |

dsPIC30F Family Reference Manual

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# Table 20-5: SPI Module Related Interrupt Registers

|             | to 20 or an order of the contract the contract to the contract |          |           |        |        |        |             |        |        |       |            |        |         |         |            |        |                     |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|--------|--------|--------|-------------|--------|--------|-------|------------|--------|---------|---------|------------|--------|---------------------|

| SFR<br>Name | Bit 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Bit 14   | Bit 13    | Bit 12 | Bit 11 | Bit 10 | Bit 9       | Bit 8  | Bit 7  | Bit 6 | Bit 5      | Bit 4  | Bit 3   | Bit 2   | Bit 1      | Bit 0  | Reset State         |

| INTCON1     | NSTDIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1        | 1         |        | I      | OVATE  | OVBTE       | COVTE  |        | 1     | 1          | SWTRAP | OVRFLOW | ADDRERR | STKERR     | 1      | 0000 0000 0000 0000 |

| INTCON2     | ALTIVT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DISI     | 1         |        | I      | 1      | LEV8F       | 1      | 1      | 1     | 1          | INT4EP | INT3EP  | INT2EP  | INT1EP     | INT0EP | 0000 0000 0000 0000 |

| IFS0        | CNIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MI2CIF   | SI2CIF    | NVMIF  | ADIF   | U1TXIF | U1RXIF      | SPI1IF | T3IF   | T2IF  | OC2IF      | IC2IF  | T1IF    | OC1IF   | IC1IF      | INT0   | 0000 0000 0000 0000 |

| IFS1        | IC6IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | IC5IF    | IC4IF     | IC3IF  | C1IF   | SPI2IF | U2TXIF      | U2RXIF | INT2IF | T5IF  | T4IF       | OC4IF  | OC3IF   | IC8IF   | IC7IF      | INT1IF | 0000 0000 0000 0000 |

| IEC0        | CNIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MI2CIE   | SI2CIE    | NVMIE  | ADIE   | U1TXIE | U1RXIE      | SPI1IE | T3IE   | T2IE  | OC2IE      | IC2IE  | T1IE    | OC1IE   | IC1IE      | INT0IE | 0000 0000 0000 0000 |

| IEC1        | IC6IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | IC5IE    | IC4IE     | IC3IE  | C1IE   | SPI2IE | U2TXIE      | U2RXIE | INT2IE | T5IE  | T4IE       | OC4IE  | OC3IE   | IC8IE   | IC7IE      | INT1IE | 0000 0000 0000 0000 |

| IPC2        | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | ADIP<2:0> |        | I      | U      | 1TXIP<2:0   | >      | 1      | U     | 1RXIP<2:0  | )>     | 1       | S       | PI1IP<2:0> |        | 0100 0100 0100 0100 |

| IPC6        | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CAID 0:0 |           |        | -      | 5      | SPI2IP<2:0: | >      | -      | U     | 12TXIP<2:0 | )>     | -       | U       | 2RXIP<2:0> | >      | 0100 0100 0100 0100 |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Shaded bits are not applicable to the SPI module. For full descriptions of these bits see Section 6. "Interrupts" (DS70053) of the "dsPIC30F Family Reference Manual".

# Section 20. Serial Peripheral Interface (SPI)

#### 20.7 **Related Application Notes**

This section lists application notes that are related to this section of the manual. These application notes may not be written specifically for the dsPIC30F product family, but the concepts are pertinent and could be used with modification and possible limitations. The current application notes related to the SPI module are:

Title Application Note #

Interfacing Microchip's MCP41XXX/MCP42XXX Digital Potentiometers to a PIC® Microcontroller AN746

Interfacing Microchip's MCP3201 Analog-to-Digital Converter to the

PIC® Microcontroller

AN719

Please visit the Microchip web site (www.microchip.com) for additional Application Note: Notes and code examples for the dsPIC30F family of devices.

# 20.8 Revision History

#### Revision A

This is the initial released revision of this document.

#### Revision B

This revision reflects editorial and technical content changes for the dsPIC30F Serial Peripheral Interface (SPI) module.

#### **Revision C**

There were no technical content revisions to this section of the manual. However, this section was updated to reflect Revision C throughout the manual.

#### **Revision D**

In Figure 20-3, the fourth clock mode of SCKx has been updated to CKP = 1, CKE = 1. Updated 1:1 primary prescaler setting information for 1:1 and 2:1 secondary prescaler in Table 20-1.

# Revision E (January 2010)

This revision incorporates the following updates:

- · Figures:

- Replaced the existing diagram in Figure 20-8.

- Updated the label [SPI Master, Frame Slave] as [SPI Slave Frame Slave] in Figure 20-12.

- · Note:

- Deleted the following note in **20.1 "Introduction"**: The SPI module can be configured to operate using 3 or 4 pins. In the 3-pin mode, the SSx pin is not used.

- Added a note with information to customers for utilizing family reference manual sections and data sheets as a joint reference (see note above **20.1** "Introduction").

- · Register Map:

- Removed the Address column in the following register maps: SPI1 Register Map (seeTable 20-3), SPI2 Register Map (see Table 20-4), SPI Module Related Interrupt Registers (see Table 20-5).

- Added Legend section in the following register maps: SPI1 Register Map (see Table 20-3), SPI2 Register Map (see Table 20-4), SPI Module Related Interrupt Registers (see Table 20-5).

- Additional minor corrections such as language and formatting updates are incorporated throughout the document.