AC410

Application Note

Using AES System Services in SmartFusion2 and

IGLOO2 Devices - Libero SoC v11.8

Power Matters.\*

Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo,

CA 92656 USA

Within the USA: +1 (800) 713-4113

Outside the USA: +1 (949) 380-6100

Fax: +1 (949) 215-4996

Email: sales.support@microsemi.com

www.microsemi.com

© 2017 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

### **About Microsemi**

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

### **Contents**

| 1 | Revisi | ion His         | tory                                                   | 1  |

|---|--------|-----------------|--------------------------------------------------------|----|

|   | 1.1    | Revisio         | n 6.0                                                  | 1  |

|   | 1.2    | Revisio         | n 5.0                                                  | 1  |

|   | 1.3    | Revisio         | n 4.0                                                  | 1  |

|   | 1.4    |                 | n 3.0                                                  |    |

|   | 1.5    |                 | n 2.0                                                  |    |

|   | 1.6    |                 | n 1.0                                                  |    |

| 2 | Using  | AES S           | System Services in SmartFusion2 and IGLOO2 Devices     | 2  |

|   | 2.1    |                 | Requirements                                           |    |

|   | 2.2    | •               | gine                                                   |    |

|   |        | 2.2.1           | AES Mode of Operation                                  |    |

|   | 2.3    | SmartF          | usion2 and IGLOO2 Cryptographic Block                  | 4  |

|   |        | 2.3.1           | System Controller Block in SmartFusion2 Devices        | 4  |

|   |        | 2.3.2           | System Controller Block in IGLOO2                      |    |

|   | 2.4    | Using A         | SES Services in SmartFusion2 and IGLOO2 Devices        | 6  |

|   | 2.5    | Design          | Description                                            | 9  |

|   | 2.6    | Design          | Example - Using AES Services in SmartFusion2 Devices   |    |

|   |        | 2.6.1           | Hardware Implementation                                |    |

|   |        | 2.6.2           | Software Implementation                                |    |

|   |        | 2.6.3           | Running the Design                                     |    |

|   | 2.7    | Design<br>2.7.1 | Example - Using AES Services in IGLOO2 Devices         | 15 |

|   |        | 2.7.1           | Running the Design                                     |    |

|   | 2.8    |                 | AC Example                                             |    |

|   | 2.9    | Design          | Example - CBC-MAC                                      | 18 |

|   |        | 2.9.1           | Design Example - Using CBC-MAC in SmartFusion2 Devices |    |

|   |        | 2.9.2           | Design Example - Using CBC-MAC in IGLOO2 Devices       | 20 |

|   | 2.10   | Design          | and Programming Files                                  | 21 |

|   | 2.11   | Conclus         | sion                                                   | 21 |

## **Figures**

| Figure 1  | AES Encryption Algorithm (128-bit Cipher Key)                     | 3  |

|-----------|-------------------------------------------------------------------|----|

| Figure 2  | System Controller Block in SmartFusion2 Devices                   | 5  |

| Figure 3  | System Controller Block in IGLOO2 Devices                         | 6  |

| Figure 4  | AES Service Flow Diagram for IGLOO2 Devices                       | 8  |

| Figure 5  | AES Service Flow Diagram for SmartFusion2 Devices                 | 9  |

| Figure 6  | SmartFusion2 AES System Service Design Example                    | 10 |

| Figure 7  | FlashPro Programmer Number                                        | 11 |

| Figure 8  | SmartFusion2 Security Evaluation Kit (M2S-EVAL-KIT) Board         | 12 |

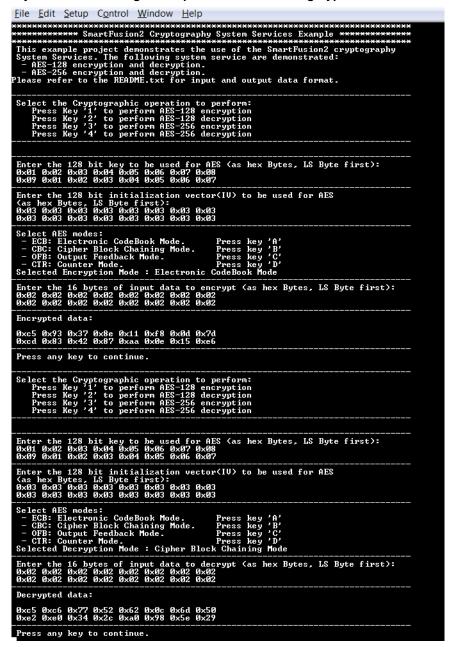

| Figure 9  | AES System Service Design Example in ECB Mode Using HyperTerminal | 13 |

| Figure 10 | AES System Service Design Example in CBC Mode Using HyperTerminal | 14 |

| Figure 11 | AES System Service Design Example in OFB Mode Using HyperTerminal | 15 |

| Figure 12 | IGLOO2 AES System Service Design Example                          | 16 |

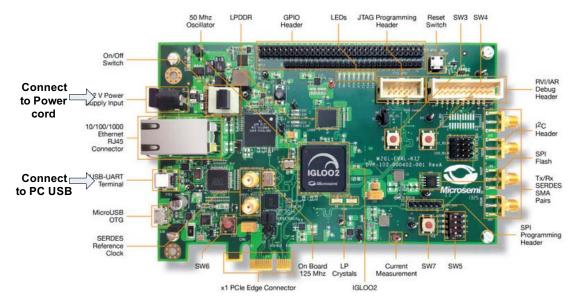

| Figure 13 | IGLOO2 Evaluation Kit Board                                       | 17 |

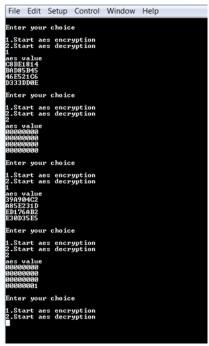

| Figure 14 | HyperTerminal Showing CoreSysService Design Output                | 17 |

| Figure 15 | CBC-MAC Computation Diagram                                       | 18 |

| Figure 16 | HyperTerminal showing CBC-MAC Design in a SmartFusion2 Device     | 19 |

| Figure 17 | IGLOO2 CBC-MAC Design Example                                     | 20 |

| Figure 18 | CBC-MAC of a Message                                              | 20 |

### **Tables**

| Table 1 | Design Requirements for SmartFusion2 Devices |

|---------|----------------------------------------------|

| Table 2 | Design Requirements for IGLOO2 Devices       |

| Table 3 | AES128DATAPTR Structure                      |

|         | AES Command Value                            |

| Table 5 | 128-bit AES Service Response Parameters      |

| Table 6 | Service Response Status Codes                |

### 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

### 1.1 **Revision 6.0**

The following changes were made in revision 6.0 of this document.

- A footnote about SoftConsole was removed from the SmartFusion2 design requirements. For more information, see Design Requirements, page 2.

- The procedure to run the design was updated. For more information, see Running the Design, page 11.

### 1.2 **Revision 5.0**

The document was updated for Libero v11.7 software release (SAR 76152).

### 1.3 **Revision 4.0**

The document was updated for Libero v11.6 software release (SAR 71462).

### 1.4 **Revision 3.0**

The document was updated for Libero v11.5 software release (SAR 64229).

### 1.5 Revision 2.0

The following changes were made in revision 2.0 of this document.

- The document was updated for Libero version 11.4 (SAR 61019).

- Updates were made to maintain the style and consistency of the document.

### 1.6 **Revision 1.0**

Revision 1.0 was the first publication of this document.

# 2 Using AES System Services in SmartFusion2 and IGLOO2 Devices

AES is an encryption solution developed to achieve several rapidly-evolving security concerns that have arisen within the computer and embedded semiconductor industries. Selected devices of the SmartFusion®2 SoC FPGA and IGLOO®2 FPGA families allow the user to access the built-in AES engines and use AES encryption and decryption operation. These devices are marked as S (Data and Design Security) in the device part number. The AES engine in the SmartFusion2 and IGLOO2 devices is part of the Cryptographic Services block and resides in the system controller. The AES engine in the SmartFusion2 and IGLOO2 devices can accept 128-bit plain text input word and generates the corresponding 128-bit ciphertext output word using a supplied 128-/256-bit AES key. It also provides a reverse function by generating plaintext from the supplied ciphertext using the same AES key as used for encryption. The AES engine is accessible through the system services. The system services are system controller actions initiated by asynchronous events from the ARM Cortex-M3 processor in the SmartFusion2 device or a fabric master in the SmartFusion2 and IGLOO2 devices. The AES cryptographic services can be used for data security applications and can be disabled through factory or user security settings.

### 2.1 Design Requirements

The following tables list the design requirements of SmartFusion2 and IGLOO2 devices, respectively.

Table 1 • Design Requirements for SmartFusion2 Devices

| Design Requirements                                                                                                                                                          | Description                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| Hardware Requirements                                                                                                                                                        |                                     |

| SmartFusion2 Security Evaluation Kit (M2S-EVAL-KIT):  – 12 V adapter (provided along with the kit)  – FlashPro4 programmer (provided along with the kit)  – M2S090TS-1FGG484 | Rev D or later                      |

| Host PC or Laptop                                                                                                                                                            | Any 64-bit Windows operating system |

| Software Requirements                                                                                                                                                        |                                     |

| Libero® System-on-Chip (SoC)                                                                                                                                                 | v11.8                               |

| SoftConsole                                                                                                                                                                  | 4.0                                 |

### Table 2 • Design Requirements for IGLOO2 Devices

| Hardware Requirements  IGLOO2 Evaluation Kit:  - 12 V wall-mounted power supply (provided along with the kit)  - FlashPro4 programmer (provided along with the kit)  - M2GL090TS-1FGG484  Host PC or Laptop  Any 64-bit Windows Operating System  Software Requirements        | Design Requirements                                                                                                                          | Description                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| <ul> <li>12 V wall-mounted power supply (provided along with the kit)</li> <li>FlashPro4 programmer (provided along with the kit)</li> <li>M2GL090TS-1FGG484</li> <li>Host PC or Laptop</li> <li>Any 64-bit Windows Operating System</li> <li>Software Requirements</li> </ul> | Hardware Requirements                                                                                                                        |                                     |

| Software Requirements                                                                                                                                                                                                                                                          | <ul> <li>12 V wall-mounted power supply (provided along with the kit)</li> <li>FlashPro4 programmer (provided along with the kit)</li> </ul> | Rev D or later                      |

| ·                                                                                                                                                                                                                                                                              | Host PC or Laptop                                                                                                                            | Any 64-bit Windows Operating System |

| 11 00                                                                                                                                                                                                                                                                          | Software Requirements                                                                                                                        |                                     |

| Libero SoC V11.8                                                                                                                                                                                                                                                               | Libero SoC                                                                                                                                   | v11.8                               |

Note: The IGLOO2 design uses the M2GL090TS-1FGG484 device in the IGLOO2 Evaluation Kit. However, the official IGLOO2 Evaluation Kit uses M2GL010T-1FGG484 device. To run the application note design on an M2GL010T-1FGG484 device, refer to the KB5659 for migrating from M2GL090TS-1FGG484 to M2GL010T-1FGG484.

### 2.2 AES Engine

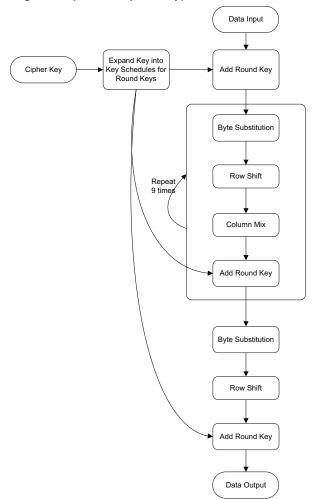

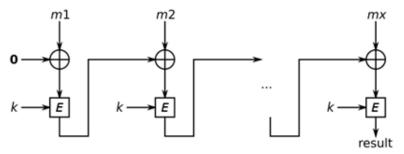

The AES engine uses the Rijndael algorithm with national institute of standards and technology (NIST) approved parameters as described in federal information processing standards (FIPS) publication (PUB) 197. The AES encryption algorithm receives 128-bit of plaintext data and 128-/192-/256-bit of a cipher key as input. After several rounds of computation, it produces 128-bit enciphered version of the original plaintext data as output. The key size used for an AES cipher determines the number of transformation rounds to convert the input into the final output, ciphertext. During the rounds of the algorithm, the data bits are subjected to byte substitution, data shift operations, data mixing operations, and additional operations (XOR) with an expanded version of the original 128-/192-/256-bit cipher key. The reverse happens during the decryption operation.

The SmartFusion2 and IGLOO2 AES engine can be operated in 128-bit key mode or 256-bit key mode and supports both encryption and decryption services.

The following figure shows the AES encryption algorithm with 128-bit key.

Figure 1 • AES Encryption Algorithm (128-bit Cipher Key)

The SmartFusion2 and IGLOO2 AES engine assumes that the input data is in complete 128-bit blocks and provides the complete 128-bit output blocks. Add any padding bits to the incomplete plaintext blocks before calling the AES encryption service and remove any padding bits after receiving the results of the

AES decryption service. The input and output data format of the AES services is little-endian type. The first byte of the first block is at the lowest address and there are no word alignment requirements. In other words, consecutive bytes of the plaintext, ciphertext, and keys from the first to last are stored in order in memory from the lowest to the highest bit address.

### 2.2.1 AES Mode of Operation

The mode of operation describes how to apply the ciphers single-block operation repeatedly to securely transform the data that is larger than a block. The built-in system services are designed to support the following cipher operating modes as recommended in NIST Special Publication 800-38A, recommendation for Block Cipher Modes of Operation:

#### 2.2.1.1 Electronic Codebook

The electronic codebook (ECB) mode is a confidentiality mode that features, for a given key, the assignment of a fixed ciphertext block to each plaintext block, analogous to the assignment of code words in a codebook. It is the simplest encryption mode. The message is divided into blocks and each block is encrypted separately. Identical plaintext blocks are encrypted into identical ciphertext blocks; thus, it does not hide data patterns well.

### 2.2.1.2 Cipher-Block Chaining

The cipher block chaining (CBC) mode features the combination (chaining) of the plaintext blocks with the previous ciphertext blocks. To make each message unique, an initialization vector (IV) must be used in the first block. The IV need not to be secret, but it must be unpredictable.

### 2.2.1.3 Output Feedback

The output feedback (OFB) features the iteration of the forward cipher on an IV to generate a sequence of output blocks that are XORed with the plaintext to produce the ciphertext and vice-versa. The OFB mode requires a nonce IV, that is, the IV must be unique for each execution of the mode under the given key.

#### 2.2.1.4 Counter

The counter (CTR) mode features the application of the forward cipher to a set of input blocks, called counters, to produce a sequence of output blocks that are XORed with the plaintext to produce the ciphertext and vice-versa. The sequence of counters must have the property that each block in the sequence is different from every other block, thus the IV should be a nonce and must be unique for each execution of the mode under the given key.

In the SmartFusion2 and IGLOO2 devices, the OPMODE parameter specifies the cipher operating mode, refer to Table 3, page 7. The IV parameter used during the AES system service specifies the IV.

Refer to Using AES Services in SmartFusion2 and IGLOO2 Devices, page 6 for more information.

### 2.3 SmartFusion2 and IGLOO2 Cryptographic Block

In the SmartFusion2 and IGLOO2 devices, the AES engine is part of this Cryptographic Services block that resides in System Controller.

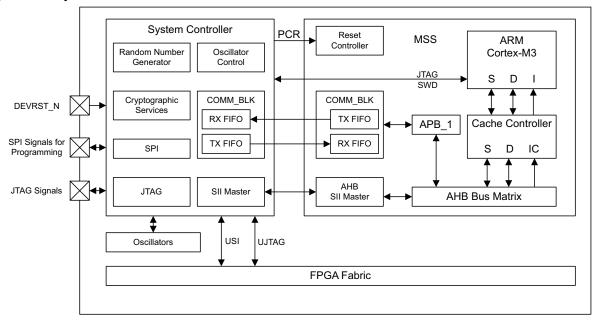

### 2.3.1 System Controller Block in SmartFusion2 Devices

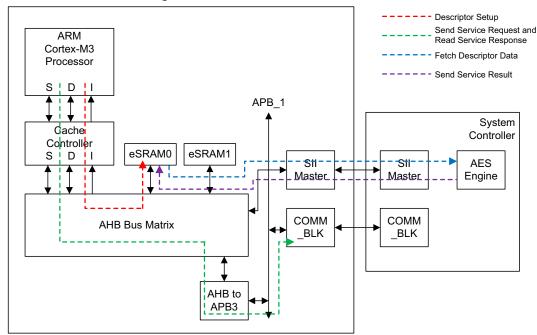

The Cryptographic Services block can be accessed through the communication block (COMM\_BLK). There are two COMM\_BLK instances: one in the microcontroller subsystem (MSS) that the user interfaces with and the other that communicates with the first block that is located in the system controller. The COMM\_BLK consists an APB interface, eight byte transmit FIFO, and eight byte receive FIFO. The COMM\_BLK provides a bi-directional message passing facility between the MSS and the system controller. The AES system services are initiated using the COMM\_BLK in the MSS, which can be read or write by any master on the AMBA high performance bus (AHB) matrix; typically either the Cortex-M3 processor or a design in the FPGA fabric (also known as a fabric master). The system controller receives the command through the COMM\_BLK in the system controller. The system controller uses the SII master, an MSS bus master controlled by the system controller, to get the additional details and options of the AES command at an address provided in the original COMM\_BLK command, pointing where this structured data has been stored in the memory before invoking the command. The AES

output bytes returned by the system controller are written to a memory address specified in this data structure. On completion of the requested service, the system controller returns a status message through the COMM\_BLK.

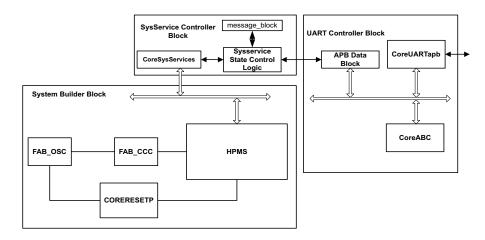

The following figure shows the system controller block in the SmartFusion2 device, where the Cryptographic Services block resides.

Figure 2 • System Controller Block in SmartFusion2 Devices

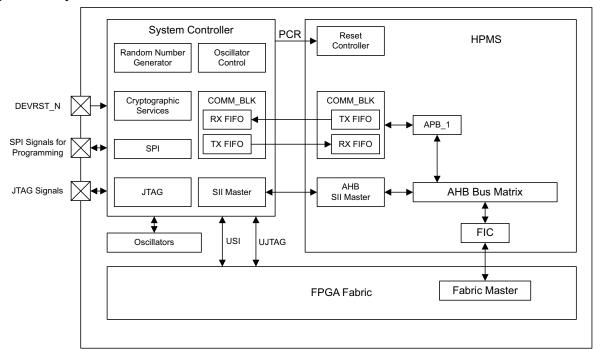

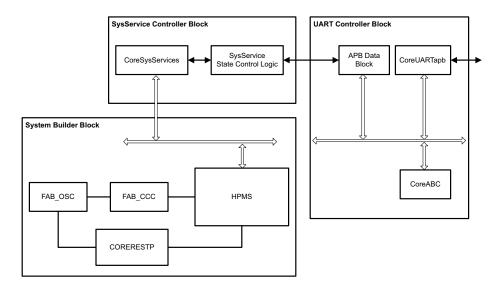

### 2.3.2 System Controller Block in IGLOO2

The architecture and uses of the AES engine are similar to the IGLOO2 device except the COMM\_BLK in the system controller communicated with COMM\_BLK in high performance memory subsystem (HPMS). It is required to use a fabric master to initiate the AES system services. Microsemi<sup>®</sup> provides the CoreSysService DirectCore IP that acts as fabric master to use the AES system services. The CoreSysServices soft IP communicates with the COMM\_BLK through one of the fabric interface controllers (FICs), sends the AES system service request, retrieves the ciphertext output, and sends to use the interface.

The following figure shows the system controller block in the IGLOO2 device.

Figure 3 • System Controller Block in IGLOO2 Devices

Refer to the *UG0450*: SmartFusion2 SoC and IGLO02 FPGA System Controller User Guide for more details on System Controller.

Also, refer to the Communication Block chapter in the *UG0331: SmartFusion2 Microcontroller* Subsystem User Guide, *UG0448: IGLOO2 FPGA High Performance Memory Subsystem User Guide* for more information on System Controller.

## 2.4 Using AES Services in SmartFusion2 and IGLOO2 Devices

In the SmartFusion2 device, the AES services can be accessed using the <code>mss\_sys\_services</code> driver in the firmware core configurator. In the IGLOO2 device, use a master in fabric to initiate the AES system services in the system controller through the COMM\_BLK. You can create any fabric master block following the steps explained below or use CoreSysServices soft IP for the AES services. CoreSysServices provides a simple user interface in one side and an AHB-Lite master interface on the FIC side to use the system services through the COMM\_BLK. You can use the IGLOO2 approach in the SmartFusion2 device also.

Following are the two options to use the AES engine in the SmartFusion2 device:

- Using firmware core through the MSS

- Using CoreSysService or own state logic as fabric master

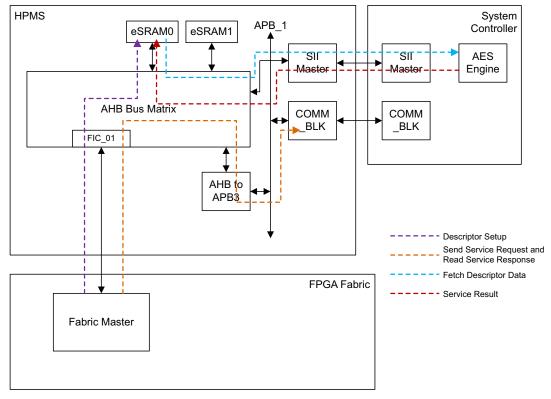

The following steps describe how to use the 128-bit AES encryption system service in the IGLOO2 device:

Set up the AES128DATAPTR descriptor in the user memory space, which contains the following 44 bytes as indicated in the following table.

Table 3 • AES128DATAPTR Structure

| Offset | Length (Bytes) | Field      | Description                                                                                                                                                                                                                                                                                                                                                                                    |

|--------|----------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 16             | KEY        | Encryption key to be used                                                                                                                                                                                                                                                                                                                                                                      |

| 16     | 16             | IV         | IV (Ignored for ECB mode)                                                                                                                                                                                                                                                                                                                                                                      |

| 32     | 2              | NBLOCKS    | Number of 128-bit blocks to process (maximum 65535)                                                                                                                                                                                                                                                                                                                                            |

| 34     | 1              | MODE       | Cipher operating mode.  - Bit 7: DECRYPT  - Bit 6: RESERVED  - Bit 1: OPMODE  - Bit 0: OPMODE  DECRYPT: If DECRYPT is 0 then the data at SRCADDRPTR field is treated as plaintext for encryption. If DECRYPT is 1 then the data at SRCADDRPTR field is treated as cipher text for decryption.  OPMODE: Defines operating mode.  - 00: ECB mode  - 01: CBC mode  - 10: OFB mode  - 11: CTR mode |

| 35     | 1              | RESERVED   | Reserved                                                                                                                                                                                                                                                                                                                                                                                       |

| 36     | 4              | DSTADDRPTR | Pointer to return data buffer                                                                                                                                                                                                                                                                                                                                                                  |

| 40     | 4              | SRCADDRPTR | Pointer to data to encrypt/decrypt                                                                                                                                                                                                                                                                                                                                                             |

- Enable the COMBLK\_INTR interrupt from the COMM\_BLK block to fabric by enabling COMBLK\_INTR\_ENBL bit (29-bit) in INTERRUPT\_ENABLE0 register at address 0x40006000.

- Setup the registers in the COMM\_BLK and send the command for 128-bit AES (0x03). The following table describes the AES command values.

Table 4 • AES Command Value

| System Service Name               | Command Value |

|-----------------------------------|---------------|

| 128-bit AES Cryptographic Service | 3             |

| 256-bit AES Cryptographic Service | 6             |

The system controller receives the command through the COMM\_BLK in the system controller. The system controller reads the key and data from the address pointer and generates the AES ciphertext test. On completion, the service system controller returns a status message through the COM-M\_BLK.

Wait for RCVOKAY bit to be set in the COMM\_BLK STATUS register.

4. Read the Word Data register in the COMM\_BLK and check the command, status code, and AES128DATAPTR descriptor pointer, as indicated in the following table.

Table 5 • 128-bit AES Service Response Parameters

| Offset | Length (Bytes) | Field         | Description                      |

|--------|----------------|---------------|----------------------------------|

| 0      | 1              | CMD = 3       | Command                          |

| 1      | 1              | STATUS        | Command status                   |

| 1      | 4              | AES128DATAPTR | Pointer to AES128DATA descriptor |

The following table lists the service response status codes.

Table 6 • Service Response Status Codes

| Status | Description                                  |

|--------|----------------------------------------------|

| 0      | Success                                      |

| 127    | HRESP error occurred during the MSS transfer |

| 253    | Not licensed                                 |

| 254    | Service disabled by factory security         |

| 255    | Service disabled by user security            |

5. Read the AES data from user memory space (at the return, data buffer address is specified in 1). The following figure shows the AES system service data flow diagram in the IGLOO2 device.

Figure 4 • AES Service Flow Diagram for IGLOO2 Devices

The steps for using the AES service in 256-bit key mode are similar to SmartFusion2. The following figure shows the system service data flow diagram while initiating the AES service from the Cortex-M3 processor.

Figure 5 • AES Service Flow Diagram for SmartFusion2 Devices

Note: You can use CoreSysServices IP in the SmartFusion2 or IGLOO2 devices and initiate the AES system service using its simple user interface. Send the AES service request with the required data/parameter to CoreSysServices IP. CoreSysServices IP performs the required steps to setup the descriptor, sends the command through the COM\_BLK to the AES service, and reads the data back from the eSRAM. Refer to the CoreSysServices Handbook for more information.

### 2.5 Design Description

This application note includes two design examples for using the AES system service:

- AES\_Services\_SF2 design example: Demonstrates 128-bit and 256-bit AES encryption and decryption in the SmartFusion2 device using the Microsemi system driver firmware code.

- AES\_Services\_IGL2 design example: Demonstrates 128-bit AES encryption and decryption in the IGLOO2 device using the Microsemi CoreSysServices IP core.

The SmartFusion2 device design is implemented on the SmartFusion2 Security Evaluation Kit (M2S-EVAL-KIT) using the M2S090TS-1FGG484 device. The IGLOO2 device design is implemented on the IGLOO2 Evaluation Kit board using the M2GL090TS-1FGG484 device.

## 2.6 Design Example - Using AES Services in SmartFusion2 Devices

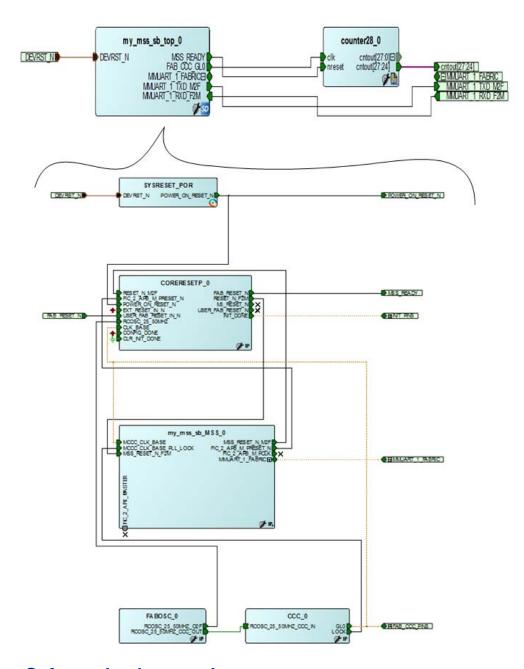

The design example consists the RC oscillator, a fabric CCC, and MSS. The fabric PLL is used to provide the base clock for the MSS. The system services are run using various C routine in the MSS, as shown in the sub-sections. In addition, a universal asynchronous receiver/transmitter (UART1) in the MSS is used to display the operation of the AES system service.

### 2.6.1 Hardware Implementation

The RC oscillator is used to generate a 50 MHz input clock and the fabric PLL is used to generate a 100 MHz clock from the RC oscillator. The 100 MHz clock is used as the base clock for the MSS. The MMUART\_1 signals are routed through the FPGA fabric for communicating with the serial terminal program. The counter block is used to show that the device is up and running.

The following figure shows a block diagram of the design example.

Figure 6 • SmartFusion2 AES System Service Design Example

### 2.6.2 Software Implementation

The software design example performs the following operations:

- 1. Initialize the System Controller Enable

- 2. Initialize MMUART\_1

- 3. Perform various cryptography services:

- Encrypt with 128-bit AES cryptography service

- Decrypt with 128-bit AES cryptography service

- Encrypt with 256-bit AES cryptography service

- Decrypt with 256-bit AES cryptography service

### 2.6.2.1 aes128\_encryption ();

The aes128\_encryption() function provides access to the SmartFusion2 AES-128 encryption cryptography service. It allows you to perform AES encryption and choose the mode of operation: ECB, CBC, OFB, or CTR mode. It allows you to specify the number of 128-bit blocks of plaintext to be processed by the AES-128 system service. It also adds the padding bits to the incomplete blocks before calling the AES system service.

### 2.6.2.2 aes128\_decryption ();

The aes128\_decryption() function provides access to the SmartFusion2 AES-128 decryption cryptography service. It allows you to perform AES decryption and choose the mode of operation: ECB, CBC, OFB, or CTR mode. It allows you to specify the number of 128-bit blocks of ciphertext to be processed by the AES-128 system service. It also adds the padding bits to the incomplete blocks before calling the AES system service.

### 2.6.2.3 aes256\_encryption ();

This function is similar to aes128\_encryption() and provides access to the SmartFusion2 AES-256 encryption cryptography service function using the 256-bit key.

### 2.6.2.4 aes256\_decryption ();

This function is similar to aes128\_decryption() and provides access to the SmartFusion2 AES-256 decryption cryptography service function using the 256-bit key.

### 2.6.3 Running the Design

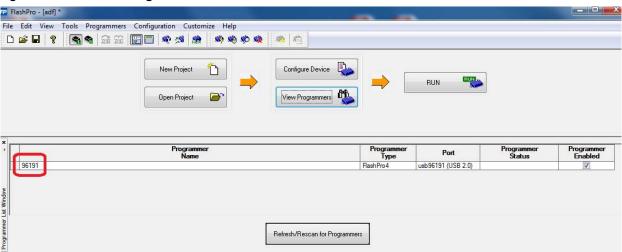

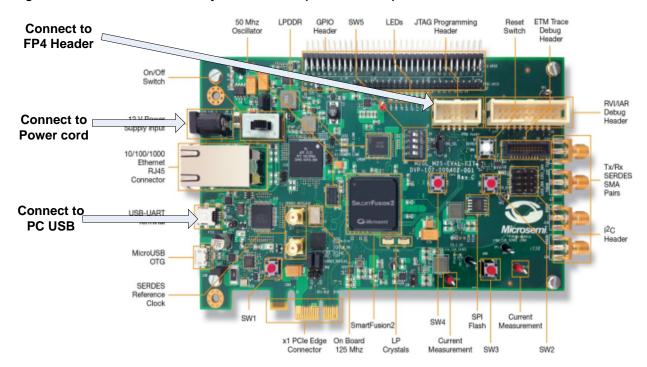

The following steps describe how to run the design example on the SmartFusion2 Security Evaluation Kit (M2S-EVAL-KIT) using the M2S090TS-1FGG484 device:

- 1. Connect the power supply to the SmartFusion2 Security Evaluation Kit (M2S-EVAL-KIT) board.

- Plug the FlashPro4 ribbon cable into JTAG Programming Header on the SmartFusion2 Security Evaluation Kit (M2S-EVAL-KIT) board.

- 3. Program the SmartFusion2 Security Evaluation Kit (M2S-EVAL-KIT) board with the provided STAPL file (refer to Design and Programming Files, page 21) using FlashPro4.

- 4. Make a note of the five-digit FlashPro 4 programmer number. To find the programmer number, open the FlashPro software while the FlashPro 4 programmer is plugged into your PC.

Figure 7 • FlashPro Programmer Number

5. Connect the host PC to the J24 connector using the USB min-B cable.

Figure 8 • SmartFusion2 Security Evaluation Kit (M2S-EVAL-KIT) Board

- Invoke the SoftConsole project, click **Debug Configurations** from the Run menu, and then click the Debugger tab.

- 7. Change the *usb* number in the following config option to match the number of your FlashPro 4 programmer (recorded during step 3):

- --command microsemi\_flashpro\_port usb96191

- 8. Click **Apply** and launch the debugger.

- 9. Start a HyperTerminal session with 57600 baud rate, 8 data bits, 1 stop bit, no parity, and no flow control. Use other serial terminal emulation programs such as PuTTY or Tera Term if HyperTerminal is not available. Refer to the *Configuring Serial Terminal Emulation Programs Tutorial* for configuring HyperTerminal, Tera Term, or PuTTY.

- 10. Run the debugger in the SoftConsole tool. The HyperTerminal window shows various options to run the AES encryption and decryption. Follow the instruction on the screen to run the example.

The following figures show the HyperTerminal.

Figure 9 • AES System Service Design Example in ECB Mode Using HyperTerminal

Figure 10 • AES System Service Design Example in CBC Mode Using HyperTerminal

```

the 128 bit key to be used for AES (as hex Bytes, LS Byte first):

0x02 0x03 0x04 0x05 0x06 0x07 0x08

0x01 0x02 0x03 0x04 0x05 0x06 0x07

the 128 bit initialization vector(IV) to be used for AES ex Bytes, LS Byte first):

Selected Decryption Mode : Cipher Block Chaining

Decrypted data:

0xc5 0xc6 0x77 0x52 0x62 0x0c 0x6d 0x50 0xe2 0xe0 0x34 0x2c 0xa0 0x98 0x5e 0x29

used for AES (as hex Bytes, LS Byte first):

3 0×23 0×23

r the 128 bit initialization vector(IU) to be used for AES

nex Bytes. LS Byte first):

0x01 0x02 0x03 0x04 0x05 0x06 0x07

0x09 0x10 0x11 0x12 0x12 0x12 0x12

IES modes:

Electronic CodeBook Mode. Press

Cipher Block Chaining Mode. Press

Output Feedback Mode. Press

Counter Mode. Press

I Encryption Mode: Output Feedback M

Enter the 16 bytes of input data to encrypt (as hex Bytes, LS Byte first):

0x12 0x23 0x34 0x45 0x67 0x78 0x89 0x0a

0x0b 0x0c 0x0d 0x0e 0x0f 0x10 0x02 0x03

Encrypted data:

0xf5 0x14 0xae 0x69 0x27 0x21 0x72 0x5a

0xe9 0x87 0xa6 0x27 0x86 0xfc 0xd3 0xe9

Press any key to continue.

```

Figure 11 • AES System Service Design Example in OFB Mode Using HyperTerminal

Note: The ASCII-Hex notation is used for input by the program so the data is more easily readable.

The data goes from the first byte to the last byte of the multi-byte message, IV, key, and so on entered or displayed from left to right (and then top to bottom, if multi-line) as shown by the terminal emulator. Each byte is represented by two ASCII characters selected by value from the ordered sixteen character set 0-9 and a-f with the leftmost ASCII character representing the first four bits of the byte (that is, bits 7:4) encoded into a hexadecimal digit having its first binary bit (bit 7) interpreted as the most significant bit, and then the resulting hexadecimal digit encoded into an 8-bit ASCII character; the rightmost ASCII character representing the following four bits (bits 3:0) are encoded with the last binary bit of the byte (bit 0) being interpreted as the least significant of the second hexadecimal digit. The AES output is the Hex data displayed in endian order.

## 2.7 Design Example - Using AES Services in IGLOO2 Devices

The design consists the IGLOO2 HPMS, the on-chip 50 MHz RC oscillator, a Fabric CCC, the CoreSysServices IP block, the CoreRESET IP block, a CoreABC IP block, a CoreUART\_apb IP block, a fabric state machine to control the CoreSysServices bock, and an APB data block to reformat the AES output so it can be displayed by a terminal emulator.

### 2.7.1 Hardware Implementation

The 50 MHz RC oscillator is used as the main clock. It is used with a CCC to provide the 100 MHz reference clock to the HPMS. The 100 MHz clock is also used as a main clock for the fabric blocks. The HPMS is configured to use the CoreResetP block to generate reset signals for all the blocks. The CoreSysServices IP is configured to use the AES system services. It sends a command to the system controller through COMM block in the HPMS. The fabric Sysservice state control logic initiates the AES system service and captures the AES data from CoreSysService. The fabric Sysservice state block sends the plaintext AES data that (in the example design) is basically a big-endian binary counter that increments the AES plaintext after every AES encryption operation. The incremented value is used as the input for the next encryption operation. The fabric Sysservice state block uses the most recent ciphertext AES data that is calculated as input for the decryption operation. The UART controller block is mainly used to display the AES output to HyperTerminal; it is not required for the AES operation. The APB data block captures the AES data values and converts the binary data to ASCII Hexa data to display in human readable format on the HyperTerminal.

The CoreABC program controls initiating fabric state machine and displaying the data through the CoreUARTapb interface.

The following figure shows the block diagram of the design example.

Figure 12 • IGLOO2 AES System Service Design Example

### 2.7.2 Running the Design

The following steps describes how to run the design example on the IGLOO2 Evaluation Kit board using the M2GL090TS-1FGG484 device:

- 1. Connect the power supply to the IGLOO2 Evaluation Kit board.

- Plug the FlashPro4 ribbon cable into connector J5 (JTAG Programming Header) on the IGLOO2 Evaluation Kit board.

- 3. Connect the mini USB cable between the FlashPro4 and the USB port of the PC.

- 4. Connect the host PC to the J18 connector using the USB min-B cable. Ensure that the USB to UART bridge drivers are automatically detected (can be verified in the Device Manager).

- If USB to UART bridge drivers are not installed, download and install the drivers from www.microsemi.com/soc/documents/CDM\_2.08.24\_WHQL\_Certified.zip.

- Start a HyperTerminal session with 57600 baud rate, 8 data bits, 1 stop bit, no parity, and no flow control. Use other serial terminal emulation programs such as PuTTY or Tera Term if HyperTerminal is not available. Refer to *Configuring Serial Terminal Emulation Programs Tutorial* for configuring HyperTerminal, Tera Term, or PuTTY.

7. Program the IGLOO2 Evaluation Kit board with the provided STAPL file (refer to Design and Programming Files, page 21) using FlashPro4.

Figure 13 • IGLOO2 Evaluation Kit Board

After programming, HyperTerminal displays a message to run the AES system services, as shown in the following figure.

Note: Depending on the terminal program used, the board may need to be power cycled after programming.

Figure 14 • HyperTerminal Showing CoreSysService Design Output

### 2.8 CBC-MAC Example

In cryptography, CBC-MAC is a technique for constructing a message authentication code from a block cipher. It uses the AES encryption in CBC mode. The IV used in first block is zero. Then a chain of blocks is created as each block depends on the proper encryption of the previous block.

The following figure shows the computation technique for CBC-MAC of a message.

Figure 15 • CBC-MAC Computation Diagram

This application note shows the design example to generate CBC-MAC in the SmartFusion2 and IGLOO2 devices.

**Note:** The CBC-MAC design example uses message size that is exact multiple of 128 bits, and it must not be used in a production environment without careful review by a qualified cryptographer.

### 2.9 Design Example - CBC-MAC

This section describes the CBC-MAC application design example. The CBC-MAC design is implemented in both the SmartFusion2 and IGLOO2 devices.

- CBC\_MAC\_SF2 design example: Demonstrates using CBC-MAC in the SmartFusion2 device. It

uses firmware code to generate CBC-MAC.

- CBC\_MAC\_IGL2 design example: Demonstrates using CBC-MAC in the IGLOO2 device. It uses CoreSysServices IP to generate CBC-MAC.

### 2.9.1 Design Example - Using CBC-MAC in SmartFusion2 Devices

This design example is similar to AES\_Services\_SF2 design example. It uses same hardware implementation and uses UART1 in the MSS to display the CBC-MAC operation.

### 2.9.1.1 Software Implementation

The software design example performs the following operations:

- 1. Initializes the system controller enable

- 2. Initializes MMUART\_1

- 3. Performs CBC-MAC

### 2.9.1.1.1 cbc\_mac ();

The **cbc\_mac ()** function allows to run CBC-MAC in the SmartFusion2 AES-128 device. It allows you to enter messages with variable length, perform CBC-MAC operation, and display the result.

### 2.9.1.2 Running the Design

This section describes how to run the CBC-MAC design example in the SmartFusion2 Security Evaluation Kit (M2S-EVAL-KIT) using the M2S090TS-1FGG484 device. Use AES\_Services\_SF2 design example steps to program the device and open HyperTerminal. Then, invoke the CBC-MAC SoftConsole project, and follow the same steps in the AES\_Services\_SF2 design example, including modifying the debugger settings to run the debugger.

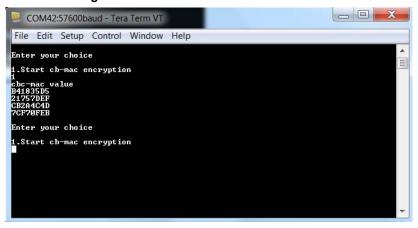

The following figure shows how to run the demo design.

Figure 16 • HyperTerminal showing CBC-MAC Design in a SmartFusion2 Device

| <u>File Edit Setup Control Window Help</u>                                                                                                                                                                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                  |

| **************************************                                                                                                                                                                           |

| **************************************                                                                                                                                                                           |

| Select the Country whice apparation to penform.                                                                                                                                                                  |

| Select the Cryptographic operation to perform: Press Key '1' to perform CBC_MAC                                                                                                                                  |

| Entag the 190 hit how to be used for OEC (so boy Duton IC Bute first):                                                                                                                                           |

| Enter the 128 bit key to be used for AES (as hex Bytes, LS Byte first):<br>0x01 0x02 0x03 0x04 0x05 0x06 0x07 0x08<br>0x09 0x01 0x02 0x03 0x04 0x05 0x06 0x07<br>Enter the number of messages for CBC-MAC :<br>5 |

| Enter Messages                                                                                                                                                                                                   |

| Enter the 16 bytes of input data to encrypt (as hex Bytes, LS Byte first): 0x11 0x11 0x11 0x11 0x11 0x11 0x11 0x1                                                                                                |

| Enter the 16 bytes of input data to encrypt (as hex Bytes, LS Byte first): 0x12 0x12 0x12 0x12 0x12 0x12 0x12 0x12                                                                                               |

| Enter the 16 bytes of input data to encrypt (as hex Bytes, LS Byte first): 0x13 0x13 0x13 0x13 0x13 0x13 0x13 0x13                                                                                               |

| Enter the 16 bytes of input data to encrypt (as hex Bytes, LS Byte first): 0x14 0x14 0x14 0x14 0x14 0x14 0x14 0x14                                                                                               |

| Enter the 16 bytes of input data to encrypt (as hex Bytes, LS Byte first): 0x15 0x15 0x15 0x15 0x15 0x15 0x15 0x15                                                                                               |

| Encrypted data output:                                                                                                                                                                                           |

| 9x7d 9xfa 9xd3 9x8d 9xd6 9x2e 9xc6 9xcf<br>9x35 9x4f 9x72 9x6b 9x50 9x37 9xe9 9x59                                                                                                                               |

| Encrypted data output:                                                                                                                                                                                           |

| 9x72 0xa8 0xd7 0x6b 0xaa 0xc8 0x33 0x8d<br>0xd2 0xc7 0xd7 0x2b 0x81 0xa8 0x64 0xfa                                                                                                                               |

| Encrypted data output:                                                                                                                                                                                           |

| 0xa3 0x5a 0x63 0xfe 0xba 0xc4 0xd7 0xe9<br>0x33 0x5e 0x7a 0x52 0xb0 0x89 0x50 0x7a                                                                                                                               |

| Encrypted data output:                                                                                                                                                                                           |

| 0x37 0xf0 0xa7 0xbe 0x35 0x4f 0x6f 0x7a<br>0xb7 0xcc 0xbc 0x53 0xba 0xb8 0x40 0x61                                                                                                                               |

| Encrypted data output:                                                                                                                                                                                           |

| 0x0a 0x80 0xd1 0x25 0xfe 0xdc 0x52 0x5a<br>0xe1 0x91 0x55 0x1d 0x43 0xbc 0x01 0x8a                                                                                                                               |

| **************************************                                                                                                                                                                           |

| 0x0a 0x80 0xd1 0x25 0xfe 0xdc 0x52 0x5a<br>0xe1 0x91 0x55 0x1d 0x43 0xbc 0x01 0x8a<br>************************************                                                                                       |

| Press any key to continue.                                                                                                                                                                                       |

### 2.9.2 Design Example - Using CBC-MAC in IGLOO2 Devices

This design example is similar to the AES\_Services\_IGL2 design example. The fabric system service state control logic configures CoreSysService to generate AES CBC mode. It also sends the appropriate IV during each AES services. The design example uses a message block that sends the messages for AES operation. The message block uses four messages in the current implementation. One of the messages is tied to DIP switch in the IGLOO2 Evaluation Kit. You can change the DIP switch and change the message.

**Note:** You can modify the message block, content, and size. However, you need to change the counter in Sysservice state control logic to match the message length. The other blocks are similar to the AES\_Services\_IGL2 design example.

The following figure shows the block diagram of CBC-MAC design.

Figure 17 • IGLOO2 CBC-MAC Design Example

### 2.9.2.1 Running the Design

This section describes running the CBC-MAC design example in the IGLOO2 Evaluation Kit using the M2GL090TS-1FGG484 device. Use AES\_Services\_IGL2 design example steps to program the device and open HyperTerminal.

The following figure shows running the demo design.

Figure 18 • CBC-MAC of a Message

### 2.10 Design and Programming Files

Download the SmartFusion2 and IGLOO2 AES design files from the Microsemi Corporation website: http://soc.microsemi.com/download/rsc/?f=m2s\_m2gl\_ac410\_aes\_services\_liberov11p8\_df

Download the SmartFusion2 and IGLOO2 CBC-MAC design files from the Microsemi Corporation website:

http://soc.microsemi.com/download/rsc/?f=m2s\_m2gl\_ac410\_cbc\_mac\_liberov11p8\_df

The SmartFusion2 design file consists a Libero Verilog project, SoftConsole software project, and programming files (.stp) for the SmartFusion2 Security Evaluation Kit (M2S-EVAL-KIT). The IGLOO2 design file consists a Libero Verilog project and programming files (.stp) for the IGLOO2 Evaluation Kit. Refer to the Readme.txt file included in the design file folder for the directory structure and description.

### 2.11 Conclusion

The SmartFusion2 and IGLOO2 family of FPGAs are the most secure programmable logic devices ever made. In selected SmartFusion2 and IGLOO2 devices, the AES engine can perform encryption or decryption on 128-bit blocks of user data using either 128-bit or 256-bit keys as defined in NIST FIPS 197. Several common modes are provided to encrypt or decrypt arbitrarily sized blocks of data, including ECB, CBC, OFB, and CTR modes as defined in NIST SP800-38a. The AES system services, along with the other cryptographic services offered, allow you to use the SmartFusion2 and IGLOO2 devices in various secure applications.