# Handling Cache Coherency Issues at Runtime Using Cache Maintenance Operations on Cortex-M7 MCUs Using MPLAB Harmony v3

#### Introduction

The cache coherency issue is inevitable on applications running on microcontrollers (MCUs) that have cacheable memory regions, which use Direct Memory Access (DMA) for data transfer operations. This is due to the CPU performing a read/write from the cache while the DMA transfers data between the peripheral and physical memory.

One of the methods to handle cache coherency requires the application to manage the cache at run-time using the Cortex-M7 cache maintenance operations. The Arm<sup>®</sup> Cortex<sup>®</sup> Microcontroller Software Interface Standard (CMSIS) provides cache maintenance Application Program Interfaces (APIs).

This document explains how an application can manage cache coherency issues at run time by using the CMSIS provided cache management APIs under MPLAB® Harmony v3.

**Note:** The concepts discussed in this document are common for all Arm Cortex-M7 MCUs, and the SAM E70 MCU is used as an example to discuss the concepts.

© 2021 Microchip Technology Inc.

Technical Brief

DS90003295A-page 1

### 1. Description

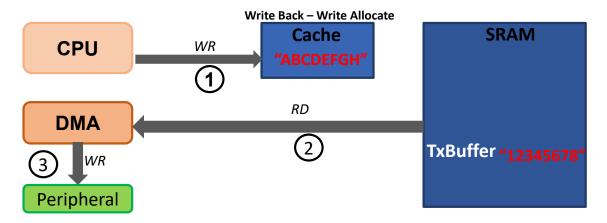

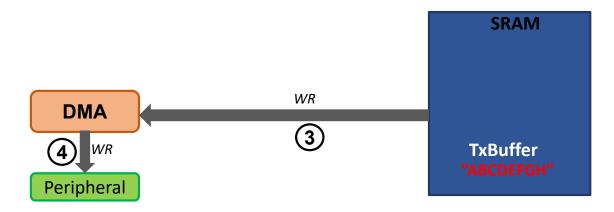

The following figure illustrates the cache coherency issue as observed when the DMA reads from the SRAM on the SAME70 MCU.

Figure 1-1. Memory to Peripheral Transfer (DMA reads from SRAM)

The application submits a request to transfer data buffer *TxBuffer* (value 'ABCDEFGH') to the peripheral. The CPU populates the DMA write buffer (*TxBuffer*) with the data to be written (value 'ABCDEFGH') to the peripheral. However, due to the set cache policy "Write Back and Write Allocate", the DMA write buffer (*TxBuffer*) may not be immediately written to the main memory, and the written data may remain in the data cache. The DMA write buffer (*TxBuffer*) in the main memory still contains the old value (12345678).

When the DMA is triggered to initiate the memory to peripheral transfer, the DMA reads the buffer (*TxBuffer*) from the main memory (12345678). As a result, the DMA ends up transferring stale data to the peripheral.

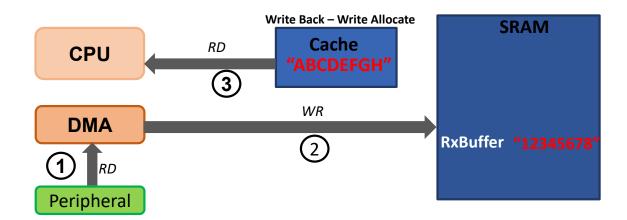

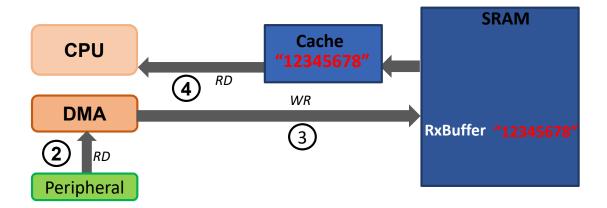

The following figure illustrates the cache coherency issue observed when the DMA writes to the SRAM.

Figure 1-2. Peripheral to Memory Transfer (DMA writes to SRAM)

The application submits a request to receive data in the *RxBuffer* (value '12345678') from the peripheral. The DMA populates the *RxBuffer* (with value '12345678') in the SRAM. However, the data cache is not updated, and it

continues to hold the previous data. When the CPU reads the *RxBuffer*, it ends up reading the previous value contained in the buffer (value 'ABCDEFGH').

#### 1.1 Handling Cache Coherency

A method to handle the cache coherency issues illustrated in the figures Cache Coherency (DMA Reads from SRAM) and Cache Coherency (DMA writes to SRAM) involves the application to manage the cache at run-time using the Cortex-M7 cache maintenance operations. The operations include the ability to perform these actions:

- · Enable or Disable the cache

- Invalidate the cache Marks the cache lines as invalid. Subsequent access forces the data to be copied from the main memory to the cache.

- · Clean the cache Writes the cache lines, which are marked as dirty, back to the main memory

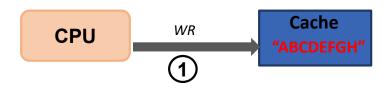

To handle the cache coherency discussed in Cache Coherency (DMA Reads from SRAM), perform the following actions:

1. The application fills the write data buffer *TxBuffer* (value 'ABCEDFGH'). Due to the default cache policy (Write Back – Write Allocate), the written data may be in the cache.

Figure 1-3. Populate Write Buffer

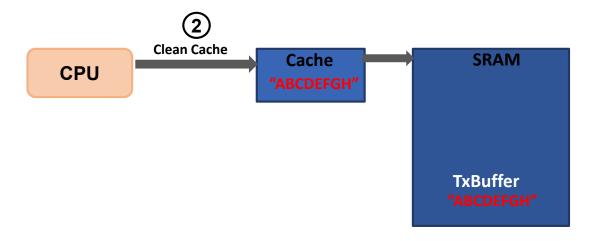

2. Flush the write data buffer *TxBuffer* (value 'ABCDEFGH') to the main memory by calling the clean cache API. **Figure 1-4. Flush Write Buffer**

3. The application submits a request to transfer data from the *TxBuffer* (value 'ABCDEFGH') to the peripheral.

Figure 1-5. Write to Peripheral

To handle the cache coherency discussed in Cache Coherency (DMA writes to SRAM), perform the following steps:

1. The application calls the 'Invalidate cache' API to mark the cache lines as invalid.

Figure 1-6. Invalidate Cache

- 2. The application submits a request to receive data in the RxBuffer (value '12345678') from the peripheral.

- 3. The DMA populates the RxBuffer (with value '12345678') in the SRAM.

- 4. Because the cache line corresponding to the *RxBuffer* is in an invalid state, a read access by the CPU results in the *RxBuffer* being copied from the main memory into the data cache.

Figure 1-7. Handle Peripheral to Memory Transfer Cache Coherency

## 2. Implementation

#### 2.1 Configuration

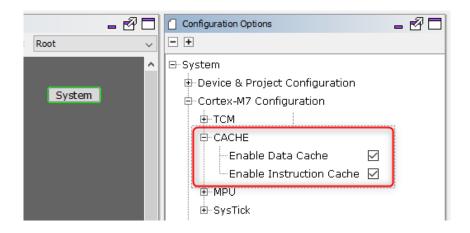

In an MPLAB Harmony v3 project for the SAM E70 MCU, by default the cache is enabled by the MPLAB Harmony Configurator (MHC). In MHC, the configuration setting can be found under *MHC project graph* > *System*.

Figure 2-1. MHC Cache Configuration

#### 2.2 CMSIS Data Cache Maintenance APIs

The Cortex Microcontroller Software Interface Standard (CMSIS) provides the following D-Cache maintenance APIs:

Table 2-1. CMSIS Data Cache Maintenace APIs

| Name                                                             | Description                                                                                                   |  |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|

| SCB_EnableDCache (void)                                          | Enables data cache. Invalidates the entire data cache before enabling it.                                     |  |

| SCB_DisableDCache (void)                                         | Disables data cache. Cleans the data cache to flush dirty data to the main memory before disabling the cache. |  |

| SCB_InvalidateDCache(void)                                       | Invalidate the entire data cache                                                                              |  |

| SCB_InvalidateDCache_by_Addr (uint32_t * addr, int32_t dsize )   | Invalidate the data cache line by address.                                                                    |  |

| SCB_CleanDCache(void)                                            | Cleans the data cache.                                                                                        |  |

| SCB_CleanDCache_by_Addr (uint32_t *addr, int32_t dsize)          | Cleans the data cache line by address.                                                                        |  |

| SCB_CleanInvalidateDCache(void)                                  | Cleans and Invalidates the entire data cache                                                                  |  |

| SCB_CleanInvalidateDCache_by_Addr(uint32_t *addr, int32_t dsize) | Cleans and Invalidates the data cache line by address.                                                        |  |

**Notes:** When using the cache clean and cache invalidate by address APIs:

- addr Must be aligned to the cache line size boundary. This means that the DMA buffer address must be aligned to the 32-byte boundary.

- dsize Must be a multiple of the cache line size. This means that the DMA buffer size must be a multiple of 32bytes.

#### 2.3 Example

The following code example demonstrates the usage of CMSIS data cache maintenance APIs along with the MPLAB Harmony v3 DMA peripheral library APIs to read and write data over the USART interface.

```

/* Buffers must be aligned to cache line boundaries and must be a multiple of cache line size

(32) */

char __attribute__ ((aligned(32))) TxBuffer[32];

char __attribute__ ((aligned(32))) RxBuffer[32];

int main ( void )

/* Initialize all peripherals and modules */

/* Fill the TxBuffer with the data to be transmitted.

The TxBuffer may be in D-cache */

memcpy((void *)TxBuffer, (const void *)"Microchip", sizeof("Microchip"));

/\star Flush the TxBuffer from D-cache to SRAM \star/

SCB CleanDCache by Addr((uint32 t *)TxBuffer, 32);

/\star Submit a DMA request to transfer data in the TxBuffer \star/ XDMAC ChannelTransfer(XDMAC_CHANNEL_0, TxBuffer,

(const void *) USART1 TRANSMIT ADDRESS, sizeof("Microchip"));

/* Invalidate the RxBuffer in D-cache */

SCB CleanInvalidateDCache by Addr((uint32 t *)RxBuffer, 32);

/* Submit a DMA request to receive 20 characters in the RxBuffer */

XDMAC ChannelTransfer(XDMAC CHANNEL 1, (const void *) USART1 RECEIVE ADDRESS,

RxBuffer, 20);

while ( true )

/* Application Code */

/* Execution should not come here during normal operation */

return ( EXIT FAILURE );

```

#### 3. References

- How to Create Non-Cacheable Memory Region on CortexM7 (SAM S70/ E70/ V70/ V71) MCUs Using MPLAB

Harmony v3

- 2. Managing Cache Coherency on Cortex-M7 Based MCUs

- 3. Usage of XDMAC on SAM S/SAM E/SAM V

- 4. MPLAB Harmony v3 Quick Docs package provides standalone help pages for users to get started developing applications on Microchip's 32-bit SAM and PIC32 MCUs. Download the <code>quick\_docs repo</code> and start with the <code>index.html</code> file present in the docs folder.

- The online version is available at microchip-mplab-harmony.github.io/quick docs/.

- 5. MPLAB Harmony v3 Landing web page: www.microchip.com/mplab/mplab-harmony.

## The Microchip Website

Microchip provides online support via our website at www.microchip.com/. This website is used to make files and information easily available to customers. Some of the content available includes:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

### **Product Change Notification Service**

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to www.microchip.com/pcn and follow the registration instructions.

## **Customer Support**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Embedded Solutions Engineer (ESE)

- **Technical Support**

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: www.microchip.com/support

## Microchip Devices Code Protection Feature

Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods being used in attempts to breach the code protection features of the Microchip devices. We believe that these methods require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Attempts to breach these code protection features, most likely, cannot be accomplished without violating Microchip's intellectual property rights.

- Microchip is willing to work with any customer who is concerned about the integrity of its code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not mean that we are guaranteeing the product is "unbreakable." Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

DS90003295A-page 8 **Technical Brief** © 2021 Microchip Technology Inc.

#### **Legal Notice**

Information contained in this publication is provided for the sole purpose of designing with and using Microchip products. Information regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL OR CONSEQUENTIAL LOSS, DAMAGE, COST OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, Anyln, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2021, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-7431-9

© 2021 Microchip Technology Inc.

Technical Brief

DS90003295A-page 9

# **Quality Management System**

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

© 2021 Microchip Technology Inc. Technical Brief DS90003295A-page 10

## **Worldwide Sales and Service**

| AMERICAS                  | ASIA/PACIFIC          | ASIA/PACIFIC            | EUROPE                |

|---------------------------|-----------------------|-------------------------|-----------------------|

| Corporate Office          | Australia - Sydney    | India - Bangalore       | Austria - Wels        |

| 2355 West Chandler Blvd.  | Tel: 61-2-9868-6733   | Tel: 91-80-3090-4444    | Tel: 43-7242-2244-39  |

| Chandler, AZ 85224-6199   | China - Beijing       | India - New Delhi       | Fax: 43-7242-2244-393 |

| Tel: 480-792-7200         | Tel: 86-10-8569-7000  | Tel: 91-11-4160-8631    | Denmark - Copenhagen  |

| Fax: 480-792-7277         | China - Chengdu       | India - Pune            | Tel: 45-4485-5910     |

| Technical Support:        | Tel: 86-28-8665-5511  | Tel: 91-20-4121-0141    | Fax: 45-4485-2829     |

| www.microchip.com/support | China - Chongqing     | Japan - Osaka           | Finland - Espoo       |

| Web Address:              | Tel: 86-23-8980-9588  | Tel: 81-6-6152-7160     | Tel: 358-9-4520-820   |

| www.microchip.com         | China - Dongguan      | Japan - Tokyo           | France - Paris        |

| Atlanta                   | Tel: 86-769-8702-9880 | Tel: 81-3-6880- 3770    | Tel: 33-1-69-53-63-20 |

| Duluth, GA                | China - Guangzhou     | Korea - Daegu           | Fax: 33-1-69-30-90-79 |

| Tel: 678-957-9614         | Tel: 86-20-8755-8029  | Tel: 82-53-744-4301     | Germany - Garching    |

| Fax: 678-957-1455         | China - Hangzhou      | Korea - Seoul           | Tel: 49-8931-9700     |

| Austin, TX                | Tel: 86-571-8792-8115 | Tel: 82-2-554-7200      | Germany - Haan        |

| Tel: 512-257-3370         | China - Hong Kong SAR | Malaysia - Kuala Lumpur | Tel: 49-2129-3766400  |

| Boston                    | Tel: 852-2943-5100    | Tel: 60-3-7651-7906     | Germany - Heilbronn   |

| Westborough, MA           | China - Nanjing       | Malaysia - Penang       | Tel: 49-7131-72400    |

| Tel: 774-760-0087         | Tel: 86-25-8473-2460  | Tel: 60-4-227-8870      | Germany - Karlsruhe   |

| Fax: 774-760-0088         | China - Qingdao       | Philippines - Manila    | Tel: 49-721-625370    |

| Chicago                   | Tel: 86-532-8502-7355 | Tel: 63-2-634-9065      | Germany - Munich      |

| Itasca, IL                | China - Shanghai      | Singapore               | Tel: 49-89-627-144-0  |

| Tel: 630-285-0071         | Tel: 86-21-3326-8000  | Tel: 65-6334-8870       | Fax: 49-89-627-144-44 |

| Fax: 630-285-0075         | China - Shenyang      | Taiwan - Hsin Chu       | Germany - Rosenheim   |

| Dallas                    | Tel: 86-24-2334-2829  | Tel: 886-3-577-8366     | Tel: 49-8031-354-560  |

| Addison, TX               | China - Shenzhen      | Taiwan - Kaohsiung      | Israel - Ra'anana     |

| Tel: 972-818-7423         | Tel: 86-755-8864-2200 | Tel: 886-7-213-7830     | Tel: 972-9-744-7705   |

| Fax: 972-818-2924         | China - Suzhou        | Taiwan - Taipei         | Italy - Milan         |

| Detroit                   | Tel: 86-186-6233-1526 | Tel: 886-2-2508-8600    | Tel: 39-0331-742611   |

| Novi, MI                  | China - Wuhan         | Thailand - Bangkok      | Fax: 39-0331-466781   |

| Tel: 248-848-4000         | Tel: 86-27-5980-5300  | Tel: 66-2-694-1351      | Italy - Padova        |

| Houston, TX               | China - Xian          | Vietnam - Ho Chi Minh   | Tel: 39-049-7625286   |

| Tel: 281-894-5983         | Tel: 86-29-8833-7252  | Tel: 84-28-5448-2100    | Netherlands - Drunen  |

| Indianapolis              | China - Xiamen        |                         | Tel: 31-416-690399    |

| Noblesville, IN           | Tel: 86-592-2388138   |                         | Fax: 31-416-690340    |

| Tel: 317-773-8323         | China - Zhuhai        |                         | Norway - Trondheim    |

| Fax: 317-773-5453         | Tel: 86-756-3210040   |                         | Tel: 47-72884388      |

| Tel: 317-536-2380         | 15 55 155 52 155 15   |                         | Poland - Warsaw       |

| Los Angeles               |                       |                         | Tel: 48-22-3325737    |

| Mission Viejo, CA         |                       |                         | Romania - Bucharest   |

| Tel: 949-462-9523         |                       |                         | Tel: 40-21-407-87-50  |

| Fax: 949-462-9608         |                       |                         | Spain - Madrid        |

| Tel: 951-273-7800         |                       |                         | Tel: 34-91-708-08-90  |

| Raleigh, NC               |                       |                         | Fax: 34-91-708-08-91  |

| Tel: 919-844-7510         |                       |                         | Sweden - Gothenberg   |

| New York, NY              |                       |                         | Tel: 46-31-704-60-40  |

| Tel: 631-435-6000         |                       |                         | Sweden - Stockholm    |

| San Jose, CA              |                       |                         | Tel: 46-8-5090-4654   |

| Tel: 408-735-9110         |                       |                         | UK - Wokingham        |

| Tel: 408-436-4270         |                       |                         | Tel: 44-118-921-5800  |

| Canada - Toronto          |                       |                         | Fax: 44-118-921-5820  |

| Tel: 905-695-1980         |                       |                         | 1 da. 77-110-321-3020 |

| Fax: 905-695-2078         |                       |                         |                       |

| I an. 300-030-20/0        |                       |                         |                       |

© 2021 Microchip Technology Inc. Technical Brief DS90003295A-page 11