### SAM G55 Series Family Silicon Errata and Data Sheet Clarification

The SAM G55 Series family of devices that you have received conform functionally to the current Device Data Sheet (Atmel-11289F-ATARM-SAM-G55G-SAM-G55J-Datasheet\_27-May-16), except for the anomalies described in this document.

#### **New Silicon Errata Issues**

Note:

This document provides information on new errata issues for the SAM G55 Series family of devices. Refer to the current device data sheet for all pre-existing silicon errata issues.

#### 1. Module: FLEXCOM in USART Mode

When the Peripheral DMA Controller (PDC) is enabled, the USART Receiver Time Out Register (RTOR) read value is incorrect.

#### Work around

To read correctly, the USART RTOR value for all PDC channels and buffers must be disabled (transmitter and receiver) by writing the PDC Peripheral Transfer Control Register (PTCR) with the value of 0x010A0202.

#### **Affected Silicon Revisions**

| Α | В |  |  |  |

|---|---|--|--|--|

| Χ | Χ |  |  |  |

#### **Data Sheet Clarifications**

The following typographic corrections and clarifications are to be noted for the latest revision of the device data sheet (Atmel-11289F-ATARM-SAM-G55G-SAM-G55J-Datasheet\_27-May-16).

Corrections in tables and paragraphs are shown in **bold.** Where possible, the original bold text formatting has been removed for the clarity.

#### 1. Module: Bootloader

Chapter 7 "Bootloader" in the data sheet has a new verbiage for the NRST line. The newly added text is shown in bold.

The SAM G55 devices ship with a factory-programmed bootoader in Flash. The Flash loader downloads code either through the SPI or through the TWI0.

The Bootloader mode is entered automatically on power-up if no valid firmware is detected in the Flash. A valid firmware is detected by performing a CRC on the content of the Flash. If the CRC is correct, the application is started. Otherwise, the Bootloader mode is entered.

Alternatively, the Bootloader mode can be forced by applying 10 low pulses of 1 ms on the NRST line (with a period of 10 ms maximum). When the Bootloader detects this sequence, it asserts the pin PA01 (NCHG) low as an acknowledge.

The Bootloader mode initializes the TWI0 in Client Mode with the  $I^2C$  address 0x26, and the SPI in Client Mode, 8-bit data length, SPI Mode 1.

### 2. Module: System Configuration - CCFG\_USBMR Register

In the current device data sheet section 15.9.7, the PLLFREQADJUST bit is missing from the register description. This bit occupies a bit offset of 4 as shown below.

PLLFREQADJUST: USB PLL Output Automatic Synchronization

0:USB PLL clock is not adjust

1:USB PLL output is automatically adjust at 48 MHz +/-0.25% whatever the internal 32 KHz accuracy.

## 3. Module: Clock Generator - CKGR\_PLLAR Register

In the current device data sheet section 18.20.9, the MULA bit field for the CKGR\_PLLAR register extends from bit 16 to bit 27. The corrected bit field extends from bit 16 to bit 28.

# 4. Module: Clock Generator - CKGR\_PLLBR Register

In the current device data sheet, the MULB bit field for the CKGR\_PLLBR register extends from bit field 16 to 26. The corrected bit field extended from 16 to 27.

### 5. Module: Clock Generator - PMC\_PMMR Register

In the current device data sheet Section 18.20.32, the PLLA\_MMAX bit field for the PMC\_PMMR register extends from bit 0 to bit 10. The corrected bit field extends from bit 0 to bit 12.

### 6. Module: Clock Generator - PMC\_PMMR Register

In the current device data sheet Section 18.20.32, the PLLB\_MMAX bit field for the PMC\_PMMR register extends from bit 16 to bit 26. The corrected bit field extends from bit 16 to bit 27.

#### 7. Module: I<sup>2</sup>S Controller - I2SC\_MR Register

In the current device data sheet Section 33.8.2, the table for the FORMAT bit is incorrect and lists left-justified format. This format is not supported for this device.

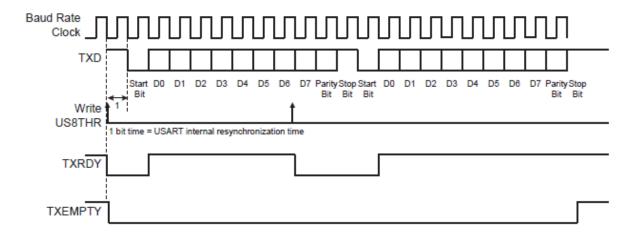

#### 8. Module: USART - Transmitter Operations

Figure 30-6 is incorrect. The corrected figure is as shown below:

#### 9. Module: USART - Multi-drop Mode

In the current device data sheet Section 30.6.3.6, the bit name SENTA is incorrect. The corrected name is SENDA.

#### 10. Module: USART - ISO7816 Mode Overview

The last paragraph of the current device data sheet Section 30.6.4.1 has erroneous text. The corrected text is given in bold.

When operating in ISO7816, either in T = 0 or T = 1 modes, the character format is fixed. The configuration is 8 data bits and 1 or 2 stop bits, regardless of the values programmed in the Mode register fields CHRL, MODE9 and CHMODE. MSBF can be used to transmit LSB or MSB first. The Parity (PAR) bit can be used to transmit in normal or inverse mode. Refer to Section 31.7.3 "USART Mode Register" and "PAR: Parity Type".

#### 11. Module: USART - US\_RTOR Register

In the Section 30.7.20, the TimeOut (TO) bit information is incomplete, therefore the following information has been added.

TimeOut (TO) value is 17 bits for USART, which supports all modes including LIN mode.

16 bits for USART, which supports all modes.

8 bits for USART, which does not support ISO7816.

#### 12. Module: USART - US LINMR Register

The following sentence in the current device data sheet Section 30.7.25 has an error and must be disregarded:

This register can only be written if the WPEN bit is cleared in the USART Write Protection Mode Register.

# 13. Module: Electrical Characteristics Recommended Operating Conditions

Table 39-2 is updated to clarify the  $V_{DDIO\_SLOPE}$  parameter. The new values are shown below.

| Symbol      | Parameter      | Conditions     | Min. | Тур. | Max. | Unit   |

|-------------|----------------|----------------|------|------|------|--------|

| V           | Slope on VDDIO | Single Supply, | 1.5  |      |      | V/ms   |

| VDDIO_SLOPE | Slope on VDDIO | See Figure 5-2 | 1.5  |      |      | v/IIIS |

| V           | Slope on VDDIO | Dual Supply,   | 7    |      |      | V/ms   |

| VDDIO_SLOPE |                | See Figure 5-3 | '    |      |      | V/IIIS |

### 14. Module: USB Host Port (UHP): User Interface

The addresses listed for the UHP Registers are incorrect. The base address is **0x20400000**. All 23 register addresses must be read as 0x20400000 + the offset listed in Table 36.2.

# 15. Module: System I/O Lines -Table 9-6 "System I/O Configuration Pin

The default function after reset of PA21 and PA22 is I/O.

#### 16. Module: Reset Controller (RSTC)

The SYSC\_WPMR register is not present. References to that register must be ignored.

#### 17. Module: Product Mapping

The offset listed for GPBR in Figure 6-1. SAM G55 Product Mapping must be 0x90.

#### 18. Module: Supply Controller (SUPC)

In the device data sheet Section 25.5.2, the Supply Controller (SUPC) user interface erroneously lists offsets 0x20 through 0x2C as reserved. They are not part of the SUPC.

## 19. Module: General Purpose Backup Registers (GPBR)

The offset listed for SYS\_GPBR7 in Table 28-1. Register Mapping must be 0x1C.

### 20. Module: ADC Channel Status Register bit descriptions

The CHx bits in the ADC\_CHSR register description must be as follows:

CHx: Channel x Status

- 0: The corresponding channel (or part of sequence, see ADC\_SEQR1.USCHx field) is disabled.

- 1: The corresponding channel (or part of sequence, see ADC\_SEQR1.USCHx field) is enabled.

Note: For example, when ADC\_MR.USEQ = 1 and a '1' is written to CH2, the channel defined in ADC\_SEQR1.USCH2 is part of the sequence of conversions.

#### 21. Module: Universal Serial Bus (USB)

The Crystal-less feature mentioned in "Crystal-less USB 2.0 Device and USB Host OHCI with Onchip transceiver" must be ignored. The SAM G55 embeds a USB 2.0 Device and USB Host OHCI with On-chip transceiver, but in general does not support Crystal-less operation.

#### 22. Module: Universal Serial Bus (USB)

In the following device data sheet sections: 37.7.4, 37.7.5, 37.5.6, 37.7.7 and 37.7.8, the EXTRSM bit description must be as follows:

EXTRSM: Disable External Resume Interrupt

0 = No effect

1 = Disables External Resume Interrupt.

#### 23. Module: Debug and Test Features

In the device data sheet, section 11.6.9, PD0 is erroneously listed as a pin to maintain low to enable JTAG Boundary Scan. There is no PD0 on the SAM G55 family of devices. The PA07 pin must be maintained low instead along with TST and JTAGSEL that must be tied high to enable JTAG Boundary Scan.

### 24. Module: Power Management Controller (PMC)

In the current device data sheet, the bit 7 in the PMC\_PCER0, PMC\_PCDR0 and PMC\_PCSR0 registers are erroneously empty. These bits must be defined as PID7 that corresponds to FLEXCOM7 peripheral identifiers.

Note: This update is not applicable for the WLC-SP49 package (SAM G55G19).

### 25. Module: Inter-IC Sound Controller (I<sup>2</sup>SC)

The section 33.6.8 of the device data sheet is incomplete, hence the following note was added.

Note: The PDC channel '0' and PDC channel '1' share I2SC\_SR.ENDRX and I2SC\_SR.ENDTX status bits. If a single PDC channel is selected, set the I2SC\_RCR and I2SC\_TCR of the unused PDC channel to any non-zero value to stop it from affecting the shared status bits.

#### APPENDIX A: REVISION HISTORY

#### Revision A Document (07/2019)

This is the initial released version of this document.

#### Revision B Document (01/2020)

This revision includes the following updates to Data Sheet Clarifications:

- 13. Module: Electrical Characteristics Recommended Operating Conditions

- 14. Module: USB Host Port (UHP): User Interface

- 15. Module: System I/O Lines -Table 9-6 "System I/O Configuration Pin List"

- 16. Module: Reset Controller (RSTC)

- 17. Module: Product Mapping

- 18. Module: Supply Controller (SUPC)

- 19. Module: General Purpose Backup Registers (GPBR)

- The offset listed for SYS\_GPBR7 in Table 28-1.

Register Mapping must be 0x1C.

#### Revision C Document (04/2020)

This revision includes the addition of silicon Issue 1. Module: FLEXCOM in USART Mode.

#### Revision D (05/2021)

The UART, TWI, SPI, I<sup>2</sup>S and USB standards use the terminology "Master" and "Slave". The equivalent Microchip terminology used in this document is "Host" and "Client". This change may not be reflected in all associated Microchip documentation. For additional information, contact a Microchip sales representative.

The following Data Sheet Clarifications were added in this revision:

- 21. Module: Universal Serial Bus (USB)

- 22. Module: Universal Serial Bus (USB)

- 23. Module: Debug and Test Features

- 24. Module: Power Management Controller (PMC)

- 25. Module: Inter-IC Sound Controller (I2SC)

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- · Microchip believes that its family of products is secure when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods being used in attempts to breach the code protection features of the Microchip devices. We believe that these methods require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Attempts to breach these code protection features, most likely, cannot be accomplished without violating Microchip's intellectual property rights.

- Microchip is willing to work with any customer who is concerned about the integrity of its code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not mean that we are guaranteeing the product is "unbreakable." Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication is provided for the sole purpose of designing with and using Microchip products. Information regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDI-RECT, SPECIAL, PUNITIVE, INCIDENTAL OR CONSEQUEN-TIAL LOSS, DAMAGE, COST OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKiT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive,  $Crypto Companion, \ Crypto Controller, \ ds PICDEM, \ ds PICDEM.net,$ Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2020-2021, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-5224-8280-2

### Worldwide Sales and Service

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/ support

Web Address:

www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

Boston

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423

Fax: 972-818-2924 **Detroit**

Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Tel: 317-536-2380 Los Angeles Mission Viejo, CA

Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

**China - Beijing** Tel: 86-10-8569-7000

China - Chengdu Tel: 86-28-8665-5511

China - Chongqing Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

**China - Guangzhou** Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

**China - Nanjing** Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

**China - Shanghai** Tel: 86-21-3326-8000

**China - Shenyang** Tel: 86-24-2334-2829

**China - Shenzhen** Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

**China - Wuhan** Tel: 86-27-5980-5300

**China - Xian** Tel: 86-29-8833-7252

China - Xiamen

Tel: 86-592-2388138

**China - Zhuhai** Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune Tel: 91-20-4121-0141

**Japan - Osaka** Tel: 81-6-6152-7160

**Japan - Tokyo** Tel: 81-3-6880- 3770

Korea - Daegu

Tel: 82-53-744-4301 **Korea - Seoul** Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

**Singapore** Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

#### **EUROPE**

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4485-5910 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

Germany - Garching Tel: 49-8931-9700

**Germany - Haan** Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-72400

**Germany - Karlsruhe** Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

**Italy - Padova** Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

**Poland - Warsaw** Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Gothenberg Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820