## PIC18F2X/4XQ10 Memory Programming Specification

#### 1.0 OVERVIEW

This programming specification describes an SPI-based programming method for the PIC18F2X/4XQ10 family of microcontrollers. Section 3.0 "Programming Algorithms" describes the programming commands, programming algorithms and electrical specifications used in that particular programming method. Appendix B: "PIC18F2X/4XQ10 Device ID, Checksums and Pinout Descriptions" contains individual part numbers, device identification and checksum values, pinout and packaging information, and Configuration Words.

- Note 1: This is an SPI-compatible programming method with 8-bit commands.

- 2: The low-voltage entry code is now 32 clocks and MSb first, unlike previous PIC18 devices which had 33 clocks and LSb first.

#### 1.1 Programming Data Flow

Nonvolatile Memory (NVM) programming data can be supplied by either the high-voltage In-Circuit Serial Programming™ (ICSP™) interface or the low-voltage In-Circuit Serial Programming (ICSP) interface. Data can be programmed into the Program Flash Memory (PFM), Data EEPROM Memory, dedicated "User ID" locations and the Configuration Words.

#### 1.2 Write and/or Erase Selection

Erasing or writing is selected according to the command used to begin operation (see Table 3-1). The terminologies used in this document, related to erasing/writing to the program memory, are defined in Table 1-1 and are detailed below.

TABLE 1-1: PROGRAMMING TERMS

| Term            | Definition                             |

|-----------------|----------------------------------------|

| Programmed Cell | A memory cell at logic '0'             |

| Erased Cell     | A memory cell at logic '1'             |

| Erase           | Change memory cell from a '0' to a '1' |

| Write           | Change memory cell from a '1' to a '0' |

| Program         | Generic erase and/or write             |

#### 1.2.1 ERASING MEMORY

Memory is erased by 128-word sectors or in bulk, where 'bulk' includes many subsets of the total memory space. The duration of the data memory erase is determined by the size of data memory. All Bulk ICSP Erase commands have minimum VDD requirements, which are higher than the Sector Erase and Write requirements.

Sectors pertain to PFM and User ID memory only. Configuration and data memory should be erased by the Bulk Erase command. For self-write operations, each byte write to data memory includes an automatic erase cycle for the location about to be programmed.

#### 1.2.2 WRITING MEMORY

Memory is written one word at a time. The duration of the write is determined internally.

#### 1.3 Hardware Requirements

#### 1.3.1 HIGH-VOLTAGE ICSP PROGRAMMING

In High-Voltage ICSP mode, the device requires two programmable power supplies: one for VDD and one for the MCLR/VPP pin.

#### 1.3.2 LOW-VOLTAGE ICSP PROGRAMMING

In Low-Voltage ICSP mode, the device can be programmed using a single VDD source in the device operating range. The MCLR/VPP pin does not have to be brought to programming voltage, but can instead be left at the normal operating voltage.

#### 1.3.2.1 Single-Supply ICSP Programming

The device's LVP Configuration bit enables single-supply (low-voltage) ICSP programming. The LVP bit defa<u>ults to</u> a '1' (enabled). The LVP bit may only be programmed to '0' by entering the High-Voltage ICSP mode, where the <u>MCLR/VPP</u> pin is raised to VIHH. Once the LVP bit is programmed to a '0', only the High-Voltage ICSP mode is available and only the High-Voltage ICSP mode can be used to program the device.

- **Note 1:** The High-Voltage ICSP mode is always available, regardless of the state of the LVP bit, by applying Vihht to the MCLR/VPP pin.

- 2: While in Low-Voltage ICSP mode, MCLR is always enabled, regardless of the MCLRE bit. Also, the port pin can no longer be used as a general purpose input.

#### 1.4 Pin Utilization

Five pins are needed for ICSP programming. The pins are listed in Table 1-2. For pin locations and packaging information, please refer to Table B-3.

TABLE 1-2: PIN DESCRIPTIONS DURING PROGRAMMING

| Pin Name  | During Programming  |                  |                                           |  |  |  |

|-----------|---------------------|------------------|-------------------------------------------|--|--|--|

| Pili Name | Function            | Pin Type         | Pin Description                           |  |  |  |

| ICSPCLK   | ICSPCLK             | I                | Clock Input – Schmitt Trigger Input       |  |  |  |

| ICSPDAT   | ICSPDAT             | I/O              | Data Input/Output – Schmitt Trigger Input |  |  |  |

| MCLR/VPP  | Program/Verify mode | <sub>[</sub> (1) | Program Mode Select                       |  |  |  |

| VDD       | VDD                 | Р                | Power Supply                              |  |  |  |

| Vss       | Vss                 | Р                | Ground                                    |  |  |  |

**Legend:** I = Input, O = Output, P = Power

Note 1: The programming high voltage is internally generated. To activate the Program/Verify mode, high voltage needs to be applied to the MCLR input. Since the MCLR is used for a level source, MCLR does not draw any significant current.

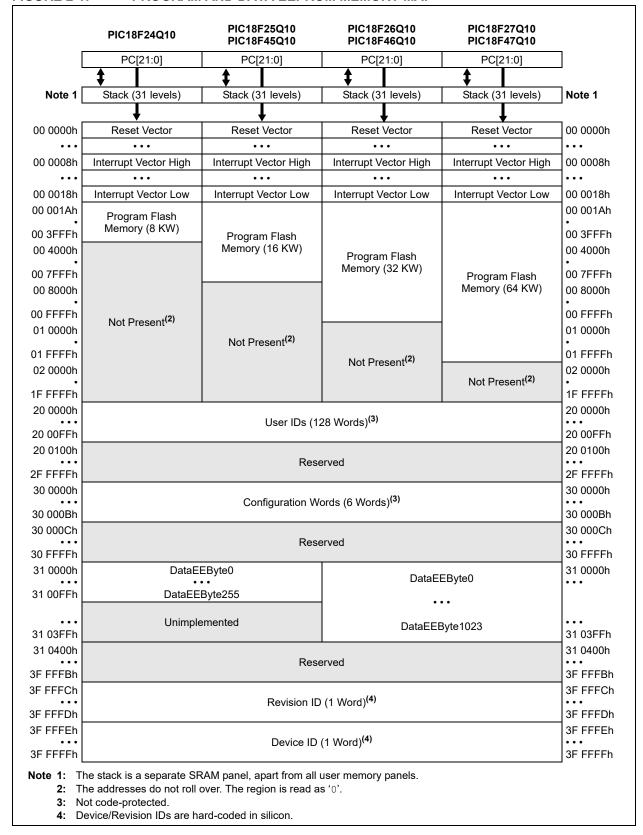

#### 2.0 MEMORY MAP

FIGURE 2-1: PROGRAM AND DATA EEPROM MEMORY MAP

TABLE 2-1: MEMORY MAP AND CODE PROTECTION CONTROL

|        |                       |                                    | Dev                                | vice                               |                                    |  |

|--------|-----------------------|------------------------------------|------------------------------------|------------------------------------|------------------------------------|--|

| Reg.   | Address<br>(from/to)  | PIC18F24Q10                        | PIC18F25Q10<br>PIC18F45Q10         | PIC18F26Q10<br>PIC18F46Q10         | PIC18F27Q10<br>PIC18F47Q10         |  |

|        | 00 0000h<br>00 07FFh  | Boot Block 1 KW<br>CP, WRTB, EBTRB | Boot Block 1 KW<br>CP, WRTB, EBTRB | Boot Block 1 KW<br>CP WRTB, EBTRB  | Boot Block 1 KW<br>CP WRTB, EBTRB  |  |

|        | 00 0800h              | Block 0<br>3 KW<br>CP, WRT0, EBTR0 | Block 0<br>3 KW<br>CP, WRT0, EBTR0 | Block 0                            | Block 0                            |  |

|        | 00 1FFFh<br>00 2000h  | Block 1<br>4 KW                    | Block 1<br>4 KW                    | 7 KW<br>CP, WRT0, EBTR0            | 7 KW<br>CP, WRT0, EBTR0            |  |

|        | 00 3FFFh              | CP, WRT1, EBTR1                    | CP, WRT1, EBTR1                    |                                    |                                    |  |

|        | 00 4000h              |                                    | Block 2<br>4 KW                    |                                    |                                    |  |

|        | 00 5FFFh<br>00 6000h  |                                    | CP, WRT2, EBTR2  Block 3           | Block 1<br>8 KW<br>CP, WRT1, EBTR1 | Block 1<br>8 KW<br>CP, WRT1, EBTR1 |  |

|        | 00 7FFFh              |                                    | 4 KW<br>CP, WRT3, EBTR3            | OI, WICH, EDITO                    | OI, WICH, EDITCH                   |  |

| PFM    | 00 8000h              | Not present                        |                                    | Block 2<br>8 KW                    | Block 2<br>8 KW                    |  |

|        | 00 BFFFh<br>00 C000h  |                                    |                                    | CP, WRT2, EBTR2  Block 3           | CP, WRT2, EBTR2  Block 3           |  |

|        | 00 FFFFh              |                                    |                                    | 8 KW<br>CP, WRT3, EBTR3            | 8 KW<br>CP, WRT3, EBTR3            |  |

|        | 01 0000h<br>01 3FFFh  |                                    |                                    |                                    | Block 4<br>8 KW<br>CP, WRT4, EBTR4 |  |

|        | 01 4000h              |                                    | Not present                        |                                    | Block 5<br>8 KW                    |  |

|        | 01 7FFFh<br>01 8000h  |                                    |                                    | Not present                        | CP, WRT6, EBTR5  Block 6 8 KW      |  |

|        | 01 BFFFh              |                                    |                                    |                                    | CP, WRT6, EBTR6                    |  |

|        | 01 C000h<br>01 FFFFh  |                                    |                                    |                                    | Block 7<br>8 KW<br>CP, WRT7, EBTR7 |  |

|        | 30 0000h              |                                    |                                    |                                    | l                                  |  |

| CONFIG |                       |                                    |                                    | ords<br>RTC                        |                                    |  |

|        | 30 000Bh              |                                    |                                    |                                    |                                    |  |

|        | 31 0000h              | 050.19                             | Mordo                              |                                    |                                    |  |

| Data   | 31 000011<br>31 00FFh | 256 V<br>CPD, '                    |                                    | 1 1                                | <b>&lt;</b> W                      |  |

| EEPROM | 31 0100h<br>31 03FFh  | Unimple                            | emented                            | CPD, WRTD                          |                                    |  |

#### 2.1 User ID Location

A user may store identification information (User ID) in 128 designated locations. The User ID locations are mapped to 20 0000h-20 00FFh. Each location is 16 bits in length. It is recommended that the Most Significant nibble of each ID be Fh. In doing so, if the user code inadvertently tries to execute from the ID space, the ID data will execute as a NOP. Code protection has no effect on these memory locations. Each location may be read with code protection enabled or disabled.

#### 2.2 Device/Revision ID

The 16-bit Device ID Word is located at 3F FFFEh and the 16-bit Revision ID is located at 3F FFFCh. These locations are read-only and cannot be erased or modified.

#### REGISTER 2-1: DEVICEID: DEVICE ID REGISTER

| R      | R         | R | R | R | R | R | R     |  |  |

|--------|-----------|---|---|---|---|---|-------|--|--|

|        | DEV[15:8] |   |   |   |   |   |       |  |  |

| bit 15 |           |   |   |   |   |   | bit 8 |  |  |

| R        | R | R | R | R | R | R | R     |

|----------|---|---|---|---|---|---|-------|

| DEV[7:0] |   |   |   |   |   |   |       |

| bit 7    |   |   |   |   |   |   | bit 0 |

| Legend:          |                  |                      |                    |

|------------------|------------------|----------------------|--------------------|

| R = Readable bit | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 15-0 **DEV[15:0]:** Device ID bits (see Table B-1)

#### REGISTER 2-2: REVISIONID: REVISION ID REGISTER

| R      | R | R | R | R           | R | R | R     |

|--------|---|---|---|-------------|---|---|-------|

| 1      | 0 | 1 | 0 | MJRREV[5:2] |   |   |       |

| bit 15 |   |   |   |             |   |   | bit 8 |

| R     | R       | R           | R | R | R | R | R     |

|-------|---------|-------------|---|---|---|---|-------|

| MJRRE | EV[1:0] | MNRREV[5:0] |   |   |   |   |       |

| bit 7 |         |             |   |   |   |   | bit 0 |

| Legend:          |                  |                     |                    |

|------------------|------------------|---------------------|--------------------|

| R = Readable bit | '1' = Bit is set | 0' = Bit is cleared | x = Bit is unknown |

bit 15-12 Read as '1010'

These bits are fixed with value, '1010', for all devices in this programming specification.

bit 11-6 MJRREV[5:0]: Major Revision ID bits

These bits are used to identify a major revision. A major revision is indicated by an all layer revision (A0, B0, C0, etc...).

Revision A = 6'b00 0000

bit 5-0 MNRREV[5:0]: Minor Revision ID bits

These bits are used to identify a minor revision.

**Revision A0 = 6'b00 0000**

#### 2.3 Configuration Words

The devices have six Configuration Words, starting at address, 30 0000h. The individual bits within these Configuration Words are critical to the correct operation of the system. Configuration bits enable or disable specific features, placing these controls outside the normal software process, and they establish configured values prior to the execution of any software.

In terms of programming, these important Configuration bits should be considered:

1. LVP: Low-Voltage Programming Enable bit

```

1 = ON - Low-Voltage Programming is enabled. \overline{MCLR}/VPP pin function is \overline{MCLR}. MCLRE Configuration bit is ignored.

```

0 = OFF - High voltage on MCLR/VPP must be used for programming.

It is important to note that the LVP bit cannot be written (to '0') while operating from the LVP programming interface. The purpose of this rule is to prevent the user from dropping out of LVP mode while programming from LVP mode, or accidentally eliminating LVP mode from the configuration state. For more information, see **Section 3.1.2 "Low-Voltage Programming (LVP) Mode"**.

2. MCLRE: Master Clear (MCLR) Enable bit

3. CPD: Data NVM (EEPROM) Memory Code Protection bit

```

1 = OFF - Data NVM code protection is disabled 0 = ON - Data NVM code protection is enabled

```

4. CP: User NVM Program Memory Code Protection bit

```

1 = OFF - User NVM code protection is disabled 0 = ON - User NVM code protection is enabled

```

For more information on code protection, see Section 3.3 "Code Protection".

#### 3.0 PROGRAMMING ALGORITHMS

#### 3.1 Program/Verify Mode

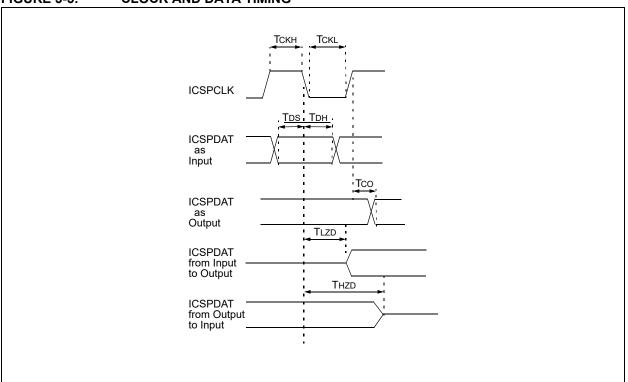

In Program/Verify mode, the program memory and the configuration memory can be accessed and programmed in serial fashion. ICSPDAT and ICSPCLK are used for the data and the clock, respectively. All commands and data words are transmitted, MSb first. Data changes on the rising edge of the ICSPCLK and is latched on the falling edge. In Program/Verify mode, both the ICSPDAT and ICSPCLK pins are Schmitt Trigger inputs. The sequence that enters the device into Program/Verify mode places all other logic into the Reset state. Upon entering Program/Verify mode, all I/Os are automatically configured as high-impedance inputs and the Program Counter (PC) is cleared.

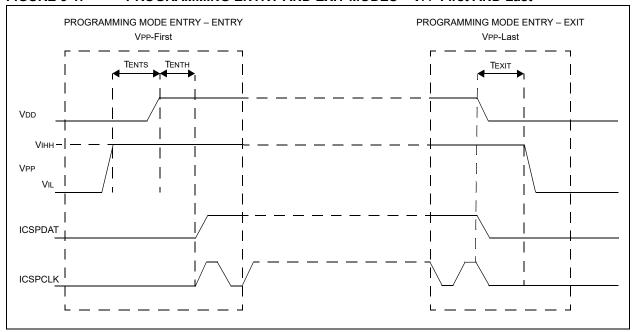

#### 3.1.1 HIGH-VOLTAGE PROGRAM/VERIFY MODE ENTRY AND EXIT

There are two different modes of entering Program/Verify mode via high voltage:

- VPP First Entry mode

- VDD First Entry mode

#### 3.1.1.1 VPP – First Entry Mode

To enter Program/Verify mode via the VPP-First Entry mode, the following sequence must be followed:

- 1. Hold ICSPCLK and ICSPDAT low. All other pins should be unpowered.

- 2. Raise the voltage on MCLR from 0V to VIHH.

- 3. Raise the voltage on VDD from 0V to the desired operating voltage.

The VPP-First Entry mode prevents the device from executing code prior to entering Program/Verify mode. For example, when the Configuration Word has already been programmed to have MCLR disabled (MCLRE = 0), the Power-up Timer disabled (PWRTE = 0) and the internal oscillator selected, the device will execute code immediately. Since this may prevent entry, VPP-First Entry mode is strongly recommended as it prevents user code from changing EEPROM contents or driving pins to affect Test mode entry. See the timing diagram in Figure 3-1.

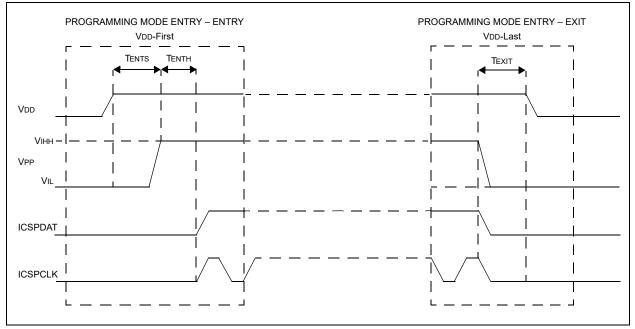

#### 3.1.1.2 VDD – First Entry Mode

To enter Program/Verify mode via the VDD-First Entry mode, the following sequence must be followed:

- 1. Hold ICSPCLK and ICSPDAT low.

- 2. Raise the voltage on VDD from 0V to the desired operating voltage.

- 3. Raise the voltage on MCLR from VDD or below to VIHH.

The VDD-First Entry mode is useful for programming the device when VDD is already applied, for it is not necessary to disconnect VDD to enter Program/Verify mode. See the timing diagram in Figure 3-2.

#### 3.1.1.3 Program/Verify Mode Exit

To exit Program/Verify mode, lower MCLR from VIHH or lower (VIL). VPP-First Entry mode should use VPP-Last Exit mode (see Figure 3-1). VDD-First Entry mode should use VDD-Last Exit mode (see Figure 3-2).

FIGURE 3-1: PROGRAMMING ENTRY AND EXIT MODES - VPP-First AND Last

FIGURE 3-2: PROGRAMMING ENTRY AND EXIT MODES – VDD-First AND Last

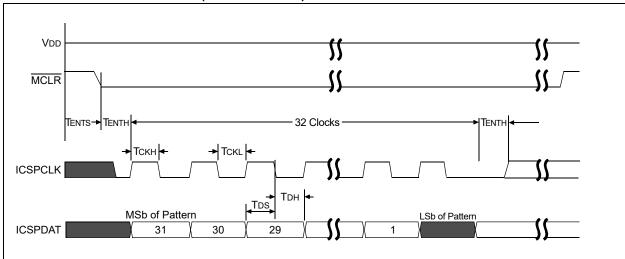

#### 3.1.2 LOW-VOLTAGE PROGRAMMING (LVP) MODE

The Low-Voltage Programming mode allows the devices to be programmed using VDD only, without high voltage. When the LVP bit of the Configuration Word 4 register is set to '1', the Low-Voltage ICSP Programming entry is enabled. To disable the Low-Voltage ICSP mode, the LVP bit must be programmed to '0'. This can only be done while in the High-Voltage Entry mode.

Entry into the Low-Voltage ICSP Program/Verify mode requires the following steps:

- 1. MCLR is brought to VIL.

- 2. A **32-bit key sequence** is presented on ICSPDAT. The LSb of the pattern is a "don't care x". The Program/Verify mode entry pattern detect hardware verifies only the first 31 bits of the sequence and the last clock is required before the pattern detect goes active.

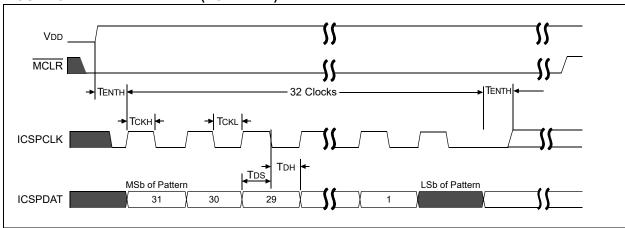

The key sequence is a specific 32-bit pattern, '32' h4d434850' (more easily remembered as MCHP in ASCII). The device will enter Program/Verify mode only if the sequence is valid. The Most Significant bit of the Most Significant nibble must be shifted in first. Once the key sequence is complete, MCLR must be held at VIL for as long as Program/Verify mode is to be maintained. For Low-Voltage Programming timing, see Figure 3-3 and Figure 3-4.

FIGURE 3-3: LVP ENTRY (POWERING UP)

FIGURE 3-4: LVP ENTRY (POWERED)

Exiting Program/Verify mode is done by raising MCLR from below VIL to VIH level (or higher, up to VDD).

**Note:** To enter LVP mode, the MSb of the Most Significant nibble must be shifted in first. This differs from entering the key sequence on some other device families.

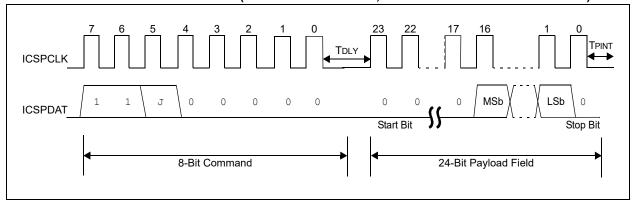

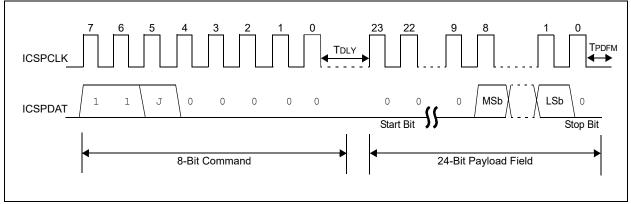

#### 3.1.3 PROGRAM/VERIFY COMMANDS

Once a device has entered ICSP Program/Verify mode (using either high-voltage or LVP entry), the programming host device may issue six commands to the microcontroller, each eight bits in length. The commands are summarized in Table 3-1. The commands are used to erase or program the device based on the location of the Program Counter (PC).

Some of the 8-bit commands also have a data payload associated with it (such as Load PC Address and Read Data from NVM).

If the programming host device issues an 8-bit command byte that has a data payload associated with it, the host device is responsible for sending an additional 24 clock pulses (for example, three 8-bit bytes) in order to send or receive the payload data associated with the command.

The payload field size is used so as to be compatible with many 8-bit SPI-based systems. Within each 24-bit payload field, the first bit transmitted is always a Start bit, followed by a variable number of Pad bits, followed by the useful data payload bits and ending with one Stop bit. The useful data payload bits are always transmitted, Most Significant bit (MSb) first.

When the programming device issues a command that involves a host to microcontroller payload (for example, Load PC Address), the Start, Stop and Pad bits should all be driven by the programmer to '0'. When the programming host device issues a command that involves microcontroller to host payload data (for example, Read Data from NVM), the Start, Stop and Pad bits should be treated as "don't care" bits and the values should be ignored by the host.

When the programming host device issues an 8-bit command byte to the microcontroller, the host should wait a minimum amount of delay (which is command-specific) prior to sending any additional clock pulses (associated with either a 24-bit data payload field or the next command byte).

TABLE 3-1: ICSP™ COMMAND SET SUMMARY(1)

|                                | Command Value       |       | Davidand            | Dalawaffan             |                                                                                                                    |

|--------------------------------|---------------------|-------|---------------------|------------------------|--------------------------------------------------------------------------------------------------------------------|

| Command Name                   | Binary<br>(MSb LSb) | Hex   | Payload<br>Expected | Delay after<br>Command | Data/Note                                                                                                          |

| Load PC Address                | 1000 0000           | 80    | Yes                 | TDLY                   | Payload Value = PC                                                                                                 |

| Bulk Erase Program<br>Memory   | 0001 1000           | 18    | No                  | TERAB                  | Depending on the current value of the PC, one or more memory regions                                               |

| Sector Erase Program<br>Memory | 1111 0000           | F0    | No                  | TERAS                  | The sector addressed by the MSbs of the PC is erased; LSbs are ignored                                             |

| Read Data from NVM             | 1111 11J0           | FC/FE | Yes                 | TDLY                   | Data output '0' if code-protect is enabled: J = 0: PC is unchanged J = 1: PC = PC + n <sup>(2)</sup> after reading |

| Increment Address              | 1111 1000           | F8    | No                  | TDLY                   | $PC = PC + n^{(2)}$                                                                                                |

| Program Data                   | 11J0 0000           | C0/E0 | Yes                 | TPROG                  | Payload value = Data Word J = 0: PC is unchanged J = 1: PC = PC + 2 after writing                                  |

- Note 1: All clock pulses for both the 8-bit commands and the 24-bit payload fields are generated by the host programming device. The microcontroller does not drive the ICSPCLK line. The ICSPDAT signal is a bidirectional data line. For all commands and payload fields, except the Read Data from NVM payload, the host programming device continuously drives the ICSPDAT line. Both the host programmer device and the microcontroller should latch received ICSPDAT values on the falling edge of the ICSPCLK line. When the microcontroller receives ICSPDAT line values from the host programmer, the ICSPDAT values must be valid a minimum of TDS before the falling edges of ICSPCLK and should remain valid for a minimum of TDH after the falling edge of ICSPDAT. See Figure 3-5.

- **2:** PC is incremented by n = 1 for data memory and n = 2 for all other regions.

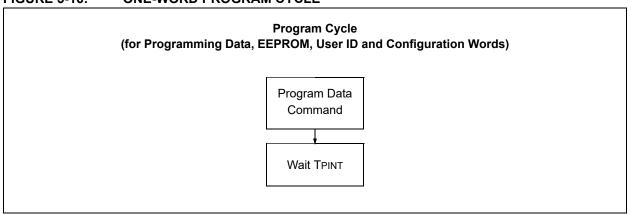

#### 3.1.3.1 Program Data

The Program Data command is used to program one NVM word (for example, one 16-bit instruction word for program memory/configuration memory/User ID memory or one 8-bit data for a Data EEPROM Memory address). The payload data is written into program or EEPROM memory immediately after the Programming Data command is issued (see Section 3.2 "Programming Algorithms"). Depending on the value of bit 5 of the command, the PC may or may not be incremented (see Table 3-1).

FIGURE 3-6: PROGRAM DATA (PROGRAM MEMORY, USER ID AND CONFIGURATION)

#### FIGURE 3-7: PROGRAM DATA (DATA EEPROM)

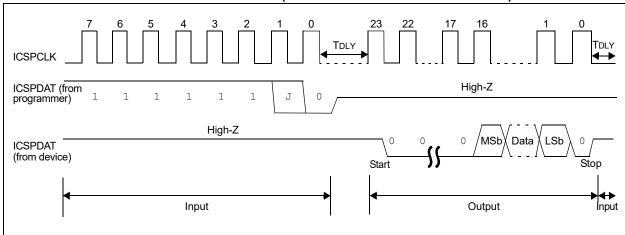

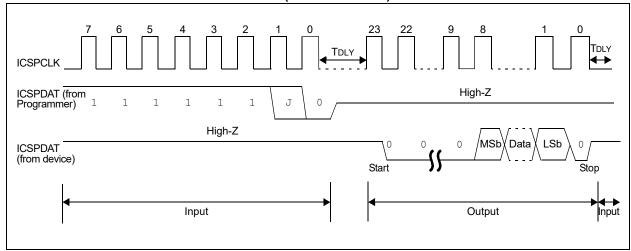

#### 3.1.3.2 Read Data from NVM

The Read Data from NVM command will transmit data bits out of the current PC address. The ICSPDAT pin will go into Output mode on the first falling edge of the ICSP data payload clock and it will revert to Input mode (high-impedance) after the 24th falling edge of the ICSP data payload clock. The Start and Stop bits are only one-half of a bit time wide; therefore, they should be ignored by the host programmer device, since the latched value may be indeterminate. Additionally, the host programmer device should only consider the MSb to LSb payload bits as valid and should ignore the values of the Pad bits. If the memory region is code-protected ( $\overline{\text{CP}}$  or  $\overline{\text{DP}}$ ), the data will be read as zeros (see Figure 3-8 and Figure 3-9). Depending on the value of bit[1] of the command, the PC may or may not be incremented (see Table 3-1). The Read Data from NVM command can be used to read data for Program Flash Memory (see Figure 3-8) or the Data EEPROM Memory (see Figure 3-9).

FIGURE 3-8: READ DATA FROM NVM (PFM OR CONFIGURATION WORDS)

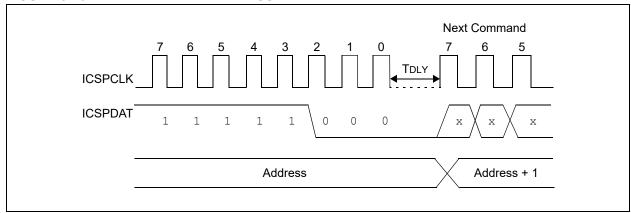

#### 3.1.3.3 Increment Address

The address is incremented when this command is received. Depending on the current value of the Program Counter, the increment varies. If the PC points to PFM, then the PC is incremented by 2; if the PC points to data EEPROM, then it is incremented by 1. It is not possible to decrement the address. To reset this counter, the user must use the Load PC Address command.

FIGURE 3-10: INCREMENT ADDRESS

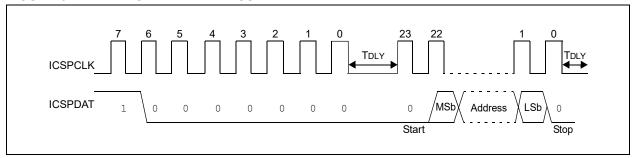

#### 3.1.3.4 Load PC Address

The PC value is set using the supplied data. The address implies the memory panel (PFM or Data EEPROM Memory) to be accessed (see Figure 3-11).

FIGURE 3-11: LOAD PC ADDRESS

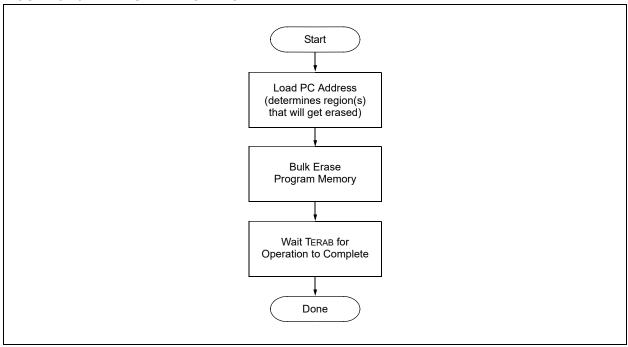

#### 3.1.3.5 Bulk Erase Program Memory

The Bulk Erase Program Memory command affects specific portions of the memory depending on the initial value of the Program Counter. Whenever a Bulk Erase command is executed, the device will erase all bytes within the regions listed in Table 3-2.

TABLE 3-2: BULK ERASE

| Address           | Area(s) Erased                                               |                                                                             |  |  |  |  |  |

|-------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|--|

| Address           | CP = 1 and CPD = 1 (both disabled)                           | CP = x or CPD = x (either enabled)                                          |  |  |  |  |  |

| 00 0000h-01 FFFFh | Program Flash Memory<br>Configuration Words                  | Program Flash Memory<br>Data EEPROM<br>Configuration Words                  |  |  |  |  |  |

| 20 0000h-20 00FFh | Program Flash Memory<br>User ID Words<br>Configuration Words | Program Flash Memory<br>Data EEPROM<br>User ID Words<br>Configuration Words |  |  |  |  |  |

| 30 0000h-30 00FFh | Program Flash Memory<br>User ID Words<br>Configuration Words | Program Flash Memory<br>Data EEPROM<br>User ID Words<br>Configuration Words |  |  |  |  |  |

| 31 0000h-3F FFFFh | Data EEPROM Only                                             | Data EEPROM Only                                                            |  |  |  |  |  |

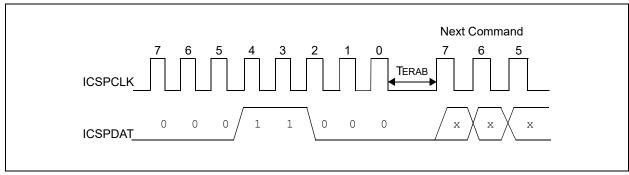

After receiving the Bulk Erase Program Memory command, the erase will not complete until the time interval, TERAB, has expired (see Figure 3-12). The programming host device should not issue another 8-bit command until after the TERAB interval has fully elapsed.

FIGURE 3-12: BULK ERASE MEMORY

#### 3.1.3.6 Sector Erase Program Memory

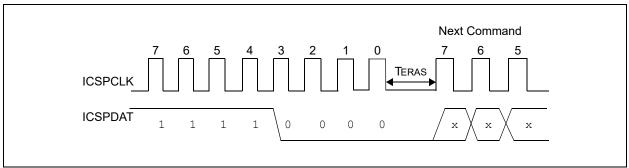

The Sector Erase Program Memory command will erase an individual sector based on the current address of the Program Counter. If the program memory is code-protected, the Sector Erase Memory command will be ignored. The Bulk Erase command must be used to erase code-protected memory.

The Flash memory sector defined by the current PC will be erased. The user must wait TERAS for erasing to complete (see Figure 3-13). Sector Erase should be used for program memory and User ID regions only. Configuration and data regions should be erased with the Bulk Erase method.

FIGURE 3-13: SECTOR ERASE MEMORY

## 3.2 Programming Algorithms

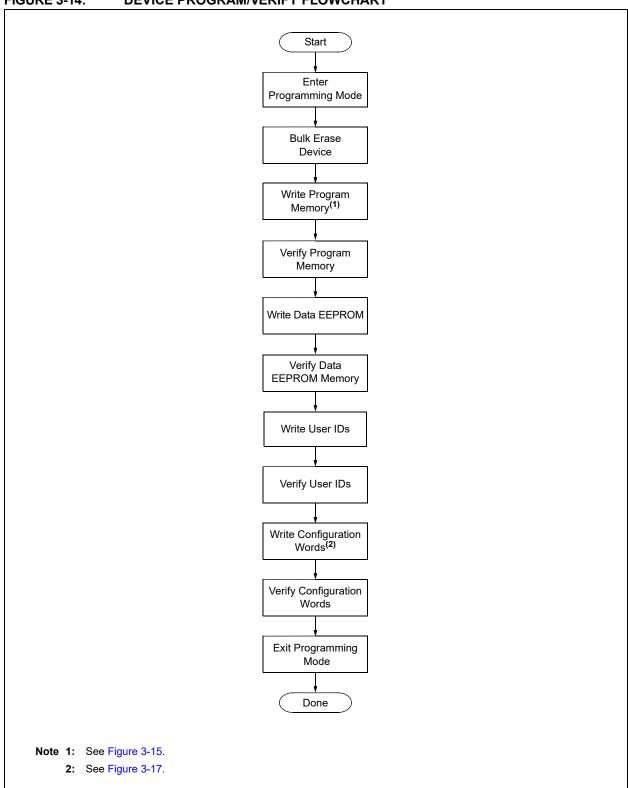

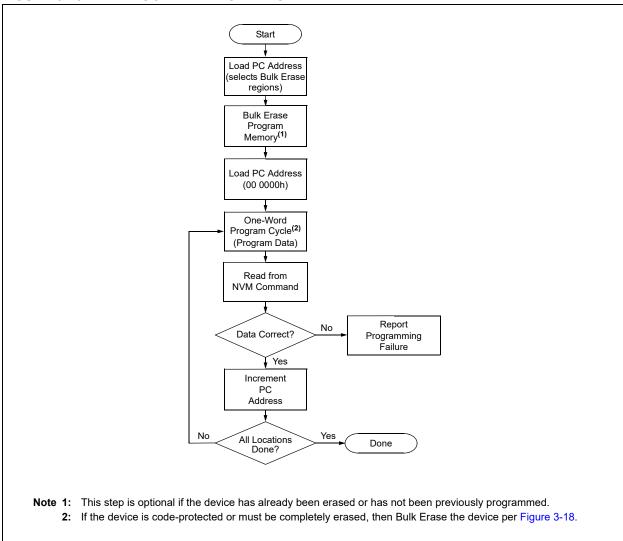

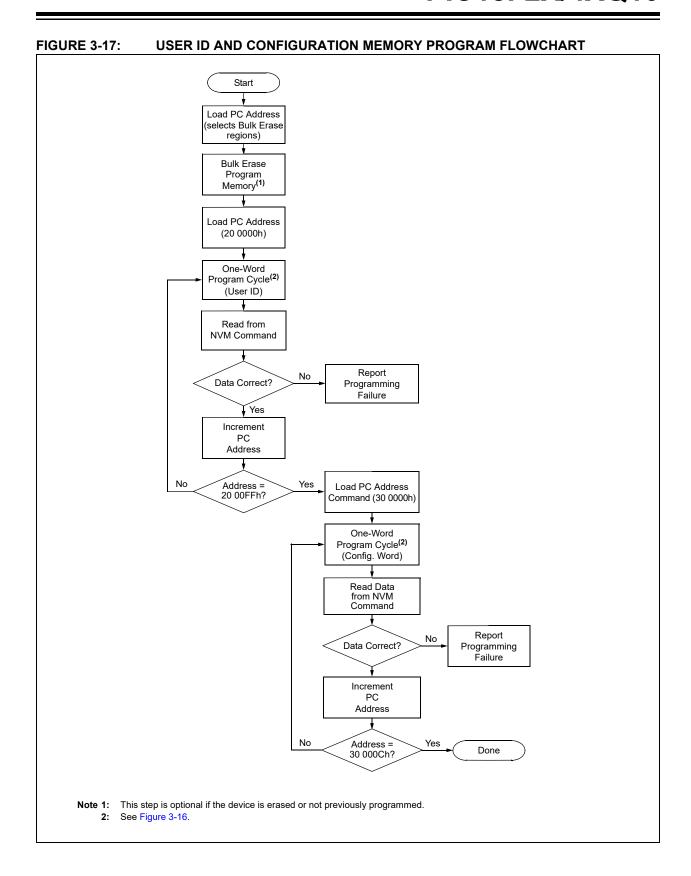

The Program Flash Memory, User ID and Configuration Word regions are programmed one word at a time (Figure 3-15). The EEPROM memory is programmed one byte at a time.

FIGURE 3-14: DEVICE PROGRAM/VERIFY FLOWCHART

FIGURE 3-15: PROGRAM MEMORY FLOWCHART

#### FIGURE 3-16: ONE-WORD PROGRAM CYCLE

FIGURE 3-18: BULK ERASE FLOWCHART

#### 3.3 Code Protection

Code protection is controlled using the  $\overline{\mathsf{CP}}$  bit. When code protection is enabled, all program memory locations read as '0'. Further programming is disabled for the program memory until the next Bulk Erase operation is performed. Program memory can still be programmed and read during program execution.

The User ID locations and Configuration Words can be programmed and read out regardless of the code protection settings.

#### 3.3.1 PROGRAM MEMORY

Code protection is enabled by programming the  $\overline{\mathsf{CP}}$  bit to '0'. The only way to disable code protection is to use the Bulk Erase Program Memory command (with the PC set to an address so as to Bulk Erase all program Flash contents).

#### 3.3.2 DATA EEPROM MEMORY

Data EEPROM Memory protection is enabled by programming the  $\overline{\text{CPD}}$  bit to '0'. The only way to disable code protection is to use the Bulk Erase Program Memory command.

#### 3.4 Hex File Usage

#### 3.4.1 EMBEDDING CONFIGURATION WORD INFORMATION IN THE HEX FILE

To allow portability of code, a programmer is required to read the Configuration Word locations from the Hex file. If Configuration Word information is not present in the Hex file, then a simple warning message should be issued. Similarly, while saving a Hex file, all Configuration Word information must be included. An option to not include the Configuration Word information may be provided. When embedding Configuration Word information in the Hex file, it should start at address, 300000h.

Microchip Technology Inc. feels strongly that this feature is important for the benefit of the end customer.

#### 3.4.2 EMBEDDING DATA EEPROM INFORMATION IN THE HEX FILE

To allow portability of code, a programmer is required to read the data EEPROM information from the Hex file. If data EEPROM information is not present, a simple warning message should be issued. Similarly, when saving a Hex file, all data EEPROM information must be included. An option to not include the data EEPROM information may be provided. When embedding data EEPROM information in the Hex file, it should start at address, 310000h.

Microchip Technology Inc. believes that this feature is important for the benefit of the end customer.

#### 3.5 Checksum Computation

The checksum is calculated by two different methods, dependent on the setting of the  $\overline{\text{CP}}$  Configuration bit. Refer to Appendix B: "PIC18F2X/4XQ10 Device ID, Checksums and Pinout Descriptions" for checksum computation examples.

#### 3.5.1 PROGRAM CODE PROTECTION DISABLED

With the program code protection disabled, the checksum is computed by reading the contents of the program memory locations and adding up the program memory data, starting at address, 00 0000h, up to the maximum user-addressable location (e.g., 00 FFFFh for the PIC18F46Q10 device). Any Carry bits exceeding 16 bits are ignored. Additionally, the relevant bits of the Configuration Words are added to the checksum. All unimplemented Configuration bits are masked to '0'.

#### 3.5.2 PROGRAM CODE PROTECTION ENABLED

When the MPLAB® IDE check box for "File->Project Properties->Conf:->Building->Insert unprotected checksum in User ID memory" is checked, then the 16-bit checksum of the equivalent unprotected device is computed and stored in the User ID. The unprotected checksum is distributed, one nibble per ID location. Each nibble is right justified. All other User ID locations are cleared to 0x0000.

The checksum of a code-protected device is computed in the following manner:

- · All of the User ID locations are added to create the sum ID

- · The sum ID is then added to the Configuration bits

- All unimplemented Configuration bits are masked to '0'

Note:

The checksum calculation differs depending on the code-protect setting. Since the code memory locations read out differently, depending on the code-protect setting, the examples in **Appendix B: "PIC18F2X/4XQ10 Device ID, Checksums and Pinout Descriptions"** describe how to manipulate the actual code memory values to simulate the values that would be read from a protected device. When calculating a checksum by reading a device, the entire code memory can simply be read and summed. The Configuration Word and ID locations can always be read.

#### 4.0 ELECTRICAL SPECIFICATIONS

Refer to the device specific data sheet for absolute maximum ratings.

TABLE 4-1: AC/DC CHARACTERISTICS TIMING REQUIREMENTS FOR PROGRAM/VERIFY MODE

| AC/DC CH | HARACTERISTICS                                                                    | Standard Operating Conditions Production tested at +25°C |           |           |       |                        |  |  |  |  |

|----------|-----------------------------------------------------------------------------------|----------------------------------------------------------|-----------|-----------|-------|------------------------|--|--|--|--|

| Sym.     | Characteristics                                                                   | Min.                                                     | Тур.      | Max.      | Units | Conditions/Comments    |  |  |  |  |

|          | Programming Supply Voltages and Currents                                          |                                                          |           |           |       |                        |  |  |  |  |

| VDD      | Supply Voltage (VDDMIN, VDDMAX)                                                   | 1.80                                                     | _         | 5.50      | V     | (Note 1)               |  |  |  |  |

| VPEW     | Read/Write and Sector Erase Operations                                            | VDDMIN                                                   | _         | VDDMAX    | V     |                        |  |  |  |  |

| VBE      | Bulk Erase Operations                                                             | VBORMAX                                                  | _         | VDDMAX    | V     | (Note 2)               |  |  |  |  |

| Iddi     | Current on VDD, Idle                                                              | _                                                        | _         | 1.0       | mA    |                        |  |  |  |  |

| IDDP     | Current on VDD, Programming                                                       | _                                                        | _         | 10        | mA    |                        |  |  |  |  |

|          | VPP                                                                               |                                                          |           |           |       |                        |  |  |  |  |

| IPP      | Current on MCLR/VPP                                                               | _                                                        | _         | 600       | μΑ    |                        |  |  |  |  |

| VIHH     | High Voltage on MCLR/VPP for Program/Verify Mode Entry                            | 7.9                                                      | _         | 9.0       | V     |                        |  |  |  |  |

| TVHHR    | MCLR Rise Time (VIL to VIHH) for Program/Verify Mode Entry                        | _                                                        | _         | 1.0       | μs    |                        |  |  |  |  |

|          | I/O Pins                                                                          |                                                          |           |           |       |                        |  |  |  |  |

| VIH      | (ICSPCLK, ICSPDAT, MCLR/VPP) Input<br>High Level                                  | 0.8 VDD                                                  | _         | VDD       | V     |                        |  |  |  |  |

| VIL      | (ICSPCLK, ICSPDAT, MCLR/VPP) Input Low Level                                      | Vss                                                      | _         | 0.2 VDD   | V     |                        |  |  |  |  |

| Voн      | ICSPDAT Output High Level                                                         | VDD - 0.7                                                | _         | _         | V     | IOH = 3 mA, VDD = 3.0V |  |  |  |  |

| Vol      | ICSPDAT Output Low Level                                                          | _                                                        | _         | Vss + 0.6 | V     | IOL = 6 mA, VDD = 3.0V |  |  |  |  |

|          | Program                                                                           | ming Mode                                                | Entry and | Exit      |       |                        |  |  |  |  |

| TENTS    | Programing Mode Entry Setup Time: ICSPCLK, ICSPDAT Setup Time before VDD or MCLR↑ | 100                                                      | _         | _         | ns    |                        |  |  |  |  |

| TENTH    | Programing Mode Entry Hold Time: ICSPCLK, ICSPDAT Hold Time after VDD or MCLR↑    | 1                                                        | _         | _         | ms    |                        |  |  |  |  |

|          | Se                                                                                | rial Progra                                              | m/Verify  |           |       |                        |  |  |  |  |

| TCKL     | Clock Low Pulse Width                                                             | 100                                                      |           | _         | ns    |                        |  |  |  |  |

| Тскн     | Clock High Pulse Width                                                            | 100                                                      | _         | _         | ns    |                        |  |  |  |  |

| TDS      | Data in Setup Time before Clock↓                                                  | 100                                                      | _         | _         | ns    |                        |  |  |  |  |

| TDH      | Data in Hold Time after Clock↓                                                    | 100                                                      |           | _         | ns    |                        |  |  |  |  |

| Tco      | Clock↑ to Data Out Valid (during a Read Data command)                             | 0                                                        | _         | 80        | ns    |                        |  |  |  |  |

Note 1: Bulk Erased devices default to Brown-out Reset enabled with BORV = 'b11 (low trip point). VDDMIN is the VBOR threshold (with BORV = 'b11) when performing Low-Voltage Programming on a Bulk Erased device to ensure that the device is not held in Brown-out Reset.

<sup>2:</sup> In high voltage test mode entry, the hardware requires VDD to be above the lowest available BOR threshold, ~1.9V nominal setting, in order to perform Bulk Erase operations. This threshold does not depend on the BORV Configuration bit settings. Refer to the microcontroller device data sheet specifications for min./typ./max. limits of the VBOR level.

**<sup>3:</sup>** *n* = number of bytes in the data memory. Bulk Erase of data memory includes an additional write of FFh for each byte in the data memory.

TABLE 4-1: AC/DC CHARACTERISTICS TIMING REQUIREMENTS FOR PROGRAM/VERIFY MODE (CONTINUED)

| AC/DC CH | IARACTERISTICS                                                                                     | Standard Operating Conditions Production tested at +25°C |      |      |       |                        |  |  |  |

|----------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------|------|------|-------|------------------------|--|--|--|

| Sym.     | Characteristics                                                                                    | Min.                                                     | Тур. | Max. | Units | Conditions/Comments    |  |  |  |

| TLZD     | Clock↓ to Data Low-Impedance (during a Read Data from NVM command)                                 | 0                                                        | _    | 80   | ns    |                        |  |  |  |

| THZD     | Clock↓ to Data High-Impedance (during a Read Data from NVM command)                                | 0                                                        | _    | 80   | ns    |                        |  |  |  |

| TDLY     | Data Input not Driven to Next Clock Input (delay required between command/data or command/command) | 1.0                                                      | _    | _    | μs    |                        |  |  |  |

| TERAB    | Bulk Erase Cycle Time                                                                              | _                                                        | _    | 75   | ms    | Program, Config and ID |  |  |  |

| TERAS    | Sector Erase Cycle Time                                                                            | _                                                        | _    | 11   | ms    |                        |  |  |  |

| TPDFM    | Internally Timed DFM (EEPROM) Programming Operation Time                                           | _                                                        | _    | 11   | ms    | EEPROM memory          |  |  |  |

| TPINT    | Internally Timed Programming Operation Time                                                        | _                                                        | _    | 65   | μs    | Program memory         |  |  |  |

| TEXIT    | Time Delay when Exiting Program/Verify Mode                                                        | 1                                                        | _    | _    | μs    |                        |  |  |  |

- Note 1: Bulk Erased devices default to Brown-out Reset enabled with BORV = `b11 (low trip point). VDDMIN is the VBOR threshold (with BORV = `b11) when performing Low-Voltage Programming on a Bulk Erased device to ensure that the device is not held in Brown-out Reset.

- 2: In high voltage test mode entry, the hardware requires VDD to be above the lowest available BOR threshold, ~1.9V nominal setting, in order to perform Bulk Erase operations. This threshold does not depend on the BORV Configuration bit settings. Refer to the microcontroller device data sheet specifications for min./typ./max. limits of the VBOR level.

- **3:** *n* = number of bytes in the data memory. Bulk Erase of data memory includes an additional write of FFh for each byte in the data memory.

#### APPENDIX A: REVISION HISTORY

#### **Revision G (3/2019)**

Updated Examples B-3 and B-4; and Section 3.5.2.

#### **Revision F (10/2018)**

Updated Table 3-3 - TPINT.

#### **Revision E (5/2018)**

Updated Table B-1.

#### **Revision D (4/2018)**

Updated Figure 2-1; Register B-1; and Tables 2-1, 3-1, 3-2, B-1, B-2 and B-3.

#### **Revision C (11/2017)**

Updated Figures 3-3 and 3-4 and Table 3-3.

#### **Revision B (08/2017)**

Updated Figure 3-7. Updated Table 3-3; adding TPDFM.

#### Revision A (02/2017)

Initial release of the document.

## APPENDIX B: PIC18F2X/4XQ10 DEVICE ID, CHECKSUMS AND PINOUT DESCRIPTIONS

## TABLE B-1: CONFIGURATION WORD AND MASK

|             |           | Confi      | ig. 1L     | Conf       | ig. 1H     | Confi      | ig. 2L     | Confi      | ig. 2H     | Conf       | ig. 3L     | Confi      | g. 3H      | Confi      | ig. 4L     | Confi      | ig. 4H     | C           | onfig.         | 5L         | C           | onfig.         | 5H         | Conf | ig. 6L     | Confi | ig. 6H     |

|-------------|-----------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|-------------|----------------|------------|-------------|----------------|------------|------|------------|-------|------------|

| Device      | Device ID | Word (Hex) | Mask (Hex) | Unprotected | Code-Protected | Mask (Hex) | Unprotected | Code-Protected | Mask (Hex) | Word | Mask (Hex) | Word  | Mask (Hex) |

| PIC18F46Q10 | 7120h     | FF         | 77         | FF         | 29         | FF         | E3         | FF         | BF         | FF         | 7F         | FF         | 3F         | FF         | 0F         | FF         | 37         | FF          | FE             | 03         | FF          | FF             | 00         | FF   | 0F         | FF    | 02         |

| PIC18F45Q10 | 7140h     | FF         | 77         | FF         | 29         | FF         | E3         | FF         | BF         | FF         | 7F         | FF         | 3F         | FF         | 0F         | FF         | 37         | FF          | FE             | 03         | FF          | FF             | 00         | FF   | 0F         | FF    | 02         |

| PIC18F26Q10 | 7180h     | FF         | 77         | FF         | 29         | FF         | E3         | FF         | BF         | FF         | 7F         | FF         | 3F         | FF         | 0F         | FF         | 37         | FF          | FE             | 03         | FF          | FF             | 00         | FF   | 0F         | FF    | 02         |

| PIC18F25Q10 | 71A0h     | FF         | 77         | FF         | 29         | FF         | E3         | FF         | BF         | FF         | 7F         | FF         | 3F         | FF         | 0F         | FF         | 37         | FF          | FE             | 03         | FF          | FF             | 00         | FF   | 0F         | FF    | 02         |

| PIC18F24Q10 | 71C0h     | FF         | 77         | FF         | 29         | FF         | E3         | FF         | BF         | FF         | 7F         | FF         | 3F         | FF         | 03         | FF         | 37         | FF          | FE             | 03         | FF          | FF             | 00         | FF   | 03         | FF    | 02         |

| PIC18F27Q10 | 7100h     | FF         | 77         | FF         | 29         | FF         | E3         | FF         | BF         | FF         | 7F         | FF         | 3F         | FF         | FF         | FF         | 37         | FF          | FE             | 03         | FF          | FF             | 00         | FF   | FF         | FF    | 02         |

| PIC18F47Q10 | 70E0h     | FF         | 77         | FF         | 29         | FF         | E3         | FF         | BF         | FF         | 7F         | FF         | 3F         | FF         | FF         | FF         | 37         | FF          | FE             | 03         | FF          | FF             | 00         | FF   | FF         | FF    | 02         |

TABLE B-2: CHECKSUM VALUES

|             |       | Checksum                          |                |                                    |  |  |  |  |  |  |  |  |

|-------------|-------|-----------------------------------|----------------|------------------------------------|--|--|--|--|--|--|--|--|

| Device      | U     | nprotected                        | Code-Protected |                                    |  |  |  |  |  |  |  |  |

|             | Blank | 0AAh at First and<br>Last Address | Blank          | 00AAh at First and<br>Last Address |  |  |  |  |  |  |  |  |

| PIC18F46Q10 | 035A  | 02B0                              | 036B           | 0366                               |  |  |  |  |  |  |  |  |

| PIC18F45Q10 | 835A  | 82B0                              | 0373           | 036E                               |  |  |  |  |  |  |  |  |

| PIC18F26Q10 | 035A  | 02B0                              | 036B           | 0366                               |  |  |  |  |  |  |  |  |

| PIC18F25Q10 | 835A  | 82B0                              | 0373           | 036E                               |  |  |  |  |  |  |  |  |

| PIC18F24Q10 | C342  | C298                              | 0356           | 0360                               |  |  |  |  |  |  |  |  |

| PIC18F27Q10 | 053A  | 0490                              | 054B           | 0546                               |  |  |  |  |  |  |  |  |

| PIC18F47Q10 | 053A  | 0490                              | 054B           | 0546                               |  |  |  |  |  |  |  |  |

# EXAMPLE B-1: CHECKSUM COMPUTED WITH PROGRAM CODE PROTECTION DISABLED: PIC18F24Q10, BLANK DEVICE

| 0 (14 ) ( 0000) ( 0555)                                                          | 00001 (10001 # 00551)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| •                                                                                | C000h (4000h * 00FFh)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| •                                                                                | FFh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| -                                                                                | 77h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| •                                                                                | FFh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| •                                                                                | 29h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| •                                                                                | FFh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Configuration Word 2L Mask                                                       | E3h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Configuration Word 2H                                                            | FFh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Configuration Word 2H Mask                                                       | BFh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Configuration Word 3L                                                            | FFh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Configuration Word 3L Mask                                                       | 7Fh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |