# AT11628: SAM D21 SERCOM I2C Configuration

ATSAMD21J18

### Introduction

This application note explains the various features of SERCOM I<sup>2</sup>C in the Atmel<sup>®</sup> SAM D21 microcontrollers and its configurations with example codes and corresponding scope shots.

For demonstration purpose two SAM D21 Xplained Pro boards will be used.

#### **Features**

- Combined interface configurable as one of the following:

- I<sup>2</sup>C Two-wire serial interface (SMbus compatible)

- SPI Serial Peripheral Interface

- USART Universal Synchronous/Asynchronous Receiver/Transmitter

- Single transmit buffer and double receive buffers

- Baud-rate generator

- · Address match/mask logic

- Operational in all sleep modes

- Can be used with DMA (not supported in SAM D20 MCUs)

# **Table of Contents**

| 1 | Glo | ssary   | /                                                  | 3  |  |

|---|-----|---------|----------------------------------------------------|----|--|

| 2 | Pre | -requi  | isites                                             | 3  |  |

| 3 | SEI | RCOM    | I Implementation in SAM D21 Microcontrollers       | 4  |  |

|   | 3.1 |         |                                                    |    |  |

|   | 3.2 | Block   | Diagram                                            | 4  |  |

|   | 3.3 | Clocks  | S                                                  | 5  |  |

| 4 | Har | dware   | e and Software Requirements                        | 6  |  |

| 5 | Арј | olicati | ion Demonstration                                  | 9  |  |

|   | 5.1 | Basic   | g                                                  |    |  |

|   |     | 5.1.1   | Main Clock                                         | 10 |  |

|   |     | 5.1.2   | Master and Slave Clock                             | 11 |  |

|   |     | 5.1.3   | Clock Flow for Master and Slave                    | 11 |  |

|   |     | 5.1.4   | System Initialization                              | 11 |  |

|   |     | 5.1.5   | I <sup>2</sup> C Clock Initialization              | 11 |  |

|   |     | 5.1.6   | I <sup>2</sup> C Pin Initialization                | 12 |  |

|   |     | 5.1.7   | I <sup>2</sup> C Master Initialization             | 13 |  |

|   |     | 5.1.8   | I <sup>2</sup> C Master Transaction                | 14 |  |

|   |     | 5.1.9   | I <sup>2</sup> C Slave Initialization              | 20 |  |

|   |     | 5.1.10  | 0 I <sup>2</sup> C Slave Transaction               | 21 |  |

|   | 5.2 | High S  | Speed Configuration                                | 28 |  |

|   |     | 5.2.1   | Master and Slave Clock in High-speed Configuration | 28 |  |

|   |     | 5.2.2   | Clock Flow for Master and Slave                    | 29 |  |

|   |     | 5.2.3   | System Initialization                              | 29 |  |

|   |     | 5.2.4   | I <sup>2</sup> C clock Initialization              | 29 |  |

|   |     | 5.2.5   | I <sup>2</sup> C Pin Initialization                | 29 |  |

|   |     | 5.2.6   | I <sup>2</sup> C Master Initialization             | 30 |  |

|   |     | 5.2.7   | I <sup>2</sup> C Master Transaction                | 31 |  |

|   |     | 5.2.8   | I <sup>2</sup> C Slave Initialization              | 36 |  |

|   |     | 5.2.9   | I <sup>2</sup> C Slave Transaction                 | 37 |  |

|   | 5.3 | Addre   | ess Match and Mode Configuration                   | 44 |  |

|   |     | 5.3.1   | Address Match and Mask Mode                        | 44 |  |

|   |     | 5.3.2   | Master and Slave Clock                             | 45 |  |

|   |     | 5.3.3   | Clock Flow for Master and slave                    | 45 |  |

|   |     | 5.3.4   | System Initialization                              | 45 |  |

|   |     | 5.3.5   | I <sup>2</sup> C clock Initialization              | 45 |  |

|   |     | 5.3.6   | I <sup>2</sup> C Pin Initialization                | 45 |  |

|   |     | 5.3.7   | I <sup>2</sup> C Master Initialization             | 45 |  |

|   |     | 5.3.8   | I <sup>2</sup> C Master Transaction                | 46 |  |

|   |     | 5.3.9   | I <sup>2</sup> C Slave Initialization              | 51 |  |

|   |     | 5.3.10  | 0 I <sup>2</sup> C Slave Transaction               | 52 |  |

| 6 | Ref | erenc   | ces                                                | 56 |  |

| 7 |     |         | History                                            |    |  |

# 1 Glossary

SERCOM Serial communication interface

I<sup>2</sup>C Inter-Integrated Circuit

USART Universal asynchronous receiver/transmitter

SPI Serial communication interface

EDBG Embedded Debugger

IDE Integrated Development Environment

SCL Serial Clock Line SDA Serial Data Line

SMBus System Management Bus DMA Direct Memory Access

# 2 Pre-requisites

The solutions discussed in this document require basic familiarity with the following skills and technologies:

- Atmel Studio 6.2 or above

- ASF version 3.22.0 or above

- SAM D21 Xplained Pro kit

# 3 SERCOM Implementation in SAM D21 Microcontrollers

Generally microcontrollers will have separate serial communication modules with different pinouts for each module. Separate dedicated peripherals and user registers will be available for each module. For example USART will be a separate peripheral with dedicated pins for its function and I<sup>2</sup>C will be a separate peripheral with its own dedicated pins.

In SAM D microcontrollers, all the serial peripherals are designed into a single module as serial communication interface (SERCOM). A SERCOM module can be either configured as USART or I<sup>2</sup>C or SPI selectable by user. Each SERCOM will be assigned four pads from PAD0 to PAD3. The functionality of each pad is configurable depending on the SERCOM mode used. Unused pads can be used for other purpose and the SERCOM module will not control them unless it is configured to be used by the SERCOM module.

For example, SERCOM0 can be configured as USART mode with PAD0 as transmit pad and PAD1 as receive pad. Other unused pads (PAD2 and PAD3) can be either used as GPIO pins or can be assigned to some other peripherals. The assignment of SERCOM functionality for different pads is highly flexible making the SERCOM module more advantageous compared to the typical serial communication peripheral implementation.

## 3.1 SERCOM Overview

The serial communication interface (SERCOM) can be configured to support three different modes: I<sup>2</sup>C, SPI, and USART. Once configured and enabled, all SERCOM resources are dedicated to the selected mode.

The SERCOM serial engine consists of a transmitter and receiver, baud-rate generator and address matching functionality. It can be configured to use either the internal generic clock or an external clock, making operation in all sleep modes possible.

## 3.2 Block Diagram

Figure 3-1 depicts the block diagram of a SERCOM module. The module mainly consists of a serial engine handling the actual data transfers and mode specific IPs implementing the corresponding protocol.

SERCOM Register Interface CONTROL/STATUS TX/RX DATA BAUD/ADDR Mode Specific Serial Engine Mode n **Baud Rate** Transmitter Mode 1 Generator PAD[3:0] Mode 0 Address Receiver Match

Figure 3-1. SERCOM Block Diagram

### 3.3 Clocks

SERCOM module needs below clocks for its operation:

- SERCOM bus clock (APB clock)

- SERCOM CORE generic clock

- SERCOM SLOW generic clock

SERCOM bus clock (CLK\_SERCOMx\_APB) is used for reading and writing SERCOM registers by the CPU. This clock is disabled by default and can be enabled or disabled in Power Manager (PM) module.

Two generic clocks are used by the SERCOM module namely GCLK\_SERCOMx\_CORE and GCLK\_SERCOMx\_SLOW. The generic clocks are used for SERCOM's operation. All the SERCOM communication timings are based on the generic clocks.

The core clock (GCLK\_SERCOMx\_CORE) is required to clock the SERCOM while operating as a master, while the slow clock (GCLK\_SERCOMx\_SLOW) is only required for certain functions like I<sup>2</sup>C timeouts.

Note: In this application note only the SERCOM bus clock (CLK\_SERCOMx\_APB) and core clock (GCLK\_SERCOMx\_CORE) are used.

# 4 Hardware and Software Requirements

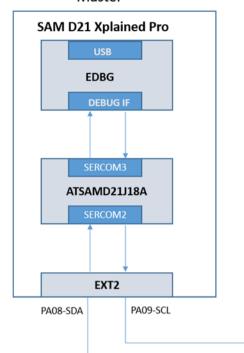

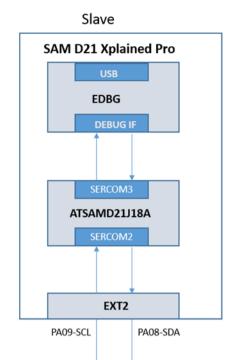

The application demonstration require two SAM D21 Xplained Pro boards. One board will be configured as master and other board as slave.

Figure 4-1. SAM D21 Xplained Pro Board

There are two USB ports on the SAM D21 Xplained Pro board – DEBUG USB and TARGET USB. For debugging the target SAM D21 MCU using the Embedded debugger (EDBG), a Micro-B USB cable should be connected between a host PC running Atmel Studio and the DEBUG USB port on the SAM D21 Xplained Pro board.

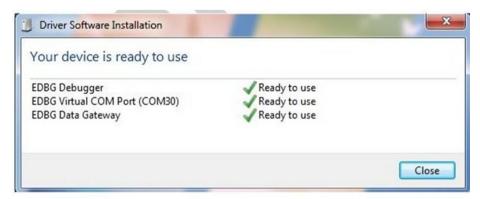

Once the kit is successfully connected for the first time, the Windows® Task bar will pop up a message as shown in Figure 4-2.

Figure 4-2. SAM D21 Xplained Pro Driver Installation

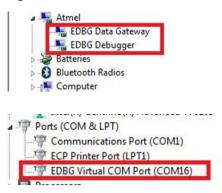

If the driver installation is proper, EDBG will be listed in the Device Manager as shown in Figure 4-3.

Figure 4-3. Successful EDBG Driver Installation

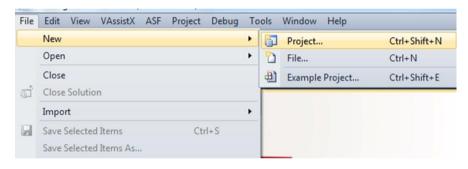

Application codes are tested in Atmel Studio 6.2 with ASF version 3.22.0 and above. Two projects are needed for implementing the functionalities; one for master and other for slave. GCC C ASF Board project from Atmel Studio is used for the implementation.

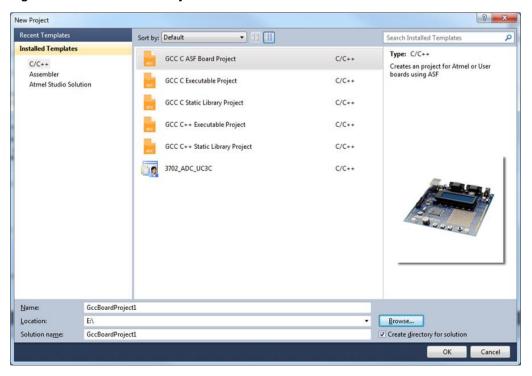

To create an ASF board project for SAM D21 Xplained pro board, go to File menu  $\rightarrow$  New  $\rightarrow$  Project and select "GCC C ASF Board project" in the new project wizard.

Figure 4-4. New project in Atmel Studio

Figure 4-5. ASF Board Project

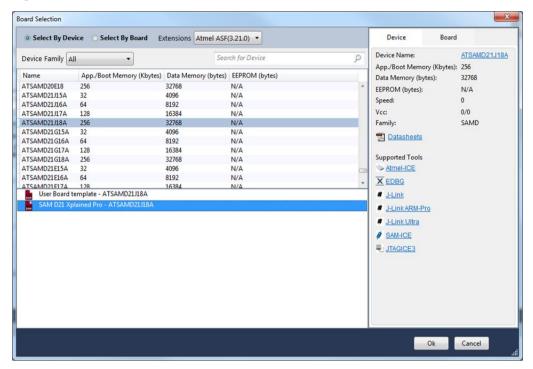

In the next window, select the device family as "SAM D", scroll down, and select the device "ATSAMD21J18A" and Board as "SAM D21 Xplained PRO - ATSAMD21J18A", and click on "OK" to create the new project.

Figure 4-6. Device and Board Selection

The new project by default has a minimal application that will turn ON or OFF the LED on SAM D21 Xplained Pro based on the state of the SW0 push button. Pressing the SW0 button will turn the LED ON and releasing the button will turn the LED OFF. To verify that the SAM D21 Xplained Pro is connected correctly this application can be run and checked whether it shows the expected output.

# 5 Application Demonstration

This section will demonstrate the various features of the SERCOM I<sup>2</sup>C module of SAM D21 with different example codes. Following are the examples demonstrated in this application note.

- Basic Configuration

- High speed configuration

- Address mode configuration

Note: This section assumes that the user has previous knowledge on programming/debugging a SAM D21 device using Atmel Studio IDE.

For easier understanding, the examples will use register level coding for SERCOM module configuration. The clock configuration will, however, use ASF functions.

**A** WARNING

Since this application note is demonstrated using the ASF template project, build errors are expected when compiling the project with SERCOM drivers included from ASF. This because ASF SERCOM drivers will predefine all the SERCOM handlers which will make redefinition error as SERCOM handlers are defined again as per the application note.

## 5.1 Basic Configuration

In Basic configuration application, the master will transmit a data buffer of few bytes to the slave and the slave will re-transmit the same data buffer to the master.

Basic configuration application performs the following actions:

- Master write (Slave read)

- Slave write (Master read

SERCOM I<sup>2</sup>C lines (PA08 - SDA, PA09 - SCL) of the two SAM D21 Xplained Pro boards should be connected through EXT2 connector using a pair of wires as shown in Figure 5-1.

Note that the same I<sup>2</sup>C lines (PA08 and PA09) are available on all three EXT headers in SAM D21 Xplained Pro board so any of the three headers can be used for this connection.

Figure 5-1. Block Diagram

Master

The SAM D21 Xplained Pro board has on-board pull-up resistors on  $I^2C$  lines with 4.7k $\Omega$  resistance value and with reference designators R305 and R306.

Note: To get better  $I^2C$  signal timings the  $4.7k\Omega$  pull-up resistors on both the master and slave SAM D21 Xplained Pro boards have been replaced by  $2k\Omega$  resistors and all the modes have been tested with this pull-up configuration.

In Basic configuration section, both master and slave communicates at the fast mode plus – 1MHz speed.

Following are the common function calls used in master and slave applications in basic configuration example:

- system init()

- i2c\_clock\_init()

- i2c pin init()

Detailed explanation on each function will be provided in the upcoming sections. At the end of each section a complete code will be provided for reference.

The Complete Project solution for all the applications can be found in the zipped folder attachment that comes with this application note.

#### 5.1.1 Main Clock

In SAM D21 devices, the output from GCLK Generator 0 will be used as the main clock. The Generic Clock Generator 0, also called GCLK\_MAIN, is the clock feeding the Power Manager used to generate synchronous clocks. The GCLK Generator 0 can have one of the SYSCTRL oscillators as its source clock.

By default, after reset, 1MHz clock from OSC8M (prescaler set to 8) is used as the clock source for GCLK Generator 0 and hence the main clock. However, as per the default ASF clock configuration, 8MHz clock from OSC8M (prescaler set to 1) is used as the clock source for GCLK Generator 0.

#### 5.1.2 Master and Slave Clock

The master and slave application uses OSC8M as the clock source for Generator 0. The following lines in the conf\_clocks.h will initialize the source clock for generator 0.

The flash wait state can be set to 0 as the CPU will not run in maximum speed in this example.

#### 5.1.3 Clock Flow for Master and Slave

Figure 5-2. Clock Flow Diagram for Master and Slave

### 5.1.4 System Initialization

system\_init() is an ASF function used to configure the clock sources and GCLK generators as per the settings in the conf\_clocks.h file. The main clock will be configured as stated in the Section 5.1.2. It also initializes the board hardware of SAM D21 Xplained Pro and the event system.

#### 5.1.5 I<sup>2</sup>C Clock Initialization

i2c\_clock\_init() function configures the peripheral bus clock (APB clock) and generic clock for the SERCOM I2C module. SERCOM2 is used in both the master and slave boards.

```

void i2c_clock_init()

{

struct system_gclk_chan_config gclk_chan_conf;

uint32_t gclk_index = SERCOM2_GCLK_ID_CORE;

/* Turn on module in PM */

system_apb_clock_set_mask(SYSTEM_CLOCK_APB_APBC, PM_APBCMASK_SERCOM2);

/* Turn on Generic clock for I2C */

system_gclk_chan_get_config_defaults(&gclk_chan_conf);

/* Default is generator 0. Other wise need to configure like below */

/* gclk_chan_conf.source_generator = GCLK_GENERATOR_1; */

system_gclk_chan_set_config(gclk_index, &gclk_chan_conf);

system_gclk_chan_enable(gclk_index);

}

```

- A structure variable gclk\_chan\_conf is declared. This structure is used to configure the generic clock for the SERCOM used.

- SERCOM2 core clock "SERCOM2\_GCLK\_ID\_CORE" and bus clock "SYSTEM\_CLOCK\_APB\_APBC" are configured

- Generic clock "SERCOM2 GCLK ID CORE" uses GCLK Generator 0 as source generator (generic clock source can be changed to any other GCLK Generators as per user needs). So the SERCOM2 module is clocked at 48MHz from DFLL48M.

- system\_gclk\_chan\_set\_config will set the generic clock channel configuration

- system gclk chan enable will enable the generic clock "SERCOM2 GCLK ID CORE"

#### 5.1.6 I<sup>2</sup>C Pin Initialization

i2c pin init() function will initialize pins PA08 and PA09 to the SERCOM-Alternate peripheral function (D).

```

void i2c pin init()

/* PA08 and PA09 set into peripheral function D*/

pin_set_peripheral_function(PINMUX_PA08D_SERCOM2_PAD0);

pin set peripheral function(PINMUX PA09D SERCOM2 PAD1);

}

```

i2c pin init function calls the pin set peripheral function to assign I/O lines PA08 and PA09 to the SERCOM peripheral function.

```

static void pin set peripheral function(uint32 t pinmux)

uint8 t port = (uint8 t)((pinmux \Rightarrow 16)/32);

PORT->Group[port].PMUX[((pinmux >> 16) - (port*32))/2].reg &= ~(0xF << (4 * ((pinmux >>

16) & 0x01u)));

0x0000FFFF) << (4 * ((pinmux >> 16) & 0x01u)));

PORT->Group[port].PINCFG[((pinmux >> 16) - (port*32))].bit.PMUXEN = 1;

}

```

The function pin\_set\_peripheral\_function() will switch the GPIO functionality of an I/O pin to peripheral functionality and assigns the given peripheral function to the pin. The function takes a 32-bit pinmux value as its argument. The 32-bit pinmux value contains the pin number in its 16-bit MSB part and the peripheral function number in its 16-bit LSB part. So each 32-bit pinmux value is unique per pin per peripheral function. The function first identifies the PORT group from the pin number (MSB 16-bit) and updates the PMUX register with the peripheral number (LSB 16-bit).

SERCOM2 PAD0 will be SDA line and SERCOM2 PAD1 will be SCL line as per the SERCOM I2C pad assignment shown in Table 5-1.

**Table 5-1. Signal Description**

| Signal name | Туре        | Description      |

|-------------|-------------|------------------|

| PAD[0]      | Digital I/O | SDA              |

| PAD[1]      | Digital I/O | SDL              |

| PAD[2]      | Digital I/O | SDA_OUT (4-wire) |

| PAD[3]      | Digital I/O | SDC_OUT (4-wire) |

System initialization, I<sup>2</sup>C clock initialization, and I<sup>2</sup>C pin initialization are common for both master and slave. For Note: the slave part the same will be applicable.

#### 5.1.7 I<sup>2</sup>C Master Initialization

The i2c\_master\_init function will initialize the I<sup>2</sup>C master function by configuring the control registers, baud registers, and setting the respective interrupt enable bits.

```

void i2c master init()

/* By setting the SPEED bit field as 0x01, I2C Master runs at Fast mode + - 1MHz,

By setting the SDAHOLD bit field as 0x02, SDA hold time is configured for 300-600ns,

By setting the RUNSTDBY bit as 0x01, Generic clock is enabled in all sleep modes,

any interrupt can wake up the device,

SERCOM2 is configured as an I2C Master by writing the MODE bitfield as 0x5 */

SERCOM2->I2CM.CTRLA.reg = SERCOM_I2CM_CTRLA SPEED (FAST MODE PLUS)

SERCOM I2CM CTRLA SDAHOLD(0x2)

SERCOM_I2CM_CTRLA_RUNSTDBY

SERCOM_I2CM_CTRLA_MODE_I2C_MASTER;

/* smart mode enabled by setting the bit SMEN as 1 */

SERCOM2->I2CM.CTRLB.reg = SERCOM I2CM CTRLB SMEN;

/* synchronization busy */

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* BAUDLOW is non-zero, and baud register is loaded */

SERCOM2->I2CM_BAUD.reg = SERCOM_I2CM_BAUD_BAUD(11) | SERCOM_I2CM_BAUD_BAUDLOW(22);

/* synchronization busy */

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* SERCOM2 peripheral enabled by setting the ENABLE bit as 1*/

SERCOM2->I2CM.CTRLA.reg |= SERCOM I2CM CTRLA ENABLE;

/* SERCOM Enable synchronization busy */

while((SERCOM2->I2CM.SYNCBUSY.reg & SERCOM_I2CM_SYNCBUSY_ENABLE));

/* bus state is forced into idle state */

SERCOM2->I2CM.STATUS.bit.BUSSTATE = 0x1;

/* synchronization busy */

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* Both master on bus and slave on bus interrupt is enabled */

SERCOM2->I2CM.INTENSET.reg = SERCOM_I2CM_INTENSET_MB | SERCOM_I2CM_INTENSET_SB;

/* SERCOM2 handler enabled */

system interrupt enable(SERCOM2 IRQn);

}

```

- The CTRLA register is used to configure the I<sup>2</sup>C speed, SDA hold time, and I<sup>2</sup>C mode. In the above function I<sup>2</sup>C speed is configured as Fast-mode plus, SDA hold time is set for 300 600ns. I<sup>2</sup>C is configured as master and the I<sup>2</sup>C module is made to run even in standby sleep mode.

- CTRLB register is used to write the commands and to enable Smart Mode. In the above function SMEN

Smart Mode Enable bit is set.

- For BAUD.BAUDLOW non-zero, the following formula is used to determine the SCL frequency, F<sub>SCL</sub> = f<sub>GCLK</sub>/(10 + BAUD +BAUDLOW + f<sub>GCLK</sub> T<sub>RISE</sub>)

```

F<sub>SCL</sub> = I<sup>2</sup>C clock frequency

f<sub>GCLK</sub> = SERCOM generic clock frequency

BAUD = BAUD register value

BAUDLOW = BAUD LOW register value

T<sub>RISE</sub> = Rise time for I<sup>2</sup>C in the defined mode

```

Rise time for the respective speed modes can be found in section Electrical Characteristics  $\rightarrow$  Timing Characteristics  $\rightarrow$  SERCOM I<sup>2</sup>C Mode Timing in the SAM D21 device datasheet.

In this configuration, the I<sup>2</sup>C runs at the speed of 1MHz and the worst case rise time for fast mode plus is 100ns.

From the equation:

```

BAUD + BAUDLOW = fgclk/Fscl - (fgclk Trise) - 10

= 48M/1M - (48M x 100ns) - 10

= 33.2

```

Note: For Fast-mode plus the nominal high to low SCL ratio is 1 to 2 and BAUD should be set accordingly. At a minimum, BAUD.BAUD and/or BAUD.BAUDLOW must be non-zero.

So the BAUD value is set to 11 and BAUDLOW value is set to 22.

Apart from high-speed mode, the same equation given above can be used for BAUD-BAUDLOW calculation for other speed modes like standard mode and fast mode with appropriate rise time taken from the SERCOM I<sup>2</sup>C Mode Timing section in the datasheet as mentioned earlier.

- CTRLA, CTRLB, and BAUD registers can be written only when the I<sup>2</sup>C is disabled because these registers are enable protected. So once configuring these registers the I<sup>2</sup>C is enabled.

- As CLK\_SERCOMx\_APB and GCLK\_SERCOMx\_CORE are not synchronized and some registers

needs synchronization when they are accessed. CTRLA register is Write-Synchronized so the

application should wait until the synchronization busy flag (SYSOP bit in SYNCBUSY register) is cleared

after performing a write to this register.

- The I<sup>2</sup>C bus-state is unknown when the master is disabled. During this time writing 0x1 to BUSSTATE forces the bus state into the idle state.

- Each peripheral has a dedicated interrupt line, which is connected to the Nested Vector Interrupt

Controller in the Cortex®-M0+ core. In the above function SERCOM2 interrupt request line (IRQ 11) is

enabled.

- The INTENSET register is used to enable the required SERCOM interrupts. In the above function SB –

Slave on bus and MB Master on bus interrupts are enabled

### 5.1.8 I<sup>2</sup>C Master Transaction

The i2c\_master\_transact function is used to perform a transaction with the connected slave device.

```

void i2c_master_transact(void)

{

i = 0;

/* Acknowledge section is set as ACK signal by

writing 0 in ACKACT bit */

SERCOM2->I2CM.CTRLB.reg &= ~SERCOM_I2CM_CTRLB_ACKACT;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* slave address with Write(0) */

SERCOM2->I2CM.ADDR.reg = (SLAVE ADDR << 1) | 0;

while(!tx done);

i = 0;

/* Acknowledge section is set as ACK signal by

writing 0 in ACKACT bit */

SERCOM2->I2CM.CTRLB.reg &= ~SERCOM I2CM CTRLB ACKACT;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* slave address with read (1) */

```

```

SERCOM2->I2CM.ADDR.reg = (SLAVE_ADDR << 1) | 1;

while(!rx_done);

/*interrupts are cleared */

SERCOM2->I2CM.INTENCLR.reg = SERCOM_I2CM_INTENCLR_MB | SERCOM_I2CM_INTENCLR_SB;

}

```

• In master application a global variable for iteration count and two Boolean variables to indicate transmission done status and reception done status are used

```

uint8_t i

volatile bool tx_done = false, rx_done = false

```

- In CTRLB register, ACKACT field is used to define the I<sup>2</sup>C master's acknowledge behavior after a data byte is received from the I<sup>2</sup>C slave. The acknowledge action will be executed when a command is written to CTRLB.CMD bits or after a transfer with Smart Mode is enabled.

- In the above function, ACKACT is set to 0, so ACK will be sent by master after a data byte is received

- In the application we are using 7-bit addressing mode. The slave address is written into the Address register, which initiates a transfer by sending a start condition followed by address on the I<sup>2</sup>C line.

- The slave address is shifted by 1 bit and LSB of ADDR register is written as 0 because application is going to write/transmit the data to slave

- Once placing the address in the ADDR register, the address will be kept in Data register and transferred to Slave

- The Boolean flag variable tx\_done is initialized as false, so it remains in the while loop until SERCOM2 handler sets it to true indicating the completion of transfer

```

while(!tx_done);

```

Once transmitting the address of slave and then after receiving the ACK/NACK, the Master on Bus (MB) interrupt will be set and SERCOM2\_Handler will be serviced

- Buffer size has been set by macro BUF SIZE

- In SERCOM2 handler it will check for Master on bus interrupt set condition and enters that loop

- In that loop, variable i is checked with the BUF\_SIZE. If i is not equal to BUF\_SIZE the transmit buffer data will be placed in the data register.

- Each time when the placed data is successfully transferred on the bus, the MB interrupt will be triggered

- Once i value equals the BUF\_SIZE, STOP condition will be sent and Boolean variable tx\_done is set to true condition

- Now the code execution will reach the i2c\_master\_transact function. tx\_done is true so it will come out

of while loop.

- Now the application is going to read the data from the slave

- Again the variable i is set to 0

- In the address register, again address value is loaded by shifting it left by one bit and LSB of ADDR register is set as 1 for read operation

- Once placing the address (Address + R) in the ADDR register, the address will be kept in data register

and transferred to slave. Then slave will acknowledge the address and since it is master read operation

so the slave device will send the data to master and now slave on bus interrupt condition will be set in

master.

```

if (SERCOM2->I2CM.INTFLAG.bit.SB)

{

if (i == (BUF SIZE-1))

{ /* NACK should be sent before reading the last byte */

SERCOM2->I2CM.CTRLB.reg |= SERCOM I2CM CTRLB ACKACT;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

SERCOM2->I2CM.CTRLB.bit.CMD = 0x3;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

rx buf[i++] = SERCOM2->I2CM.DATA.reg;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

rx done = true;

}

else

{

SERCOM2->I2CM.CTRLB.reg &= ~SERCOM I2CM CTRLB ACKACT;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

rx buf[i++] = SERCOM2->I2CM.DATA.reg;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* sending ACK after reading each byte */

SERCOM2->I2CM.CTRLB.bit.CMD = 0x2;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

}

}

```

- The received data byte will be read into the read buffer rx\_buf and acknowledgement ACK will be sent

- Last data byte should be read only after giving the STOP condition and NACK should be sent by the Master

- In CTRLB register the Acknowledge action is set as NACK for last byte read and STOP condition is sent

- After sending the STOP condition the last byte is read from DATA register into read buffer

- Now the code execution will reach the i2c\_master\_transact function and clears the interrupt enable bits

Note: CTRLA, CTRLB, ADDR, DATA registers are write synchronized so SYSOP bit in the SYNCBUSY register should be checked after writing these registers.

The final application "Basic Configuration" in main.c file will be as below for MASTER:

```

3

#define BUF_SIZE

/* Function Prototype */

void i2c clock init(void);

void i2c pin init(void);

void i2c_master_init(void);

void i2c master transact(void);

uint32 t calculate_baud(uint32_t, uint32_t);

uint8 t tx buf[BUF SIZE] = {1, 2, 3};

uint8_t rx_buf[BUF_SIZE];

uint8_t i;

volatile bool tx_done = false, rx_done = false;

/* I2C handler */

void SERCOM2 Handler(void)

/* Master on bus interrupt checking */

if (SERCOM2->I2CM.INTFLAG.bit.MB)

{

if (i == BUF SIZE)

/* After transferring the last byte stop condition will be sent */

SERCOM2->I2CM.CTRLB.bit.CMD = 0x3;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

tx done = true;

i = 0:

}

else

{ /* placing the data from transmitting buffer to DATA register*/

SERCOM2->I2CM.DATA.reg = tx buf[i++];

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

}

}

/* Slave on bus interrupt checking */

if (SERCOM2->I2CM.INTFLAG.bit.SB)

{

if (i == (BUF_SIZE-1))

{ /* NACK should be sent before reading the last byte */

SERCOM2->I2CM.CTRLB.reg |= SERCOM_I2CM_CTRLB_ACKACT;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

SERCOM2->I2CM.CTRLB.bit.CMD = 0x3;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

rx buf[i++] = SERCOM2->I2CM.DATA.reg;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

rx done = true;

}

else

{

SERCOM2->I2CM.CTRLB.reg &= ~SERCOM_I2CM_CTRLB_ACKACT;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

rx buf[i++] = SERCOM2->I2CM.DATA.reg;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* sending ACK after reading each byte */

SERCOM2->I2CM.CTRLB.bit.CMD = 0x2;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

}

}

}

```

```

/*Assigning pin to the alternate peripheral function*/

static inline void pin set peripheral function(uint32 t pinmux)

uint8 t port = (uint8 t)((pinmux \Rightarrow 16)/32);

PORT->Group[port].PINCFG[((pinmux >> 16) - (port*32))].bit.PMUXEN = 1;

PORT->Group[port].PMUX[((pinmux >> 16) - (port*32))/2].reg &= ~(0xF << (4 * ((pinmux >>

16) & 0x01u)));

PORT->Group[port].PMUX[((pinmux >> 16) - (port*32))/2].reg |= (uint8 t)((pinmux &

0x0000FFFF) << (4 * ((pinmux >> 16) & 0x01u)));

}

/* calculating the BAUD value using Fgclk,Fscl,Trise

FSCL = FGCLK / (10 + BAUD + BAUDLOW + FGCLKTRISE )*/

uint32 t calculate baud(uint32 t fgclk, uint32 t fscl)

{

float f temp, f baud;

f_temp = ((float)fgclk/(float)fscl) - (((float)fgclk/(float)1000000)*0.3);

f_baud = (f_temp/2)-5;

return ((uint32_t)f_baud);

/* SERCOM clock and peripheral bus clock initialization */

void i2c clock init()

{

struct system gclk chan config gclk chan conf;

uint32 t gclk index = SERCOM2 GCLK ID CORE;

/* Turn on module in PM */

system apb clock set mask(SYSTEM CLOCK APB APBC, PM APBCMASK SERCOM2);

/* Turn on Generic clock for I2C */

system gclk chan get config defaults(&gclk chan conf);

/* Default is generator 0. Other wise need to configure like below */

/* gclk_chan_conf.source_generator = GCLK_GENERATOR_1; */

system gclk chan set config(gclk index, &gclk chan conf);

system gclk chan enable(gclk index);

}

/* I2C pin initialization */

void i2c_pin_init()

{

/* PA08 and PA09 set into peripheral function D*/

pin set peripheral function(PINMUX PA08D SERCOM2 PAD0); // SDA

pin set peripheral function(PINMUX PA09D SERCOM2 PAD1); // SCL

}

/* I2C master initialization */

void i2c_master_init()

/* By setting the SPEED bit field as 0x01, I2C Master runs at Fast mode + - 1MHz,

By setting the SDAHOLD bit field as 0x02, SDA hold time is configured for 300-600ns,

By setting the RUNSTDBY bit as 0x01, Generic clock is enabled in all sleep modes, any

interrupt can wake up the device,

SERCOM2 is configured as an I2C Master by writing the MODE bitfield as 0x5 */

SERCOM2->I2CM.CTRLA.reg = SERCOM I2CM CTRLA SPEED (FAST MODE PLUS)

SERCOM I2CM CTRLA SDAHOLD(0x2)

SERCOM I2CM CTRLA RUNSTDBY

SERCOM_I2CM_CTRLA_MODE_I2C_MASTER;

/* smart mode enabled by setting the bit SMEN as 1 */

SERCOM2->I2CM.CTRLB.reg = SERCOM I2CM CTRLB SMEN;

/* synchronization busy */

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

```

```

/* BAUDLOW is non-zero, and baud register is loaded */

SERCOM2->I2CM.BAUD.reg = SERCOM I2CM BAUD BAUD(11) | SERCOM I2CM BAUD BAUDLOW(22);

/* synchronization busy */

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* SERCOM2 peripheral enabled by setting the ENABLE bit as 1*/

SERCOM2->I2CM.CTRLA.reg |= SERCOM_I2CM_CTRLA_ENABLE;

/* SERCOM Enable synchronization busy */

while((SERCOM2->I2CM.SYNCBUSY.reg & SERCOM I2CM SYNCBUSY ENABLE));

/* bus state is forced into idle state */

SERCOM2->I2CM.STATUS.bit.BUSSTATE = 0x1;

/* synchronization busy */

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* Both master on bus and slave on bus interrupt is enabled */

SERCOM2->I2CM.INTENSET.reg = SERCOM_I2CM_INTENSET_MB | SERCOM_I2CM_INTENSET_SB;

/* SERCOM2 handler enabled */

system interrupt enable(SERCOM2 IRQn);

}

/* I2C master Transaction */

void i2c_master_transact(void)

{

i = 0;

/* Acknowledge section is set as ACK signal by

writing 0 in ACKACT bit */

SERCOM2->I2CM.CTRLB.reg &= ~SERCOM_I2CM_CTRLB_ACKACT;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* slave address with Write(0) */

SERCOM2->I2CM.ADDR.reg = (SLAVE ADDR << 1) | 0;

while(!tx done);

i = 0;

/* Acknowledge section is set as ACK signal by

writing 0 in ACKACT bit */

SERCOM2->I2CM.CTRLB.reg &= ~SERCOM_I2CM_CTRLB_ACKACT;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* slave address with read (1) */

SERCOM2->I2CM.ADDR.reg = (SLAVE ADDR << 1) | 1;

while(!rx done);

/*interrupts are cleared */

SERCOM2->I2CM.INTENCLR.reg = SERCOM_I2CM_INTENCLR_MB | SERCOM_I2CM_INTENCLR_SB;

}

int main (void)

system_init();

i2c clock_init();

i2c pin init();

i2c master init();

i2c master transact();

while(1);

}

```

#### 5.1.9 I<sup>2</sup>C Slave Initialization

The i2c\_slave\_init function will initialize the I<sup>2</sup>C slave function by configuring the control registers, address register, and setting the respective interrupt enable bits.

```

void i2c slave init()

/* By setting the SPEED bit field as 0x01, I2C communication runs at 1MHz,

By setting the SDAHOLD bit field as 0x02, SDA hold time is configured for 300-600ns,

By setting the RUNSTDBY bit as 0x01. Generic clock is enabled in all sleep modes.

any interrupt can wake up the device.

SERCOM2 is configured as an I2C Slave by writing the MODE bitfield as 0x04 */

SERCOM2->I2CS.CTRLA.reg = SERCOM I2CS CTRLA SPEED (FAST MODE PLUS)

SERCOM I2CS CTRLA SDAHOLD(0x2)

SERCOM I2CM CTRLA RUNSTDBY

SERCOM_I2CS_CTRLA_MODE_I2C_SLAVE;

/* smart mode enabled by setting the bit SMEN as 1 */

SERCOM2->I2CS.CTRLB.reg = SERCOM I2CS CTRLB SMEN;

/* writing the slave address into ADDR register */

SERCOM2->I2CS.ADDR.reg = SLAVE ADDR << 1;</pre>

/* Address match interrupt, Data ready interrupt, stop received

interrupts are enabled */

SERCOM2->12CS.INTENSET.reg = SERCOM 12CS INTENSET PREC | SERCOM 12CS INTENSET AMATCH |

SERCOM I2CS INTENSET DRDY;

/* SERCOM2 peripheral enabled by setting the ENABLE bit as 1*/

SERCOM2->I2CS.CTRLA.reg |= SERCOM I2CS CTRLA ENABLE;

/* SERCOM enable synchronization busy */

while((SERCOM2->I2CS.SYNCBUSY.reg & SERCOM I2CS SYNCBUSY ENABLE));

/* SERCOM2 handler enabled */

system interrupt enable(SERCOM2 IRQn);

}

```

- I<sup>2</sup>C slave CTRLA register is used to configure the I<sup>2</sup>C speed, SDA Hold time, and the I<sup>2</sup>C mode of the device. In the above function, I<sup>2</sup>C runs at fast mode plus (1MHz) and is configured to have a SDA hold time of 300 600ns, and device runs as I<sup>2</sup>C slave mode. SERCOM module is made to run even in standby sleep mode.

- CTRLB register is used to configure the acknowledge action, user to write commands during transaction and to enable smart mode. In the above function Smart Mode is enabled.

- ADDR register is used to hold the address of slave

- The INTENSET register is used to enable the required interrupts. In the above function, address match interrupt, stop received interrupt and data ready interrupts are enabled.

- CTRLA, CTRLB, and BAUD registers can be written only when the I<sup>2</sup>C is disabled because these registers are enable protected. So once configuring these registers, the I<sup>2</sup>C is enabled.

- Due to the asynchronicity between CLK\_SERCOMx\_APB and GCLK\_SERCOMx\_CORE, some

registers must be synchronized when accessed. ENABLE bit in CTRLA register is Write-Synchronized so

the application should wait until the synchronization busy flag (ENABLE bit in SYNCBUSY register) is

cleared after performing a write to this register.

- Each peripheral has a dedicated interrupt line, which is connected to the Nested Vector Interrupt

Controller in the Cortex-M0+ core. In the above function SERCOM2 interrupt request line (IRQ 11) is

enabled.

#### 5.1.10 I<sup>2</sup>C Slave Transaction

SERCOM2 Handler will serve the I<sup>2</sup>C slave transaction function.

```

void SERCOM2_Handler(void)

/* Check for Address match interrupt */

if(SERCOM2->I2CS.INTFLAG.bit.AMATCH)

{

/* clearing the Address match interrupt */

SERCOM2->I2CS.INTFLAG.bit.AMATCH = 1;

}

/* Data Ready interrupt check */

if(SERCOM2->I2CS.INTFLAG.bit.DRDY)

/* Checking for direction,

DIR - 0 for slave read,

DIR - 1 for slave write */

if (SERCOM2->I2CS.STATUS.bit.DIR)

{

/* Slave write */

if (i == (BUF SIZE-1))

SERCOM2->I2CS.DATA.reg = rx_buff[i++];

/* wait for stop condition */

SERCOM2->I2CS.CTRLB.bit.CMD = 0x2;

i = 0;

}

else

{

SERCOM2->I2CS.DATA.reg = rx_buff[i++];

/* Execute a byte read operation followed by ACK/NACK reception by master*/

SERCOM2->I2CS.CTRLB.bit.CMD = 0x3;

}

}

else

{

/* Slave read */

if (i == (BUF SIZE-1))

SERCOM2->I2CS.CTRLB.bit.ACKACT = 0;

(S/Sr) condition */

/* Execute acknowledge action succeeded by waiting for any start

SERCOM2->I2CS.CTRLB.bit.CMD = 0x2;

}

else

{

rx_buff[i++] = SERCOM2->I2CS.DATA.reg;

SERCOM2->I2CS.CTRLB.bit.ACKACT = 0;

/* Execute acknowledge action succeeded by reception of next byte to master*/

SERCOM2->I2CS.CTRLB.bit.CMD = 0x3;

}

}

if (SERCOM2->I2CS.INTFLAG.bit.PREC)

SERCOM2->I2CS.INTFLAG.bit.PREC = 1;

```

- In the SERCOM2 handler, three interrupt conditions are checked:

- Address match interrupt

- Data Ready interrupt

- Stop Interrupt

- Address match interrupt flag is set when the received address matches the configured slave address.

Clearing the flag by writing one to it will automatically send the configured acknowledge action when smart mode is enabled.

- Data Ready interrupt is set when I<sup>2</sup>C slave byte needs to be transmitted or received

- In I<sup>2</sup>C status register, DIR bit will be set for master read operation and cleared for master write operation

- When master transmits the buffer data, code will enter into the below loop of slave SERCOM2 handler

- Once receiving the data byte in the DATA register, it will be copied into receive buffer rx\_buff

- Acknowledgement action (ACK) for each byte should be sent by the slave. After receiving, a byte slave sends the ACK by writing command value 0x3 to CMD bits in CTRLB register. Command value 0x3 is used to send acknowledge action followed by next byte reception.

- For the last data byte, command value 0x2 is written to CMD bits in CTRLB register, which waits for a STOP/Repeated START condition. The last data received should only be read after receiving a STOP condition.

- Inside STOP interrupt condition, the application will clear the STOP interrupt flag and read the last received data into the receive buffer in master write mode

Below code is for the master read operation:

```

if (SERCOM2->I2CS.STATUS.bit.DIR)

{

/* Slave write */

if (i == (BUF SIZE-1))

{

SERCOM2->I2CS.DATA.reg = rx buff[i++];

/* wait for stop condition */

SERCOM2->I2CS.CTRLB.bit.CMD = 0x2;

i = 0;

}

else

{

SERCOM2->I2CS.DATA.reg = rx buff[i++];

/* Execute a byte read operation followed by ACK/NACK reception by master */

SERCOM2->I2CS.CTRLB.bit.CMD = 0x3;

}

}

```

- Received data from the master will be in the receive buffer rx buff

- In master read operation, receive buffer data i.e.data byte which received from the master is transmitted by slave to master by placing in the DATA register

- Once writing the data byte, the command is set to 0x3 for executing a byte read operation by master followed by ACK/NACK reception by slave

- For the last byte transfer, after writing the last data byte stop command will be placed in command register

The final application "Basic Configuration" in main.c file will be as below for **SLAVE**:

```

#include <asf.h>

#define STANDARD MODE FAST MODE 0x0

#define FAST MODE PLUS

0X01

#define HIGHSPEED MODE

0X02

#define SLAVE ADDR

0x12

#define BUF SIZE

/* Function Prototype */

void i2c_clock_init(void);

void i2c_pin_init(void);

void i2c_slave_init(void);

uint8 t i = 0;

uint8_t rx_buff[BUF_SIZE];

/* SERCOM2 I2C handler */

void SERCOM2_Handler(void)

/* Check for Address match interrupt */

if(SERCOM2->I2CS.INTFLAG.bit.AMATCH)

```

```

{

/* clearing the Address match interrupt */

SERCOM2->I2CS.INTFLAG.bit.AMATCH = 1;

}

/* Data Ready interrupt check */

if(SERCOM2->I2CS.INTFLAG.bit.DRDY)

/* Checking for direction,

DIR - 0 for slave read,

DIR - 1 for slave write */

if (SERCOM2->I2CS.STATUS.bit.DIR)

{

/* Slave write */

if (i == (BUF SIZE-1))

{

SERCOM2->I2CS.DATA.reg = rx buff[i++];

/* wait for stop condition */

SERCOM2->I2CS.CTRLB.bit.CMD = 0x2;

i = 0;

}

else

{

SERCOM2->I2CS.DATA.reg = rx buff[i++];

/* Execute a byte read operation followed by ACK/NACK reception by master */

SERCOM2->I2CS.CTRLB.bit.CMD = 0x3;

}

}

else

{

/* Slave read */

if (i == (BUF SIZE-1))

{

SERCOM2->I2CS.CTRLB.bit.ACKACT = 0;

/* Execute acknowledge action succeeded by waiting for any start (S/Sr) condition */

SERCOM2->I2CS.CTRLB.bit.CMD = 0x2;

}

else

{

rx_buff[i++] = SERCOM2->I2CS.DATA.reg;

SERCOM2->I2CS.CTRLB.bit.ACKACT = 0;

/* Execute acknowledge action succeeded by reception of next byte to master*/

SERCOM2->I2CS.CTRLB.bit.CMD = 0x3;

}

}

if (SERCOM2->I2CS.INTFLAG.bit.PREC)

SERCOM2->I2CS.INTFLAG.bit.PREC = 1;

if (!SERCOM2->I2CS.STATUS.bit.DIR)

{

rx buff[i++] = SERCOM2->I2CS.DATA.reg;

}

i = 0;

}

}

/*Assigning pin to the alternate peripheral function*/

static inline void pin_set_peripheral_function(uint32_t pinmux)

```

```

{

uint8 t port = (uint8 t)((pinmux \Rightarrow 16)/32);

PORT->Group[port].PINCFG[((pinmux >> 16) - (port*32))].bit.PMUXEN = 1;

PORT->Group[port].PMUX[((pinmux >> 16) - (port*32))/2].reg &= ~(0xF << (4 * ((pinmux >>

16) & 0x01u)));

PORT->Group[port].PMUX[((pinmux >> 16) - (port*32))/2].reg |= (uint8 t)((pinmux &

0x0000FFFF) << (4 * ((pinmux >> 16) & 0x01u)));

/* SERCOM clock and peripheral bus clock initialization */

void i2c clock init()

struct system gclk chan config gclk chan conf;

uint32_t gclk_index = SERCOM2_GCLK_ID_CORE;

/* Turn on module in PM */

system apb clock set mask(SYSTEM CLOCK APB APBC, PM APBCMASK SERCOM2);

/* Turn on Generic clock for I2C */

system gclk chan get config defaults(&gclk chan conf);

/* Default is generator 0. Other wise need to configure like below */

/* gclk_chan_conf.source_generator = GCLK_GENERATOR_1; */

system_gclk_chan_set_config(gclk_index, &gclk_chan_conf);

system gclk chan enable(gclk index);

/* I2C pin initialization */

void i2c pin init()

/* PA08 and PA09 set into peripheral function D*/

pin set peripheral function(PINMUX PA08D SERCOM2 PAD0);

pin set peripheral function(PINMUX PA09D SERCOM2 PAD1);

/* I2C Slave initialization */

void i2c slave init()

{

/* By setting the SPEED bit field as 0x01, I2C communication runs at 1MHz,

By setting the SDAHOLD bit field as 0x02, SDA hold time is configured for 300-600ns,

By setting the RUNSTDBY bit as 0x01, Generic clock is enabled in all sleep modes,

any interrupt can wake up the device,

SERCOM2 is configured as an I2C Slave by writing the MODE bitfield as 0x04 */

SERCOM2->I2CS.CTRLA.reg = SERCOM_I2CS_CTRLA_SPEED (FAST MODE PLUS)

SERCOM I2CS CTRLA SDAHOLD(0x2)

SERCOM I2CM CTRLA RUNSTDBY

SERCOM_I2CS_CTRLA_MODE_I2C_SLAVE;

/* smart mode enabled by setting the bit SMEN as 1 */

SERCOM2->I2CS.CTRLB.reg = SERCOM_I2CS_CTRLB_SMEN;

/* writing the slave address into ADDR register */

SERCOM2->I2CS.ADDR.reg = SLAVE ADDR << 1;</pre>

/* Address match interrupt, Data ready interrupt, stop received

interrupts are enabled */

SERCOM2->12CS.INTENSET.reg = SERCOM 12CS INTENSET PREC | SERCOM 12CS INTENSET AMATCH |

SERCOM I2CS INTENSET DRDY;

/* SERCOM2 peripheral enabled by setting the ENABLE bit as 1*/

SERCOM2->I2CS.CTRLA.reg |= SERCOM I2CS CTRLA ENABLE;

/* SERCOM enable synchronization busy */

while((SERCOM2->I2CS.SYNCBUSY.reg & SERCOM I2CS SYNCBUSY ENABLE));

/* SERCOM2 handler enabled */

system_interrupt_enable(SERCOM2_IRQn);

}

int main (void)

```

```

system_init();

i2c_clock_init();

i2c_pin_init();

i2c_slave_init();

while(1);

}

```

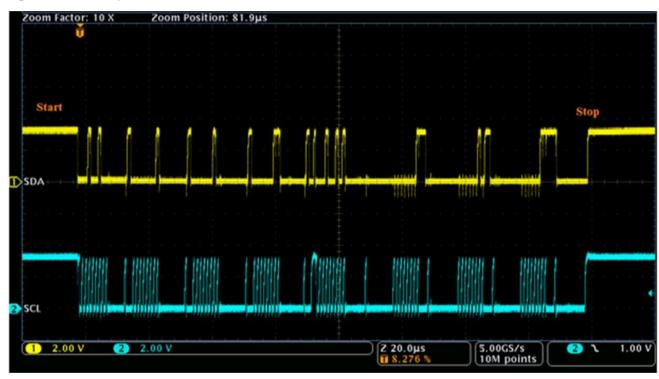

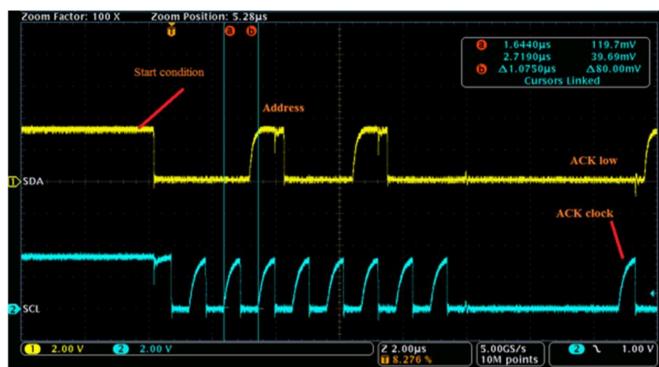

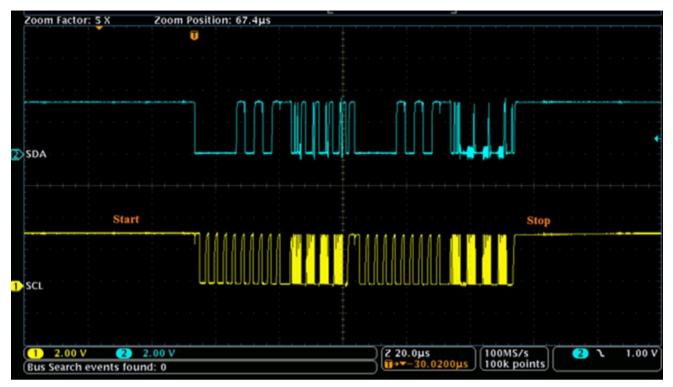

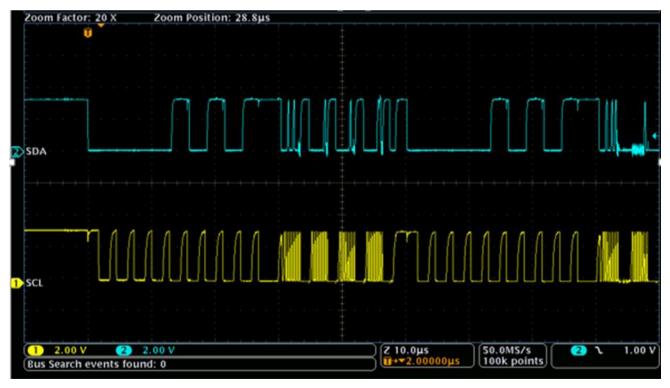

Scope plot for Basic configuration application – Fast mode plus (1MHz).

Figure 5-3. Complete Transaction

Figure 5-4. Start Condition + Address + Write Transmission

The Complete Project solution for all the applications can be found in the zipped folder attachment that comes with this application note.

#### 5.2 **High Speed Configuration**

In high speed configuration, SERCOM I<sup>2</sup>C communicates at an SCL clock frequency of 3.4MHz.

Unlike other speed modes the high speed mode starts the communication in full speed mode (fast mode – 400kHz) frequency in which it sends a unique code and then continues the normal transaction in high speed frequency (3.4MHz).

High speed mode application example does the following actions:

- Master write (Slave read)

- Master read (Slave write)

The example configuration is almost similar to the Basic Configuration example but with some additional steps. This section explains only the additional steps from the Basic Configuration step.

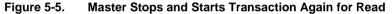

#### 5.2.1 Master and Slave Clock in High-speed Configuration

The default ASF clock configuration in conf clocks.h header file should be changed to make the device as well as the SERCOM module clocked at a maximum speed of 48MHz.

Following changes should be implemented in conf clocks.h file in both master and slave applications for 48MHz operation.

1. Set the flash wait-states to 1.

```

# define CONF CLOCK FLASH WAIT STATES 1

```

2. Configure and enable the XOSC32K oscillator which will be used as the reference clock for DFLL48M module.

```

/* SYSTEM CLOCK SOURCE XOSC32K configuration - External 32KHz crystal/clock oscillator

*/

# define CONF CLOCK XOSC32K ENABLE

true

# define CONF CLOCK XOSC32K EXTERNAL CRYSTAL

SYSTEM CLOCK EXTERNAL CRYSTAL

# define CONF_CLOCK_XOSC32K_STARTUP_TIME

SYSTEM_XOSC32K_STARTUP_65536

# define CONF CLOCK XOSC32K AUTO AMPLITUDE CONTROL false

define CONF CLOCK XOSC32K ENABLE 1KHZ OUPUT

false

define CONF CLOCK XOSC32K ENABLE 32KHZ OUTPUT

true

# define CONF_CLOCK_XOSC32K_ON_DEMAND

true

# define CONF CLOCK XOSC32K RUN IN STANDBY

false

```

Set XOSC32K as the clock source for GCLK Generator 1.

```

/* Configure GCLK generator 1 */

# define CONF CLOCK GCLK 1 ENABLE

true

# define CONF CLOCK GCLK 1 RUN IN STANDBY

false

# define CONF CLOCK GCLK 1 CLOCK SOURCE

SYSTEM CLOCK SOURCE XOSC32K

# define CONF_CLOCK_GCLK_1_PRESCALER

1

# define CONF_CLOCK_GCLK_1_OUTPUT_ENABLE

false

```

4. Configure and enable DFLL48M in closed loop mode using GCLK Generator 1 as reference clock generator and with appropriate multiplication factor.

```

/* SYSTEM CLOCK SOURCE DFLL configuration - Digital Frequency Locked Loop */

# define CONF_CLOCK_DFLL_ENABLE

# define CONF CLOCK DFLL LOOP MODE

SYSTEM CLOCK DFLL LOOP MODE CLOSED

# define CONF CLOCK DFLL ON DEMAND

false

/* DFLL closed loop mode configuration */

# define CONF CLOCK DFLL SOURCE GCLK GENERATOR

GCLK GENERATOR 1

```

5. Set DFLL48M as clock source for GCLK Generator 0 which sources the main clock domain and also used as clock source for SERCOM module.

#### 5.2.2 Clock Flow for Master and Slave

Figure 5-6. Clock Flow Diagram for Master and Slave

### 5.2.3 System Initialization

system\_init() is an ASF function used to configure the clock sources and GCLK generators as per the settings in the conf\_clocks.h file. The main clock will be configured as stated in Section 5.2.1. It also initializes the board hardware of SAM D21 Xplained Pro and the event system.

### 5.2.4 I<sup>2</sup>C clock Initialization

This section is the same as Section 5.1.5.

### 5.2.5 I<sup>2</sup>C Pin Initialization

This section is the same as Section 5.1.6.

Note: System initialization, I<sup>2</sup>C clock initialization, and I<sup>2</sup>C pin initialization are common for both master and slave. For the slave part the same will be applicable.

#### 5.2.6 I<sup>2</sup>C Master Initialization

The i2c\_master\_init function will initialize the I2C master by configuring the control registers, baud registers, and setting the respective interrupt enable bits.

```

void i2c master init()

/* By setting the SPEED bit field as 0x02, I2C Master runs at High speed - 3.4 MHz,

By setting the SDAHOLD bit field as 0x02, SDA hold time is configured for 300-600ns,

By setting the RUNSTDBY bit as 0x01, Generic clock is enabled in all sleep modes,

any interrupt can wake up the device,

SERCOM2 is configured as an I2C Master by writing the MODE bitfield as 0x5,

SCL stretch only after ACK bit is selected by setting the SCLSM bit as 1

SERCOM2->I2CM.CTRLA.reg = SERCOM_I2CM_CTRLA_SPEED (HIGHSPEED_MODE)

SERCOM I2CM CTRLA SDAHOLD(0x2)

SERCOM I2CM CTRLA RUNSTDBY

SERCOM I2CM CTRLA SCLSM

SERCOM I2CM CTRLA MODE I2C MASTER;

/* smart mode enabled */

SERCOM2->I2CM.CTRLB.reg = SERCOM_I2CM_CTRLB_SMEN;

/* synchronization busy */

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* loading the BAUD register */

SERCOM2->I2CM.BAUD.reg = SERCOM_I2CM_BAUD_HSBAUD(4) | SERCOM_I2CM_BAUD_HSBAUDLOW(8) |

SERCOM_I2CM_BAUD_BAUD(48) | SERCOM_I2CM_BAUD_BAUDLOW(48);

/* synchronization busy */

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* SERCOM2 peripheral enabled by setting the ENABLE bit as 1*/

SERCOM2->I2CM.CTRLA.reg |= SERCOM I2CM CTRLA ENABLE;

/* SERCOM Enable synchronization busy */

while((SERCOM2->I2CM.SYNCBUSY.reg & SERCOM I2CM SYNCBUSY ENABLE));

/* bus state is forced into idle state */

SERCOM2->I2CM.STATUS.bit.BUSSTATE = 0x1;

/* SERCOM2 handler enabled */

system interrupt enable(SERCOM2 IRQn);

}

```

- The CTRLA register is used to configure the I<sup>2</sup>C speed, SDA hold time, and I<sup>2</sup>C mode. In the above function I<sup>2</sup>C runs at high speed mode 3.4MHz, SDA hold time is set for 300 600ns. I<sup>2</sup>C is configured as master and the SERCOM module is made to run even in standby sleep mode.

- CTRLB register is used to write commands and to enable Smart Mode. In the above function SMEN Smart Mode Enable is set.

- Equation for calculating the SCL frequency is:

```

\begin{split} F_{SCL} &= F_{GCLK}/2 + HSBAUD + HSBAUDLOW \\ F_{SCL} &= I^2C \text{ clock frequency} \\ F_{GCLK} &= SERCOM \text{ generic clock frequency} \\ HSBAUD &= BAUD \text{ register value of high speed} \\ HSBAUDLOW &= BAUD \text{ LOW register value of high speed} \end{split}

```

From the equation:

```

HSBAUD + HSBAUDLOW = (F_{GCLK} / F_{SCL}) - 2

= (48M/3.4M) - 2

= 12.11 \sim 12

```

```

HSBAUD = 4

HSBAUDLOW = 8

```

Note: For High-speed the nominal high to low SCL ratio is 1 to 2 and HSBAUD should be set accordingly. At a minimum, BAUD.BAUD and/or BAUD.BAUDLOW must be non-zero. Since the high speed transfer starts in full speed mode, the BAUD and BAUDLOW bits should be set to values corresponding to 400kHz apart from configuring the HSBAUD and HSBAUDLOW bits.

The nominal high to low SCL ratio is 1 to 2 is not applicable for 100 and 400 KHz, so the BAUD and BAUDLOW value should be equal.

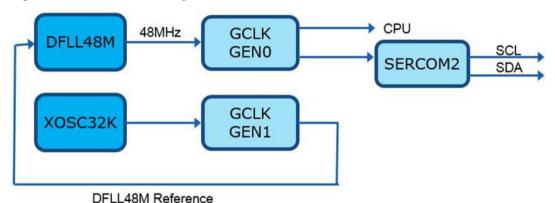

- First, a master code (0000 1nnn where nnn is a unique master code) is transmitted in full speed mode, followed by a NACK reception since no slave should acknowledge this code. Arbitration is performed only during the full speed Master Code phase. The master code is transmitted by writing the master code to the address register (ADDR) with the high-speed bit (ADDR.HS) written to zero.

- In BAUD register HSBAUD, HSBAUDLOW, BAUD, and BAUDLOW values are loaded

- CTRLA, CTRLB, and BAUD registers can be written only when the I<sup>2</sup>C is disabled because these registers are enable protected. So once configuring these registers, the I<sup>2</sup>C is enabled.

- Due to the asynchronicity between CLK\_SERCOMx\_APB and GCLK\_SERCOMx\_CORE, some

registers must be synchronized when accessed. The ENABLE bit in CTRLA register is WriteSynchronized so the application has to wait until the SYSOP bit in SYNCBUSY register is cleared after

writing to the ENABLE bit.

- The I<sup>2</sup>C bus-state is unknown when the master is disabled. During this time writing 0x1 to BUSSTATE forces the bus state into the idle state.

- Each peripheral has a dedicated interrupt line, which is connected to the Nested Vector Interrupt

Controller in the Cortex-M0+ core. In the above function the SERCOM2 interrupt request line (IRQ 11)

is enabled.

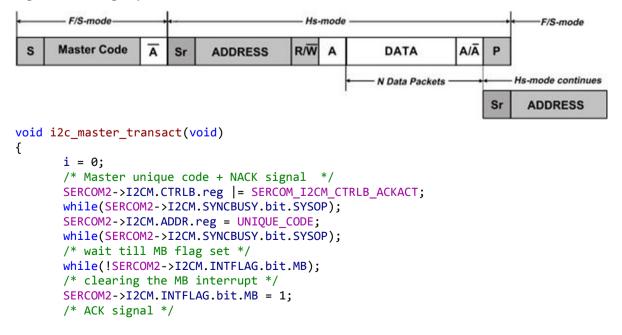

### 5.2.7 I<sup>2</sup>C Master Transaction

The i2c\_master\_transact() function will transfer the master unique code in fast mode followed by a NACK reception since no slave should acknowledge this code.

Figure 5-7. High Speed Transfer

```

SERCOM2->I2CM.CTRLB.reg &= ~SERCOM I2CM CTRLB ACKACT;

/* synchronization busy */

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* slave address+w, High speed transfer enabled */

SERCOM2->I2CM.ADDR.reg = (SLAVE ADDR << 1) | 0 | SERCOM I2CM ADDR HS;

/* synchronization busy */

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* MB and SB interrupts are set */

SERCOM2->I2CM.INTENSET.reg = SERCOM I2CM INTENSET MB | SERCOM I2CM INTENSET SB;

while(!tx done);

/* MB and SB interrupts are cleared */

SERCOM2->I2CM.INTENCLR.reg = SERCOM I2CM INTENCLR MB | SERCOM I2CM INTENCLR SB;

i = 0:

/* Master unique code + NACK signal */

SERCOM2->I2CM.CTRLB.reg |= SERCOM I2CM CTRLB ACKACT;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP)

/* Master unique code + NACK signal */;

SERCOM2->I2CM.ADDR.reg = UNIQUE_CODE;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* wait till MB flag set */

while(!SERCOM2->I2CM.INTFLAG.bit.MB);

/* clearing the MB interrupt */

SERCOM2->I2CM.INTFLAG.bit.MB = 1;

/* ACK signal */

SERCOM2->I2CM.CTRLB.reg &= ~SERCOM I2CM CTRLB ACKACT;

/* synchronization busy */

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* slave address+R, High speed transfer enabled */

SERCOM2->I2CM.ADDR.reg = (SLAVE ADDR << 1) | 1 | SERCOM I2CM ADDR HS;

/* synchronization busy */

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

//while(!SERCOM2->I2CM.INTFLAG.bit.MB);

//SERCOM2->I2CM.INTFLAG.bit.MB = 1;

/* MB and SB interrupts are set */

SERCOM2->I2CM.INTENSET.reg = SERCOM I2CM INTENSET MB | SERCOM I2CM INTENSET SB;

while(!rx done);

/* MB and SB interrupts are cleared */

SERCOM2->I2CM.INTENCLR.reg = SERCOM_I2CM_INTENCLR_MB | SERCOM_I2CM_INTENCLR_SB;

}

```

- CTRLB register is used to configure the commands, acknowledge action, Smart mode enabling. In the above function, NACK action is set for the Master unique code.

- In the Application code we have the Master code of 0x0A. Format of master code is 0000 1nnn where nnn is unique master code.

- Master code is written into the ADDR register with HS bit in the ADDR register set to 0

- MB interrupt flag will be set once the master code is transmitted

- NACK will be received as acknowledge action is set as NACK in the CTRLB register

- After receiving the NACK signal, the acknowledge action should be set as ACK, and address of slave is written in ADDR register

- The Address of slave is left shifted by 1 bit and LSB of ADDR register is set as 0 for master write

- HS bit in ADDR register should be enabled for high speed mode

- Once placing the address in the ADDR register, the address will be kept in Data register and transferred to Slave

- MB and SB interrupts are enabled

The Boolean flag variable is initialized as false, so it while remain in the while loop and reach the SERCOM2 handler

```

while(!tx done);

```

- Once transmitting the Address of slave, the Master on bus interrupt will be set and SERCOM2\_Handler will be serviced

- SERCOM2 Handler is the same as Basic configuration

- Once writing the data bytes, the application stops the I<sup>2</sup>C transaction by using stop command

- Before starting the master read operation, the master unique code should be used as before

- In ADDR register, LSB should be set as 1 for master read operation

Note: CTRLA, CTRLB, ADDR, and DATA registers are write synchronized so SYSOP bit in the SYNCBUSY register should be checked after writing these registers.

The final application "High speed Configuration" in main.c file will be as below for **MASTER**.

```

#include <asf.h>

```

```

#define STANDARD MODE FAST MODE 0x0

#define FAST MODE PLUS

0X01

#define HIGHSPEED MODE

0X02

#define SLAVE ADDR

0x12

#define BUF SIZE

3

#define UNIQUE CODE

0x0A

/* Function Prototype */

void i2c clock init(void);

void i2c pin init(void);

void i2c_master_init(void);

void i2c_master_transact(void);

uint8_t tx_buf[BUF_SIZE] = {1, 2, 3};

uint8_t rx_buf[BUF_SIZE];

uint8_t i;

volatile bool tx done = false, rx done = false, addr transmitted = false;

uint32 t read flag;

/* I2C handler */

void SERCOM2_Handler(void)

{

/* Master on bus interrupt checking */

if (SERCOM2->I2CM.INTFLAG.bit.MB)

{

if (i == BUF SIZE)

/* After transferring the last byte stop condition will be sent */

SERCOM2->I2CM.CTRLB.bit.CMD = 0x3;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

tx done = true;

i = 0;

}

else

/* placing the data from transmitting buffer to DATA register*/

SERCOM2->I2CM.DATA.reg = tx buf[i++];

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

}

```

```

/* Slave on bus interrupt checking */

if (SERCOM2->I2CM.INTFLAG.bit.SB)

if (i == (BUF SIZE-1))

{

/* NACK should be sent before reading the last byte */

SERCOM2->I2CM.CTRLB.reg |= SERCOM I2CM CTRLB ACKACT;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

SERCOM2->I2CM.CTRLB.bit.CMD = 0x3;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

rx buf[i++] = SERCOM2->I2CM.DATA.reg;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

rx_done = true;

}

else

{

SERCOM2->I2CM.CTRLB.reg &= ~SERCOM_I2CM_CTRLB_ACKACT;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

rx_buf[i++] = SERCOM2->I2CM.DATA.reg;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* sending ACK after reading each byte */

SERCOM2->I2CM.CTRLB.bit.CMD = 0x2;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

}

}

}

/*Assigning pin to the alternate peripheral function*/

static inline void pin set peripheral function(uint32 t pinmux)

{

uint8 t port = (uint8 t)((pinmux \Rightarrow 16)/32);

PORT->Group[port].PINCFG[((pinmux >> 16) - (port*32))].bit.PMUXEN = 1;

PORT->Group[port].PMUX[((pinmux >> 16) - (port*32))/2].reg &= ~(0xF << (4 * ((pinmux >>

16) & 0x01u)));

PORT->Group[port].PMUX[((pinmux >> 16) - (port*32))/2].reg |= (uint8_t)((pinmux &

0x0000FFFF) << (4 * ((pinmux >> 16) & 0x01u)));

}

/* SERCOM clock and peripheral bus clock initialization */

void i2c_clock_init()

struct system_gclk_chan_config gclk_chan_conf;

uint32_t gclk_index = SERCOM2_GCLK_ID_CORE;

/* Turn on module in PM */

system apb clock set mask(SYSTEM CLOCK APB APBC, PM APBCMASK SERCOM2);

/* Turn on Generic clock for I2C */

system gclk chan get config defaults(&gclk chan conf);

//Default is generator 0. Other wise need to configure like below

/* gclk_chan_conf.source_generator = GCLK_GENERATOR_1; */

system gclk chan set config(gclk index, &gclk chan conf);

system gclk chan enable(gclk index);

}

/* I2C pin initialization */

void i2c_pin_init()

{

/* PA08 and PA09 set into peripheral function D*/

pin set peripheral function(PINMUX PA08D SERCOM2 PAD0);

```

```

pin set peripheral function(PINMUX PA09D SERCOM2 PAD1);

}

/* I2C master initialization */

void i2c master init()

/* By setting the SPEED bit field as 0x02, I2C Master runs at High speed - 3.4 MHz,

By setting the SDAHOLD bit field as 0x02, SDA hold time is configured for 300-600ns,

By setting the RUNSTDBY bit as 0x01, Generic clock is enabled in all sleep modes,

any interrupt can wake up the device,

SERCOM2 is configured as an I2C Master by writing the MODE bitfield as 0x5,

SCL stretch only after ACK bit is selected by setting the SCLSM bit as 1

SERCOM2->I2CM.CTRLA.reg = SERCOM_I2CM_CTRLA_SPEED (HIGHSPEED_MODE)

SERCOM I2CM CTRLA SDAHOLD(0x2)

SERCOM I2CM CTRLA RUNSTDBY

SERCOM I2CM CTRLA SCLSM

SERCOM_I2CM_CTRLA_MODE_I2C_MASTER;

/* smart mode enabled */

SERCOM2->I2CM.CTRLB.reg = SERCOM_I2CM_CTRLB_SMEN;

/* synchronization busy */

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* loading the BAUD register */

SERCOM2->I2CM.BAUD.reg = SERCOM I2CM BAUD HSBAUD(4) | SERCOM I2CM BAUD HSBAUDLOW(8) |

SERCOM I2CM BAUD BAUD(48) | SERCOM I2CM BAUD BAUDLOW(48);

/* synchronization busy */

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* SERCOM2 peripheral enabled by setting the ENABLE bit as 1*/

SERCOM2->I2CM.CTRLA.reg |= SERCOM_I2CM_CTRLA_ENABLE;

/* SERCOM Enable synchronization busy */

while((SERCOM2->I2CM.SYNCBUSY.reg & SERCOM I2CM SYNCBUSY ENABLE));

/* bus state is forced into idle state */

SERCOM2->I2CM.STATUS.bit.BUSSTATE = 0x1;

/* SERCOM2 handler enabled */

system interrupt enable(SERCOM2 IRQn);

}

/* I2C master Transaction */

void i2c master transact(void)

i = 0;

/* Master unique code + NACK signal */

SERCOM2->I2CM.CTRLB.reg |= SERCOM_I2CM_CTRLB_ACKACT;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

SERCOM2->I2CM.ADDR.reg = UNIQUE_CODE;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* wait till MB flag set */

while(!SERCOM2->I2CM.INTFLAG.bit.MB);

/* clearing the MB interrupt */

SERCOM2->I2CM.INTFLAG.bit.MB = 1;

/* ACK signal */

SERCOM2->I2CM.CTRLB.reg &= ~SERCOM I2CM CTRLB ACKACT;

/* synchronization busy */

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* slave address+w, High speed transfer enabled */

SERCOM2->I2CM.ADDR.reg = (SLAVE_ADDR << 1) | 0 | SERCOM_I2CM_ADDR_HS;</pre>

/* synchronization busy */

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* MB and SB interrupts are set */

```

```

SERCOM2->I2CM.INTENSET.reg = SERCOM I2CM INTENSET MB | SERCOM I2CM INTENSET SB;

while(!tx done);

/* MB and SB interrupts are cleared */

SERCOM2->I2CM.INTENCLR.reg = SERCOM I2CM INTENCLR MB | SERCOM I2CM INTENCLR SB;

i = 0;

/* Master unique code + NACK signal */

SERCOM2->I2CM.CTRLB.reg |= SERCOM I2CM CTRLB ACKACT;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP)

/* Master unique code + NACK signal */;

SERCOM2->I2CM.ADDR.reg = UNIQUE CODE;

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* wait till MB flag set */

while(!SERCOM2->I2CM.INTFLAG.bit.MB);

/* clearing the MB interrupt */

SERCOM2->I2CM.INTFLAG.bit.MB = 1;

/* ACK signal */

SERCOM2->I2CM.CTRLB.reg &= ~SERCOM I2CM CTRLB ACKACT;

/* synchronization busy */

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

/* slave address+R, High speed transfer enabled */

SERCOM2->I2CM.ADDR.reg = (SLAVE ADDR << 1) | 1 | SERCOM I2CM ADDR HS;

/* synchronization busy */

while(SERCOM2->I2CM.SYNCBUSY.bit.SYSOP);

//while(!SERCOM2->I2CM.INTFLAG.bit.MB);

//SERCOM2->I2CM.INTFLAG.bit.MB = 1;

/* MB and SB interrupts are set */

SERCOM2->I2CM.INTENSET.reg = SERCOM_I2CM_INTENSET_MB | SERCOM I2CM INTENSET SB;

while(!rx done);

/* MB and SB interrupts are cleared */

SERCOM2->I2CM.INTENCLR.reg = SERCOM I2CM INTENCLR MB | SERCOM I2CM INTENCLR SB;

}

int main (void)

system init();

i2c_clock_init();

i2c pin init();

i2c_master_init();

i2c_master_transact();

while(1);

}

```

### 5.2.8 I<sup>2</sup>C Slave Initialization

The i2c\_slave\_init function will initialize the I<sup>2</sup>C slave by configuring the control registers, address register, and setting the respective interrupt enable bits.

```

void i2c_slave_init()

{

/* By setting the SPEED bit field as 0x02, I2C Slave runs at High speed - 3.4 MHz,

By setting the RUNSTDBY bit as 0x01,Generic clock is enabled in all sleep modes,

```

```

any interrupt can wake up the device,

SERCOM2 is configured as an I2C Slave by writing the MODE bitfield as 0x04,

SCL stretch only after ACK bit is selected by setting the SCLSM bit as 1,

SERCOM2 is configured as an I2C Slave by writing the MODE bitfield as 0x04

SERCOM2->I2CS.CTRLA.reg = SERCOM I2CS CTRLA SPEED (HIGHSPEED MODE)

SERCOM I2CS CTRLA RUNSTDBY

SERCOM I2CS CTRLA SCLSM

SERCOM I2CS CTRLA MODE I2C SLAVE;

/* smart mode enabled by setting the bit SMEN as 1 */

SERCOM2->I2CS.CTRLB.reg = SERCOM I2CS CTRLB SMEN;

//while(SERCOM2->I2CS.STATUS.bit.SYNCBUSY);

/* writing the slave address into ADDR register */

SERCOM2->I2CS.ADDR.reg = SLAVE_ADDR << 1 ;</pre>

/* Address match interrupt, Data ready interrupt, stop received

interrupts are enabled */

SERCOM2->12CS.INTENSET.reg = SERCOM 12CS INTENSET PREC | SERCOM 12CS INTENSET AMATCH |

SERCOM I2CS INTENSET DRDY;

/* SERCOM2 peripheral enabled */

SERCOM2->I2CS.CTRLA.reg |= SERCOM I2CS CTRLA ENABLE;

/* SERCOM enable synchronization busy */

while((SERCOM2->I2CS.SYNCBUSY.reg & SERCOM I2CS SYNCBUSY ENABLE));

/* SERCOM2 handler enabled */

system interrupt enable(SERCOM2 IRQn);

}

```

- I<sup>2</sup>C slave CTRLA register is used to configure the I<sup>2</sup>C speed, clock stretch, and the I<sup>2</sup>C mode of the device. In the above function, I<sup>2</sup>C runs at high speed, clock stretch only after ACK bit, and device runs as I<sup>2</sup>C slave mode. SERCOM module is made to run even in standby sleep mode.

- CTRLB register is used to configure the acknowledge action, command bits to write commands and enabling smart mode. In the above function the Smart Mode is enabled.

- ADDR register is used to hold the address of slave

- The INTENSET register is used to enable the required interrupts. In the above function, address match interrupt, stop received interrupt, and Data ready interrupt are enabled.

- CTRLA, CTRLB, and BAUD registers can be written only when the I<sup>2</sup>C is disabled because these registers are enable protected. So once configuring these registers, the I<sup>2</sup>C is enabled.

- Due to the asynchronicity between CLK\_SERCOMx\_APB and GCLK\_SERCOMx\_CORE, some

registers must be synchronized when accessed. ENABLE bit in CTRLA register is Write-Synchronized so

the application has to wait until SYSOP bit in SYNCBUSY register is cleared after writing to the ENABLE

bit.

- Each peripheral has a dedicated interrupt line, which is connected to the Nested Vector Interrupt

Controller in the Cortex-M0+ core. In the above function SERCOM2 interrupt request line (IRQ 11) is

enabled.

## 5.2.9 I<sup>2</sup>C Slave Transaction

SERCOM2 Handler will serve the I<sup>2</sup>C slave transaction function.

- In high speed mode, SCLSM bit should be set one, which is handled by application in the I<sup>2</sup>C slave initialization function

- For master reads (slave write), an address and data interrupt will be issued simultaneously with SCLSM

=1

- So for this purpose inside the SERCOM handler application will check for the direction flag inside the AMATCH condition. If DIR is set (Master Read – Slave Write) a Boolean flag 'slave\_write\_mode' will be set to true.

- In the same AMATCH condition inside the SERCOM handler application will check for the flag 'slave\_write\_mode' flag. If it is true, the application will write the first data byte from the buffer 'rx\_buff' followed by clearing the AMATCH interrupt flag. Otherwise the application will simply clear the AMATCH interrupt flag without performing any data read. Note that the same buffer 'rx\_buff' will be used for both slave transmission and reception.

- Inside the DRDY condition in SERCOM handler application will check for the Boolean flag

'slave\_write\_mode' status. If it is true (Master Read Slave Write), the application will write the data

from the buffer 'rx\_buff' for (BUF\_SIZE-1) times since the first data byte was already transmitted in

previous step. When DRDY is hit for the last time (iteration count is equal to BUF\_SIZE) the I²C lines are

released by writing command register with value 0x2.

- Otherwise, if the Boolean flag is false (Master Write Slave Read), the application will read the received data into buffer and send acknowledgment for each byte received by writing command register with value 0x3. When the iteration count reaches BUF\_SIZE-1 application will release the I<sup>2</sup>C lines by writing the command register with value 0x2 followed by reception of STOP condition.

- After reception of STOP condition (PREC condition inside SERCOM handler) application will clear the stop interrupt flag PREC and then reads the last received byte into buffer

```

void SERCOM2 Handler(void)

/* Check for Address match interrupt */

if(SERCOM2->I2CS.INTFLAG.bit.AMATCH)

{

/* Checking for direction,

DIR - 0 for slave read,

DIR - 1 for slave write */

if (SERCOM2->I2CS.STATUS.bit.DIR)

slave write mode = true;

else

slave write mode = false;

if (slave_write_mode)

{

SERCOM2->I2CS.DATA.reg = rx buff[i++];

/* clearing the Address match interrupt */

SERCOM2->I2CS.INTFLAG.bit.AMATCH = 1;

SERCOM2->I2CS.CTRLB.bit.CMD = 0x3;

}

else

{

/* clearing the Address match interrupt */

SERCOM2->I2CS.INTFLAG.bit.AMATCH = 1;

}

}

/* Data Ready interrupt check */

if(SERCOM2->I2CS.INTFLAG.bit.DRDY)

if (slave_write_mode)

{

if (i == BUF SIZE)

//SERCOM2->I2CS.DATA.reg = rx buff[i++];

```

```

/* wait for stop condition */

SERCOM2->I2CS.CTRLB.bit.CMD = 0x2;

i = 0;

}

else

{

SERCOM2->I2CS.DATA.reg = rx buff[i++];

/* Execute a byte read operation followed by ACK/NACK reception by master */

SERCOM2->I2CS.CTRLB.bit.CMD = 0x3;

}

}

else

{

if (i == BUF_SIZE-1)

SERCOM2->I2CS.CTRLB.bit.ACKACT = 0;

/* Execute acknowledge action succeeded by waiting for any start (S/Sr) condition */

SERCOM2->I2CS.CTRLB.bit.CMD = 0x2;

//i = 0;

}

else

{

rx_buff[i++] = SERCOM2->I2CS.DATA.reg;

SERCOM2->I2CS.CTRLB.bit.ACKACT = 0;

/* Execute acknowledge action succeeded by reception of next byte to master*/

SERCOM2->I2CS.CTRLB.bit.CMD = 0x3;

}

}

/* Stop received interrupt check */

if (SERCOM2->I2CS.INTFLAG.bit.PREC)

{

SERCOM2->I2CS.INTFLAG.bit.PREC = 1;

if (!slave_write_mode)

rx_buff[i++] = SERCOM2->I2CS.DATA.reg;

i = 0;

}

}

```

The final application "High speed Configuration" in main.c file will be as below for SLAVE.

```

uint8_t rx_buff[BUF_SIZE];

volatile bool slave write mode = false;

/* I2C handler */

void SERCOM2 Handler(void)

/* Check for Address match interrupt */

if(SERCOM2->I2CS.INTFLAG.bit.AMATCH)

{

/* Checking for direction,

DIR - 0 for slave read,

DIR - 1 for slave write */

if (SERCOM2->I2CS.STATUS.bit.DIR)

slave_write_mode = true;

else

slave write mode = false;

if (slave_write_mode)

SERCOM2->I2CS.DATA.reg = rx_buff[i++];

/* clearing the Address match interrupt */

SERCOM2->I2CS.INTFLAG.bit.AMATCH = 1;

SERCOM2->I2CS.CTRLB.bit.CMD = 0x3;

}

else

{

/* clearing the Address match interrupt */

SERCOM2->I2CS.INTFLAG.bit.AMATCH = 1;

}

}

/* Data Ready interrupt check */

if(SERCOM2->I2CS.INTFLAG.bit.DRDY)

{

if (slave write mode)

{

if (i == BUF_SIZE)

//SERCOM2->I2CS.DATA.reg = rx_buff[i++];

/* wait for stop condition */

SERCOM2->I2CS.CTRLB.bit.CMD = 0x2;

i = 0;

}

else

{

SERCOM2->I2CS.DATA.reg = rx_buff[i++];

/* Execute a byte read operation followed by ACK/NACK reception by master */

SERCOM2->I2CS.CTRLB.bit.CMD = 0x3;

}

}

else

{

if (i == BUF SIZE-1)

SERCOM2->I2CS.CTRLB.bit.ACKACT = 0;

/* Execute acknowledge action succeeded by waiting for any start (S/Sr) condition */

SERCOM2->I2CS.CTRLB.bit.CMD = 0x2;

//i = 0;

}

```

```

else

{

rx buff[i++] = SERCOM2->I2CS.DATA.reg;

SERCOM2->I2CS.CTRLB.bit.ACKACT = 0;

/* Execute acknowledge action succeeded by reception of next byte to master*/

SERCOM2->I2CS.CTRLB.bit.CMD = 0x3;

}

}

/* Stop received interrupt check */

if (SERCOM2->I2CS.INTFLAG.bit.PREC)

SERCOM2->I2CS.INTFLAG.bit.PREC = 1;

if (!slave_write_mode)

rx buff[i++] = SERCOM2->I2CS.DATA.reg;

i = 0;

}

}

/*Assigning pin to the alternate peripheral function*/

static inline void pin set peripheral function(uint32 t pinmux)

{

uint8 t port = (uint8 t)((pinmux \Rightarrow 16)/32);

PORT->Group[port].PINCFG[((pinmux >> 16) - (port*32))].bit.PMUXEN = 1;

PORT->Group[port].PMUX[((pinmux >> 16) - (port*32))/2].reg &= ~(0xF << (4 * ((pinmux >>

16) & 0x01u)));

PORT->Group[port].PMUX[((pinmux >> 16) - (port*32))/2].reg |= (uint8 t)((pinmux &

0x0000FFFF) << (4 * ((pinmux >> 16) & 0x01u)));

/* SERCOM clock and peripheral bus clock initialization */

void i2c clock init()

{

struct system gclk chan config gclk chan conf;

uint32_t gclk_index = SERCOM2_GCLK_ID_CORE;

/* Turn on module in PM */

system_apb_clock_set_mask(SYSTEM_CLOCK_APB_APBC, PM_APBCMASK_SERCOM2);

/* Turn on Generic clock for I2C */

system gclk chan get config defaults(&gclk chan conf);

//Default is generator 0. Other wise need to configure like below

/* gclk_chan_conf.source_generator = GCLK_GENERATOR_1; */

system_gclk_chan_set_config(gclk_index, &gclk_chan_conf);