# Atmel PLDs' Architectures Simplify Timing Calculation<sup>(1)</sup>

### Introduction

This application note shows different graphical timing models that can help the user visualize the AC timing of the various Atmel PLD families of devices. Because of their deterministic and pathindependent delays, timing calculation becomes straight forward.

Atmel PLDs have regular AND-OR architecture which simplifies timing calculation. All the AC timing parameters are clearly stated in the data book. Even for complex designs it only takes a few minutes to calculate the delays by hand.

If the design engineer has access to tools such as the Atmel-ViewPLD, he/she can easily predict the performance of the PLD. PLD software packages with timing simulation capabilities let the design engineer know the performance of the PLD immediately after the design is entered and check the

results of the timing simulator and quickly modify the design to meet the system timing requirements. Atmel offers a complete design entry package called Atmel-ViewPLD that has such a timing simulator.

# Architectures/Timing Models

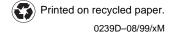

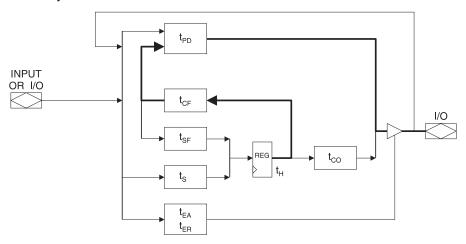

The AT22V10 represents the classic PAL<sup>™</sup>-type architecture with the programmable AND and fixed OR structure. A very small set of AC timing parameters can describe all the delays that occur in the implementation of register and combinatorial logic as shown in Figure 1.

For example, an output is described in the following Boolean equation:

OUTPUT = A0 & !A1 & A2 # SELECT;

Note: 1. Timing models for the ATF15XX devices are in their own specific application note (see: Using the ATF1500 CPLD).

Figure 1. AT22V10, ATV750, ATV750B, and ATV2500 Timing Model

# Programmable Logic Device

# Application Note

Rev. 0239D-08/99

A0, A1, A2, and SELECT can be inputs or I/O's and the delay will be simply the time for the signal to propagate from a pin through the AND-OR array, the macrocell, and to the output pin. This is described by the AC parameter  $t_{\text{PD}}$ .

The ATV750/ATV750B and ATV2500 with more advanced macrocells, maintain the same AND-OR structure as the AT22V10. Because of this, they can also be described by the same AT22V10 timing model. Even when using the buried registers found in the ATV750/ATV750B and ATV2500, the method of calculation for delays stays the same. For example, an ABEL™ description of a binary counter may look like:

### COUNT.d = COUNT.fb + 1;

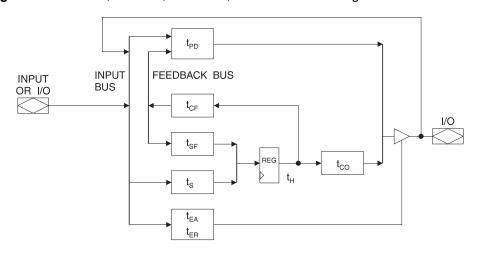

The counter can be implemented using only the internal buried registers of the ATV750, ATV750B, or ATV2500. In this case the minimum cycle time will be equal to  $t_{\rm CF}$  (clock

to feedback) +  $t_{SF}$  (feedback setup). See Figure 2. This is also equal to  $1/(F_{MAX}$  internal).

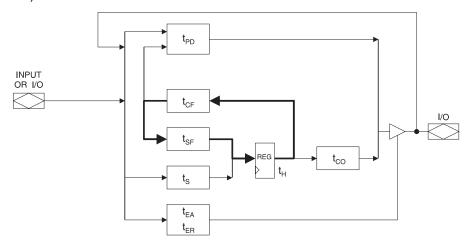

Figure 3 shows the registered data path for a pin-to-pin delay, as might be described by output logic:

If A1, B1, and C1 are all signals from either input or I/O pins, then the minimum cycle time will be  $t_{\rm S}$  (setup time for input or I/O pin) +  $t_{\rm CO}$  (clock to output) which is equal to 1/( $F_{\rm MAX}$  external).

Figure 4 shows how data propagates for a typical Mealy state-machine, in which the state bits are inputs to combinatorial outputs:

Figure 2. 1/(F<sub>MAX</sub> internal)

Figure 3. 1/(F<sub>MAX</sub> external)

In this case, it will take FULL the delay of  $t_{\rm CF}$  +  $t_{\rm PD}$  to go from the rising edge of the clock driving the counter to the changing of FULL's output value.

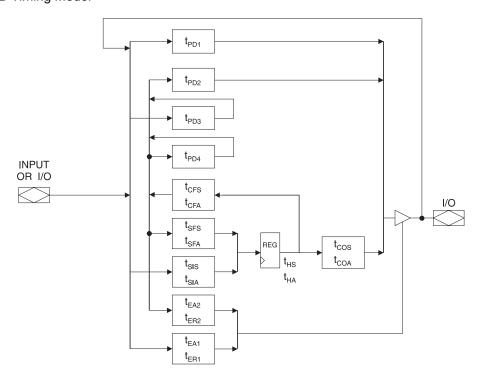

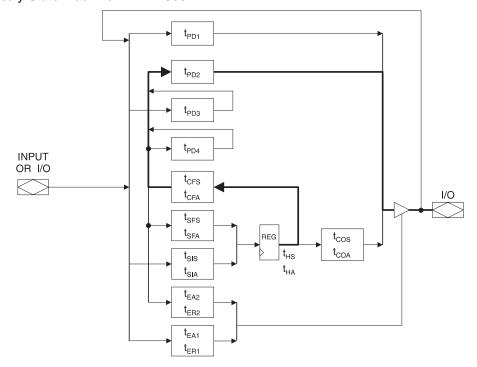

These devices have both synchronous and asynchronous modes of operation. With the addition of the synchronous clocking option, the devices perform at a higher clock rate. The AC parameters have either the suffix of "S" (synchronous) or "A" (asynchronous) to distinguish the two registered clocking options.

Input latch setup and hold time are additional requirements when the latch is used. If the latch is bypassed, no delay is added.

For ATV2500B, the  $t_{PD}$  parameter is broken down further to show different delay paths separately.  $t_{PD1}$  and  $t_{PD2}$  are similar to the traditional  $t_{PD}$  parameter.  $t_{PD1}$  is the delay from any pin to any combinatorial output.  $t_{PD2}$  is the delay from internal feedback nodes to a combinatorial output pin.

$t_{\mbox{\scriptsize PD}3}$  is the delay from a pin to an internal combinatorial feedback.

t<sub>PD4</sub> is the delay from an internal feedback, through the AND/OR array, to an internal combinatorial feedback.

The ATV2500B lets the user configure internal combinatorial or registered feedbacks.

Figure 4. Mealy Machine Delay Path

Figure 5. ATV2500B Timing Model

The most straightforward way to determine the delays is to look at the documentation generated by PLD software after the design has been reduced and fitted. If a reduced equation looks like:

OUTA = WATCHDOG "Product term 1 # A1 & A2 & A3 "Product term 2 # C\_OUT; "Product term 3

- Determine whether the logic is registered or combinatorial.

- 2. Determine whether OUTA is an internal node or an output pin.

- 3. Find the source of each of the components that makes up the product terms.

To analyze the various cases, let's assume the following:

- OUTA is combinatorial. We will look at OUTA implemented mented on an output pin versus OUTA implemented on a combinatorial node.

- WATCHDOG is an internal registered node, A1 through A3 are directly from the inputs, and C\_OUT

is an internal combinatorial node (this covers all signal sources).

Table 1 summarizes the various timing requirements.

Case 1 (Figure 6) is the typical Mealy state machine where the internal state registers are decoded to form a combinatorial output. The total delay from clock to output is  $t_{\rm CF}$  +  $t_{\rm PD2}$ .

Case 2 is the pin-to-pin delay. The AC parameter for that is  $t_{\text{PD1}}$ .

Case 3 is an internal combinatorial feedback's delay from the AND/OR array to the output pin:  $t_{PD2}$ .

Case 4 is a "buried Mealy" where the internal state registers are decoded but not placed on an output pin. Instead the result is implemented on an internal combinatorial node where the logic is only useful internal to the design.

Case 5 is the delay from pin to internal combinatorial feedback:  $t_{\text{PD3}}$ .

Case 6 is the delay from one internal combinatorial node to another internal combinatorial node.

Table 1.

|                           | Registered Feedback<br>P.T. 1              | Input from Pins<br>P.T. 2 | Internal Combinatorial Node P.T. 3 |

|---------------------------|--------------------------------------------|---------------------------|------------------------------------|

| Combinatorial Output OUTA | Case 1: t <sub>CF</sub> + t <sub>PD2</sub> | Case 2: t <sub>PD1</sub>  | Case 3: t <sub>PD2</sub>           |

| Combinatorial Node OUTA   | Case 4: t <sub>CF</sub> + t <sub>PD4</sub> | Case 5: t <sub>PD3</sub>  | Case 6: t <sub>PD4</sub>           |

Figure 6. Typical Mealy State Machine in ATV2500B

## Conclusion

The graphical representation of the AC timing models illustrate how simple it is to determine the performance of logic implemented in a Atmel PLD. Atmel complex PLDs, even

with their high pin counts and advanced features, have simple timing calculation. They aren't any harder to use than a common AT22V10.

### **Atmel Headquarters**

Corporate Headquarters 2325 Orchard Parkway San Jose, CA 95131 TEL (408) 441-0311 FAX (408) 487-2600

#### Europe

Atmel U.K., Ltd.

Coliseum Business Centre

Riverside Way

Camberley, Surrey GU15 3YL

England

TEL (44) 1276-686-677

FAX (44) 1276-686-697

#### Asia

Atmel Asia, Ltd.

Room 1219

Chinachem Golden Plaza

77 Mody Road Tsimhatsui

East Kowloon

Hong Kong

TEL (852) 2721-9778

FAX (852) 2722-1369

#### Japan

Åtmel Japan K.K. 9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581

### **Atmel Operations**

Atmel Colorado Springs 1150 E. Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL (719) 576-3300 FAX (719) 540-1759

Atmel Rousset

Zone Industrielle

13106 Rousset Cedex

France

TEL (33) 4-4253-6000

FAX (33) 4-4253-6001

Fax-on-Demand North America: 1-(800) 292-8635 International: 1-(408) 441-0732

e-mail literature@atmel.com

Web Site http://www.atmel.com

BBS 1-(408) 436-4309

#### © Atmel Corporation 1999.

Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

Marks bearing ® and/or ™ are registered trademarks and trademarks of Atmel Corporation.

PAL™ and ABEL™ may be registered trademarks of others.