# PIC16(L)F19155/56/75/76/85/86 Family Silicon Errata and Data Sheet Clarifications

The PIC16(L)F19155/56/75/76/85/86 family devices that you have received conform functionally to the current device data sheet (DS40001923**B**), except for the anomalies described in this document.

The silicon issues discussed in the following pages are for silicon revisions with the Device and Revision IDs listed in Table 1. The silicon issues are summarized in Table 2.

The errata described in this document will be addressed in future revisions of the PIC16(L)F19155/56/75/76/85/86 silicon.

Note: This document summarizes all silicon errata issues from all revisions of silicon, previous as well as current. Only the issues indicated in the last column of Table 2 apply to the current silicon revision (A4).

Data Sheet clarifications and corrections start on page 7, following the discussion of silicon issues.

The silicon revision level can be identified using the current version of MPLAB® IDE and Microchip's programmers, debuggers, and emulation tools, which are available at the Microchip corporate website (www.microchip.com).

For example, to identify the silicon revision level using MPLAB IDE in conjunction with a hardware debugger:

- 1. Using the appropriate interface, connect the device to the hardware debugger.

- 2. Open an MPLAB IDE project.

- 3. Configure the MPLAB IDE project for the appropriate device and hardware debugger.

- 4. For MPLAB X IDE, select <u>Window > Dashboard</u> and click the **Refresh Debug Tool Status** icon ( ☑ ).

- 5. Depending on the development tool used, the part number *and* Device Revision ID value appear in the **Output** window.

**Note:** If you are unable to extract the silicon revision level, please contact your local Microchip sales office for assistance.

The DEVREV values for the various PIC16(L)F19155/56/75/76/85/86 silicon revisions are shown in Table 1.

TABLE 1: SILICON DEVREV VALUES

| Don't Name have | Device ID <sup>(1)</sup> | Revisio | n ID for Silicon Re | vision <sup>(2)</sup> |

|-----------------|--------------------------|---------|---------------------|-----------------------|

| Part Number     | Device ID(··)            | A1      | А3                  | A4                    |

| PIC16F19155     | 3096h                    | 2001h   | 2003h               | 2004h                 |

| PIC16LF19155    | 3097h                    | 2001h   | 2003h               | 2004h                 |

| PIC16F19156     | 3098h                    | 2001h   | 2003h               | 2004h                 |

| PIC16LF19156    | 3099h                    | 2001h   | 2003h               | 2004h                 |

| PIC16F19175     | 309Ah                    | 2001h   | 2003h               | 2004h                 |

| PIC16LF19175    | 309Bh                    | 2001h   | 2003h               | 2004h                 |

| PIC16F19176     | 309Ch                    | 2001h   | 2003h               | 2004h                 |

| PIC16LF19176    | 309Dh                    | 2001h   | 2003h               | 2004h                 |

| PIC16F19185     | 30BAh                    | 2001h   | 2003h               | 2004h                 |

| PIC16LF19185    | 30BBh                    | 2001h   | 2003h               | 2004h                 |

| PIC16F19186     | 30BCh                    | 2001h   | 2003h               | 2004h                 |

| PIC16LF19186    | 30BDh                    | 2001h   | 2003h               | 2004h                 |

- **Note 1:** The Device and Revision IDs is located at the respective addresses 8006h and 8005h of configuration memory space.

- 2: Refer to the "PIC16(L)F191XX Memory Programming Specification" (DS40001880) for detailed information on Device and Revision IDs for your specific device.

TABLE 2: SILICON ISSUE SUMMARY

| Module                                                       | Feature                                                   | Item   | Summary                                                                                                   | Affec      | ted Rev | isions |

|--------------------------------------------------------------|-----------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------|------------|---------|--------|

| Wodule                                                       | reature                                                   | Number | Summary                                                                                                   | <b>A</b> 1 | А3      | A4     |

|                                                              | ADC <sup>2</sup> with Fixed<br>Voltage Reference<br>(FVR) | 1.1    | Using the FVR as the ADC positive voltage reference can cause missing codes.                              | Х          |         |        |

|                                                              | ADC <sup>2</sup> with Guard<br>Ring Outputs               | 1.2    | The Guard Ring Output feature is not implemented.                                                         | Х          |         |        |

| Analog-to-Digital<br>Converter with<br>Computation<br>(ADC2) | ADC <sup>2</sup> FRC Clock<br>Sleep Mode                  | 1.3    | If in Sleep and ADCRC is used, the oscillator continues to run after conversion.                          | Х          |         |        |

|                                                              | ADC <sup>2</sup> FRC Clock<br>ADGO Delay                  | 1.4    | When using FRC as clock source, there is a delay of one instruction cycle.                                | Х          |         |        |

|                                                              | ADC <sup>2</sup> Conversion                               | 1.5    | At the very beginning of the ADC conversion, the input signal may briefly be pulled to ground.            | Х          |         |        |

| Reset and Vbat                                               | VBAT with ULPBOR                                          | 2.1    | Higher current with ULPBOR active.                                                                        | Χ          |         |        |

| Liquid Crystal                                               | Internal VLCD3<br>Measurement                             | 3.1    | Non-stable readings.                                                                                      | Χ          |         |        |

| Display (LCD)<br>Controller                                  | 1/2 MUX, 1/2 Bias<br>with External<br>Resistor Ladder     | 3.2    | 1/2 MUX, 1/2 Bias with External Resistor Ladder is not operational.                                       |            |         |        |

| Comparator<br>(CMP)                                          |                                                           |        | Unstable output.                                                                                          | Х          | Х       | х      |

| Windowed<br>Watchdog Timer<br>(WWDT)                         | Watchdog Timer<br>Clock Source                            | 5.1    | WWDT only operates from the LFINTOSC clock source.                                                        | Х          |         |        |

| Real-Time Clock<br>and Calendar<br>(RTCC)                    | RTCC Alarm                                                | 6.1    | An alarm will not occur if the lower nibble of ALRMLSEC <3:0> is configured to 0x0.                       | Х          |         |        |

|                                                              | SMBus VIL Level                                           | 7.1    | The maximum VIL level changes when VDD is below 4.0V.                                                     | Х          |         |        |

| Electrical<br>Specifications                                 | Fixed Voltage<br>Reference (FVR)<br>Accuracy              | 7.2    | Fixed Voltage Reference (FVR) output tolerance may be higher than specified at temperatures below - 20°C. | Х          | х       | х      |

| Specifications                                               | Nonvolatile Memory<br>(NVM) for LF<br>Devices             | 7.3    | Performing a row erase through the NVMREG access may not execute as expected when VDD is lowered.         | Х          | Х       | х      |

|                                                              | Min VDD<br>Specification                                  | 7.4    | VDD Min. specifications are changed for LF devices only.                                                  | Х          | Х       | Х      |

| Device<br>Information Area<br>(DIA)                          | Fixed Voltage<br>Reference Data                           | 8.1    | FVR Reference Data may be missing                                                                         | Х          |         |        |

| TMR0                                                         | Clock Source                                              | 9.1    | TMRH register does not increment when the clock source is Fosc/4 and the T0ASYNC bit is cleared.          | Х          | Х       | х      |

#### Silicon Errata Issues

Note:

This document summarizes all silicon errata issues from all revisions of silicon, previous as well as current. Only the issues indicated by the shaded column in the following tables apply to the current silicon revision (A4).

### 1. Module: Analog-to-Digital Converter with Computation (ADC<sup>2</sup>)

#### 1.1 ADC<sup>2</sup> with Fixed Voltage Reference (FVR)

Using the FVR as the positive voltage reference (VREF+) for the ADC can cause an increase in missing codes.

#### Work around

Method 1: Increase the bit conversion time, known as TAD, to 8  $\mu$ s or higher.

Method 2: Use VDD as the positive voltage reference to the ADC.

#### **Affected Silicon Revisions**

| <b>A</b> 1 | А3 | <b>A4</b> |  |  |  |

|------------|----|-----------|--|--|--|

| Χ          |    |           |  |  |  |

#### 1.2 ADC<sup>2</sup> with Guard Ring Outputs

The two guard ring drive outputs ADGRDA and ADGRDB are not implemented on these devices.

#### Work around

None.

#### **Affected Silicon Revisions**

| <b>A</b> 1 | А3 | A4 |  |  |  |

|------------|----|----|--|--|--|

| Х          |    |    |  |  |  |

#### 1.3 ADC<sup>2</sup> FRC Clock Sleep Mode

If the part is in Sleep and the ADCRC oscillator is used as the clock source to the ADC, the oscillator continues to run after the conversion is complete. This will increase the current consumption in Sleep mode. The oscillator will stop after the device exits Sleep mode and resumes normal code execution.

#### Work around

None.

#### **Affected Silicon Revisions**

| <b>A</b> 1 | А3 | A4 |  |  |  |

|------------|----|----|--|--|--|

| Χ          |    |    |  |  |  |

#### 1.4 ADC<sup>2</sup> FRC Clock ADGO Delay

When using the FRC as the clock source for ADC<sup>2</sup>, there is a delay of one instruction cycle between the user setting the ADGO bit and being able to read it. This can lead to a false conversion complete scenario (i.e., ADGO being cleared) if the user code has a bit clear test (BTFSC) instruction on the ADGO bit immediately after setting the ADGO bit. See Code Example below.

| ADCON0, ADGO | ;Start conversion     |

|--------------|-----------------------|

| ADCON0, ADGO | ; Is conversion done? |

| \$-1         | ;No, test again       |

|              | ADCON0, ADGO          |

The BTFSC will pass the very first time in this situation.

#### Work around

Add a NOP instruction after setting the ADGO bit and before testing the bit for completion of conversion. See Code Example below:

| BSF   | ADCON0, ADGO; Start conversion     |

|-------|------------------------------------|

| NOP   |                                    |

| BTFSC | ADCON0, ADGO ; Is conversion done? |

| GOTO  | \$-1 ;No, test again               |

#### **Affected Silicon Revisions**

| <b>A</b> 1 | А3 | <b>A4</b> |  |  |  |

|------------|----|-----------|--|--|--|

| Χ          |    |           |  |  |  |

#### 1.5 ADC<sup>2</sup> Conversion

At the very beginning of the ADC conversion, the input signal may briefly be pulled to ground, which in turn may take some charge out of the internal sample and hold capacitor. The problem is more pronounced on inputs with an impedance greater than 1 k $\Omega$ .

This issue will be seen when sampling the FVR, DAC and Temperature Indicator internal channel inputs and when sampling external sources on an analog pin, including the CVD.

#### Work around

When sampling the internal channel inputs FVR, DAC and Temperature Indicator, increase the minimum TAD time to 4  $\mu s$  to increase accuracy.

When sampling an external source through an analog pin, keep the input impedance below 1  $k\Omega$ .

When using the ADC as an internal reference for the CVD module, there is no work around.

#### **Affected Silicon Revisions**

| <b>A</b> 1 | А3 | A4 |  |  |  |

|------------|----|----|--|--|--|

| Χ          |    |    |  |  |  |

2. Module: Reset and VBAT

#### 2.1 VBAT with ULPBOR

To avoid high IBAT currents of 10  $\mu$ A or greater, when utilizing VBAT to provide battery backup, the ULPBOR should not be activated. When the part is used in this manner, VDD should either be off (0 volts) or >1.5V.

#### Work around

Do not use VBAT along with ULPBOR.

#### **Affected Silicon Revisions**

| <b>A</b> 1 | А3 | <b>A4</b> |  |  |  |

|------------|----|-----------|--|--|--|

| Χ          |    |           |  |  |  |

### 3. Module: Liquid Crystal Display (LCD) Controller

#### 3.1 Internal VLCD3 Measurement

The ¼ scale tap point provided on the LP Resistor Ladder for use together with the ADC does not provide stable readings to support monitoring of the LCD pump output level.

#### Work around

Measure the VLCD3 via an external ADC.

#### **Affected Silicon Revisions**

| <b>A</b> 1 | А3 | A4 |  |  |  |

|------------|----|----|--|--|--|

| Х          |    |    |  |  |  |

### 3.2 1/2 MUX, 1/2 Bias with External Resistor Ladder

The 1/2 MUX, 1/2 Bias with External Resistor Ladder mode of operation is non-functional.

#### Work around

For 1/2 MUX, 1/2 Bias mode operation use the internal LP, MP or HP ladder.

#### Affected Silicon Revisions

|   | <b>A1</b> | А3 | A4 |  |  |  |

|---|-----------|----|----|--|--|--|

| Ī | Χ         |    |    |  |  |  |

#### 4. Module: Comparator (CMP)

#### 4.1 C2 Low-Power Clocked Comparator

The output of the Low-Power Clocked Comparator (CMP2) is unstable and is not recommended for use.

#### Work around

None.

#### **Affected Silicon Revisions**

| <b>A</b> 1 | А3 | A4 |  |  |  |

|------------|----|----|--|--|--|

| Χ          | Χ  | Χ  |  |  |  |

### 5. Module: Windowed Watchdog Timer (WWDT)

#### 5.1 Watchdog Timer Clock Source

When the WDTCS <2:0> bits of the WDTCON1 register are set to either the MFINTOSC (b'001') or the SOSC (b'010') clock source, the WWDT does not operate.

#### Work around

Use the LFINTOSC (b'000') as the clock source for the WWDT.

#### Affected Silicon Revisions

| <b>A</b> 1 | А3 | A4 |  |  |  |

|------------|----|----|--|--|--|

| Χ          |    |    |  |  |  |

## 6. Module: Real-Time Clock and Calendar (RTCC)

#### 6.1 Real-Time Clock and Calendar (RTCC) Alarm

When using the RTCC alarm function in any mode other than AMASK<3:0> =  $0 \pm 00000$  or AMASK<3:0> =  $0 \pm 00001$ , an alarm will not occur if the lower nibble of the ALRMSEC register, ALRMLSEC <3:0>, is configured to 0x0.

#### Work around

If an alarm is desired when the lower nibble of the SECONDS register = 0x0, configure ALRMLSEC<3:0> = 0xA.

#### **Affected Silicon Revisions**

| <b>A1</b> | А3 | <b>A4</b> |  |  |  |

|-----------|----|-----------|--|--|--|

| Χ         |    |           |  |  |  |

#### 7. Module: Electrical Specifications

#### 7.1 SMBus VIL Level

When the VDD voltage level supplied to the device is 4.0V and above, the maximum SMBus voltage level for the VIL parameter is 0.8V. When VDD drops below 4.0V, the maximum SMBus voltage level for VIL drops to 0.7V.

#### Work around

None.

#### **Affected Silicon Revisions**

| A1 | А3 | <b>A4</b> |  |  |  |

|----|----|-----------|--|--|--|

| Х  |    |           |  |  |  |

#### 7.2 Fixed Voltage Reference (FVR) Accuracy

At temperatures below -20°C, the output voltage for the FVR may be greater than the levels specified in the data sheet. This will apply to all three gain amplifier settings (1X, 2X, 4X). The affected parameter numbers found in the data sheet are: FVR01 (1X gain setting), FVR02 (2X gain setting), and FVR03 (4X gain setting).

#### Work around

At temperatures above -20°C, the stated tolerances in the data sheet remain in effect. Operate the FVR only at temperatures above -20°C.

#### **Affected Silicon Revisions**

| <b>A</b> 1 | А3 | <b>A4</b> |  |  |  |

|------------|----|-----------|--|--|--|

| Χ          | Χ  | Χ         |  |  |  |

#### 7.3 Nonvolatile Memory (NVM) for LF Devices

Performing a row erase through the NVMREG access on LF devices may not execute as expected when VDD is lowered from >3.3V down to <2.0V before or during the row erase, while also operating between +25°C and -40°C.

#### Work around

None.

#### **Affected Silicon Revisions**

| A1 | А3 | <b>A4</b> |  |  |  |

|----|----|-----------|--|--|--|

| Χ  | Х  | X         |  |  |  |

#### 7.4 Minimum VDD Specification for LF Devices

VDD minimum parameter (D002) at -40°C to +25°C = 2.3V. (See Table 39-1 for reference.)

#### Work around

None.

#### **Affected Silicon Revisions**

| <b>A</b> 1 | А3 | A4 |  |  |  |

|------------|----|----|--|--|--|

| Χ          | Χ  | Χ  |  |  |  |

#### 8. Module: Device Information Area (DIA)

#### 8.1 Fixed Voltage Reference Data

Devices marked with date code 1846 and older may or may not have the measured FVR reference data stored in DIA address locations 8118h through 811Dh. Devices marked with date code 1847 and newer are not affected.

#### Work around

None.

#### Affected Silicon Revisions

| <b>A</b> 1 | А3 | <b>A4</b> |  |  |  |

|------------|----|-----------|--|--|--|

| Х          |    |           |  |  |  |

9. Module: TMR0

#### 9.1 Clock Source

Clocking Timer0 in 16-bit mode with Fosc/4 and clearing the T0ASYNC bit in the T0CON1 register may cause the High-Byte register, TMRH, not to increment. This issue is only valid when Fosc/4 is used as the clock source.

#### Work around

When using Fosc/4 as the Timer0 clock, set the T0ASYNC bit in the T0CON1 register to '1'.

#### **Affected Silicon Revisions**

| A1 | А3 | <b>A4</b> |  |  |  |

|----|----|-----------|--|--|--|

| Χ  | Х  | Х         |  |  |  |

#### **Data Sheet Clarifications**

The following typographic corrections and clarifications are to be noted for the latest version of the device data sheet (DS40001923**B**):

**Note:** Corrections are shown in **bold**. Where possible, the original bold text formatting has been removed for clarity.

1. Module: Electrical Specifications

#### 1.1 Table 39-1: Supply Voltage

The minimum VDD specification for LF devices is shown below: VDD minimum parameter (D002) at  $-40^{\circ}$ C to  $25^{\circ}$ C = 2.3V.

#### **TABLE 39-1: SUPPLY VOLTAGE**

| PIC16(L)      | PIC16(L)F19155/56/75/76/85/86 |                 |                   | Standard Operating Conditions (Unless Otherwise Stated) |                   |             |                                                                                                                                                                                                          |

|---------------|-------------------------------|-----------------|-------------------|---------------------------------------------------------|-------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No. | Sym.                          | Characteristics | Min.              | Тур.                                                    | Max.              | Units       | Comments                                                                                                                                                                                                 |

| D002          | VDD                           |                 | 1.8<br>2.3<br>2.5 | _                                                       | 3.6<br>3.6<br>3.6 | V<br>V<br>V | $\begin{aligned} &\text{Fosc} \leq \text{16 MHz, TA} > 25^{\circ}\text{C} \\ &\text{Fosc} \leq \text{16 MHz, -40°C} \leq \text{TA} \leq 25^{\circ}\text{C} \\ &\text{Fosc} > \text{16 MH} \end{aligned}$ |

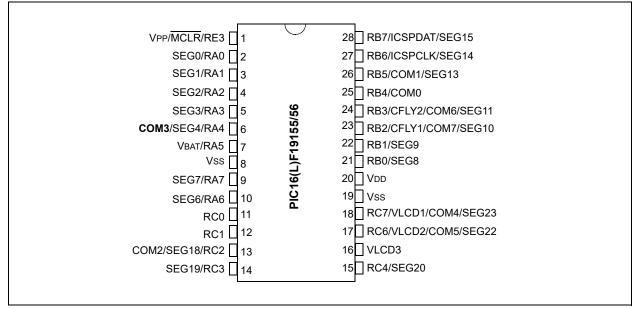

2. Module: Pin Diagrams

#### 2.1 Pin Diagrams, Figure 1

The COM0 function multiplexed to RA4 is changed to COM3, as shown below.

FIGURE 1: 28-PIN SSOP, SPDIP AND SOIC PIN DIAGRAM FOR PIC16(L)F19155/56

# APPENDIX A: DOCUMENT REVISION HISTORY

#### Rev K Document (07/2024)

Added Module 9.1 (TMR0).

#### Rev J Document (10/2022)

Added DS Clarification, Module 2: Pin Diagrams.

#### Rev H Document (11/2021)

Added silicon revision A4.

#### Rev G Document (02/2021)

Updated Table 2 and sub-section 7.4. Added DS Clarifications Module 1: Electrical Specifications. Other minor editorial corrections.

#### **Rev F Document (06/2019)**

Data Sheet Clarifications: Removed all modules (Data Sheet updated).

#### Rev E Document (04/2019)

Added silicon rev. A3.

Removed Module 1.5: ADC<sup>2</sup> Channel Switching.

Added Module 8: Device Information Area (DIA).

Data Sheet Clarifications: Added Module 1.2: TAD Parameters. Updated Section 3: Capture/Compare/PWM Modules.

#### **Rev D Document (09/2018)**

Added Module 1.3 ADC<sup>2</sup> FRC Clock Sleep Mode. Added Module 1.4 ADC<sup>2</sup> FRC Clock ADGO Delay. Added Module 1.5 ADC<sup>2</sup> Channel Switching. Added Module 1.6 ADC<sup>2</sup> Conversion. Added Module 3.2 1/2 MUX, 1/2 Bias with External Resistor Ladder. Added 5.1 Watchdog Timer Clock Source. Added Module 6: Real-Time Clock and Calendar (RTCC) and 6.1 RTCC Alarm. Updated Table 2.

#### **Rev C Document (05/2018)**

Added silicon issue 5.4: Min VDD Specification for LF devices.

Data Sheet Clarifications: Added Module 1: Analog-to-Digital with Computation (ADC<sup>2</sup>) and Module 2: Real-Time Clock and Calendar (RTCC).

#### **Rev B Document (11/2017)**

Added silicon issue 5.3: Nonvolatile Memory (NVM) for LF devices.

#### **Rev A Document (06/2017)**

Initial release of this document; issued for revision A1. Includes silicon issues 1.1 (ADC $^2$ ), 2.1 (VBAT), 3.1 (LCD), 4.1 (CMP), Electrical Specifications: 5.1 SMBus, 5.2 Program Flash Memory, and 5.3 FVR.

#### Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable" Code protection is constantly evolving. Microchip is committed to

continuously improving the code protection features of our products.

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at <a href="https://www.microchip.com/en-us/support/design-help/client-support-services">https://www.microchip.com/en-us/support/design-help/client-support-services</a>.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPlC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, TimeCesium, TimeHub, TimePictra, TimeProvider, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, Clockstudio, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, EyeOpen, GridTime, IdealBridge, IGaT, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, IntelliMOS, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, MarginLink, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mSiC, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, Power MOS IV, Power MOS 7, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, Trusted Time, TSHARC, Turing, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2024, Microchip Technology Incorporated and its subsidiaries.

All Rights Reserved.

ISBN: 978-1-6683-4809-3

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

#### **Worldwide Sales and Service**

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/

support Web Address:

www.microchip.com

Atlanta Duluth, GA

Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX

Tel: 281-894-5983 Indianapolis

Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

**China - Beijing** Tel: 86-10-8569-7000

China - Chengdu Tel: 86-28-8665-5511

China - Chongqing Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

**China - Nanjing** Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

**China - Shanghai** Tel: 86-21-3326-8000

**China - Shenyang** Tel: 86-24-2334-2829

China - Shenzhen Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

**China - Wuhan** Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

China - Xiamen

Tel: 86-592-2388138

**China - Zhuhai** Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune

Tel: 91-20-4121-0141

Japan - Osaka

Tel: 81-6-6152-7160 Japan - Tokyo

Tel: 81-3-6880- 3770

Korea - Daegu Tel: 82-53-744-4301

Korea - Seoul Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

**Singapore** Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

#### **EUROPE**

**Austria - Wels** Tel: 43-7242-2244-39

Fax: 43-7242-2244-393

Denmark - Copenhagen Tel: 45-4485-5910

Fax: 45-4485-2829 Finland - Espoo

Tel: 358-9-4520-820

France - Paris

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

Germany - Garching Tel: 49-8931-9700

**Germany - Haan** Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-72400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

**Israel - Hod Hasharon** Tel: 972-9-775-5100

**Italy - Milan** Tel: 39-0331-742611

Fax: 39-0331-466781

Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

**Poland - Warsaw** Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Gothenberg** Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820