### **Hardware Limit Timer on PIC® Microcontrollers**

Author: Swathi Sridhar

Microchip Technology Inc.

#### INTRODUCTION

PIC<sup>®</sup> microcontrollers are equipped with hardware features that are useful for implementing Fault detection in safety critical applications. The Hardware Limit Timer (HLT), which has hardware monitoring capabilities for missed periodic events, is one such feature. This on-chip peripheral helps in detecting external hardware Fault conditions like Stall and Stop conditions in a motor control application. It can also be used for any precise timing application that has a dependency on an external signal. This document aims at familiarizing the reader with the functionality of the HLT and its different modes of operation.

#### THE HARDWARE LIMIT TIMER

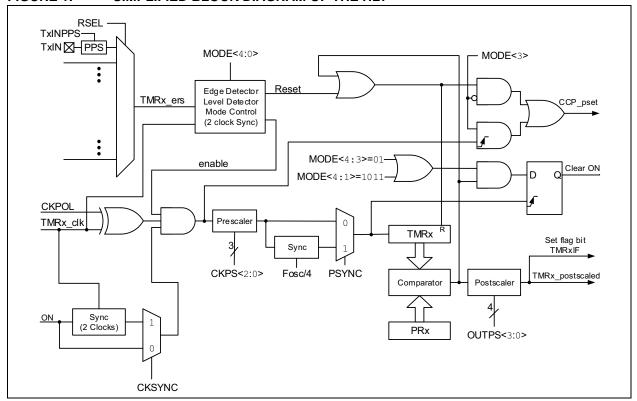

The Hardware Limit Timer is an enhanced version of Microchip's PIC microcontroller Timer2 module with the addition of an asynchronous external Reset capability and one-shot functionality. The timer can be started, stopped and reset based on an external event. This external signal can be from an external input pin or can be derived from on-chip core independent peripherals such as a comparator or the Zero-Cross Detect (ZCD). The timer can produce an interrupt signal when an expected event is missed. Using the HLT feature minimizes the CPU overhead, thereby freeing the CPU for other time-critical applications. The HLT also eliminates the need of any external components for fault handling. It has multiple modes of operation and selectable clock sources, which makes the design flexible. The simplified block diagram of Timer2 with the hardware limit feature is shown in Figure 1. The HLT is started by setting the ON bit of the TxCON register. The mode of operation is controlled by the MODE bits of the TxHLT register.

FIGURE 1: SIMPLIFIED BLOCK DIAGRAM OF THE HLT

The Hardware Limit Timer can be clocked using one of the following clock sources:

- FOSC (System Clock)

- FOSC/4 (Instruction Clock)

- LFINTOSC (Low-Frequency Internal Oscillator)

- MFINTOSC (Medium-Frequency Internal Oscillator)

- HFINTOSC (High-Frequency Internal Oscillator)

- Timer0 or Timer1 Output Pin

- Timer Input Pin

For the external source to the HLT, the following external trigger sources can be chosen:

- Complementary Waveform Generator (CWG)

- Zero-Cross Detect (ZCD)

- Capture/Compare/PWM (CCP)

- Timer4

- Timer6

- Comparator

**Note:** Some of these features might vary depending on the family of products. Refer to the product specific data sheet for

further details.

#### MODES OF OPERATION

The modes in the HLT can be broadly classified into Rollover Pulse mode, One-Shot mode and Monostable mode. The Hardware Limit Timer feature for these modes allows the selected input to clear the TMRx register and restart the timing sequence. There are both edge-sensitive and level-sensitive options defined. Table 1 summarizes all the modes of the timer and the working of each mode.

#### TABLE 1: MODES OF OPERATION OF HLT WITH START, STOP AND RESET CONDITIONS

| Mode           |                                                                                                                            | Operation                                                 | Start                                         | Reset              | Stop                          |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------|--------------------|-------------------------------|--|

| Rollover Pulse | Software Gate                                                                                                              | Software-controlled<br>ON bit, legacy<br>Timer2 operation | ON = 1                                        | Period match event | ON = 0                        |  |

|                | Hardware Gate,<br>Active-High                                                                                              | Hardware gate, active-high                                | Input signal = 1 and ON = 1 Period match even |                    | Input signal = 0<br>or ON = 0 |  |

|                | Hardware Gate,<br>Active-Low                                                                                               | Hardware gate, active-low                                 | Input signal = 0<br>and ON = 1                | Period match event | Input signal = 1<br>or ON = 0 |  |

|                | Rollover Pulse with HLT action (Edge-Triggered Hardware Limit mode and Level-Triggered Hardware Limit mode) <sup>(1)</sup> | Input either edge<br>Reset                                |                                               | Input edge         | <b>ON</b> = 0                 |  |

|                |                                                                                                                            | Input rising edge<br>Reset                                |                                               | Input rising edge  |                               |  |

|                |                                                                                                                            | Input falling edge<br>Reset                               | ON = 1                                        | Input falling edge |                               |  |

|                |                                                                                                                            | Input active-low Reset                                    |                                               | Input signal = 0   | ON = 0 or held in Reset by    |  |

|                |                                                                                                                            | Input active-high Reset                                   |                                               | Input signal = 1   | input signal                  |  |

Note 1: The modes that are highlighted in the table are the HLT modes.

TABLE 1: MODES OF OPERATION OF HLT WITH START, STOP AND RESET CONDITIONS

| Mode          |                                                                                                                                 | Operation                                          | Start                                | Reset                     | Stop                                                                   |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------|---------------------------|------------------------------------------------------------------------|--|

| One-Shot mode | One-Shot SW<br>Start                                                                                                            | Software-controlled ON bit                         | ON = 1                               | Period match event        |                                                                        |  |

|               | One-Shot<br>Edge-Triggered<br>Start                                                                                             | Input rising edge start                            | Input signal rising edge and ON = 1  |                           |                                                                        |  |

|               |                                                                                                                                 | Input falling edge start                           | Input signal falling edge and ON = 1 | Period match event        | ON = 0 or next<br>clock after                                          |  |

|               |                                                                                                                                 | Input either edge start                            | Input signal either edge and ON = 1  |                           |                                                                        |  |

|               | One-Shot<br>Edge-Triggered<br>Start with HLT<br>Action<br>(Edge-Triggered<br>Hardware Limit<br>One-Shot<br>mode) <sup>(1)</sup> | Input rising edge start and Reset                  | Input signal rising edge and ON = 1  | Input signal rising edge  | period match<br>until ON bit is<br>set by software                     |  |

|               |                                                                                                                                 | Input falling edge start and Reset                 | Input signal falling edge and ON = 1 | Input signal falling edge |                                                                        |  |

|               |                                                                                                                                 | Input rising edge<br>start and<br>active-low Reset | Input signal rising edge and ON = 1  | Input signal = 0          |                                                                        |  |

|               |                                                                                                                                 | Input falling edge start and active-high Reset     | Input signal falling edge and ON = 1 | Input signal = 1          |                                                                        |  |

|               | One-Shot<br>Level-Triggered<br>Start with HLT<br>Action (Level<br>Triggered<br>Hardware Limit<br>One-Shot<br>Mode)*             | Input high start<br>and active-low<br>Reset        | Input signal = 1<br>and ON = 1       | Input signal = 0          |                                                                        |  |

|               |                                                                                                                                 | Input low start and active-high Reset              | Input signal = 0<br>and ON = 1       | Input signal = 1          | ON = 0 or held<br>in Reset                                             |  |

| Monostable    | Edge-Triggered<br>Start                                                                                                         | Input either edge<br>Reset                         | Input signal rising edge and ON = 1  |                           | ON = 0 or next<br>clock after period<br>match until next<br>input edge |  |

|               |                                                                                                                                 | Input rising edge<br>Reset                         | Input signal rising edge and ON = 1  | Period match event        |                                                                        |  |

|               |                                                                                                                                 | Input falling edge<br>Reset                        | Input signal rising edge and ON = 1  |                           | mpat ougo                                                              |  |

Note 1: The modes that are highlighted in the table are the HLT modes.

The following sections will provide more details about the HLT modes of the Rollover Pulse mode and the One-Shot modes.

### Rollover Pulse Mode with Hardware Limit Timer

In the Rollover Pulse mode, the ON bit allows the user to start and stop the timer. The timer increments with each clock input with the ON bit set and stops incrementing when the ON bit is cleared. If the ON bit is set again, then the timer continues to increment from where it stopped. On a period match, the timer resets on the next clock and continues counting from '0'. The Rollover Pulse modes with the hardware limit feature are:

- Edge-Triggered Hardware Limit mode

- · Level-Triggered Hardware Limit mode

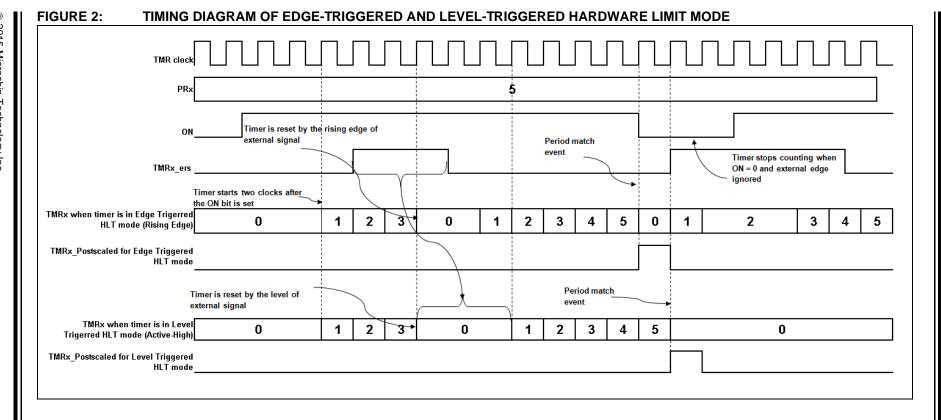

In Edge-Triggered Hardware Limit mode, setting the ON bit starts the timer. The external signal can reset the timer before the period match occurs.

The external edges for Reset can be:

- Reset on rising edge (MODE<4:0> = 00101)

- Reset on falling edge (MODE<4:0>= 00100)

- Rising or falling either edge can reset the counter (MODE<4:0> = 00011)

The external signal level can also be used to reset the timer. This level can be a high state or a low state (MODE<4:0> = 00010 or MODE<4:0> = 00001). The operation of the Edge-Triggered Hardware Limit mode and Level-Triggered Hardware Limit mode is illustrated in Figure 2.

- **Note 1:** The setting and clearing of the ON bit is executed by the CPU. CPU execution is asynchronous to the timer clock input.

- **2:** The timer events consume up to two clock cycles for starting and stopping.

#### TB3122

#### **One-Shot Mode**

Unlike in the Rollover Pulse mode, in One-Shot mode, the ON bit is cleared in hardware when the timer rolls over. Only one timer interrupt is generated and the timer stops counting. The ON bit must be set by software to start another timer cycle. This mode is useful when the user desires to time a single event rather than a periodic event. The One-Shot modes with the hardware limit feature are:

- Edge-Triggered Hardware Limit One-Shot mode

- · Level-Triggered Hardware Limit One-Shot mode

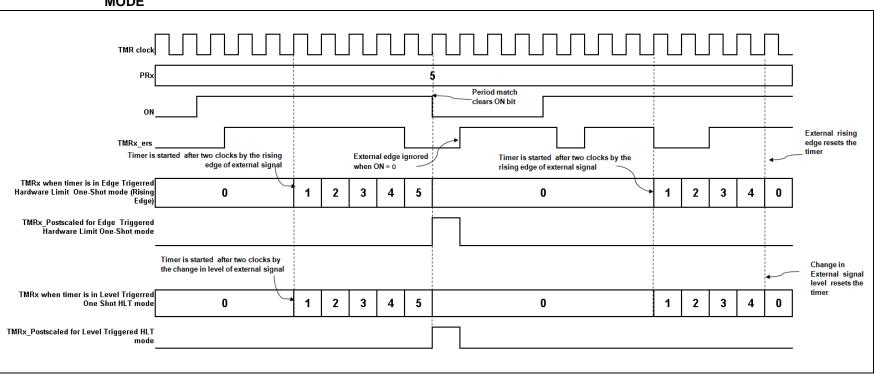

Edge-Triggered Hardware Limit One-Shot mode features not only an edge-triggered start but it also resets the timer on subsequent edges of the external signal (i.e., once the ON bit is set, the occurrence of the first edge of the external signal will start the timer). The timer runs until another edge of the external signal or until a period match occurs. The timer will automatically resume counting after the subsequent Reset edge and it will run until the period match occurs. There are two ways that this mode can be achieved:

- Rising Edge Start and Reset (MODE<4:0> = 01100)

- Falling Edge Start and Reset (MODE<4:0> = 01101)

In Level-Triggered Hardware Limit One-Shot mode, the level of the external signal starts and resets the timer. This level can be configured to either a high state or a low state (MODE<4:0> = 011110 or MODE<4:0> = 01111). The timer does not start until the ON bit is set and the external signal occurs. The timer keeps running until the external signal is at the same level. Once the level of the external signal changes its state, the timer is reset. Reset levels can either be high or low. The operation of the Edge-Triggered One-Shot Hardware Limit mode and Level-Triggered One-Shot Hardware Limit mode are illustrated in Figure 3.

FIGURE 3: TIMING DIAGRAM OF EDGE-TRIGGERED HARDWARE LIMIT AND LEVEL-TRIGGERED HARDWARE LIMIT ONE-SHOT MODE

#### **Monostable Mode**

In this mode, the timer stops after a rollover but it does not clear the ON bit. An external signal edge is again required to start the timer. The timer stops either on clearing the ON bit or on the period match event. The following edges will start the timer:

- Rising Edge (MODE<4:0> = 10001)

- Falling Edge (MODE<4:0> = 10010)

- Rising or Falling Edge (MODE<4:0> = 10011)

### CONFIGURATION OF TIMER2 WITH THE HARDWARE LIMIT FEATURE

Table 2 contains the summary of registers associated with the Hardware Limit Timer.

TABLE 2: REGISTERS ASSOCIATED WITH TIMER2 WITH THE HARDWARE LIMIT FEATURE

| Name     | Bit 7 | Bit 6     | Bit 5  | Bit 4 | Bit 3      | Bit 2     | Bit 1 | Bit 0 |

|----------|-------|-----------|--------|-------|------------|-----------|-------|-------|

| TxCLKCON | _     | _         | _      | _     | _          | TxCS<2:0> |       |       |

| TxCON    | ON    | CKPS<2:0> |        |       | OUTPS<3:0> |           |       |       |

| TxRST    | _     | _         | _      | _     | RSEL<3:0>  |           |       |       |

| TxHLT    | PSYNC | CKPOL     | CKSYNC | _     | MODE<3:0>  |           |       |       |

The TxCS bits of the TxCLKCON register are used for the clock selection. The external signal source selection is done in the TxRST register. Prescaler and postscaler settings are done in the TxCON register. Example 1 shows the code snippet used to configure Timer2 registers to operate in Edge-Triggered Rollover Pulse Hardware Limit mode.

### EXAMPLE 1: CODE SNIPPET FOR CONFIGURATION OF TIMER2 IN EDGE-TRIGGERED HARDWARE LIMIT MODE

```

T2CLKCONbits.T2CS = 0b0000; //Clock input is Fosc/4

T2CONbits.CKPS = 0b111; //Prescaler setting 1:128

T2CONbits.OUTPS = 0b1111; //Postscaler setting 1:16

T2RSTbits.RSEL = 0b0000; //Selecting Timer2 input as external source

T2HLTbits.PSYNC = 1; //Prescaler synchronization bit

T2HLTbits.CKPOL = 0; //Rising edge of input clock clocks timer

T2HLTbits.CKSYNC = 1; //ON bit synchronized to input clock

T2HLTbits.MODE = 0b01100; //Edge triggered hardware limit mode -rising edge

T2CONbits.ON = 1; //Timer is switched on

```

# USING THE MPLAB® CODE CONFIGURATOR FOR CODE GENERATION OF THE HLT

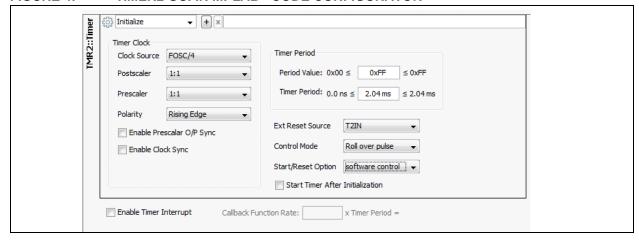

The MPLAB<sup>®</sup> Code Configurator, which is a plug-in tool for MPLAB<sup>®</sup> X IDE, generates the drivers for controlling and driving the HLT based on the settings and selections made in the GUI.

The clock source selection, prescaler and postscaler settings can be done to meet the time period requirements desired by the user. External source selection and mode of operation can be picked from the drop-down selection provided by the GUI (see Figure 4). For further details refer to the "MPLAB® Code Configurator User's Guide" (DS40001725).

#### FIGURE 4: TIMER2 GUI IN MPLAB® CODE CONFIGURATOR

#### **API List for the HLT**

The following API is generated by MCC for the HLT module:

- void TMR2\_Initialize(void): This API initializes the TxCON, TxCLKCON, TxHLT, TxRST, TxPR, TxTMR and interrupt flags, and it starts the timer.

- void TMR2\_ModeSet(TMR2\_HLT\_MODE mode):

This API configures different types of HLT modes.

- void TMR2\_ExtResetSourceSet (TMR2\_HLT\_EXT\_RESET\_SOURCE reset): This API configures different types of HLT external Reset source.

- void TMR2\_Start(void): This API starts the timer by writing to the TMRxON bit.

- void TMR2\_Stop(void): This API stops the timer by clearing the TMRxON bit.

- uint8\_t TMR2\_Counter8BitGet(void): This API is used to get the TxTMR register value.

- void TMR2\_Counter8BitSet(uint8\_t timerVal): This API writes to the Timer register.

- void TMR2\_Period8BitSet(uint8\_t periodVal): This API is used to set the Period register to a particular value.

- void TMR2\_Period8BitSet(uint8\_t periodVal): This API is used to check if overflow has occurred, which is done by checking the TMRIF bit.

#### CONCLUSION

This technical brief describes how the Hardware Limit Timer module works on PIC microcontrollers. It familiarizes the reader with the hardware limit features of the Rollover Pulse modes and One-Shot modes. As explained in this technical brief, the timer in its suitable mode can be used for Fault detection in motors and in variable frequency PWM for power supply. More details can be found in each product specific data sheet.

## APPENDIX A: APPLICATIONS OF THE HARDWARE LIMIT TIMER

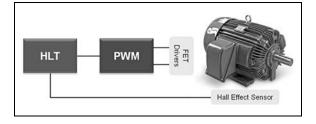

### A.1 Fault Detection in a Motor Using the HLT

The HLT in Edge-Triggered Hardware Limit Timer mode can be used in Fault detection of a cooling fan motor (Figure A-1). The RPM sensor or tachometer output of the fan is used as an external signal to the HLT. The Period register of the timer is set to a value that is sufficiently larger than the RPM count of the fan or more than the frequency of the fan tachometer output. Under normal conditions, when the fan is spinning, it gives periodic tachometer pulses. These pulses reset the timer before the period match occurs and the timer starts counting again. In the case of a Fault condition in the fan (i.e., the fan has stalled), it stops giving tachometer pulses. In this scenario, the timer continues to increment until the period match occurs. This event generates an interrupt and this interrupt can be registered to indicate that the fan is not spinning and that there is a Fault.

### FIGURE A-1: FAULT DETECTION IN A MOTOR

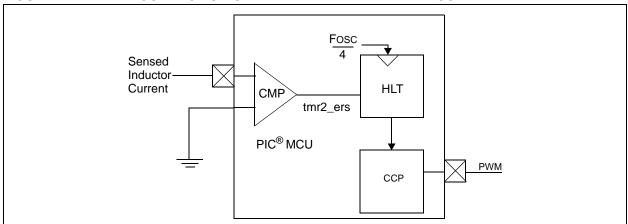

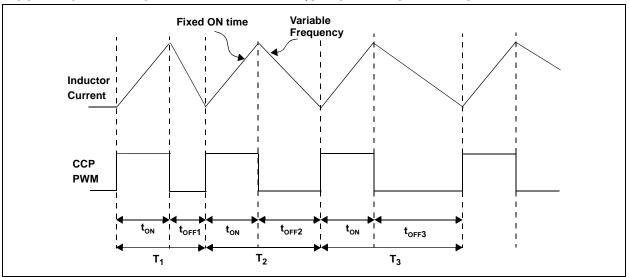

### A.2 Fixed ON Time Variable Frequency PWM Generation Using the HLT

Monostable Edge-Triggered Start mode can be used in a DC-DC converter application that is operating in Critical Conduction mode, with soft switching. By detecting the zero inductor current (used as external signal to the timer), HLT can be started for a fixed ON time. The Period register can be set to a value that is sufficiently large value, more than the maximum ON time. When HLT is used along with CCP for PWM generation, the output pulse remains active until a match of the CCP Duty register with the Timer register occurs (Figure A-2). The next pulse begins only at the next external edge, which is the ZCD event of the inductor current. This is an example of a fixed ON time variable frequency PWM generation (Figure A-3).

FIGURE A-2: INTERCONNECTION OF THE TIMER2 WITH HLT AND CCP

FIGURE A-3: FIXED ON TIME VARIABLE FREQUENCY PWM GENERATION

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, flexPWR, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC<sup>32</sup> logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

The Embedded Control Solutions Company and mTouch are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, ECAN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, KleerNet, KleerNet logo, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, RightTouch logo, REAL ICE, SQI, Serial Quad I/O, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2015, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-63276-983-1

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELoQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### **Worldwide Sales and Service**

#### **AMERICAS**

**Corporate Office** 2355 West Chandler Blvd.

Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277

Technical Support: http://www.microchip.com/

support

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX

Tel: 512-257-3370

**Boston** Westborough, MA Tel: 774-760-0087

Fax: 774-760-0088 Chicago

Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi. MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis

Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles

Mission Vieio, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

Canada - Toronto Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong

Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongging Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Hangzhou

Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR

Tel: 852-2943-5100 Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-3019-1500

Japan - Osaka

Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

Japan - Tokyo

Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7830

Taiwan - Taipei Tel: 886-2-2508-8600

Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351

Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Dusseldorf**

Tel: 49-2129-3766400

**Germany - Munich**

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Germany - Pforzheim** Tel: 49-7231-424750

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice

Tel: 39-049-7625286

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw

Tel: 48-22-3325737

Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm

Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800

Fax: 44-118-921-5820

03/25/14