# AN1829 Application Note Power Diode Datasheet Notation

Final May 2018

## **Contents**

| 1            | Revision History           |                                        | 1 |

|--------------|----------------------------|----------------------------------------|---|

|              | 1.1 Revi                   | sion B                                 | 1 |

|              | 1.2 Revi                   | sion A                                 | 1 |

|              |                            | ode Datasheet Notation                 |   |

|              | 2.1 Nom                    | enclature                              | 2 |

|              | 2.2 Tabular Specifications |                                        | 2 |

|              | 2.2.1                      | Absolute Maximum Ratings               | 2 |

|              | 2.2.2                      | Electrical Performance                 | 3 |

|              | 2.2.3                      | Dynamic Characteristics                | 4 |

|              | 2.2.4                      | Thermal and Mechanical Characteristics | 5 |

|              | 2.2.5                      | Typical Performance Curves             | 5 |

| 3 References |                            | 9                                      |   |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

## 1.1 Revision B

Revision B was published in May 2018. The following is a summary of the changes in revision B of this document:

- Added sections for silicon carbide Schottky barrier diodes and ultrafast recovery DQ diodes.

- Document updated from AN301.

## 1.2 Revision A

Revision A (AN301) was published in February 2003. It was the first publication of this document.

## 2 Power Diode Datasheet Notation

This application note is a description of notation on Microsemi DPG power diodes. It supersedes AN301 with the introduction of silicon carbide Schottky barrier diodes and ultrafast recovery DQ diodes. It is applicable to diodes with the "MSC" prefix and all "D" and "DQ" diodes starting in 2017. The ordering of this document follows the order of specifications in device datasheets.

## 2.1 Nomenclature

Lowercase letters will be used for instantaneous values of signals. Uppercase letters will be used for limits, averages, and DC values. Consequently,  $i_R$  is the instantaneous value of the diode reverse current, whereas  $I_R$  is the specified DC reverse current under certain conditions of reverse voltage ( $V_R$ ) and case temperature ( $T_C$ ). In datasheets, this distinction is sometimes not made. An example of using a capital letter two different ways is found in datasheet sections dealing with maximum DC reverse voltage ( $V_R$ ) and junction capacitance ( $C_T$ ). The voltage at which the junction capacitance ( $C_T$ ) is measured is 200 V. That voltage is called  $V_R$  to designate it as the applied DC reverse voltage. It is therefore left to the reader to discern from the context whether  $V_R$  is the maximum DC reverse voltage or the applied DC reverse voltage.

## 2.2 Tabular Specifications

This section explains the notations for tabular specifications in power diode datasheets.

## 2.2.1 Absolute Maximum Ratings

The three voltage ratings discussed below—V<sub>R</sub>, V<sub>RRM</sub>, and V<sub>RWM</sub>—describe the maximum voltage to be applied to a diode as steady state and various transient conditions. They may differ with diodes that are highly leaky or have other special conditions. Examples of this are silicon Schottky barrier diodes, selenium diodes, and vacuum tube diodes. With most modern diodes there is one limit regardless of the timing. It is customary to provide the three values, but there are very few instances with modern diodes where they will differ.

## V<sub>R</sub>, Maximum DC Reverse Voltage

$V_R$  is the maximum allowable DC reverse voltage that may be applied to the diode. Industry practice is that this is a 25 °C limit unless stated otherwise. Expect a significantly lower breakdown at low temperatures with silicon and silicon carbide diodes. At -50 °C there can be a 10% reduction in breakdown voltage.

## **VRRM, Maximum Peak Repetitive Reverse Voltage**

$V_{RRM}$  is the maximum allowable repetitive reverse voltage. There is no standard definition for this term. The specifics describing this limit must be specified in the datasheet if it differs from  $V_R$ .

## VRWM, Maximum Working Peak Reverse Voltage

$V_{RRM}$  is the maximum allowable non-repetitive reverse voltage. There is no standard definition for this term. The specifics describing this limit must be specified in the datasheet if it differs from  $V_R$ .

## IF(AV), Maximum Average Forward Current

$I_{\text{F(AV)}}$  is the maximum allowable average forward current with the case temperature at the specified value. It is a figure arrived at using the derated maximum  $R_{\text{BIC}}$ , the forward characteristics of the diode, and the maximum allowable junction temperature. It is sometimes derived assuming a 50% conduction cycle or other special conditions. Diodes are often used with peak currents above this value. It is a good number to start with when selecting diodes, but ultimately the current and voltage across the diode, the cooling, and the switching losses all weigh into calculating diode performance. It is not an instantaneous operating limit like voltage limits.

#### IF(RMS), RMS Forward Current

$I_{F(RMS)}$  expresses a physical limit of the bond wires. This is because the heating of the wire is proportional to the square of the current.

#### **IFRM, Repetitive Forward Surge Current**

IFRM is the maximum allowable repetitive half-sine wave surge current under the specified condition. The devices are slowly (>1 second) repetitively stressed for 1000 to 10000 cycles. It is then verified that there is no degradation of any device electrical or mechanical parameters. The test current chosen is based upon the package transient thermal impedance while keeping the junction temperature under the maximum rated value.

#### **IFSM, Non-Repetitive Forward Surge Current**

IFSM is the maximum allowable non-repetitive half-sine wave surge current under the specified condition, usually at 25 °C. This is tested under the specified conditions by raising the current to failure. Multiple devices are tested. The average figure arrived at is then significantly de-rated from the failure point. Note that the rating is not based upon the package transient thermal impedance. The junction temperature is allowed to exceed the maximum junction temperature rating of the package.

#### EAVL, Avalanche Energy Rating

This expresses the avalanche energy that can be absorbed at the given condition. This is not normally tested in production unless explicitly stated. Like IFSM, this specification does not assume the junction temperature will stay within the package rating.

#### Ptot, Power Dissipation

This expresses the maximum power dissipation of the device. Like  $I_{F(AV)}$ , this is a figure derived from  $R_{\Theta/C}$ . Ultimately, the method of cooling sets the maximum power dissipation and this figure is only useful initially when selecting devices.

## TJ, TSTG, Operating and Storage Temperature Range

$T_{\rm J}$  is the allowable range of operating junction temperatures, typically –55 °C to 150 °C or to 175 °C with SiC. In like manner,  $T_{\rm STG}$  is the range of allowable storage temperatures. As shown in the various diode datasheets, both ranges are usually the same. Operation or storage outside this range is not recommended. Exceeding these temperatures can result in various forms of latent damage.

## T<sub>L</sub>, Lead Temperature for 10 Seconds

$T_L$  is the maximum allowable lead temperature when soldering for a duration of 10 seconds. This typically assumes a distance of 0.063 inches from the case.

## 2.2.2 Electrical Performance

Whereas the ratings presented in the previous section are maximum ratings, the following ratings are presented as typical or maximum, depending on the parameter or conditions. Note that these are static or DC ratings for the particular conditions stated in the datasheet.

#### V<sub>F</sub>, Forward Voltage

$V_F$  is the diode's forward voltage under the specified current and temperature condition. There will be a typical and maximum value at 25 °C. There may also be a typical value at various elevated temperatures. The maximum value is the test limit applied in production. The actual production limit is below the specified  $V_F$ .

#### **IRM, Maximum Reverse Leakage Current**

IRM is the specified maximum reverse leakage current at the given voltage, typically the maximum voltage, VR. Microsemi specifies a maximum leakage current at elevated temperatures with some devices. This is a limit by design based on the 25 °C leakage. Diode leakages are highly temperature dependent and highly dependent upon the margin between the actual voltage and the individual breakdown voltage. If leakage is of concern, a higher voltage diode or better cooling should be considered. The actual production limit is below the specified limit.

## C<sub>J</sub>, Junction Capacitance

$C_{\rm J}$  is the junction small signal capacitance of the diode at a specified reverse voltage. Normally,  $C_{\rm J}$  is a monotonically decreasing function of  $V_{\rm R}$ , as can be seen in the diode datasheet figure entitled "Junction Capacitance vs. Reverse Voltage." With SiC diodes at high voltages, the capacitance will become constant, independent of voltage.

#### Ls, Series Inductance

L<sub>S</sub> is the series inductance measured from one lead to another lead. The measurement is performed at a distance of 5 mm from the case on each lead with through-hole packages.

## 2.2.3 Dynamic Characteristics

All of the parameters described in this section are concerned with forward or reverse recovery of the diode. This is associated with minority carrier conduction and is not applicable to silicon carbide Schottky barrier diodes.

Microsemi tests diode recovery using methods described in JEDEC No 24-7 and JEDEC No 24-10. A method described by Catt [1] [2] is used with faster diodes and silicon carbide SBDs.

The JEDEC standard is a baseline applicable in lower stress applications. The recovery process is dependent upon the following:

- The current leading into the switching event

- The rate of change of the current leading into the switching event

- The blocking voltage

- The temperature of the device

In higher stress applications, the charge recovery process is also dependent upon the blocking voltage in relation to the actual breakdown voltage of the device.

High-stress applications introduce additional dynamic avalanche charge into the recovery process. Dynamic avalanche is a highly nonlinear phenomenon. This application note is limited to the classical recovery notation. Reference Application Note AN1830 for further information on recovery under high-stress conditions.

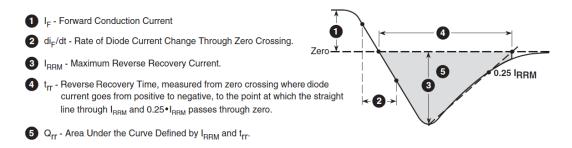

## trr, Reverse Recovery Time

Reference Figure 3 (see page 8) at the end of this document. The reverse recovery time (t<sub>rr</sub>) is an approximation of the time it takes for the reverse current to decay. In fact, the current tail on a conventional diode is closely approximated by an exponential decay and has no defined end.

To work around this, the JEDEC standard describes a method by which the time is approximated using a graphical technique. The details are beyond the scope of this application note. It should be remembered that it is an approximation and is not applicable under higher stress conditions.

## **Qrr, Reverse Recovery Charge**

Reference Figure 3 (see page 8) at the end of this document.  $Q_{rr}$  is the area under the reverse current curve measured from the zero crossing to the point at which  $t_{rr}$  is extrapolated off of the reverse recovery current curve.

## IRRM, Maximum Reverse Recovery Current

Reference Figure 3 (see page 8) at the end of this document. The maximum reverse recovery current specification (IRRM) is simply the peak current observed during the recovery process. It should be mentioned that there are two components to this. There is a capacitive component associated with the majority charge and a minority carrier component. The minority carrier component is dominant in most applications with conventional "D" and "DQ" diodes.

#### 2.2.4 Thermal and Mechanical Characteristics

The following parameters are thermal and mechanical—not electrical. Some are maximum, some are typical.

#### Resc, Junction-to-Case Thermal Resistance

Resc is the resistance to heat flow as measured from the diode's junction to the base plate of the diode's case. The units are degrees Celsius per watt. The junction temperature is measured using the diode forward voltage versus temperature dependence (the k factor). The case temperature is measured by placing a thermal couple under a device that is mounted to a large copper block just under the device.

This method is the standard industry practice. However, it is a poor method to use with a very small die—such as with SiC diodes. This is because with a high thermal conductivity interface, the heat flux is concentrated under the die. In that case, the addition of a thermal interface material adds more thermal resistance than would be expected using the area of the backside metal of the package.

Microsemi is developing a method to aid in calculating the actual thermal resistance. If this is of concern, please make a request to Microsemi for thermal modeling data through the web interface.

## Reja, Junction-to-Ambient Thermal Resistance

$R_{\theta JA}$  is the resistance to heat flow as measured from the diode's junction to the ambient with no heat sink between the case and the ambient. This is based on assumptions that may be stated, such as mounting a given distance from a PCB. The devices covered by this note are not normally operated without a heat sink and generally will not have this specification. See the discussion of  $R_{\theta JC}$  (see page 5). The same principles apply to  $R_{\theta JA}$ .

## W<sub>T</sub>, Package Weight

W<sub>T</sub> is the package weight expressed in ounces and grams.

#### **Torque, Maximum Mounting Torque**

Torque is the maximum allowable mounting torque to be applied to the mounting screw(s) for the given package. The units are lb·in and N·m.

## 2.2.5 Typical Performance Curves

The following are descriptions of the common figure types used in datasheets.

## Maximum Effective Transient Thermal Impedance, Junction-to-Case vs. Pulse Duration

The graph "Maximum Effective Transient Thermal Impedance, Junction-to-Case vs. Pulse Duration" is based on measured device data.

Often these curves are reduced to one-dimensional models. The one-dimensional thermal impedance for a device is then represented as a parallel combination of resistors (the Cauer model), or a series combination (the Foster model). This introduces model components  $R_{\theta}$  and  $C_{\theta}$ .

In a circuit simulator,  $R_{\theta}$  (thermal resistance) is modeled as resistance (ohms),  $C_{\theta}$  (thermal capacity) is modeled as capacitance (farads), P (power) is modeled as current (amps), and  $\Delta T$  is treated as voltage (volts). Current is interpreted as watts, and every node voltage is interpreted as temperature (°C) referenced to the ground node, which is the case temperature. Whatever voltage is measured at one of the nodes other than the ground node is a temperature of that value above the case temperature.

One-dimensional models work best when the device die is relatively large relative to the copper header underneath it. This is because the heat mostly flows from the die straight down into the heat sink. If there is a thermal interface material under the device, the heat flows in the same manner. Hence, the thermal resistances can be added.

Silicon carbide dies tend to be very small relative to the device header. When the device is mounted on a copper block, heat flows both sideways and down to the heat sink. The effect of confined heat flux is that the heat sink underneath will have a higher thermal resistance than would be expected if the heat flux were across the whole back area of the package.

On the other hand, if there is a thermal interface material that adds thermal resistance between the device and the package, then the heat tends to flow sideways (spreads) before passing through the thermal interface material. The  $R_\theta$  in effect from junction to case is lower than with a direct connection to a heat sink and lower than the value in a datasheet.

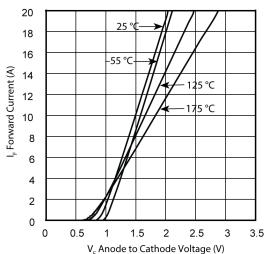

## Forward Current vs. Forward Voltage

The curves in Figure 1 (see page 6) represent the conduction transfer characteristic of the diode. With all diodes, as the temperature increases the intrinsic forward voltage decreases (assuming a constant current). With silicon carbide SBDs and some high-voltage silicon diodes at higher currents, the voltage increases with the temperature. With all diodes, there is also a series resistive component. The resistance increases with temperature. For this reason, silicon carbide SBDs can be paralleled relatively easily; but silicon conventional diodes, which are dominated by the negative temperature coefficient region, are harder to parallel without current hogging.

The following graph is from SiC MSC010SDA070K. Note how the graphs cross at higher currents. This is an example of an SBD that can share current because at the higher currents, the forward voltage increases as the device heats.

Figure 1 ● MSC010SDA070K Forward Current vs. Forward Voltage

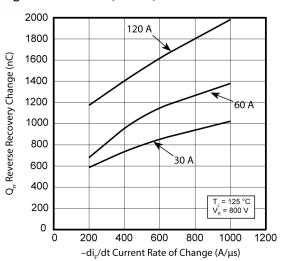

#### **Qrr vs. Current Rate of Change**

The "Qrr vs. Current Rate of Change" graph shows how the reverse recovery charge varies as a function of dif/dt leading into the reverse conduction phase—not applicable to SiC SBDs. For all conventional diodes, as dif/dt increases for a given  $I_F$ , the reverse recovery charge ( $Q_{rr}$ ) also increases. The same figure also shows that for a given  $di_F/dt$ , as the forward current ( $I_F$ ) increases, the reverse recovery charge increases.

The graph below is a typical graph of  $Q_{rr}$  versus  $d_1/dt$ . Note that the recovery charge can roughly be estimated as having two components: one is a constant, the other is proportional to the current multiplied by  $d_1/dt$ . The graph also indicates that the device can be used at 1000 A/ $\mu$ S safely at 400 V on a 600 V part in this case. It should not be assumed that this device can be safely used above 1000 A/ $\mu$ S, especially when operating close to the diode voltage rating. At higher rates ( $d_1/dt$ ), the curves will curve up significantly due to dynamic avalanche. In high-stress applications, the diode should be evaluated in a double-pulse test to judge its suitability for an application.

Figure 2 • APT60DQ60SG Qrr vs. Current Rate of Change

## IRRM vs. Current Rate of Change

The "I<sub>RRM</sub> vs. Current Rate of Change" graph shows how the reverse recovery current peak varies as a function of di<sub>F</sub>/dt—not applicable to SiC SBDs. As di<sub>F</sub>/dt increases for a given IF the reverse recovery current peak (I<sub>RRM</sub>) also increases. The same figure also shows that for a given di<sub>F</sub>/dt, as the forward current (I<sub>F</sub>) increases, the reverse recovery current peak increases.

## **Dynamic Parameters vs. Junction Temperature**

The "Dynamic Parameters vs. Junction Temperature" graph shows how trr, Qrr, and IRRM vary with temperature—not applicable to SiC SBDs. All three increase as the junction temperature increases. These parameters are typically highly temperature dependent.

#### trr vs. Current Rate of Change

The " $t_{rr}$  vs. Current Rate of Change" graph shows how the reverse recovery time varies as a function of di f/dt—not applicable to SiC SBDs. With all conventional diodes, as dif/dt increases,  $t_{rr}$  decreases. Also in the same figure, for a given dif/dt, as the forward current (If) increases,  $t_{rr}$  increases.

## Junction Capacitance vs. Reverse Voltage

The "Junction Capacitance vs. Reverse Voltage" graph shows how the junction capacitance varies as a function of reverse voltage V<sub>R</sub>. The capital "V" is used here because the voltage in view is DC. In all conventional diodes, as V<sub>R</sub> increases, C<sub>J</sub> decreases. The exception is silicon carbide SBDs, which can have a flat plateau at high voltage.

## **Maximum Average Forward Current vs. Case Temperature**

The "Maximum Average Forward Current vs. Case Temperature" graph indicates the maximum current allowable with the given case temperature. This is based on the thermal resistance internal to the device and the forward voltage characteristic of the device at temperature. Note that this is normally either a continuous or 50% pulsed rating. With most applications, the diode current is pulsed and it is allowed to exceed the value presented by the graph as long as the maximum junction temperature is observed.

## **Diode Reverse Recovery Waveform and Definitions**

The figure below is from the JEDEC standard. It represents diode recovery in low-stress applications. Real applications have ringing. At higher voltages and dl/dt, a second pulse will form due to dynamic avalanche. Refer to Application Note AN1830 for more information on high-stress diode recovery.

Figure 3 • Diode Reverse Recovery Waveform

## **Package Outlines**

Depending on the datasheet, there will be one or two drawings showing the outlines of the package(s) covered by the datasheet, along with dimensions of the package and pins.

# 3 References

- 1. Jamie Catt, "An Improved Method for Ultrafast Recovery Diode Testing" in *Applied Electronics Conference and Exposition* (APEC), 1994, Ninth Annual, IEEE.

- 2. Juergen Stahl, Daniel Kuebrich, Thomas Duerbaum, Christian Oeder, "Fully Automated Measurement Set-up for Ultrafast Recovery Diode Testing" in *Applied Electronics Conference and Exposition* (APEC), 2011 Twenty-Sixth Annual, IEEE.

#### Microsemi Corporate Headquarters

One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

© 2018 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or prameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided is, where is' and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

AN1829