# How to Use the 12-Bit Differential ADC with PGA in Series Accumulation Mode

#### **Features**

- 12-Bit Resolution

- Sample Accumulation up to 1024 Samples

- · Differential and Single-Ended Conversion

- Up to 15 analog inputs

- 15 positive and seven negative inputs

- 4 Internal Inputs

- GND

- $-V_{DD}/10$

- Temperature Sensor

- DACREF from Analog Comparator

- Built-in Internal Reference and External Reference Options

- · Programmable Gain Amplifier from 1x to 16x

- · Left or Right Adjusted Result

- Optional: Event-Triggered Conversion

- · Configurable Window Comparator

### Introduction

Authors: Amund Aune, Egil Rotevatn, and Rupali Honrao, Microchip Technology Inc.

This technical brief explains how to use the Series mode with the 12-bit Analog-to-Digital Converter (ADC) featured in the tinyAVR® 2 family.

The code examples below are given using the Series mode:

- Interrupt using Window Comparator

- · Event-triggered series conversion

- · ADC oversampling to increase resolution

- · Series Accumulation with Scaling to increase ADC resolution

In Series mode, one conversion is performed per ADC trigger and a selectable number of samples are automatically accumulated into a single ADC result. A maximum of 1024 samples can be accumulated.

The ADC operation modes can be split into three groups:

- Single mode Single conversion per trigger, with 8- or 12-bit conversion output

- Series Accumulation mode One conversion per trigger, with accumulation of n samples

- Burst Accumulation mode A burst with n samples accumulated as fast as possible after a single trigger

Refer to Section 1. Relevant Documents for details on the other ADC modes.

© 2020 Microchip Technology Inc.

Technical Brief

DS90003257A-page 1

# **Table of Contents**

| Fea  | atures.           |                                     | 1  |  |  |

|------|-------------------|-------------------------------------|----|--|--|

| Intr | oducti            | ion                                 | 1  |  |  |

| 1.   | Rele              | vant Documents                      | 3  |  |  |

| 2.   | Configuration     |                                     |    |  |  |

|      | 2.1.              | Series Mode Configuration           |    |  |  |

|      | 2.2.              | References                          |    |  |  |

|      | 2.3.              | Single-Ended and Differential Modes | 4  |  |  |

|      | 2.4.              | Programmable Gain Amplifier         |    |  |  |

|      | 2.5.              | Interrupts                          | 5  |  |  |

|      | 2.6.              | Window Comparator                   | 6  |  |  |

|      | 2.7.              | Events                              | 7  |  |  |

| 3.   | Input             | t Circuitry                         | 11 |  |  |

|      | 3.1.              | Input Impedance                     | 11 |  |  |

|      | 3.2.              | Sample Duration                     | 12 |  |  |

| 4.   | Power and Timing  |                                     |    |  |  |

|      | 4.1.              | Clock                               | 13 |  |  |

|      | 4.2.              | PGA Bias and Output Sample Duration |    |  |  |

|      | 4.3.              | Conversion Time                     | 13 |  |  |

| 5.   | Output Processing |                                     |    |  |  |

|      | 5.1.              | Result Range                        | 15 |  |  |

|      | 5.2.              | Accumulation                        | 15 |  |  |

|      | 5.3.              | Left Adjust                         | 17 |  |  |

|      | 5.4.              | Signed and Unsigned Output          | 18 |  |  |

| 6.   | Get (             | Code Examples from GitHub           | 20 |  |  |

| 7.   | Revi              | sion History                        | 21 |  |  |

| The  | e Micro           | ochip Website                       | 22 |  |  |

| Pro  | oduct (           | Change Notification Service         | 22 |  |  |

| Cu   | stome             | r Support                           | 22 |  |  |

| Mic  | crochip           | Devices Code Protection Feature     | 22 |  |  |

| Lec  | gal No            | tice                                | 22 |  |  |

|      |                   | rks                                 |    |  |  |

|      |                   | Management System                   |    |  |  |

|      | •                 | le Sales and Service                |    |  |  |

|      | . 14 77 14        |                                     | ∠¬ |  |  |

# 1. Relevant Documents

The following documents are relevant to this technical brief:

- Datasheet: tinyAVR 2 Data Sheet (.pdf) on Product Pages:

- www.microchip.com/wwwproducts/en/ATtiny1624

- www.microchip.com/wwwproducts/en/ATtiny1626

- www.microchip.com/wwwproducts/en/ATtiny1627

- How to use the 12-Bit Differential ADC with PGA in Single Mode: www.microchip.com/DS90003256

- How to use the 12-Bit Differential ADC with PGA in Burst Accumulation Mode: www.microchip.com/DS90003254

Configuration

# 2. Configuration

## 2.1 Series Mode Configuration

There are two available Series modes: Series Accumulation and Series Accumulation with Scaling. In both modes, the ADC requires one trigger per conversion, where the Sample (ADCn.SAMPLE) register is updated with each conversion result. The samples are automatically accumulated and placed in the Result (ADCn.RESULT) register when the last conversion in the series is finished. In Series Accumulation mode, the accumulated result is presented as-is, while in Series Accumulation with Scaling, the result is scaled to ease output processing as shown in Section 5.2.2 Series Accumulation with Scaling.

The two modes can be selected by writing the MODE bits in the ADCn.COMMAND register. Below are code examples showing the configuration of the Series modes.

```

/* Series Accumulation mode */

ADC0.COMMAND = ADC_MODE_SERIES_gc;

/* Series Accumulation with Scaling mode */

ADC0.COMMAND = ADC_MODE_SERIES_SCALING_gc;

```

#### 2.2 References

- · External Reference

- Internal Reference

- 1.024V

- 2.048V

- 2.500V

- 4.096V

- $-V_{DD}$

The reference voltage for the ADC (V<sub>REF</sub>) controls the conversion range of the ADC. External reference and five internal references are available.

```

ADCO.CTRLC = ADC_REFSEL_1024MV_gc; /* Reference selection 1.024V */

```

Except for  $V_{DD}$ , the internal reference voltages are generated from an internal band gap reference.  $V_{DD}$  must be at least 0.5V higher than the selected band gap reference voltage.

Changing the reference while a conversion is ongoing will corrupt the output.

# 2.3 Single-Ended and Differential Modes

In Single-Ended mode, the ADC reads the voltage of a single selectable input source, while in Differential mode, the ADC reads the voltage difference between two input sources.

The Differential mode is configured by writing '1' to the DIFF bit as shown below.

```

/* Differential Mode Configuration */

ADCO.COMMAND |= ADC_DIFF_bm;

```

The Single-Ended mode is configured by writing '0' to DIFF bit as shown below.

```

/* Single-Ended Mode Configuration */

ADCO.COMMAND &= ~ADC_DIFF_bm;

```

### 2.4 Programmable Gain Amplifier

The Programmable Gain Amplifier (PGA) can be used to amplify the input signal to the ADC. The available range is from 1x to 16x gain. The PGA is enabled by writing a '1' to the PGA Enable (PGAEN) bit and configuring the GAIN bit field in the PGA Control (ADCn.PGACTRL) register.

```

ADCO.PGACTRL |= ADC_GAIN_16X_gc | ADC_PGAEN_bm; /* Enable the PGA with 16x gain */

```

**Note:** PGA Control is one of few AVR registers with a nonzero reset value. This must be taken into account if only configuring parts of the register.

When PGA is enabled, the configuration of the VIA bit fields in the Positive and Negative Multiplexer (ADCn.MUXPOS and ADCn.MUXNEG) registers is required. The VIA bits are shared, so a value written to the VIA bit field in MUXPOS or MUXNEG is updated in both registers. It is, therefore, not possible to have one input using the PGA and the other not using the PGA.

```

ADCO.MUXPOS |= ADC VIA gm; /* Enable VIA */

```

### 2.5 Interrupts

The ADC features three separate interrupt vectors. When one of the interrupt conditions occurs, an interrupt flag is set, and the CPU is notified and pointed to the corresponding Interrupt Service Routine (ISR). The following table shows the available interrupt vectors for the ADC.

Table 2-1. Available Interrupt Vectors and Sources

| Name    | Vector Description     | Interrupt Flag | Conditions                                                                  |

|---------|------------------------|----------------|-----------------------------------------------------------------------------|

|         | Error interrupt        | TRIGOVR        | A new conversion is triggered while one is ongoing                          |

| ERROR   |                        | SAMPOVR        | A new conversion overwrites an unread sample in ADCn.SAMPLE                 |

|         |                        | RESOVR         | A new conversion or accumulation overwrites an unread result in ADCn.RESULT |

| SAMPRDY | Sample Ready interrupt | SAMPRDY        | The sample is available in ADCn.SAMPLE                                      |

| SAMPRUT |                        | WCMP           | As defined by WINSRC and WINCM in ADCn.CTRLD                                |

| RESRDY  | Result Ready interrupt | RESRDY         | The result is available in ADCn.RESULT                                      |

| NEGRUT  | Nesult Neady Interrupt | WCMP           | As defined by WINSRC and WINCM in ADCn.CTRLD                                |

An interrupt source is enabled or disabled by writing to the corresponding bit in the Interrupt Control (ADCn.INTCTRL) register as shown in the code snippet below.

```

ADCO.INTCTRL = ADC_RESRDY_bm; /* Enable Result Ready interrupt */

```

The interrupt flag is cleared by writing a '1' to the bit position in the Interrupt Flags (ADCn.INTFLAGS) register as shown in the code snippet below.

```

ADCO.INTFLAGS = ADC_RESRDY_bm; /* Clear Result Ready interrupt flag */

```

Interrupt flags SAMPRDY and RESRDY can also be cleared by reading respectively the ADCn.SAMPLE and ADCn.RESULT registers.

### 2.6 Window Comparator

The ADC can raise the Window Comparator Interrupt (WCMP) flag in the Interrupt Flags (ADCn.INTFLAGS) register and request an interrupt (WCMP) when the output of a conversion or accumulation is above and/or below certain thresholds. The available modes are:

- ABOVE The value is above a threshold

- · BELOW The value is below a threshold

- INSIDE The value is inside a window (above the lower threshold and below the upper threshold)

- OUTSIDE The value is outside a window (below the lower threshold or above the upper threshold)

The thresholds are set by writing to the Window Comparator Low and High Threshold (ADCn.WINLT and ADCn.WINHT) registers. The Window mode to use is selected by the Window Comparator Mode (WINCM) bit field in the Control D (ADCn.CTRLD) register.

The Window Mode Source (WINSRC) bit in the Control D (ADCn.CTRLD) register selects if the comparison is done on the 16 LSb of the Result (ADCn.RESULT) register or the Sample (ADCn.SAMPLE) register. If an interrupt request is enabled for the WCMP flag, WINSRC selects which interrupt vector to request, RESRDY or SAMPRDY.

When accumulating multiple samples, if the Window Comparator source is the Result register, the comparison between the result and the threshold(s) will happen after the last conversion is complete. If the source is the Sample register, the comparison will happen after every conversion.

The following code shows how to configure the thresholds of the window comparator, and how to configure the INSIDE mode comparing against the Result register.

#### 2.6.1 Code Example

The code example below shows an application example where an ADC reading of below 2000 or above 3000 is considered an invalid signal spike. The window comparator is used to filter these out by restarting the sample accumulation in the SAMPRDY interrupt when the signal is outside of the thresholds. The voltage of the signal is calculated in the RESRDY Interrupt Service Routine (ISR) when all samples are accumulated.

```

#define F CPU 33333333ul

#include <avr/io.h>

#include <avr/interrupt.h>

#include <util/delay.h>

#include <math.h>

#define TIMEBASE VALUE

((uint8 t) ceil(F CPU*0.000001))

#define ADC MAX \overline{V}ALUE

((1 << \overline{12}) - 1) /* In single-ended mode, the max value is 4095 */

/* Defines to easily configure ADC accumulation */

#define ADC_SAMPNUM_CONFIG ADC_SAMPNUM_ACC256_gc

/st Left shifting (1 << SAMPNUM) results in the number of accumulated samples st/

#define ADC SAMPLES

(1 << ADC SAMPNUM CONFIG)

/* Volatile variables to improve debug experience */

static volatile uint32_t adc_reading;

static volatile float voltage;

ADC initialization

void adc init()

ADCO.CTRLA = ADC ENABLE bm;

ADCO.CTRLB = ADC_PRESC_DIV2_gc; /* fCLK_ADC = 3.333333/2 MHz */

ADCO.CTRLC = ADC_REFSEL_VDD_gc | (TIMEBASE_VALUE << ADC_TIMEBASE_gp);

ADCO.CTRLE = 17; /* (SAMPDUR + 0.5) * fCLK ADC = 10.5 \mu s sample duration */

ADCO.CTRLF = ADC SAMPNUM CONFIG;

```

```

ADCO.MUXPOS = ADC MUXPOS AIN6 gc; /* ADC channel AIN6 -> PA6 */

ADCO.WINHT = 3000; /* Window High Threshold */

ADCO.WINLT = 2000; /* Window Low Threshold */

^{\prime} Window Comparator mode: Outside. Use SAMPLE register as Window Comparator source ^{\star}/

ADCO.CTRLD = ADC_WINCM_OUTSIDE_gc | ADC_WINSRC_SAMPLE_gc;

/* Enable Window Compare and Result Ready interrupt *

ADCO.INTCTRL = ADC_WCMP_bm | ADC_RESRDY_bm;

ADCO.COMMAND = ADC MODE SERIES gc; /* Series Accumulation mode */

}

Window Compare interrupt:

In this example, when a sample is outside a certain window, this is considered an

invalid signal spike. When such a spike is detected, the accumulated ADC result is

disregarded by restarting the series conversion.

ISR (ADC0 SAMPRDY vect)

ADCO.INTFLAGS = ADC WCMP bm;

/* Clear WCMP flag */

/* Clear the accumulator by resetting the Mode bit field */

ADCO.COMMAND = ADC START STOP gc;

/* Reconfigure Series Accumulation mode */

ADCO.COMMAND = ADC MODE SERIES qc;

}

Result Ready interrupt:

If no spike was detected, the result is read and the corresponding

voltage is calculated

ISR(ADC0 RESRDY vect)

ADCO.INTFLAGS = ADC RESRDY bm;

/* Clear RESRDY flag */

/* Check if the last sample was inside the window */

if(!(ADC0.INTFLAGS & ADC WCMP bm))

adc reading = ADCO.RESULT; /* Read ADC result */

/* Calculate voltage on ADC pin, VDD = 3.3V, 12-bit resolution, 256 samples */

voltage = (float)(((adc_reading * 3.3) / ADC_MAX_VALUE) / ADC_SAMPLES);

}

int main (void)

adc init();

sei(); /* Enable global interrupts */

while (1)

/* Start a conversion once every 1 ms */

ADCO.COMMAND |= ADC START IMMEDIATE gc;

_delay_ms(1);

```

#### 2.7 Events

The ADC can be connected to the event system. The event system lets peripherals communicate without CPU intervention, enabling the CPU to perform other tasks or stay in a sleep mode. The ADC can be connected either as an event generator, providing signals to another peripheral, or an event user, performing tasks based on the signals from another peripheral.

The following table shows the different available event generators from the ADC.

Table 2-2. ADC Event Generators

| Generator Name |         | Description          | Event Type | Generating   | Length of Event    |  |

|----------------|---------|----------------------|------------|--------------|--------------------|--|

| Peripheral     | Event   |                      |            | Clock Domain |                    |  |

| ADCn           | RESRDY  | Result ready         | Pulse      | CLK_PER      | One CLK_PER period |  |

| ADCn           | SAMPRDY | Sample ready         | Pulse      | CLK_PER      | One CLK_PER period |  |

| ADCn           | WCMP    | Window compare match | Pulse      | CLK_PER      | One CLK_PER period |  |

Below is a code snippet showing the configuration of event generator ADC0\_RESRDY connected through event channel 1 to the EVOUT event user, which in this case outputs the event to PB2.

- Event Generator: ADC0 RESRDY

- Event USER: EVOUT (PB2)

The ADC has one event user for detecting and acting upon input events. The table below describes the event user and the associated functionality.

Table 2-3. ADC Event Users and Available Event Actions

| User Name  |       | Description        | Input Detection | Async/Sync |

|------------|-------|--------------------|-----------------|------------|

| Peripheral | Event |                    |                 |            |

| ADCn       | START | ADC start on event | Edge            | Async      |

The START event action can be triggered if the EVENT\_TRIGGER setting is written to the START bit field in the Command (ADCn.COMMAND) register as shown in the code snippet below.

```

ADCO.COMMAND = ADC_START_EVENT_TRIGGER_gc;

```

Below is a code snippet showing the configuration of ADC0\_START as an event user, reacting to RTC overflow.

```

EVSYS.CHANNELO = EVSYS_CHANNELO RTC_OVF_gc; /* Real Time Counter overflow */

EVSYS.USERADCOSTART = EVSYS_USER_CHANNELO_gc; /* Asynchronous Event Channel 0 */

```

#### 2.7.1 Code Example

Below is a code example showing the configuration of the ADC as an event generator and an event user:

- · Event user: ADC conversion triggered by RTC overflow event

- RTC is configured to generate an RTC overflow event at the desired ADC sampling rate. The sampling rate in the example is 100 Hz.

- ADC conversion is triggered at a rate of 100 Hz, and the result is read when the Result Ready (RESRDY) bit in the Interrupt Flags (ADCn.INTFLAGS) register is set.

- · Event generator: Pin PB2 outputs an event (Pulse) when the ADC result is ready

```

#define ADC_SAMPNUM_CONFIG ADC_SAMPNUM_ACC8_gc

/* Left shifting (1 << SAMPNUM) results in the number of accumulated samples */#define ADC_SAMPLES (1 << ADC_SAMPNUM_CONFIG)

/*Defines to easily configure RTC event frequency */

#define ADC_SAMPLING_FREQ 100 /* Hz */

#define RTC_CLOCK 32768 /* Hz */

#define RTC_PERIOD (RTC_CLOCK / ADC_SAMPLING_FREQ)

/* Volatile variables to improve debug experience */

static volatile int32 t adc reading;

static volatile float voltage;

EVSYS initialization:

Channel 0:

Event system generator: RTC Overflow

Event system user: ADC0

Channel 1:

Event system generator: ADCO Result Ready

Event system user: EVOUTB (PIN PB2)

void event_system_init(void)

PORTB.DIRSET = PIN2 bm; /* Configure EVOUTB to output */

}

RTC initialization

void rtc init(void)

while (RTC.STATUS > 0); /* Wait for all registers to be synchronized */

RTC.CTRLA = RTC_PRESCALER_DIV1_gc | RTC_RTCEN_bm; /* Enable RTC, no prescaler */

RTC.CLKSEL = RTC_CLKSEL_INT32K_gc; /* Select 32.768 kHz internal RC oscillator */

RTC.PER = RTC \overline{PERIOD};

while (RTC.STATUS > 0); /* Wait for all registers to be synchronized */

/************************

ADC initialization

void adc init()

ADCO.CTRLA = ADC ENABLE bm;

ADCO.CTRLB = ADC_ENABLE_DIM,

ADCO.CTRLB = ADC_PRESC_DIV2_gc; /* fCLK_ADC = 3.3333333/2 MHz */

ADCO.CTRLC = ADC_REFSEL_VDD_gc | (TIMEBASE_VALUE << ADC_TIMEBASE_gp);

ADCO.CTRLE = 17; /* (SAMPDUR + 0.5) * fCLK_ADC = 10.5 µs sample duration */

ADCO.CTRLF = ADC SAMPNUM CONFIG;

\label{eq:adcomuxpos} $$ ADC0.MUXPOS = ADC_MUXPOS_AIN6_gc; /* ADC channel AIN6 -> PA6 */ ADC0.MUXNEG = ADC_MUXNEG_AIN7_gc; /* ADC channel AIN7 -> PA7 */ A

/* Start ADC Series conversion on event trigger */

ADCO.COMMAND = ADC_DIFF_bm | ADC_MODE_SERIES_gc | ADC_START_EVENT_TRIGGER_gc;

int main (void)

event system init();

rtc init();

adc init();

if(ADCO.INTFLAGS & ADC RESRDY bm) /* Check if ADC sample is ready */

/\star Read accumulated ADC result, clears the interrupt flag \star/

adc reading = ADCO.RESULT;

/* Calculate voltage on ADC pin, VDD = 3.3V, 8 samples in 12-bit resolution */voltage = (float)(((adc_reading * 3.3) / ADC_MAX_VALUE) / ADC_SAMPLES);

```

} }

#### 3. **Input Circuitry**

#### Input Impedance 3.1

When a voltage level imposed on a pin is sampled, it is first captured by the Sample-and-Hold capacitor (C<sub>IN</sub>). This ensures that the voltage does not change while the ADC samples the signal.

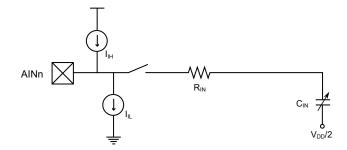

#### Figure 3-1. Model of Internal Analog Input Circuit

The time it takes to charge or discharge  $C_{IN}$  to a certain voltage level is limited by the input resistance ( $R_{IN}$ ). The following equation shows the proportional relation between the time constant t and the input impedance.

$$\tau = R_{IN} \times C_{IN}$$

Refer to the Electrical Characteristics section in the data sheet for details on the input characteristics of the ADC.

The 12-bit resolution of the ADC (and optional gain) requires the impulse response of the input circuit settled to more than 99.9% of the final voltage to be certain the measurement will be correct. The following example calculations without gain and with 16x gain show how settled a signal needs to be for the ADC to sample correctly at 12-bit resolution.

$$V_{\text{MSb}} = V_{\text{REF}} - \frac{V_{\text{REF}}}{4096 \times \text{Gain}}$$

$$V_{\text{MSb}} \% = \left(1 - \frac{1}{4096 \times \text{Gain}}\right) \times 100 \%$$

$$V_{\text{MSb}} \%_{\text{without gain}} = \left(1 - \frac{1}{4096 \times 1}\right) \times 100 \% = 99.975 \%$$

$$V_{\text{MSb}} \%_{16 \text{x gain}} = \left(1 - \frac{1}{4096 \times 16}\right) \times 100 \% = 99.998 \%$$

The impulse response for the input circuit is given by the following equation.

$$V(t) = V_{\rm IN} \times (1 - e^{-t/\tau})$$

Solving the two examples for  $V_{\text{MSb}}$  where  $V_{\text{IN}}$  is 100%, the following settling times are obtained.

$$t_{\text{without gain}} = 8.29\tau$$

$$t_{16\text{x gain}} = 10.81\tau$$

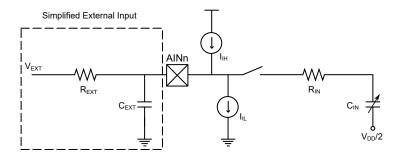

The impedance of the external signal should also be taken into consideration when calculating the settling time, expanding the circuit into a more complex system as shown in the figure below.

Technical Brief DS90003257A-page 11 © 2020 Microchip Technology Inc.

Figure 3-2. Model of Analog Input Circuit with External Signal

The characteristics of the external impedance determine how complex the settling time calculation will be. However, this is not covered by this technical brief.

#### 3.1.1 PGA

The PGA is connected between the analog input pin and the ADC, with an input impedance depending on the selected gain setting. Refer to the *Electrical Characteristics* section for details on the input characteristics of the PGA. The equations above are the same for calculating the appropriate sample duration when using the PGA impedance values.

When the PGA is used, it is continuously sampling and will only be in the Hold state when the ADC is sampling the PGA. If the time between conversions is longer than the needed sampling time, this can be utilized to get a shorter total conversion time by setting the SAMPDUR to the minimum supported value.

### 3.2 Sample Duration

A suitable ADC sample duration can either be calculated based on the impulse response of the circuit, as shown in Section 3.1 Input Impedance, or found by tuning the sample duration in firmware until a stable output from the ADC conversion is achieved.

The sample duration for this ADC can be a maximum of 256 ADC clock (CLK\_ADC) cycles, and is configured using the Sample Duration (SAMPDUR) bit field in the Control E (ADCn.CTRLE) register. The sample duration is SAMPDUR + 0.5 (CLK\_ADC) cycles when the PGA is disabled, and SAMPDUR + 1 (CLK\_ADC) when the PGA is enabled. If the input impedance is very high, increasing the ADC prescaler can also be used to further increase the sample duration.

Minimum sample duration is configured as shown in the following code snippet. The calculations are based on the CPU clock running at 16 MHz, with PGA disabled.

```

ADCO.CTRLB = ADC PRESC_DIV2_gc; /* ADC clock: 8 MHz */

ADCO.CTRLE = 0; 7* Sample Duration: (0 + 0.5) / 8 MHz = 0.06 µS */

```

Maximum sample duration is configured as shown in the following code snippet. The calculations are based on the CPU clock running at 16 MHz, with PGA disabled.

```

ADCO.CTRLB = ADC_PRESC_DIV40_gc; /* ADC clock: 400 kHz */

ADCO.CTRLE = 255; /* Sample Duration: (255 + 0.5) / 400 kHz = 639 µS */

```

# 4. Power and Timing

#### 4.1 Clock

The ADC clock (CLK\_ADC) is scaled down from the peripheral clock (CLK\_PER). This can be configured by the Prescaler (PRESC) bit field in the CTRLB (ADCn.CTRLB) register.

```

ADCO.CTRLB = ADC_PRESC_DIV20_gc; /* CLK_ADC = CLK_PER/20 */

```

Some of the internal timings in the ADC and the PGA are independent of CLK\_ADC. To ensure correct internal timing regardless of the ADC clock frequency, a 1 µs timebase (given in CLK\_PER cycles) must be written to the TIMEBASE bit field in the Control C (ADCn.CTRLC) register. The timebase must be rounded up to the closest integer. The following code snippet shows how this can be done using the ceil function.

```

#include <math.h>

#define F_CPU 33333333ul

#define TIMEBASE_VALUE ((uint8_t) ceil(F_CPU*0.000001))

ADCO.CTRLC = (TIMEBASE_VALUE << ADC_TIMEBASE_gp);</pre>

```

### 4.2 PGA Bias and Output Sample Duration

The PGA Bias Select (PGABIASSEL) bit field in the ADC PGA Control (ADCn.PGACTRL) register can be configured to reduce the power consumption depending on the ADC clock frequency. The ADC PGA Sample Duration (ADCPGASAMPDUR) bit field can be configured to reduce the number of CLK\_ADC cycles the ADC is sampling the output of the PGA. This is also dependent of the ADC clock frequency.

See the register description for these bit fields in the data sheet for recommended combinations of  $f_{\text{CLK\_ADC}}$  and PGABIASSEL and ADCPGASAMPDUR.

An example configuration is shown below.

**Note:** PGA Control is one of few AVR registers with a nonzero reset value. This must be taken into account if only configuring parts of the register.

#### 4.3 Conversion Time

The conversion time for a single sample is calculated by:

```

\label{eq:Sample Conversion Time} \begin{aligned} \text{Sample Conversion Time} &= \text{Initialization} + \frac{\text{SAMPDUR} + 15.5}{f_{\text{CLK\_ADC}}} \end{aligned}

```

For example, given initialization =  $60 \mu s$ , SAMPDUR =  $2 \text{ an } f_{CLk\_ADC} = 1 \text{ MHz}$ , the conversion time for each sample is given by:

Sample Conversion Time =

$$60 \mu s + \frac{2+15.5}{1 \text{ MHz}} = 77.5 \mu s$$

With the Low Latency (LOWLAT) bit written to '1' in the Control A (ADCn.CTRLE) register, the initialization time is only needed once upon enabling the ADC. After that, the example above will give a sample conversion time of 17.5  $\mu$ s.

© 2020 Microchip Technology Inc. Technical Brief DS90003257A-page 13

The sampling period of the ADC is configured through the Sample Duration (SAMPDUR) bit field in the Control E (ADCn.CTRLE) register as (SAMPDUR +  $\frac{1}{2}$ ) CLK\_ADC cycles.

```

ADCO.CTRLE = 2; /* Sample duration configured to 2 */

```

If PGA is used, the input sample duration is (SAMPDUR + 1) CLK\_ADC cycles, while the ADC PGA Sample Duration (ADCPGASAMPDUR) bit field in the PGA Control (ADCn.PGACTRL) register controls how long the ADC samples the PGA.

ADCO.PGACTRL = ADC\_ADCPGASAMPDUR\_15CLK\_gc; /\* 15 CLK\_ADC cycles \*/

# 5. Output Processing

### 5.1 Result Range

The output from an ADC conversion is given by the following equations:

$$Single-Ended \ conversion = \frac{V_{\rm INP} \times {\rm Gain}}{V_{\rm REF}} \times 4096 \in [0,4095]$$

$$\text{Differential conversion} = \frac{(V_{\text{INP}} - V_{\text{INN}}) \times \text{Gain}}{V_{\text{REF}}} \times 2048 \in [-2048, 2047]$$

$V_{INP}$  and  $V_{INN}$  are the positive and negative inputs to the ADC and  $V_{REF}$  is the selected voltage reference. The gain is between 1x and 16x as configured in the PGA, and 1x if the PGA is not in use.

The ADC has two output registers, the Sample (ADCn.SAMPLE) and Result (ADCn.RESULT) registers. The 16-bit Sample register will always be updated with the latest ADC conversion output (one sample). In Series Accumulation mode, after the SAMPNUM number of conversions are finished, the Result register will be updated with the accumulated result.

With a Single-Ended conversion, the average voltage applied to the analog pin is calculated by:

$$V_{\text{INP}} = \frac{\text{ADCn.RESULT} \times V_{\text{REF}}}{4096 \times \text{Gain} \times \text{SAMPNUM}}$$

#### 5.2 Accumulation

The ADC supports sampling in series where a configurable number of conversion results are automatically accumulated into a single ADC result. A maximum of 1024 samples can be accumulated. Sample accumulation is configured by writing the Sample Accumulation Number Select (SAMPNUM) bit field in the Control F (ADCn.CTRLF) register.

The 16-bit Sample (SAMPLE) register will always be updated with the latest ADC conversion output (one sample). The samples are accumulated in an internal sample accumulator which is sufficiently wide to avoid overflow for all supported accumulation configurations. The accumulated result is transferred to the 32-bit Result (ADCn.RESULT) register when the selected number of samples are finished, and the Result Ready (RESRDY) bit in the Interrupt Flags (ADCn.INTFLAGS) register is set.

The code snippet below shows the configuration to accumulate 1024 samples:

```

ADCO.CTRLF = ADC_SAMPNUM_ACC1024_gc;

```

### 5.2.1 Oversampling

The Series Accumulation mode can be used to achieve higher ADC resolution. For example, by using 1024 12-bit samples, a 17-bit result could be achieved.

To increase the resolution, for each additional bit of ADC resolution, n, the signal must be oversampled  $4^n$  samples. To achieve 17-bit ADC, an additional 5-bit resolution is needed. Hence, the signal has to be sampled  $4^5$  = 1024 times. To scale the result down to the desired resolution, it must be right-shifted by n which is equivalent to dividing the result by  $2^n$ .

#### 5.2.1.1 Code Example

The following code example shows how to increase the ADC resolution from 12-bit to 17-bit by using oversampling, and how to calculate the voltage applied to ADC channel AIN6.

```

#define F_CPU 333333331

#include <avr/io.h>

#include <math.h>

```

```

#include <util/delay.h>

#define TIMEBASE VALUE

((uint8 t) ceil(F CPU*0.000001))

/* Defines to configure ADC accumulation */

5 /* 5 bits extra */

#define OVERSAMPLING BITS

#define OVERSAMPLING MAX VALUE ((uint32 t) ((1 << 12) - 1) << OVERSAMPLING BITS) /* 12 + 5

bits = 17 bits */

#define ADC_SAMPNUM_CONFIG

match this formula */

(OVERSAMPLING BITS << 1) /* The SAMPNUM bit field setting

#define ADC SAMPLES

(1 << ADC SAMPNUM CONFIG) /* 5 bits = 1024 samples */

/* Volatile variables to improve debug experience */

static volatile uint32_t adc_reading;

static volatile float voltage;

ADC initialization

void adc init()

ADCO.CTRLA = ADC ENABLE bm;

ADCO.CTRLB = ADC_PRESC_DIV2_gc; /* fCLK_ADC = 3.333333/2 MHz */

ADCO.CTRLC = ADC_REFSEL_VDD_gc | (TIMEBASE_VALUE << ADC_TIMEBASE_gp); ADCO.CTRLE = 17; /* (SAMPDUR + 0.5) * fCLK_ADC = 10.5 \mus sample duration */

ADCO.CTRLF = ADC SAMPNUM CONFIG;

ADCO.MUXPOS = ADC MUXPOS AIN6 gc; /* ADC channel AIN6 -> PA6 */

ADCO.COMMAND = ADC MODE SERIES gc; /* Series Accumulation mode */

int main (void)

adc init();

while(1)

ADCO.COMMAND |= ADC START IMMEDIATE gc;

while(!(ADCO.INTFLAGS & ADC_SAMPRDY bm)); /* Wait until conversion is done */

ADCO.INTFLAGS = ADC SAMPRDY bm; /* Clear Sample Ready interrupt flag */

if(ADCO.INTFLAGS & ADC RESRDY bm) /* If result is ready */

/st Oversampling compensation as explained in the tech brief st/

adc reading = ADCO.RESULT >> OVERSAMPLING BITS; /* Scale accumulated result by

right shifting the number of extra bits */

voltage = (float)((adc_reading * 3.3) / OVERSAMPLING MAX VALUE); /* Calculate

voltage using 17-bit resolution, V\overline{D}D = 3.3V */

_{	t delay\_ms(1);}

```

#### 5.2.2 Series Accumulation with Scaling

Like in the Series Accumulation mode, a SAMPNUM number of samples are in this mode automatically accumulated into a single result. The difference is that in Series Accumulation with Scaling, the result is automatically scaled to a 16-bit value. Scaling is always applied after accumulating the last sample and is carried out by right shifting the accumulated result by SAMPNUM-4 bits.

This mode can simply be used to accumulate and automatically get an averaged result, or it may be used in combination with the oversampling technique as described in Section 5.2.1 Oversampling to achieve a 16-bit resolution by accumulating at least  $4^4 = 256$  samples and automatically scaling down to 16 bits.

#### 5.2.2.1 Code Example

The following code example shows how to measure  $V_{DD}$  using the Series Accumulation with Scaling mode and oversampling to achieve 16-bit resolution.

```

#define F_CPU 33333333ul

#include <avr/io.h>

#include <math.h>

```

```

#include <util/delay.h>

#define TIMEBASE VALUE

((uint8_t) ceil(F_CPU*0.000001))

((1 << \overline{1}2) - 1)

/* In single-ended mode, the

#define ADC MAX \overline{V}ALUE

max value is 4095 */

#define ADC MAX VALUE 16BIT

((uint32 t) ADC MAX VALUE << 4)

/* Left shift 12-bit max

value up to \overline{16} bits *7

/* Defines to easily configure ADC accumulation */

#define ADC_SAMPNUM_CONFIG ADC_SAMPNUM_ACC256_gc

/* Left shifting (1 << SAMPNUM) results in the number of accumulated samples */#define ADC SAMPLES (1 << ADC SAMPNUM CONFIG)

/* Volatile variables to improve debug experience */

static volatile uint16 t adc reading;

static volatile float voltage;

ADC initialization

void adc init()

ADCO.CTRLA = ADC ENABLE bm;

ADCO.CTRLB = ADC PRESC DIV2 gc; /* fCLK ADC = 3.3333333/2 MHz */

ADCO.CTRLC = ADC_REFSEL_1024MV_gc | (TIMEBASE_VALUE << ADC_TIMEBASE_gp);

ADCO.CTRLE = 17; /* (SAMPDUR + 0.5) * fCLK ADC = 10.5 \mus sample duration */

ADCO.CTRLF = ADC LEFTADJ bm | ADC SAMPNUM CONFIG; /* Enable left adjust if accumulating <

16 samples */

ADCO.MUXPOS = ADC MUXPOS VDDDIV10 gc; /* ADC channel VDD/10 */

ADCO.COMMAND = ADC MODE \overline{\text{SERIES}} SCALING gc; /* Series Accumulation with Scaling */

}

int main (void)

adc init();

while(1)

ADCO.COMMAND |= ADC_START_IMMEDIATE_gc; while(!(ADCO.INTFLAGS & ADC SAMPRDY bm)); /* Wait until conversion is done */

ADCO.INTFLAGS = ADC SAMPRDY bm; /* Clear Sample Ready interrupt flag */

if(ADCO.INTFLAGS & ADC RESRDY bm) /* If result is ready */

adc reading = ADCO.RESULT; /* Read 16 bit scaled or left adjusted result */

/* \overline{\text{C}}alculate VDD, VREF = 1.024V, 16-bit resolution.

Multiplied by 10 because the input channel is VDD/10. ^{\star}/

voltage = (float) (adc reading * 1.024 * 10) / ADC MAX VALUE 16BIT;

delay ms(10);

```

### 5.3 Left Adjust

The Left Adjust (LEFTADJ) bit in the Control F (ADCn.CTRLF) register enables left-shift of the output data in the modes where this is supported. If enabled, this will left-shift the output from both the Result and the Sample registers. It is configured as shown in the following code snippet:

```

ADCO.CTRLF = ADC_LEFTADJ_bm; /* Enable Left Adjust bit */

```

Left adjust is available in ADC mode 3, Series Accumulation with Scaling.

The following tables show how the left adjust feature affects the Result register output format in Single-Ended and Differential modes.

Table 5-1. RESULT Register - Single-Ended Mode - ADC Mode 3

| LEFTADJ | RES[31:24] | RES[23:16] | RES[15:12] | RES[11:8]                                     | RES[7:0]                  |                               |  |

|---------|------------|------------|------------|-----------------------------------------------|---------------------------|-------------------------------|--|

| 0       |            | 0x00       |            |                                               | Scaled accumulation[15:0] |                               |  |

| 1       |            | 0x00       |            | 0x00 Scaled accumulation[15:0] <sup>(1)</sup> |                           | mulation[15:0] <sup>(1)</sup> |  |

Table 5-2. RESULT Register - Differential Mode - ADC Mode 3

| LEFTADJ | RES[31:24] | RES[23:16]     | RES[15:12] | RES[11:8]                                       | RES[7:0]                         |  |  |

|---------|------------|----------------|------------|-------------------------------------------------|----------------------------------|--|--|

| 0       |            | Sign Extension |            |                                                 | Signed Scaled accumulation[15:0] |  |  |

| 1       |            | Sign Extension |            | Signed Scaled accumulation[15:0] <sup>(1)</sup> |                                  |  |  |

If SAMPNUM < 4, the result is left-shifted 4 - SAMPNUM bits such that bit 15 is the MSb. If SAMPNUM > 4, the scaling feature of the ADC mode right-shifts the result by SAMPNUM - 4 bits.

#### Example 1: SAMPNUM = 3 (Accumulation with 8 samples)

When the Left Adjust bit is 0, ADCn.SAMPLE =  $0 \times FFF$  for all samples, and 8 samples are accumulated, the accumulated value in ADCn.RESULT is 8 x 4095 =  $0 \times 7FF8$ .

After enabling the Left Adjust bit, the result will be left-shifted by 4 - SAMPNUM = 1 bit (SAMPNUM is 3 to accumulate 8 samples). So by left-shifting 0x7FF8 by 1 bit, ADCn.RESULT = 0xFFF0.

#### Example 2: SAMPNUM = 5 (Accumulation with 32 samples)

When the Left Adjust bit is 0, ADCn.SAMPLE = 0xFFF for all samples, and 32 samples are accumulated, the accumulated value is  $32 \times 4095 = 0x1FFE0$ .

In Scaling mode, the result will be right-shifted by SAMPNUM - 4 = 1 bit (SAMPNUM is 5 to accumulate 32 samples). So by right-shifting 0x1FFE0 by 1 bit, ADCn.RESULT = 0xFFF0.

The following table show how the left adjust feature affects the Sample register output format in Single-Ended and Differential modes.

Table 5-3. SAMPLE Register – Single-Ended/Differential Mode – ADC Mode 3

|  | LEFTADJ | DIFF | SAMPLE[15:12]         | SAMPLE[11:8]                 | SAMPLE[7:0] |  |

|--|---------|------|-----------------------|------------------------------|-------------|--|

|  | 0       | 0    | 0x00                  | Conversion[11:0]             |             |  |

|  | 0       | 1    | Sign extension        | Signed conversion[11:0]      |             |  |

|  | 1       | 0    | Conversion[11:0] << 4 |                              |             |  |

|  | ı       | 1    |                       | Signed conversion[11:0] << 4 |             |  |

For example, if the Left Adjust feature is disabled and the ADCn.SAMPLE value is 0x0FFF, the corresponding ADCn.SAMPLE value when Left Adjust is enabled is 0xFFF0.

### 5.4 Signed and Unsigned Output

The data format for a sample in Single-Ended mode is unsigned one's complement, where  $0 \times 0000$  represents zero and  $0 \times 0$  FFF represents the largest number. If the analog input is higher than the reference level of the ADC, the 12-bit ADC output will be equal to the maximum value of  $0 \times 0$  FFF. Likewise, if the input is below 0V, the ADC output will be  $0 \times 0000$ .

For Differential mode, the data format is two's complement with sign extension.

#### Sample Register Output

The data type of the sample variable should be uint16 t when using Single-Ended mode.

The data type of the sample variable should be  $int16_t$  when using Differential mode.

For example, when using Single-Ended mode in 12-bit mode, the voltage of a single sample may be interpreted as shown in the code snippet below.

```

uint16_t sample_variable = ADCn.SAMPLE;

float sample_voltage = (sample_variable * VREF) / 4095;

```

When using Differential mode in 12-bit mode, the voltage of a single sample may be interpreted as shown in the code snippet below.

```

int16_t sample_variable = ADCn.SAMPLE;

float sample_voltage = (sample_variable * VREF) / 2047;

```

#### **Result Register Output**

The data type of the result variable should be uint32 t when using Single-Ended mode.

The data type of the result variable should be int32\_t when using Differential mode.

For example, when using Single-Ended mode in 12-bit mode, the voltage of SAMPNUM accumulated samples may be interpreted as shown in the code snippet below.

```

uint32_t result_variable = ADCn.SAMPLE;

float result_voltage = ((result_variable * VREF) / SAMPNUM) / 4095;

```

When using Differential mode in 12-bit mode, the voltage of SAMPNUM accumulated samples may be interpreted as shown in the code snippet below.

```

int32_t result_variable = ADCn.SAMPLE;

float result_voltage = ((result_variable * VREF) / SAMPNUM) / 2047;

```

# 6. Get Code Examples from GitHub

The code examples are available through GitHub, which is a web-based server that provides the application codes through a Graphical User Interface (GUI). The code examples can be opened in both Atmel Studio and MPLAB X. To open the Atmel Studio project in MPLAB X, select from the menu in MPLAB X, *File > Import > Atmel Studio Project* and navigate to .cproj file.

The GitHub webpage: GitHub.

#### **Code Examples**

Finding example code for devices in the tinyAVR 2 family can be done by searching for the device name, e.g. ATtiny1627, in the GitHub example browser.

Download the code as a .zip file from the example page on GitHub by clicking the Clone or download button.

# 7. Revision History

| Revision | Date    | Description              |

|----------|---------|--------------------------|

| Α        | 07/2020 | Initial document release |

# The Microchip Website

Microchip provides online support via our website at www.microchip.com/. This website is used to make files and information easily available to customers. Some of the content available includes:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# **Product Change Notification Service**

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to www.microchip.com/pcn and follow the registration instructions.

# **Customer Support**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Embedded Solutions Engineer (ESE)

- **Technical Support**

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: www.microchip.com/support

# Microchip Devices Code Protection Feature

Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today. when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

# Legal Notice

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with

DS90003257A-page 22 © 2020 Microchip Technology Inc.

your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TempTrackr, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, Vite, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, Anyln, AnyOut, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, INICnet, Inter-Chip Connectivity, JitterBlocker, KleerNet logo, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2020, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-6464-8

# **Quality Management System**

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

© 2020 Microchip Technology Inc.

Technical Brief

DS90003257A-page 23

# **Worldwide Sales and Service**

| AMERICAS                  | ASIA/PACIFIC          | ASIA/PACIFIC            | EUROPE                |

|---------------------------|-----------------------|-------------------------|-----------------------|

| Corporate Office          | Australia - Sydney    | India - Bangalore       | Austria - Wels        |

| 2355 West Chandler Blvd.  | Tel: 61-2-9868-6733   | Tel: 91-80-3090-4444    | Tel: 43-7242-2244-39  |

| Chandler, AZ 85224-6199   | China - Beijing       | India - New Delhi       | Fax: 43-7242-2244-393 |

| Tel: 480-792-7200         | Tel: 86-10-8569-7000  | Tel: 91-11-4160-8631    | Denmark - Copenhagen  |

| Fax: 480-792-7277         | China - Chengdu       | India - Pune            | Tel: 45-4485-5910     |

| Technical Support:        | Tel: 86-28-8665-5511  | Tel: 91-20-4121-0141    | Fax: 45-4485-2829     |

| www.microchip.com/support | China - Chongqing     | Japan - Osaka           | Finland - Espoo       |

| Web Address:              | Tel: 86-23-8980-9588  | Tel: 81-6-6152-7160     | Tel: 358-9-4520-820   |

| www.microchip.com         | China - Dongguan      | Japan - Tokyo           | France - Paris        |

| Atlanta                   | Tel: 86-769-8702-9880 | Tel: 81-3-6880- 3770    | Tel: 33-1-69-53-63-20 |

| Duluth, GA                | China - Guangzhou     | Korea - Daegu           | Fax: 33-1-69-30-90-79 |

| Tel: 678-957-9614         | Tel: 86-20-8755-8029  | Tel: 82-53-744-4301     | Germany - Garching    |

| Fax: 678-957-1455         | China - Hangzhou      | Korea - Seoul           | Tel: 49-8931-9700     |

| Austin, TX                | Tel: 86-571-8792-8115 | Tel: 82-2-554-7200      | Germany - Haan        |

| Tel: 512-257-3370         | China - Hong Kong SAR | Malaysia - Kuala Lumpur | Tel: 49-2129-3766400  |

| Boston                    | Tel: 852-2943-5100    | Tel: 60-3-7651-7906     | Germany - Heilbronn   |

| Westborough, MA           | China - Nanjing       | Malaysia - Penang       | Tel: 49-7131-72400    |

| Tel: 774-760-0087         | Tel: 86-25-8473-2460  | Tel: 60-4-227-8870      | Germany - Karlsruhe   |

| Fax: 774-760-0088         | China - Qingdao       | Philippines - Manila    | Tel: 49-721-625370    |

| Chicago                   | Tel: 86-532-8502-7355 | Tel: 63-2-634-9065      | Germany - Munich      |

| Itasca, IL                | China - Shanghai      | Singapore               | Tel: 49-89-627-144-0  |

| Tel: 630-285-0071         | Tel: 86-21-3326-8000  | Tel: 65-6334-8870       | Fax: 49-89-627-144-44 |

| Fax: 630-285-0075         | China - Shenyang      | Taiwan - Hsin Chu       | Germany - Rosenheim   |

| Dallas                    | Tel: 86-24-2334-2829  | Tel: 886-3-577-8366     | Tel: 49-8031-354-560  |

| Addison, TX               | China - Shenzhen      | Taiwan - Kaohsiung      | Israel - Ra'anana     |

| Tel: 972-818-7423         | Tel: 86-755-8864-2200 | Tel: 886-7-213-7830     | Tel: 972-9-744-7705   |

| Fax: 972-818-2924         | China - Suzhou        | Taiwan - Taipei         | Italy - Milan         |

| Detroit                   | Tel: 86-186-6233-1526 | Tel: 886-2-2508-8600    | Tel: 39-0331-742611   |

| Novi, MI                  | China - Wuhan         | Thailand - Bangkok      | Fax: 39-0331-466781   |

| Tel: 248-848-4000         | Tel: 86-27-5980-5300  | Tel: 66-2-694-1351      | Italy - Padova        |

| Houston, TX               | China - Xian          | Vietnam - Ho Chi Minh   | Tel: 39-049-7625286   |

| Tel: 281-894-5983         | Tel: 86-29-8833-7252  | Tel: 84-28-5448-2100    | Netherlands - Drunen  |

| Indianapolis              | China - Xiamen        |                         | Tel: 31-416-690399    |

| Noblesville, IN           | Tel: 86-592-2388138   |                         | Fax: 31-416-690340    |

| Tel: 317-773-8323         | China - Zhuhai        |                         | Norway - Trondheim    |

| Fax: 317-773-5453         | Tel: 86-756-3210040   |                         | Tel: 47-72884388      |

| Tel: 317-536-2380         | 15 55 155 52 155 15   |                         | Poland - Warsaw       |

| Los Angeles               |                       |                         | Tel: 48-22-3325737    |

| Mission Viejo, CA         |                       |                         | Romania - Bucharest   |

| Tel: 949-462-9523         |                       |                         | Tel: 40-21-407-87-50  |

| Fax: 949-462-9608         |                       |                         | Spain - Madrid        |

| Tel: 951-273-7800         |                       |                         | Tel: 34-91-708-08-90  |

| Raleigh, NC               |                       |                         | Fax: 34-91-708-08-91  |

| Tel: 919-844-7510         |                       |                         | Sweden - Gothenberg   |

| New York, NY              |                       |                         | Tel: 46-31-704-60-40  |

| Tel: 631-435-6000         |                       |                         | Sweden - Stockholm    |

| San Jose, CA              |                       |                         | Tel: 46-8-5090-4654   |

| Tel: 408-735-9110         |                       |                         | UK - Wokingham        |

| Tel: 408-436-4270         |                       |                         | Tel: 44-118-921-5800  |

| Canada - Toronto          |                       |                         | Fax: 44-118-921-5820  |

| Tel: 905-695-1980         |                       |                         | 1 da. 77-110-321-3020 |

| Fax: 905-695-2078         |                       |                         |                       |

| I an. 300-030-20/0        |                       |                         |                       |