# **CAN Flexible Data-Rate (FD) Protocol Module**

This section of the manual contains the following major topics:

| 1.0  | Introduction              | 2   |

|------|---------------------------|-----|

| 2.0  | CAN FD Message Frames     | 5   |

| 3.0  | Control Registers         | 9   |

| 4.0  | Modes of Operation        | 53  |

| 5.0  | Configuration             | 59  |

| 6.0  | Message Transmission      | 72  |

| 7.0  | Transmit Event FIFO – TEF | 81  |

| 8.0  | Message Filtering         | 86  |

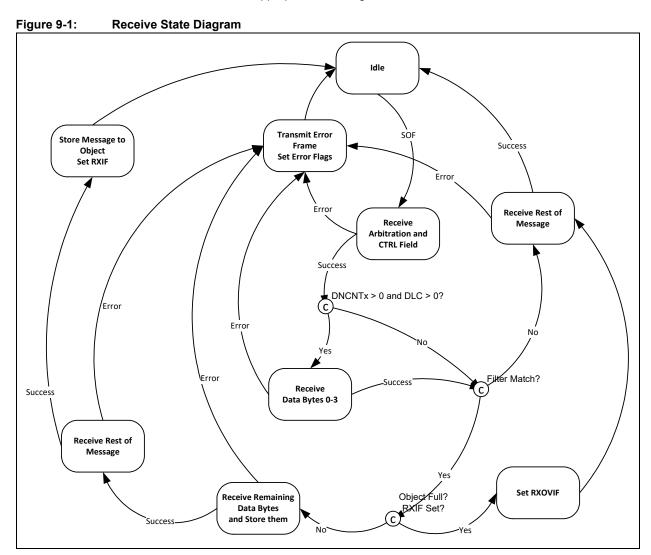

| 9.0  | Message Reception         | 91  |

| 10.0 | FIFO Behavior             | 97  |

| 11.0 | Timestamping              | 108 |

| 12.0 | Interrupts                | 109 |

| 13.0 | Error Handling            | 116 |

| 14.0 | Related Application Notes | 118 |

| 15.0 | Revision History          | 119 |

### 1.0 INTRODUCTION

CAN Flexible Data-Rate (FD) addresses the increasing demand for bandwidth on CAN buses. The two major enhancements over CAN 2.0B consist of:

- Increased data field of up to 64 data bytes (from a maximum eight data bytes for CAN 2.0B)

- · Option to switch to faster bit rate after the arbitration field

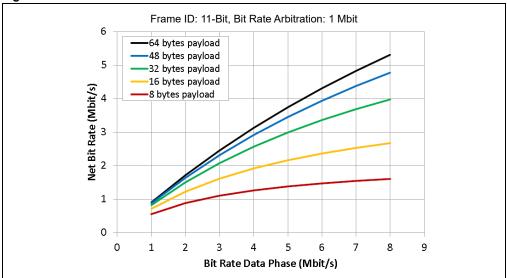

Figure 1-1 shows the possible increase in net bit rate due to the higher Data Bit Rate (DBR) and increased data bytes per frame.

Figure 1-1: Net CAN FD Bit Rate

The CAN FD protocol is defined to allow CAN 2.0 messages and CAN FD messages to coexist on the same bus. This does not imply that non-CAN FD controllers can be mixed with CAN FD controllers on the same bus. Non-CAN FD controllers will generate error frames while receiving a CAN FD message.

#### 1.1 Features

The CAN FD module has the following features:

#### General

- · Nominal (Arbitration) Bit Rate up to 1 Mbps

- Data Bit Rate up to 8 Mbps

- · CAN FD Controller modes:

- Mixed CAN 2.0B and CAN FD mode

- CAN 2.0B mode

- Conforms to ISO11898-1:2015

#### Message FIFOs

- 31 FIFOs Configurable as Transmit or Receive FIFOs

- One Transmit Queue (TXQ)

- · Transmit Event FIFO (TEF) with 32-Bit Timestamp

#### **Message Transmission**

- · Message Transmission Prioritization:

- Based on priority bit field and/or

- Message with lowest ID gets transmitted first using the TXQ

- Programmable Automatic Retransmission Attempts: Unlimited, Three Attempts or Disabled

# **CAN FD Protocol Module**

#### **Message Reception**

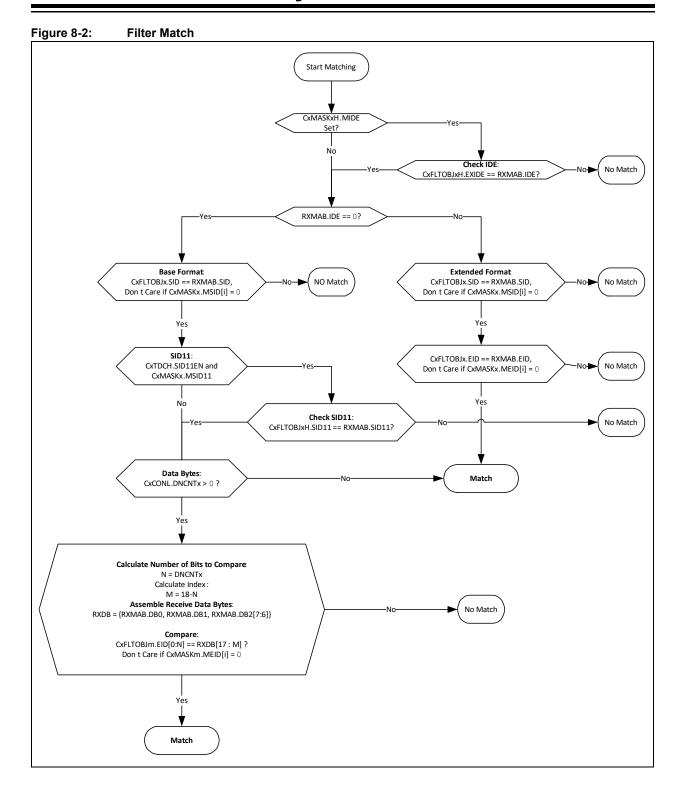

- · 32 Flexible Filter and Mask Objects

- · Each Object can be Configured to Filter either:

- Standard ID and first 18 data bits or

- Extended ID

- · 32-Bit Timestamp

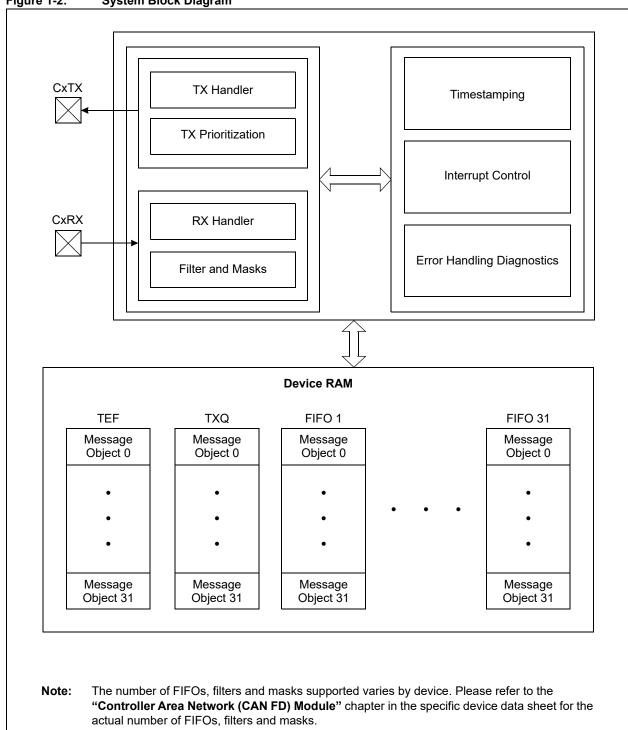

- The CAN FD Bit Stream Processor (BSP) implements the Medium Access Control (MAC)

of the CAN FD protocol described in ISO11898-1:2015. It serializes and describing the bit

stream, encodes and decodes the CAN FD frames, manages the medium access,

Acknowledges frames, and detects and signals errors.

- The TX handler prioritizes the messages that are requested for transmission by the transmit FIFOs. It uses the RAM interface to fetch the transmit data from RAM and provides it to the BSP for transmission.

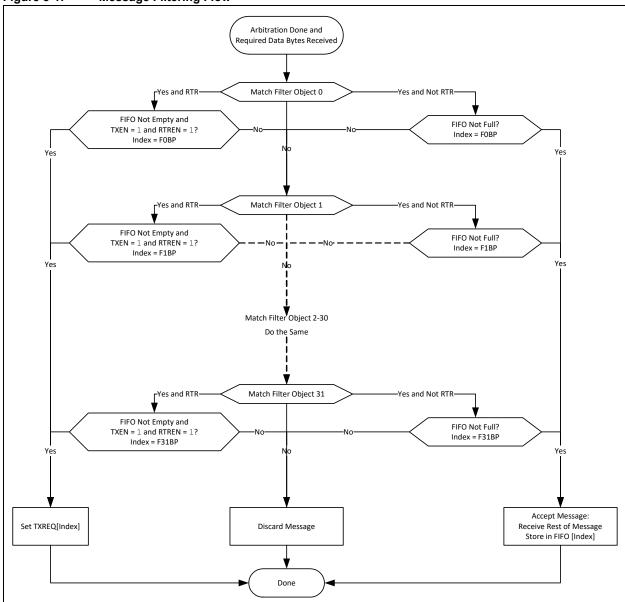

- The BSP provides received messages to the RX handler. The RX handler uses an

acceptance filter to filter the messages that shall be stored in the receive FIFOs. It uses the

RAM interface to store received data into RAM.

- Each FIFO can be configured either as a transmit or receive FIFO. The FIFO control keeps track of the FIFO head and tail, and calculates the user address. In a TX FIFO, the user address points to the address in RAM where the data for the next transmit message is stored. In an RX FIFO, the user address points to the address in RAM where the data of the next receive message will be read. The user notifies the FIFO that a message is written to or read from RAM by incrementing the head/tail of the FIFO.

- The TXQ is a special transmit FIFO that transmits the messages based on the ID of the messages stored in the queue.

- The TEF stores the message IDs of the transmitted messages.

- A free-running Time Base Counter (TBC) is used to timestamp received messages.

Messages in the TEF can also be timestamped.

- The CAN FD controller module generates interrupts when new messages are received or when messages are transmitted successfully.

Figure 1-2 shows the system block diagram.

Figure 1-2: System Block Diagram

### 2.0 CAN FD MESSAGE FRAMES

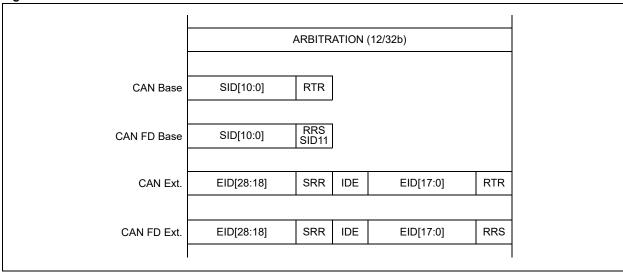

The ISO11898-1:2015 describes the different CAN message frames in detail. Figure 2-1 through Figure 2-6 explain and summarize the construction of the messages and fields.

There are four different CAN data/remote frames (see Figure 2-2):

- CAN Base Frame: Classic CAN 2.0 frame using Standard ID

- · CAN FD Base Frame: CAN FD frame using Standard ID

- CAN Extended Frame: Classic CAN 2.0 frame using Extended ID

- · CAN FD Extended Frame: CAN FD frame using Extended ID

There are no remote frames in CAN FD frames; therefore, the RTR bit is replaced with the RRS bit (see Figure 2-2). The RRS bit in the CAN FD base frame can be used to extend the SID to 12 bits. When enabled, it is referred to as SID11; it is the Least Significant bit (LSb) of SID[11:0].

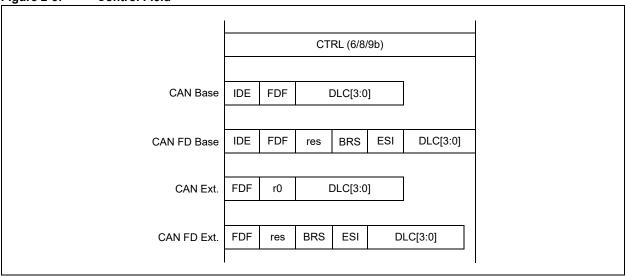

Figure 2-3 specifies the control field of the different CAN messages. Before CAN FD was added to the ISO11898-1:2015, the FDF bit was a reserved bit. Now the FDF bit selects between Classic and CAN FD formats.

The BRS bit selects if the bit rate should be switched in the data phase of CAN FD frames. Figure 2-6 illustrates the error and overload frames. These special frames do not change.

Note:

If an error is detected during the data phase of a CAN FD frame, the bit rate will be switched back to the Nominal Bit Rate (NBR). Error frames are always transmitted at the arbitration bit rate.

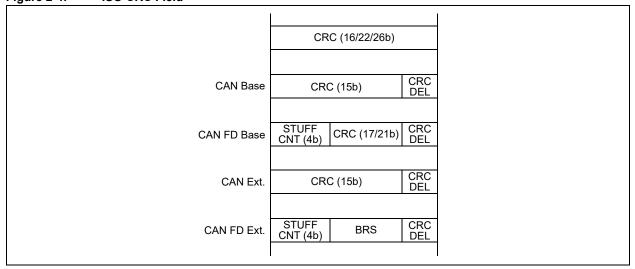

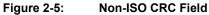

#### 2.1 ISO vs. Non-ISO CRC

To support the system validation of non-ISO CRC ECUs, the CAN FD controller module supports both ISO CRC (according to ISO11898-1:2015) and non-ISO CRC (see Figure 2-4 and Figure 2-5). The CRC field is selectable using the ISOCRCEN bit (CxCONL[5]). The ISO CRC field contains the stuff count. This count was not included in the original CAN FD specification; it was added to fix a minor issue in the error detection of the original specification.

CAN FD frames use two different lengths of CRC: 17-bit for up to 16 data bytes and 21-bit for 20 or more data bytes. Technically, there are a total of six different CAN data/remote frames in the CAN FD.

Figure 2-1: General Data Frame

|               |             | DATA FRAME           |               |                         |                                    |          |          |               |  |  |

|---------------|-------------|----------------------|---------------|-------------------------|------------------------------------|----------|----------|---------------|--|--|

| IFS<br>(= 3b) | SOF<br>(1b) | ARBITRATION (12/32b) | CTRL (6/8/9b) | DATA<br>(0 to 64 bytes) | CRC (16/18/22b)<br>CRC (16/22/26b) | ACK (2b) | EOF (7b) | IFS<br>(= 3b) |  |  |

|               |             |                      |               |                         |                                    |          |          |               |  |  |

Figure 2-2: Arbitration Field

Figure 2-3: Control Field

Figure 2-4: ISO CRC Field

Figure 2-6: Error and Overload Frame

| J |                            |              |             |                   |

|---|----------------------------|--------------|-------------|-------------------|

|   |                            | ERROR        |             |                   |

|   | ANYWHERE WITHIN DATA FRAME | ERRFLAG (6b) | ERRDEL (8b) | IFS (= 3b) or OVL |

|   |                            | OVERLOAD     |             |                   |

|   | EOF or ERRDEL or OVLDEL    | OVLFLAG (6b) | OVLDEL (8b) | IFS (= 3b) or OVL |

|   |                            |              |             |                   |

### 2.1.1 DLC ENCODING

The Data Length Code (DLC) specifies the number of data bytes a message frame contains. Table 2-1 illustrates the encoding.

Table 2-1: DLC Encoding

| Frame              | DLC  | Number of Data Bytes |

|--------------------|------|----------------------|

| CAN 2.0 and CAN FD | 0    | 0                    |

|                    | 1    | 1                    |

|                    | 2    | 2                    |

|                    | 3    | 3                    |

|                    | 4    | 4                    |

|                    | 5    | 5                    |

|                    | 6    | 6                    |

|                    | 7    | 7                    |

|                    | 8    | 8                    |

| CAN 2.0            | 9-15 | 8                    |

| CAN FD             | 9    | 12                   |

|                    | 10   | 16                   |

|                    | 11   | 20                   |

|                    | 12   | 24                   |

|                    | 13   | 32                   |

|                    | 14   | 48                   |

|                    | 15   | 64                   |

### 3.0 CONTROL REGISTERS

CAN FD operations are controlled using the following Special Function Registers (SFRs). The following registers are described later in this section:

- Register 3-1: CxCONL

- Register 3-2: CxCONH

- Register 3-3: CxNBTCFGL

- Register 3-4: CxNBTCFGH

- Register 3-5: CxDBTCFGL

- Register 3-6: CxDBTCFGH

- Register 3-7: CxTDCL

- Register 3-8: CxTDCH

- Register 3-9: CxTBCL

- Register 3-10: CxTBCH

- Register 3-11: CxTSCONL

- Register 3-12: CxTSCONH

- Register 3-13: CxVECL

- Register 3-14: CxVECH

- Register 3-15: CxINTL

- Register 3-16: CxINTH

- Register 3-17: CxRXIFL

- Register 3-18: CxRXIFH

- Register 3-19: CxRXOVIFL

- Register 3-20: CxRXOVIFH

- Register 3-21: CxTXIFL

- Register 3-22: CxTXIFH

- Register 3-23: CxTXATIFL

- Register 3-24: CxTXATIFH

- Register 3-25: CxTXREQL

- Register 3-26: CxTXREQH

- Register 3-27: CxFIFOBAL

- Register 3-28: CxFIFOBAH

- Register 3-29: CxTXQCONL

- Register 3-30: CxTXQCONH

- Register 3-31: CxTXQSTA

- Register 3-32: CxFIFOCONxLRegister 3-33: CxFIFOCONxH

- Register 3-34: CxFIFOSTAx

- Register 3-35: CxTEFCONL

- Register 3-36: CxTEFCONH

- Register 3-37: CxTEFSTA

- Register 3-38: CxFIFOUAxL

- Register 3-39: CxFIFOUAxH

- Register 3-40: CxTEFUAL

- Register 3-41: CxTEFUAH

- Register 3-42: CxTXQUAL

- Register 3-43: CxTXQUAH

- Register 3-44: CxTRECL

- Register 3-45: CxTRECH

- Register 3-46: CxBDIAG0L

- Register 3-47: CxBDIAG0H

- Register 3-48: CxBDIAG1L

- Register 3-49: CxBDIAG1H

- Register 3-50: CxFLTCONxL

- Register 3-51: CxFLTCONxH

- Register 3-52: CxFLTOBJxL

- Register 3-53: CxFLTOBJxH

- Register 3-54: CxMASKxL

- Register 3-55: CxMASKxH

#### Register 3-1: CxCONL: CAN Control Register Low

| R/W-0  | U-0 | R/W-0 | R/W-0  | R-0  | R/W-1 | R/W-1 | R/W-1                 |

|--------|-----|-------|--------|------|-------|-------|-----------------------|

| CON    | _   | SIDL  | BRSDIS | BUSY | WFT1  | WFT0  | WAKFIL <sup>(1)</sup> |

| bit 15 |     |       |        |      |       |       | bit 8                 |

| R/W-0                 | R/W-1                 | R/W-1                   | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-----------------------|-----------------------|-------------------------|--------|--------|--------|--------|--------|

| CLKSEL <sup>(1)</sup> | PXEDIS <sup>(1)</sup> | ISOCRCEN <sup>(1)</sup> | DNCNT4 | DNCNT3 | DNCNT2 | DNCNT1 | DNCNT0 |

| bit 7                 |                       |                         |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 CON: CAN Enable bit

1 = CAN module is enabled

0 = CAN module is disabled

bit 14 **Unimplemented:** Read as '0'

bit 13 SIDL: CAN Stop in Idle Control bit

1 = Stops module operation in Idle mode

0 = Does not stop module operation in Idle mode

bit 12 BRSDIS: Bit Rate Switching (BRS) Disable bit

1 = Bit Rate Switching is disabled, regardless of BRS in the transmit message object

0 = Bit Rate Switching depends on BRS in the transmit message object

bit 11 BUSY: CAN Module is Busy bit

${\tt 1}$  = The CAN module is active

0 = The CAN module is inactive

bit 10-9 WFT[1:0]: Selectable Wake-up Filter Time bits

11 **= T11**FILTER

10 = T10FILTER

01 **= T01**FILTER

00 **= T00**FILTER

bit 8 **WAKFIL:** Enable CAN Bus Line Wake-up Filter bit<sup>(1)</sup>

1 = Uses CAN bus line filter for wake-up

0 = CAN bus line filter is not used for wake-up

bit 7 CLKSEL: Module Clock Source Select bit (1)

1 = Auxiliary clock is active when module is enabled

0 = Clock from the CAN clock generator is active when the module is enabled

bit 6 **PXEDIS:** Protocol Exception Event Detection Disabled bit<sup>(1)</sup>

A recessive "reserved bit" following a recessive FDF bit is called a "Protocol Exception".

1 = Protocol exception is treated as a form error

0 = If a protocol exception is detected, CAN will enter the bus integrating state

bit 5 **ISOCRCEN:** Enable ISO CRC in CAN FD Frames bit<sup>(1)</sup>

1 = Includes Stuff Bit Count in CRC field and uses non-zero CRC initialization vector

0 = Does not include Stuff Bit Count in CRC field and uses CRC initialization vector with all zeros

### Register 3-1: CxCONL: CAN Control Register Low (Continued)

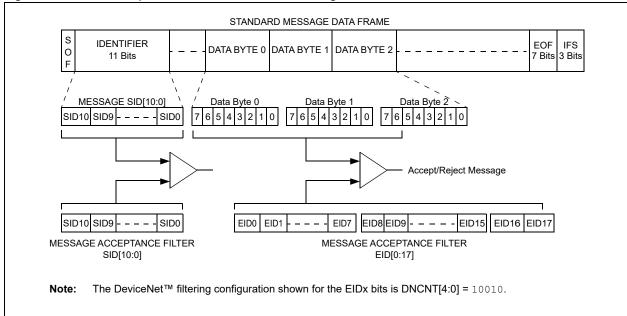

bit 4-0 **DNCNT[4:0]:** DeviceNet™ Filter Bit Number bits

10011-11111 = Invalid selection (compares up to 18 bits of data with EIDx)

10010 = Compares up to Data Byte 2, bit 6 with EID17

. . .

00001 = Compares up to Data Byte 0, bit 7 with EID0

00000 = Does not compare data bytes

#### Register 3-2: CxCONH: CAN Control Register High

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | S/HC-0 | R/W-1  | R/W-0  | R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TXBWS3 | TXBWS2 | TXBWS1 | TXBWS0 | ABAT   | REQOP2 | REQOP1 | REQOP0 |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R-1    | R-0    | R-0    | R/W-1                | R/W-1               | R/W-0                  | R/W-0                | R/W-0                |

|--------|--------|--------|----------------------|---------------------|------------------------|----------------------|----------------------|

| OPMOD2 | OPMOD1 | OPMOD0 | TXQEN <sup>(1)</sup> | STEF <sup>(1)</sup> | SERRLOM <sup>(1)</sup> | ESIGM <sup>(1)</sup> | RTXAT <sup>(1)</sup> |

| bit 7  |        |        |                      |                     |                        |                      | bit 0                |

| Legend:           | S = Settable bit | HC = Hardware Clearable bit        |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15-12 **TXBWS[3:0]:** Transmit Bandwidth Sharing bits

1111-1100 = 4096

1011 = 2048

1010 = 1024

1001 = 512

1000 = 256

0111 = 1280110 = 64

0101 = 32

0100 = 16

0011 = 8

0010 = 4

0001 = 2

0000 = No delay

bit 11 ABAT: Abort All Pending Transmissions bit

1 = Signals all transmit buffers to abort transmission

0 = Module will clear this bit when all transmissions are aborted

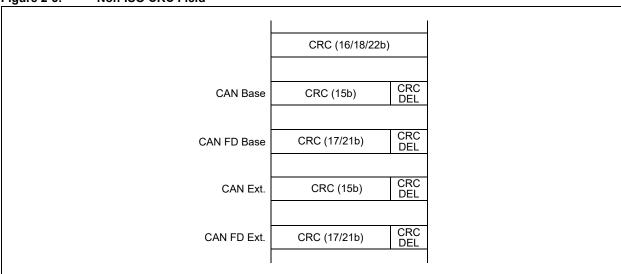

bit 10-8 **REQOP[2:0]:** Request Operation Mode bits

111 = Sets Restricted Operation mode

110 = Sets Normal CAN 2.0 mode; error frames on CAN FD frames

101 = Sets External Loopback mode

100 = Sets Configuration mode

011 = Sets Listen Only mode

010 = Sets Internal Loopback mode

001 = Sets Disable mode

000 = Sets Normal CAN FD mode; supports mixing of full CAN FD and Classic CAN 2.0 frames

bit 7-5 **OPMOD[2:0]:** Operation Mode Status bits

111 = Module is in Restricted Operation mode

110 = Module is in Normal CAN 2.0 mode; error frames on CAN FD frames

101 = Module is in External Loopback mode

100 = Module is in Configuration mode

011 = Module is in Listen Only mode

010 = Module is in Internal Loopback mode

001 = Module is in Disable mode

000 = Module is in Normal CAN FD mode; supports mixing of full CAN FD and Classic CAN 2.0 frames

bit 4 **TXQEN:** Enable Transmit Queue bit<sup>(1)</sup>

1 = Enables TXQ and reserves space in RAM

0 = Does not reserve space in RAM for TXQ

# **CAN FD Protocol Module**

#### Register 3-2: **CxCONH: CAN Control Register High (Continued)** STEF: Store in Transmit Event FIFO bit(1) bit 3 1 = Saves transmitted messages in TEF 0 = Does not save transmitted messages in TEF bit 2 SERRLOM: Transition to Listen Only Mode on System Error bit (1) 1 = Transitions to Listen Only mode 0 = Transitions to Restricted Operation mode bit 1 **ESIGM:** Transmit ESI in Gateway Mode bit<sup>(1)</sup> 1 = ESI is transmitted as recessive when the ESI of message is high or CAN controller is error passive 0 = ESI reflects error status of the CAN controller bit 0 RTXAT: Restrict Retransmission Attempts bit (1) 1 = Restricted retransmission attempts, uses TXAT[1:0] (CxFIFOCONxH[6:5]) 0 = Unlimited number of retransmission attempts, TXAT[1:0] bits will be ignored

**Note 1:** These bits can only be modified in Configuration mode (OPMOD[2:0] = 100).

# Register 3-3: CxNBTCFGL: CAN Nominal Bit Time Configuration Register Low<sup>(1)</sup>

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-1      | R/W-1 | R/W-1 | R/W-1 |

|--------|-------|-------|-------|------------|-------|-------|-------|

| _      |       |       |       | TSEG2[6:0] |       |       |       |

| bit 15 |       |       |       |            |       |       | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-1    | R/W-1 | R/W-1 | R/W-1 |

|-------|-------|-------|-------|----------|-------|-------|-------|

| _     |       |       |       | SJW[6:0] |       |       |       |

| bit 7 |       |       |       |          |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-8 **TSEG2[6:0]:** Time Segment 2 bits (Phase Segment 2)

111 1111 = Length is 128 x TQ

. . .

000 0000 = Length is 1 x TQ

bit 7 **Unimplemented:** Read as '0'

bit 6-0 **SJW[6:0]:** Synchronization Jump Width bits

111 1111 = Length is 128 x TQ

. . .

000 0000 = Length is  $1 \times TQ$

# Register 3-4: CxNBTCFGH: CAN Nominal Bit Time Configuration Register High<sup>(1)</sup>

| R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------|----------|-------|-------|-------|-------|-------|-------|--|

|        | BRP[7:0] |       |       |       |       |       |       |  |

| bit 15 |          |       |       |       |       |       |       |  |

| R/W-0      | R/W-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-0 | R/W-0 |  |  |

|------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| TSEG1[7:0] |       |       |       |       |       |       |       |  |  |

| bit 7      |       |       |       |       |       |       | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 BRP[7:0]: Baud Rate Prescaler bits

1111 1111 = TQ = 256/FCAN

. . .

0000 0000 = TQ = 1/FCAN

bit 7-0 **TSEG1[7:0]:** Time Segment 1 bits (Propagation Segment + Phase Segment 1)

1111 1111 = Length is 256 x TQ

0000 0000 = Length is 1 x TQ

**Note 1:** These bits can only be modified in Configuration mode (OPMOD[2:0] = 100).

## Register 3-5: CxDBTCFGL: CAN Data Bit Time Configuration Register Low<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-1  | R/W-1 |

|--------|-----|-----|-----|-------|-------|--------|-------|

| _      | _   | _   | _   |       | TSEG  | 2[3:0] |       |

| bit 15 |     |     |     |       |       |        | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-1  | R/W-1 |

|-------|-----|-----|-----|-------|-------|--------|-------|

| _     | _   | _   | _   |       | SJW   | /[3:0] |       |

| bit 7 |     |     |     |       |       |        | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 **Unimplemented:** Read as '0'

bit 11-8 **TSEG2[3:0]:** Time Segment 2 bits (Phase Segment 2)

1111 = Length is 16 x TQ

. . .

$0000 = \text{Length is } 1 \times \text{TQ}$

bit 7-4 **Unimplemented:** Read as '0'

bit 3-0 **SJW[3:0]:** Synchronization Jump Width bits

1111 = Length is 16 x TQ

• • •

$0000 = \text{Length is } 1 \times \text{TQ}$

#### CxDBTCFGH: CAN Data Bit Time Configuration Register High<sup>(1)</sup> Register 3-6:

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|----------|-------|-------|-------|-------|-------|-------|-------|--|--|

| BRP[7:0] |       |       |       |       |       |       |       |  |  |

| bit 15   |       |       |       |       |       |       | bit 8 |  |  |

| U-0   | U-0 | U-0 | R/W-0 | R/W-1 | R/W-1      | R/W-1 | R/W-0 |

|-------|-----|-----|-------|-------|------------|-------|-------|

| _     | _   | _   |       |       | TSEG1[4:0] |       |       |

| bit 7 |     |     |       |       |            |       | bit 0 |

R = Readable bit

Legend:

U = Unimplemented bit, read as '0' W = Writable bit

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 BRP[7:0]: Baud Rate Prescaler bits

1111 1111 = TQ = 256/FCAN

0000 0000 = TQ = 1/FCAN

bit 7-5 Unimplemented: Read as '0'

bit 4-0 TSEG1[4:0]: Time Segment 1 bits (Propagation Segment + Phase Segment 1)

1 1111 = Length is 32 x TQ

0 0000 = Length is 1 x TQ

**Note 1:** This register can only be modified in Configuration mode (OPMOD[2:0] = 100).

## Register 3-7: CxTDCL: CAN Transmitter Delay Compensation Register Low<sup>(1)</sup>

| U-0    | R/W-0 | R/W-0 | R/W-1 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-----------|-------|-------|-------|

| _      |       |       |       | TDCO[6:0] |       |       |       |

| bit 15 |       |       |       |           |       |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| _     | _   |       |       | TDC   | V[5:0] |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

```

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

-n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

```

```

bit 15

Unimplemented: Read as '0'

TDCO[6:0]: Transmitter Delay Compensation Offset bits (Secondary Sample Point (SSP))

111 1111 = -64 x TCAN

...

011 1111 = 63 x TCAN

...

000 0000 = 0 x TCAN

bit 7-6

Unimplemented: Read as '0'

bit 5-0

TDCV[5:0]: Transmitter Delay Compensation Value bits (Secondary Sample Point (SSP))

11 1111 = 63 x TCAN

...

00 0000 = 0 x TCAN

```

**Note 1:** This register can only be modified in Configuration mode (OPMOD[2:0] = 100).

### Register 3-8: CxTDCH: CAN Transmitter Delay Compensation Register High<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0    | R/W-0   |

|--------|-----|-----|-----|-----|-----|----------|---------|

| _      | _   | _   | _   | _   | _   | EDGFLTEN | SID11EN |

| bit 15 |     |     |     |     |     |          | bit 8   |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-1   | R/W-0   |

|-------|-----|-----|-----|-----|-----|---------|---------|

| _     | _   | _   | _   | _   | _   | TDCMOD1 | TDCMOD0 |

| bit 7 |     |     |     |     |     |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-10 **Unimplemented:** Read as '0'

bit 9 EDGFLTEN: Enable Edge Filtering During Bus Integration State bit

1 = Edge filtering is enabled according to ISO11898-1:2015

0 = Edge filtering is disabled

bit 8 SID11EN: Enable 12-Bit SID in CAN FD Base Format Messages bit

1 = RRS is used as SID11 in CAN FD base format messages: SID[11:0] = {SID[10:0], SID11}

0 = Does not use RRS; SID[10:0]

bit 7-2 **Unimplemented:** Read as '0'

bit 1-0 TDCMOD[1:0]: Transmitter Delay Compensation mode bits (Secondary Sample Point (SSP))

10-11 = Auto: Measures delay and adds TDCO

01 = Manual: Does not measure, uses TDCV[5:0] + TDCO[6:0] from register

00 = Disables

# **CAN FD Protocol Module**

# Register 3-9: CxTBCL: CAN Time Base Counter Register Low<sup>(1,2)</sup>

| R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-----------|-------|-------|-------|-------|-------|-------|-------|--|--|

| TBC[15:8] |       |       |       |       |       |       |       |  |  |

| bit 15    |       |       |       |       |       |       | bit 8 |  |  |

| R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|----------|-------|-------|-------|-------|-------|-------|-------|--|--|

| TBC[7:0] |       |       |       |       |       |       |       |  |  |

| bit 7    |       |       |       |       |       |       | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 TBC[15:0] CAN Time Base Counter bits

This is a free-running timer that increments every TBCPRE[9:0] clock when TBCEN is set.

**Note 1:** The TBC will be stopped and reset when TBCEN = 0 to save power.

2: The TBC prescaler count will be reset on any write to CxTBCL/H (TBCPREx will be unaffected).

### Register 3-10: CxTBCH: CAN Time Base Counter Register High<sup>(1,2)</sup>

| R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| TBC[31:24] |       |       |       |       |       |       |       |  |  |  |

| bit 15     |       |       |       |       |       |       | bit 8 |  |  |  |

| R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------|------------|-------|-------|-------|-------|-------|-------|--|--|

|       | TBC[23:16] |       |       |       |       |       |       |  |  |

| bit 7 |            |       |       |       |       |       |       |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 TBC[31:16] CAN Time Base Counter bits

This is a free-running timer that increments every TBCPRE[9:0] clock when TBCEN is set.

Note 1: The Time Base Counter (TBC) will be stopped and reset when TBCEN = 0 to save power.

2: The TBC prescaler count will be reset on any write to CxTBCL/H (TBCPREx will be unaffected).

#### Register 3-11: CxTSCONL: CAN Timestamp Control Register Low

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0   |

|--------|-----|-----|-----|-----|-----|-------|---------|

| _      | _   | _   | _   | _   | _   | TBCPF | RE[9:8] |

| bit 15 |     |     |     |     |     |       | bit 8   |

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|

| TBCPRE[7:0] |       |       |       |       |       |       |       |

| bit 7       |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-10 **Unimplemented:** Read as '0'

bit 9-0 **TBCPRE[9:0]:** CAN Time Base Counter Prescaler bits

1023 = TBC increments every 1024 clocks

. . .

0 = TBC increments every 1 clock

### Register 3-12: CxTSCONH: CAN Timestamp Control Register High

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-----|-----|-------|-------|-------|

| _     | _   | _   | _   | _   | TSRES | TSEOF | TBCEN |

| bit 7 |     |     |     |     |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-3 **Unimplemented:** Read as '0'

bit 2 TSRES: Timestamp Reset bit (CAN FD frames only)

1 = At sample point of the bit following the FDF bit

0 = At sample point of Start-of-Frame (SOF)

bit 1 **TSEOF:** Timesstamp End-of-Frame (EOF) bit

1 = Timestamp when frame is taken valid (11898-1 10.7):

- RX no error until last, but one bit of EOF

- TX no error until the end of EOF

0 = Timestamp at "beginning" of frame:

- Classical Frame: At sample point of SOF

- FD Frame: see TSRES bit

bit 0 TBCEN: Time Base Counter (TBC) Enable bit

1 = Enables TBC

0 = Stops and resets TBC

#### Register 3-13: CxVECL: CAN Interrupt Code Register Low

| U-0    | U-0 | U-0 | R-0 | R-0 | R-0         | R-0 | R-0   |

|--------|-----|-----|-----|-----|-------------|-----|-------|

| _      | _   | _   |     |     | FILHIT[4:0] |     |       |

| bit 15 |     |     |     |     |             |     | bit 8 |

| U-0   | R-1 | R-0 | R-0 | R-0        | R-0 | R-0 | R-0   |

|-------|-----|-----|-----|------------|-----|-----|-------|

| _     |     |     |     | ICODE[6:0] |     |     |       |

| bit 7 |     |     |     |            |     |     | bit 0 |

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

-n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

bit 15-13 Unimplemented: Read as '0' bit 12-8 FILHIT[4:0]: Filter Hit Number bits 11111 = Filter 31 11110 = Filter 30 00001 = Filter 1 00000 = Filter 0 bit 7 Unimplemented: Read as '0' ICODE[6:0]: Interrupt Flag Code bits bit 6-0 1001011-1111111 = Reserved 1001010 = Transmit attempt interrupt (any bit in CxTXATIF is set) 1001001 = Transmit event FIFO interrupt (any bit in CxTEFSTA is set) 1001000 = Invalid message occurred (IVMIF/IE) 1000111 = CAN module mode change occurred (MODIF/IE) 1000110 = CAN timer overflow (TBCIF/IE) 1000101 = RX/TX MAB overflow/underflow (RX: Message received before previous message was saved to memory; TX: Can't feed TX MAB fast enough to transmit consistent data) (SERRIF/IE) 1000100 = Address error interrupt (illegal FIFO address presented to system) (SERRIF/IE) 1000011 = Receive FIFO overflow interrupt (any bit in CxRXOVIF is set) 1000010 = Wake-up interrupt (WAKIF/WAKIE) 1000001 = Error interrupt (CERRIF/IE) 1000000 = **No interrupt** 0100000-0111111 = Reserved 0011111 = FIFO 31 interrupt (TFIF31 or RFIF31 is set) 0000001 = FIFO 1 Interrupt (TFIF1 or RFIF1 is set) 0000000 = FIFO 0 Interrupt (TFIF0 is set)

#### Register 3-14: CxVECH: CAN Interrupt Code Register High

| U-0    | R-1 | R-0 | R-0 | R-0         | R-0 | R-0 | R-0   |

|--------|-----|-----|-----|-------------|-----|-----|-------|

| _      |     |     |     | RXCODE[6:0] |     |     |       |

| bit 15 |     |     |     |             |     |     | bit 8 |

| U-0   | R-1 | R-0 | R-0 | R-0         | R-0 | R-0 | R-0   |

|-------|-----|-----|-----|-------------|-----|-----|-------|

| _     |     |     |     | TXCODE[6:0] |     |     |       |

| bit 7 |     |     |     |             |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-8 **RXCODE[6:0]:** Receive Interrupt Flag Code bits

1000001-1111111 = Reserved

1000000 = **No interrupt**

0100000-0111111 = Reserved

0011111 = FIFO 31 interrupt (RFIF[31] is set)

. . .

0000010 = FIFO 2 interrupt (RFIF[2] is set) 0000001 = FIFO 1 interrupt (RFIF[1] is set)

0000000 = Reserved; FIFO 0 cannot receive

bit 7 **Unimplemented:** Read as '0'

bit 6-0 **TXCODE[6:0]:** Transmit Interrupt Flag Code bits

1000001-1111111 = Reserved

1000000 = No interrupt

0100000-0111111 = Reserved

0011111 = FIFO 31 interrupt (TFIF[31] is set)

• • •

0000001 = FIFO 1 interrupt (TFIF[1] is set) 0000000 = FIFO 0 interrupt (TFIF[0] is set)

#### Register 3-15: CxINTL: CAN Interrupt Register Low

| HS/C-0               | HS/C-0               | HS/C-0                | HS/C-0                | R-0    | R-0    | U-0 | U-0   |

|----------------------|----------------------|-----------------------|-----------------------|--------|--------|-----|-------|

| IVMIF <sup>(1)</sup> | WAKIF <sup>(1)</sup> | CERRIF <sup>(1)</sup> | SERRIF <sup>(1)</sup> | RXOVIF | TXATIF | _   | _     |

| bit 15               |                      |                       |                       |        |        |     | bit 8 |

| U-0   | U-0 | U-0 | R-0   | HS/C-0               | HS/C-0               | R-0  | R-0   |

|-------|-----|-----|-------|----------------------|----------------------|------|-------|

| _     | _   | _   | TEFIF | MODIF <sup>(1)</sup> | TBCIF <sup>(1)</sup> | RXIF | TXIF  |

| bit 7 |     |     |       |                      |                      |      | bit 0 |

| Legend:           | HS = Hardware Settable bit | C = Clearable bit           |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

**IVMIF:** Invalid Message Interrupt Flag bit<sup>(1)</sup> bit 15 1 = Invalid message interrupt occurred 0 = No invalid message interrupt **WAKIF:** Bus Wake-up Activity Interrupt Flag bit<sup>(1)</sup> bit 14 1 = Wake-up activity interrupt occurred 0 = No wake-up activity interrupt bit 13 **CERRIF:** CAN Bus Error Interrupt Flag bit<sup>(1)</sup> 1 = CAN bus error interrupt occurred 0 = No CAN bus error interrupt bit 12 **SERRIF:** System Error Interrupt Flag bit<sup>(1)</sup> 1 = System error interrupt occurred 0 = No system error interrupt bit 11 **RXOVIF:** Receive Buffer Overflow Interrupt Flag bit 1 = Receive buffer overflow interrupt occurred 0 = No receive buffer overflow interrupt bit 10 **TXATIF:** Transmit Attempt Interrupt Flag bit 1 = Transmit attempt interrupt occurred 0 = No transmit attempt interrupt bit 9-5 Unimplemented: Read as '0' bit 4 **TEFIF:** Transmit Event FIFO Interrupt Flag bit 1 = Transmit event FIFO interrupt occurred 0 = No transmit event FIFO bit 3 **MODIF:** CAN Mode Change Interrupt Flag bit<sup>(1)</sup> 1 = CAN module mode change occurred (OPMOD[2:0] have changed to reflect REQOP[2:0]) 0 = No mode change occurred **TBCIF:** CAN Timer Overflow Interrupt Flag bit<sup>(1)</sup> bit 2 1 = TBC has overflowed 0 = TBC has not overflow bit 1 **RXIF:** Receive Object Interrupt Flag bit 1 = Receive object interrupt is pending 0 = No receive object interrupts are pending bit 0 **TXIF:** Transmit Object Interrupt Flag bit 1 = Transmit object interrupt is pending 0 = No transmit object interrupts are pending

Note 1: CxINTL: Flags are set by hardware and cleared by application.

#### Register 3-16: CxINTH: CAN Interrupt Register High

| R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | U-0 | U-0   |

|--------|-------|--------|--------|--------|--------|-----|-------|

| IVMIE  | WAKIE | CERRIE | SERRIE | RXOVIE | TXATIE | _   | _     |

| bit 15 |       |        |        |        |        |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| _     | _   | _   | TEFIE | MODIE | TBCIE | RXIE  | TXIE  |

| bit 7 |     |     |       |       |       |       | bit 0 |

| ∟eg | ena: |  |

|-----|------|--|

| ·   |      |  |

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **IVMIE:** Invalid Message Interrupt Enable bit

1 = Invalid message interrupt is enabled

0 = Invalid message interrupt is disabled

bit 14 WAKIE: Bus Wake-up Activity Interrupt Enable bit

1 = Wake-up activity interrupt is enabled0 = Wake-up activity interrupt is disabled

viano ap donvity interrupt lo dicabled

bit 13 CERRIE: CAN Bus Error Interrupt Enable bit

1 = CAN bus error interrupt is enabled0 = CAN bus error interrupt is disabled

bit 12 SERRIE: System Error Interrupt Enable bit

1 = System error interrupt is enabled

0 = System error interrupt is disabled

bit 11 RXOVIE: Receive Buffer Overflow Interrupt Enable bit

1 = Receive buffer overflow interrupt is enabled

0 = Receive buffer overflow interrupt is disabled

bit 10 TXATIE: Transmit Attempt Interrupt Enable bit

1 = Transmit attempt interrupt is enabled

0 = Transmit attempt interrupt is disabled

bit 9-5 **Unimplemented:** Read as '0'

bit 4 **TEFIE:** Transmit Event FIFO Interrupt Enable bit

1 = Transmit event FIFO interrupt is enabled

0 = Transmit event FIFO interrupt is disabled

bit 3 MODIE: Mode Change Interrupt Enable bit

1 = Mode change interrupt is enabled

0 = Mode change interrupt is disabled

bit 2 TBCIE: CAN Timer Interrupt Enable bit

1 = CAN timer interrupt is enabled

0 = CAN timer interrupt is disabled

bit 1 RXIE: Receive Object Interrupt Enable bit

1 = Receive object interrupt is enabled

0 = Receive object interrupt is disabled

bit 0 **TXIE:** Transmit Object Interrupt Enable bit

1 = Transmit object interrupt is enabled

0 = Transmit object interrupt is disabled

# Register 3-17: CxRXIFL: CAN Receive Interrupt Status Register Low<sup>(1)</sup>

| R-0        | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |

|------------|-----|-----|-----|-----|-----|-----|-------|--|

| RFIF[15:8] |     |     |     |     |     |     |       |  |

| bit 15     |     |     |     |     |     |     | bit 8 |  |

| R-0   | R-0 | R-0 | R-0       | R-0 | R-0 | R-0 | U-0   |

|-------|-----|-----|-----------|-----|-----|-----|-------|

|       |     |     | RFIF[7:1] |     |     |     | _     |

| bit 7 |     |     |           |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-1 RFIF[15:1]: Receive FIFO Interrupt Pending bits

1 = One or more enabled receive FIFO interrupts are pending

0 = No enabled receive FIFO interrupts are pending

bit 0 **Unimplemented:** Read as '0'

Note 1: CxRXIFL: FIFO: RFIFx = 'or' of enabled RX FIFO flags (flags need to be cleared in the FIFO register).

### Register 3-18: CxRXIFH: CAN Receive Interrupt Status Register High<sup>(1)</sup>

| R-0         | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |  |

|-------------|-----|-----|-----|-----|-----|-----|-------|--|--|

| RFIF[31:24] |     |     |     |     |     |     |       |  |  |

| bit 15      |     |     |     |     |     |     | bit 8 |  |  |

| R-0         | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |  |  |

|-------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| RFIF[23:16] |     |     |     |     |     |     |     |  |  |

| bit 7       |     |     |     |     |     |     |     |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 RFIF[31:16]: Receive FIFO Interrupt Pending bits

1 = One or more enabled receive FIFO interrupts are pending

0 = No enabled receive FIFO interrupts are pending

Note 1: CxRXIFH: FIFO: RFIFx = 'or' of enabled RX FIFO flags (flags need to be cleared in the FIFO register).

# Register 3-19: CxRXOVIFL: CAN Receive Overflow Interrupt Status Register Low<sup>(1)</sup>

| R-0          | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |  |  |

|--------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| RFOVIF[15:8] |     |     |     |     |     |     |     |  |  |

| bit 15       |     |     |     |     |     |     |     |  |  |

| R-0   | R-0 | R-0 | R-0         | R-0 | R-0 | R-0 | U-0   |

|-------|-----|-----|-------------|-----|-----|-----|-------|

|       |     |     | RFOVIF[7:1] |     |     |     | _     |

| bit 7 |     |     |             |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-1 RFOVIF[15:1]: Receive FIFO Overflow Interrupt Pending bits

1 = Interrupt is pending0 = Interrupt is not pending

bit 0 **Unimplemented:** Read as '0'

Note 1: CxRXOVIFL: FIFO: RFOVIFx (flag needs to be cleared in the FIFO register).

# Register 3-20: CxRXOVIFH: CAN Receive Overflow Interrupt Status Register High<sup>(1)</sup>

| R-0    | R-0 | R-0 | R-0    | R-0     | R-0 | R-0 | R-0   |

|--------|-----|-----|--------|---------|-----|-----|-------|

|        |     |     | RFOVIF | [31:24] |     |     |       |

| bit 15 |     |     |        |         |     |     | bit 8 |

| R-0   | R-0 | R-0 | R-0    | R-0     | R-0 | R-0 | R-0   |

|-------|-----|-----|--------|---------|-----|-----|-------|

|       |     |     | RFOVIF | [23:16] |     |     |       |

| bit 7 |     |     |        |         |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 RFOVIF[31:16]: Receive FIFO Overflow Interrupt Pending bits

1 = Interrupt is pending0 = Interrupt is not pending

Note 1: CxRXOVIFH: FIFO: RFOVIFx (flag needs to be cleared in the FIFO register).

### Register 3-21: CxTXIFL: CAN Transmit Interrupt Status Register Low<sup>(1)</sup>

| R-0        | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |

|------------|-----|-----|-----|-----|-----|-----|-------|--|

| TFIF[15:8] |     |     |     |     |     |     |       |  |

| bit 15     |     |     |     |     |     |     | bit 8 |  |

| R-0   | R-0 | R-0 | R-0    | R-0                 | R-0 | R-0 | R-0   |

|-------|-----|-----|--------|---------------------|-----|-----|-------|

|       |     |     | TFIF[7 | 7:0] <sup>(2)</sup> |     |     |       |

| bit 7 |     |     |        |                     |     |     | bit 0 |

### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 TFIF[15:0]: Transmit FIFO/TXQ Interrupt Pending bits<sup>(2)</sup>

1 = One or more enabled transmit FIFO/TXQ interrupts are pending

0 = No enabled transmit FIFO/TXQ interrupts are pending

Note 1: CxTXIFL: FIFO: TFIFx = 'or' of the enabled TX FIFO flags (flags need to be cleared in the FIFO register).

2: TFIF0 is for the TXQ.

### Register 3-22: CxTXIFH: CAN Transmit Interrupt Status Register High<sup>(1)</sup>

| R-0    | R-0 | R-0 | R-0    | R-0    | R-0 | R-0 | R-0   |

|--------|-----|-----|--------|--------|-----|-----|-------|

|        |     |     | TFIF[3 | 31:24] |     |     |       |

| bit 15 |     |     |        |        |     |     | bit 8 |

| R-0   | R-0 | R-0 | R-0    | R-0    | R-0 | R-0 | R-0   |

|-------|-----|-----|--------|--------|-----|-----|-------|

|       |     |     | TFIF[2 | 23:16] |     |     |       |

| bit 7 |     |     |        |        |     |     | bit 0 |

### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 TFIF[31:16]: Transmit FIFO/TXQ Interrupt Pending bits

1 = One or more enabled transmit FIFO/TXQ interrupts are pending

0 = No enabled transmit FIFO/TXQ interrupts are pending

Note 1: CxTXIFH: FIFO: TFIFx = 'or' of the enabled TX FIFO flags (flags need to be cleared in the FIFO register).

### Register 3-23: CxTXATIFL: CAN Transmit Attempt Interrupt Status Register Low<sup>(1)</sup>

| R-0    | R-0 | R-0 | R-0    | R-0    | R-0 | R-0 | R-0   |

|--------|-----|-----|--------|--------|-----|-----|-------|

|        |     |     | TFATIF | [15:8] |     |     |       |

| bit 15 |     |     |        |        |     |     | bit 8 |

| R-0   | R-0 | R-0 | R-0    | R-0                  | R-0 | R-0 | R-0   |

|-------|-----|-----|--------|----------------------|-----|-----|-------|

|       |     |     | TFATIF | [7:0] <sup>(2)</sup> |     |     |       |

| bit 7 |     |     |        |                      |     |     | bit 0 |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **TFATIF[15:0]:** Transmit FIFO/TXQ Attempt Interrupt Pending bits<sup>(2)</sup>

1 = Interrupt is pending0 = Interrupt is not pending

**Note 1:** CxTXATIFL: FIFO: TFATIFx (flag needs to be cleared in the FIFO register).

2: TFATIF0 is for the TXQ.

### Register 3-24: CxTXATIFH: CAN Transmit Attempt Interrupt Status Register High<sup>(1)</sup>

| R-0           | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |

|---------------|-----|-----|-----|-----|-----|-----|-------|--|

| TFATIF[31:24] |     |     |     |     |     |     |       |  |

| bit 15        |     |     |     |     |     |     | bit 8 |  |

| R-0           | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |

|---------------|-----|-----|-----|-----|-----|-----|-------|--|

| TFATIF[23:16] |     |     |     |     |     |     |       |  |

| bit 7         |     |     |     |     |     |     | bit 0 |  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **TFATIF[31:16]:** Transmit FIFO/TXQ Attempt Interrupt Pending bits

1 = Interrupt is pending

0 = Interrupt is not pending

Note 1: CxTXATIFH: FIFO: TFATIFx (flag needs to be cleared in the FIFO register).

#### Register 3-25: CxTXREQL: CAN Transmit Request Register Low

| R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|

| TXREQ[15:8] |       |       |       |       |       |       |       |  |

| bit 15      |       |       |       |       |       |       | bit 8 |  |

| R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0  |

|-------|-------|-------|------------|-------|-------|-------|--------|

|       |       |       | TXREQ[7:1] |       |       |       | TXREQ0 |

| bit 7 |       |       |            |       |       |       | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

bit 15-1 **TXREQ[15:0]:** Message Send Request bits

TXEN = 1 (object configured as a transmit object):

Setting this bit to '1' requests sending a message. The bit will automatically clear when the message(s) queued in the object is (are) successfully sent. This bit can NOT be used for aborting a transmission.

TXEN = 0 (object configured as a receive object):

This bit has no effect.

bit 0 TXREQ0: Transmit Queue Message Send Request bit

Setting this bit to '1' requests sending a message. The bit will automatically clear when the message(s) queued in the object is (are) successfully sent. This bit can NOT be used for aborting a transmission.

#### Register 3-26: CxTXREQH: CAN Transmit Request Register High

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|---------|-------|-------|-------|

|        |       |       | TXREQ | [31:24] |       |       |       |

| bit 15 |       |       |       |         |       |       | bit 8 |

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|

| TXREQ[23:16] |       |       |       |       |       |       |       |  |

| bit 7        |       |       |       |       |       |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 15-0 **TXREQ[31:16]:** Message Send Request bits

TXEN = 1 (object configured as a transmit object):

Setting this bit to '1' requests sending a message. The bit will automatically clear when the message(s) queued in the object is (are) successfully sent. This bit can NOT be used for aborting a transmission.

TXEN = 0 (object configured as a receive object):

This bit has no effect.

#### Register 3-27: CxFIFOBAL: CAN Message Memory Base Address Register Low

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0           | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|-----------------|-------|-------|-------|

|        |       |       | FIFOBA | <b>\</b> [15:8] |       |       |       |

| bit 15 |       |       |        |                 |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | U-0 <sup>(1)</sup> | U-0 <sup>(1)</sup> |

|-------|-------|-------|-------|-------|-------|--------------------|--------------------|

|       |       |       |       |       |       |                    |                    |

| bit 7 |       |       |       |       |       |                    | bit 0              |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

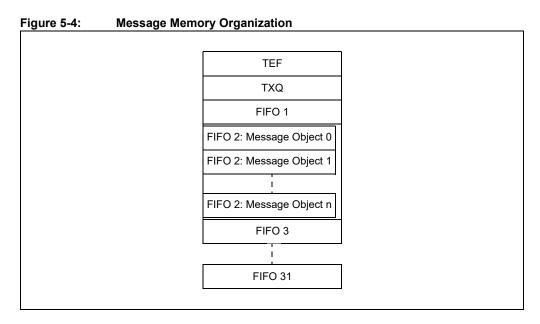

bit 15-0 FIFOBA[15:0]: Message Memory Base Address bits

Defines the base address for the transmit event FIFO followed by the message objects.

Note 1: Bits[1:0] are forced to '0' to be 32-bit word aligned.

### Register 3-28: CxFIFOBAH: CAN Message Memory Base Address Register High

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|---------------|-------|-------|-------|-------|-------|-------|-------|

| FIFOBA[31:24] |       |       |       |       |       |       |       |

| bit 15        |       |       |       |       |       |       | bit 8 |

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|---------------|-------|-------|-------|-------|-------|-------|-------|

| FIFOBA[23:16] |       |       |       |       |       |       |       |

| bit 7         |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 FIFOBA[31:16]: Message Memory Base Address bits

Defines the base address for the transmit event FIFO followed by the message objects.

# Register 3-29: CxTXQCONL: CAN Transmit Queue Control Register Low

| U-0    | U-0 | U-0 | U-0 | U-0 | S/HC-1 | R/W/HC-0 | S/HC-0 |

|--------|-----|-----|-----|-----|--------|----------|--------|

| _      | _   | _   | _   | _   | FRESET | TXREQ    | UINC   |

| bit 15 |     |     |     |     |        |          | bit 8  |

| R-1                 | U-0 | U-0 | R/W-0  | U-0 | R/W-0  | U-0 | R/W-0  |

|---------------------|-----|-----|--------|-----|--------|-----|--------|

| TXEN <sup>(1)</sup> | _   | _   | TXATIE | _   | TXQEIE | _   | TXQNIE |

| bit 7               |     |     |        |     |        |     | bit 0  |

| Legend:           | S = Settable bit | HC = Hardware Clearable bit        |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15-11 | Unimplemented: Read as '0'                                                                                                                          |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10    | FRESET: FIFO Reset bit                                                                                                                              |

|           | 1 = FIFO will be reset when bit is set, cleared by hardware when FIFO is reset; user should poll whether this bit is clear before taking any action |

|           | 0 = No effect                                                                                                                                       |

| bit 9     | TXREQ: Message Send Request bit                                                                                                                     |

|           | 1 = Requests sending a message; the bit will automatically clear when all the messages queued in<br>the TXQ are successfully sent                   |

|           | 0 = Clearing the bit to '0' while set ('1') will request a message abort                                                                            |

| bit 8     | UINC: Increment Head/Tail bit                                                                                                                       |

|           | When this bit is set, the FIFO head will increment by a single message.                                                                             |

| bit 7     | TXEN: TX Enable bit <sup>(1)</sup>                                                                                                                  |

|           | 1 = Transmit Message Queue. This bit always reads as '1'.                                                                                           |

| bit 6-5   | Unimplemented: Read as '0'                                                                                                                          |

| bit 4     | TXATIE: Transmit Attempts Exhausted Interrupt Enable bit                                                                                            |

|           | 1 = Enables interrupt                                                                                                                               |

|           | 0 = Disables interrupt                                                                                                                              |

| bit 3     | Unimplemented: Read as '0'                                                                                                                          |

| bit 2     | TXQEIE: Transmit Queue Empty Interrupt Enable bit                                                                                                   |

|           | <ul><li>1 = Interrupt is enabled for TXQ empty</li><li>0 = Interrupt is disabled for TXQ empty</li></ul>                                            |

| bit 1     | Unimplemented: Read as '0'                                                                                                                          |

| bit 0     | TXQNIE: Transmit Queue Not Full Interrupt Enable bit                                                                                                |

|           | 1 = Interrupt is enabled for TXQ not full                                                                                                           |

|           | 0 = Interrupt is disabled for TXQ not full                                                                                                          |

|           |                                                                                                                                                     |

Note 1: Please refer to the specific device data sheet for the Reset value of the TXEN bit.

#### Register 3-30: CxTXQCONH: CAN Transmit Queue Control Register High

| R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|------------------------|------------------------|------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| PLSIZE2 <sup>(1)</sup> | PLSIZE1 <sup>(1)</sup> | PLSIZE0 <sup>(1)</sup> | FSIZE4 <sup>(1)</sup> | FSIZE3 <sup>(1)</sup> | FSIZE2 <sup>(1)</sup> | FSIZE1 <sup>(1)</sup> | FSIZE0 <sup>(1)</sup> |

| bit 15                 |                        |                        |                       |                       |                       |                       | bit 8                 |

| U-0   | R/W-1 | R/W-1 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|--------|--------|--------|--------|--------|

| _     | TXAT1 | TXAT0 | TXPRI4 | TXPRI3 | TXPRI2 | TXPRI1 | TXPRI0 |

| bit 7 |       |       |        |        |        |        | bit 0  |

| Legend:           |                                                         |                      |                    |  |

|-------------------|---------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                        | '0' = Bit is cleared | x = Bit is unknown |  |

```

PLSIZE[2:0]: Payload Size bits(1)

bit 15-13

111 = 64 data bytes

110 = 48 data bytes

101 = 32 data bytes

100 = 24 data bytes

011 = 20 data bytes

010 = 16 data bytes

001 = 12 data bytes

000 = 8 data bytes

FSIZE[4:0]: FIFO Size bits<sup>(1)</sup>

bit 12-8

11111 = FIFO is 32 messages deep

00010 = FIFO is 3 messages deep

00001 = FIFO is 2 messages deep

00000 = FIFO is 1 message deep

bit 7

Unimplemented: Read as '0'

bit 6-5

TXAT[1:0]: Retransmission Attempts bits

This feature is enabled when RTXAT (CxCONH[0]) is set.

11 = Unlimited number of retransmission attempts

10 = Unlimited number of retransmission attempts

01 = Three retransmission attempts

00 = Disable retransmission attempts

bit 4-0

TXPRI[4:0]: Message Transmit Priority bits

11111 = Highest message priority

00000 = Lowest message priority

```

Note 1: These bits can only be modified in Configuration mode (OPMOD[2:0] = 100).

#### Register 3-31: CxTXQSTA: CAN Transmit Queue Status Register

| U-0    | U-0 | U-0 | R-0                   | R-0                   | R-0                   | R-0                   | R-0                   |

|--------|-----|-----|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| _      | _   | _   | TXQCI4 <sup>(1)</sup> | TXQCI3 <sup>(1)</sup> | TXQCI2 <sup>(1)</sup> | TXQCI1 <sup>(1)</sup> | TXQCI0 <sup>(1)</sup> |

| bit 15 |     |     |                       |                       |                       |                       | bit 8                 |

| R-0                  | R-0                   | R-0                  | HS/C-0 | U-0 | R-1    | U-0 | R-1    |

|----------------------|-----------------------|----------------------|--------|-----|--------|-----|--------|

| TXABT <sup>(2)</sup> | TXLARB <sup>(2)</sup> | TXERR <sup>(2)</sup> | TXATIF | _   | TXQEIF | _   | TXQNIF |

| bit 7                |                       |                      |        |     |        |     | bit 0  |

| Legend:           | C = Clearable bit | HS = Hardware Settable bit         |                    |  |

|-------------------|-------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **TXQCI[4:0]:** Transmit Queue Message Index bits<sup>(1)</sup>

A read of this register will return an index to the message that the FIFO will next attempt to transmit.

bit 7 **TXABT:** Message Aborted Status bit<sup>(2)</sup>

1 = Message was aborted

0 = Message completed successfully

bit 6 **TXLARB:** Message Lost Arbitration Status bit<sup>(2)</sup>

1 = Message lost arbitration while being sent

0 = Message did not lose arbitration while being sent

bit 5 **TXERR:** Error Detected During Transmission bit<sup>(2)</sup>

1 = A bus error occurred while the message was being sent

${\tt 0}$  = A bus error did not occur while the message was being sent

bit 4 **TXATIF:** Transmit Attempts Exhausted Interrupt Pending bit

1 = Interrupt is pending

0 = Interrupt is not pending

bit 3 **Unimplemented:** Read as '0'

bit 2 TXQEIF: Transmit Queue Empty Interrupt Flag bit

1 = TXQ is empty

0 = TXQ is not empty, at least 1 message is queued to be transmitted

bit 1 **Unimplemented:** Read as '0'

bit 0 **TXQNIF:** Transmit Queue Not Full Interrupt Flag bit

1 = TXQ is not full

0 = TXQ is full

Note 1: The TXQCI[4:0] bits give a zero-indexed value to the message in the TXQ. If the TXQ is four messages deep (FSIZE = 3), TXQCIx will take on a value of 0 to 3, depending on the state of the TXQ.

2: These bits are updated when a message completes (or aborts) or when the TXQ is reset.

#### Register 3-32: CxFIFOCONxL: CAN FIFO Control Register x (x = 1 to 31) Low

| U-0    | U-0 | U-0 | U-0 | U-0 | S/HC-1 | R/W/HC-0 | S/HC-0 |

|--------|-----|-----|-----|-----|--------|----------|--------|

| _      | _   | _   | _   | _   | FRESET | TXREQ    | UINC   |

| bit 15 |     |     |     |     |        |          | bit 8  |

| R/W-0 | R/W-0 | R/W-0                 | R/W-0  | R/W-0  | R/W-0    | R/W-0    | R/W-0    |

|-------|-------|-----------------------|--------|--------|----------|----------|----------|

| TXEN  | RTREN | RXTSEN <sup>(1)</sup> | TXATIE | RXOVIE | TFERFFIE | TFHRFHIE | TFNRFNIE |

| bit 7 |       |                       |        |        |          |          | bit 0    |

| Legend:           | S = Settable bit | HC = Hardware Clearable bit        |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-11 **Unimplemented:** Read as '0'

bit 10 FRESET: FIFO Reset bit

1 = FIFO will be reset when bit is set, cleared by hardware when FIFO is reset; user should poll whether this bit is clear before taking any action

0 = No effect

bit 9 TXREQ: Message Send Request bit

TXEN = 1 (FIFO configured as a transmit FIFO):

1 = Requests sending a message; the bit will automatically clear when all the messages queued in the FIFO are successfully sent

0 = Clearing the bit to '0' while set ('1') will request a message abort

TXEN = 0 (FIFO configured as a receive FIFO):

This bit has no effect.

bit 8 **UINC:** Increment Head/Tail bit

TXEN = 1 (FIFO configured as a transmit FIFO):

When this bit is set, the FIFO head will increment by a single message.

TXEN = 0 (FIFO configured as a receive FIFO):

When this bit is set, the FIFO tail will increment by a single message.

bit 7 TXEN: TX/RX Buffer Selection bit

1 = Transmits message object

0 = Receives message object

bit 6 RTREN: Auto-Remote Transmit (RTR) Enable bit

1 = When a Remote Transmit is received, TXREQ will be set

0 = When a Remote Transmit is received, TXREQ will be unaffected

bit 5 **RXTSEN:** Received Message Timestamp Enable bit (1)

1 = Captures timestamp in received message object in RAM

0 = Does not capture time stamp

bit 4 TXATIE: Transmit Attempts Exhausted Interrupt Enable bit

1 = Enables interrupt

0 = Disables interrupt

bit 3 RXOVIE: Overflow Interrupt Enable bit

1 = Interrupt is enabled for overflow event

0 = Interrupt is disabled for overflow event

### Register 3-32: CxFIFOCONxL: CAN FIFO Control Register x (x = 1 to 31) Low (Continued)

bit 2 TFERFFIE: Transmit/Receive FIFO Empty/Full Interrupt Enable bit

TXEN = 1 (FIFO configured as a transmit FIFO):

Transmit FIFO Empty Interrupt Enable

1 = Interrupt is enabled for FIFO empty

0 = Interrupt is disabled for FIFO empty

TXEN = 0 (FIFO configured as a receive FIFO):

Receive FIFO Full Interrupt Enable 1 = Interrupt is enabled for FIFO full 0 = Interrupt is disabled for FIFO full

bit 1 TFHRFHIE: Transmit/Receive FIFO Half Empty/Half Full Interrupt Enable bit

TXEN = 1 (FIFO configured as a transmit FIFO):

Transmit FIFO Half Empty Interrupt Enable

1 = Interrupt is enabled for FIFO half empty

0 = Interrupt is disabled for FIFO half empty

TXEN = 0 (FIFO configured as a receive FIFO):

Receive FIFO Half Full Interrupt Enable

1 = Interrupt is enabled for FIFO half full

0 = Interrupt is disabled for FIFO half full

bit 0 TFNRFNIE: Transmit/Receive FIFO Not Full/Not Empty Interrupt Enable bit

TXEN = 1 (FIFO configured as a transmit FIFO):

Transmit FIFO Not Full Interrupt Enable

1 = Interrupt is enabled for FIFO not full

0 = Interrupt is disabled for FIFO not full

TXEN = 0 (FIFO configured as a receive FIFO):

Receive FIFO Not Empty Interrupt Enable

1 = Interrupt is enabled for FIFO not empty

0 = Interrupt is disabled for FIFO not empty

#### Register 3-33: CxFIFOCONxH: CAN FIFO Control Register x (x = 1 to 31) High

| R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|------------------------|------------------------|------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| PLSIZE2 <sup>(1)</sup> | PLSIZE1 <sup>(1)</sup> | PLSIZE0 <sup>(1)</sup> | FSIZE4 <sup>(1)</sup> | FSIZE3 <sup>(1)</sup> | FSIZE2 <sup>(1)</sup> | FSIZE1 <sup>(1)</sup> | FSIZE0 <sup>(1)</sup> |

| bit 15                 |                        |                        |                       |                       |                       |                       | bit 8                 |

| U-0   | R/W-1 | R/W-1 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|--------|--------|--------|--------|--------|

| _     | TXAT1 | TXAT0 | TXPRI4 | TXPRI3 | TXPRI2 | TXPRI1 | TXPRI0 |

| bit 7 |       |       |        |        |        |        | bit 0  |

| Legend:           |                                                     |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

```

PLSIZE[2:0]: Payload Size bits(1)

bit 15-13

111 = 64 data bytes

110 = 48 data bytes

101 = 32 data bytes

100 = 24 data bytes

011 = 20 data bytes

010 = 16 data bytes

001 = 12 data bytes

000 = 8 data bytes

FSIZE[4:0]: FIFO Size bits<sup>(1)</sup>

bit 12-8

11111 = FIFO is 32 messages deep

00010 = FIFO is 3 messages deep

00001 = FIFO is 2 messages deep

00000 = FIFO is 1 message deep

bit 7

Unimplemented: Read as '0'

bit 6-5

TXAT[1:0]: Retransmission Attempts bits

This feature is enabled when RTXAT (CxCONH[0]) is set.

11 = Unlimited number of retransmission attempts

10 = Unlimited number of retransmission attempts

01 = Three retransmission attempts

00 = Disables retransmission attempts

bit 4-0

TXPRI[4:0]: Message Transmit Priority bits

11111 = Highest message priority

00000 = Lowest message priority

```

**Note 1:** These bits can only be modified in Configuration mode (OPMOD[2:0] = 100).

#### Register 3-34: CxFIFOSTAx: CAN FIFO Status Register x (x = 1 to 31)

| U-0    | U-0 | U-0 | R-0                    | R-0                    | R-0                    | R-0                    | R-0                    |

|--------|-----|-----|------------------------|------------------------|------------------------|------------------------|------------------------|

| _      | _   | _   | FIFOCI4 <sup>(1)</sup> | FIFOCI3 <sup>(1)</sup> | FIFOCI2 <sup>(1)</sup> | FIFOCI1 <sup>(1)</sup> | FIFOCIO <sup>(1)</sup> |

| bit 15 |     |     |                        |                        |                        |                        | bit 8                  |

| R-0                  | R-0                   | R-0                  | HS/C-0 | HS/C-0 | R-0      | R-0      | R-0      |

|----------------------|-----------------------|----------------------|--------|--------|----------|----------|----------|

| TXABT <sup>(3)</sup> | TXLARB <sup>(2)</sup> | TXERR <sup>(2)</sup> | TXATIF | RXOVIF | TFERFFIF | TFHRFHIF | TFNRFNIF |

| bit 7                |                       |                      |        |        |          |          | bit 0    |

| Legend:           | C = Clearable bit | HS = Hardware Settable bit |                                    |  |  |

|-------------------|-------------------|----------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit      | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared       | x = Bit is unknown                 |  |  |

bit 15-13 **Unimplemented:** Read as '0'

bit 12-8 FIFOCI[4:0]: FIFO Message Index bits<sup>(1)</sup>

TXEN = 1 (FIFO configured as a transmit buffer):

A read of this register will return an index to the message that the FIFO will next attempt to transmit.

TXEN = 0 (FIFO configured as a receive buffer):

A read of this register will return an index to the message that the FIFO will use to save the next message.

bit 7 TXABT: Message Aborted Status bit (3)

1 = Message was aborted

0 = Message completed successfully

bit 6 TXLARB: Message Lost Arbitration Status bit (2)

1 = Message lost arbitration while being sent

0 = Message did not lose arbitration while being sent

bit 5 **TXERR:** Error Detected During Transmission bit<sup>(2)</sup>

1 = A bus error occurred while the message was being sent

${\tt 0}$  = A bus error did not occur while the message was being sent

bit 4 TXATIF: Transmit Attempts Exhausted Interrupt Pending bit

TXEN = 1 (FIFO configured as a transmit buffer):

1 = Interrupt is pending

0 = Interrupt is not pending

TXEN = 0 (FIFO configured as a receive buffer):

Unused, reads as '0'.

bit 3 RXOVIF: Receive FIFO Overflow Interrupt Flag bit

TXEN = 1 (FIFO configured as a transmit buffer):

Unused, reads as '0'.

TXEN = 0 (FIFO configured as a receive buffer):

1 = Overflow event has occurred

0 = No overflow event occurred

Note 1: FIFOCI[4:0] gives a zero-indexed value to the message in the FIFO. If the FIFO is four messages deep (FSIZE = 3), FIFOCIx will take on a value of 0 to 3, depending on the state of the FIFO.

- 2: This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- 3: This bit is reset on any read of this register or when the TXQ is reset.

### Register 3-34: CxFIFOSTAx: CAN FIFO Status Register x (x = 1 to 31) (Continued)

bit 2 TFERFFIF: Transmit/Receive FIFO Empty/Full Interrupt Flag bit

TXEN = 1 (FIFO configured as a transmit FIFO):

Transmit FIFO Empty Interrupt Flag

1 = FIFO is empty

0 = FIFO is not empty, at least one message is gueued to be transmitted

TXEN = 0 (FIFO configured as a receive FIFO):

Receive FIFO Full Interrupt Flag

1 = FIFO is full

0 = FIFO is not full

bit 1 TFHRFHIF: Transmit/Receive FIFO Half Empty/Half Full Interrupt Flag bit

TXEN = 1 (FIFO configured as a transmit FIFO):

Transmit FIFO Half Empty Interrupt Flag

1 = FIFO is ≤ half full

0 = FIFO is > half full

TXEN = 0 (FIFO configured as a receive FIFO):

Receive FIFO Half Full Interrupt Flag

1 = FIFO is ≥ half full 0 = FIFO is < half full

bit 0 TFNRFNIF: Transmit/Receive FIFO Not Full/Not Empty Interrupt Flag bit

TXEN = 1 (FIFO configured as a transmit FIFO):

Transmit FIFO Not Full Interrupt Flag

1 = FIFO is not full

0 = FIFO is full

TXEN = 0 (FIFO configured as a receive FIFO):

Receive FIFO Not Empty Interrupt Flag

1 = FIFO is not empty, has at least one message

0 = FIFO is empty

**Note 1:** FIFOCI[4:0] gives a zero-indexed value to the message in the FIFO. If the FIFO is four messages deep (FSIZE = 3), FIFOCIx will take on a value of 0 to 3, depending on the state of the FIFO.

- 2: This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- 3: This bit is reset on any read of this register or when the TXQ is reset.

#### Register 3-35: CxTEFCONL: CAN Transmit Event FIFO Control Register Low

| U-0    | U-0 | U-0 | U-0 | U-0 | S/HC-1 | U-0 | S/HC-0 |

|--------|-----|-----|-----|-----|--------|-----|--------|

| _      | _   | _   | _   | _   | FRESET | _   | UINC   |

| bit 15 |     |     |     |     |        |     | bit 8  |

| U-0   | U-0 | R/W-0                  | U-0 | R/W-0   | R/W-0  | R/W-0  | R/W-0   |

|-------|-----|------------------------|-----|---------|--------|--------|---------|

| _     | _   | TEFTSEN <sup>(1)</sup> | _   | TEFOVIE | TEFFIE | TEFHIE | TEFNEIE |

| bit 7 |     |                        |     |         |        |        | bit 0   |

| Legend:           | S = Settable bit | HC = Hardware Clearat  | ble bit            |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-11 **Unimplemented:** Read as '0' bit 10 **FRESET:** FIFO Reset bit

1 = FIFO will be reset when bit is set, cleared by hardware when FIFO is reset; the user should poll

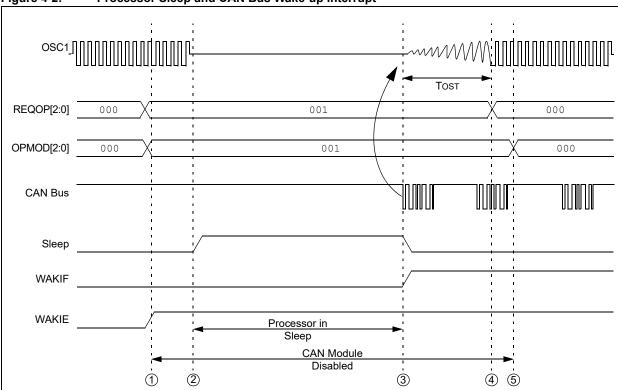

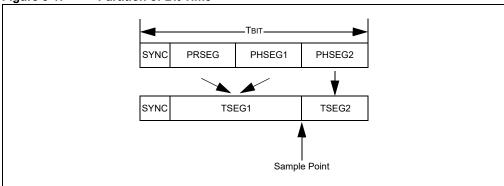

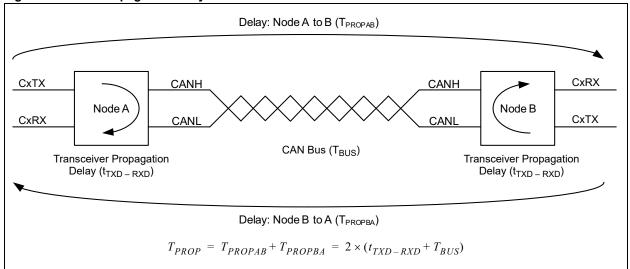

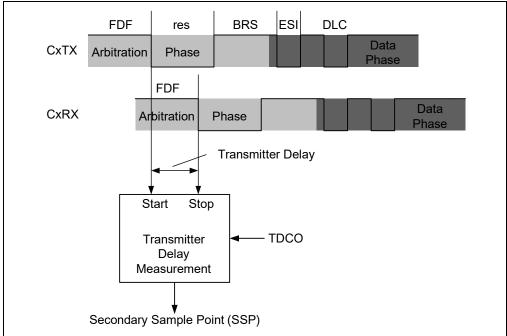

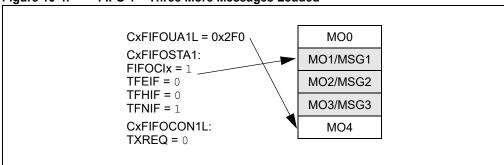

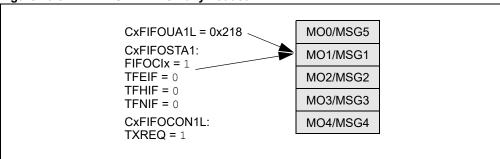

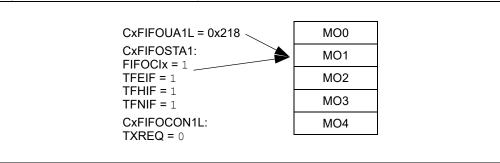

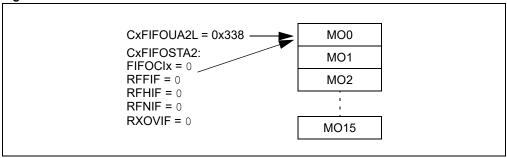

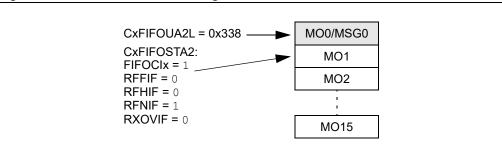

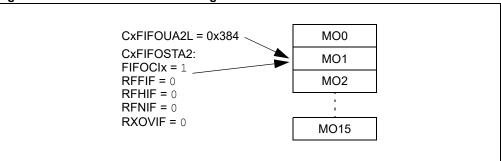

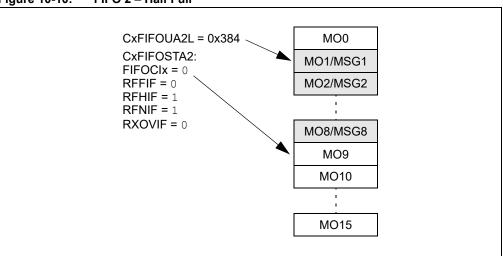

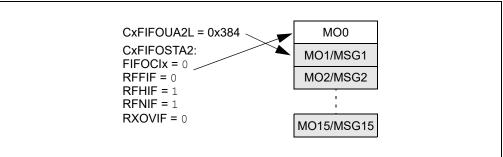

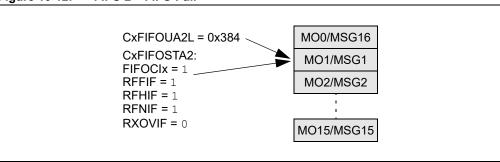

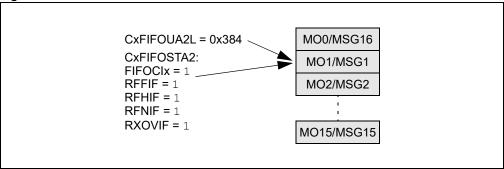

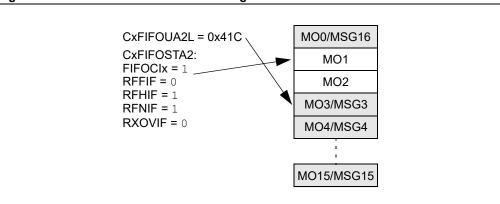

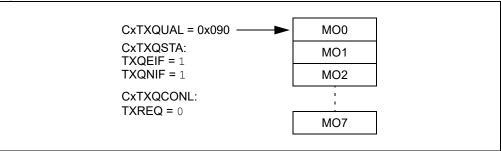

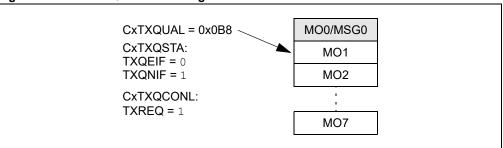

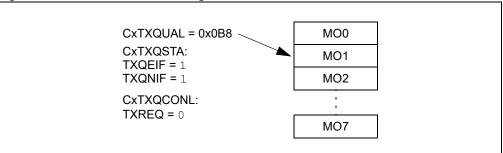

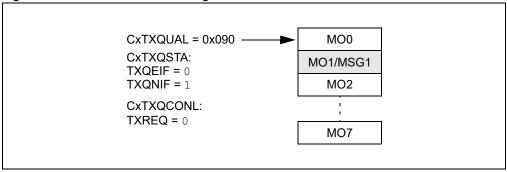

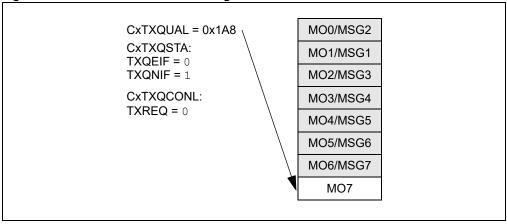

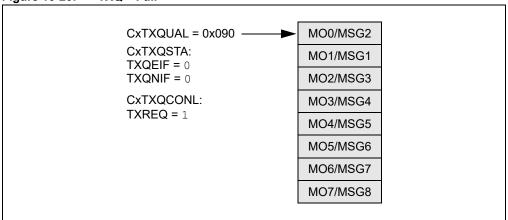

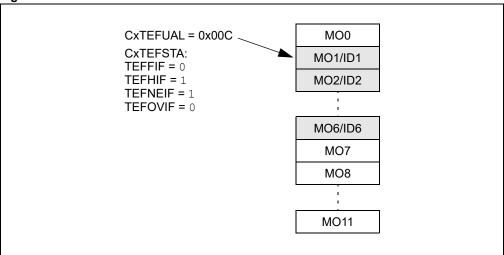

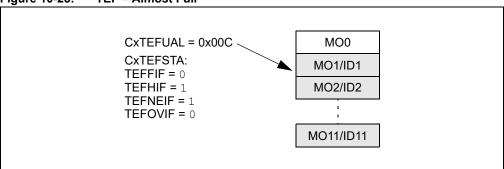

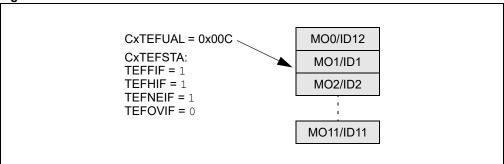

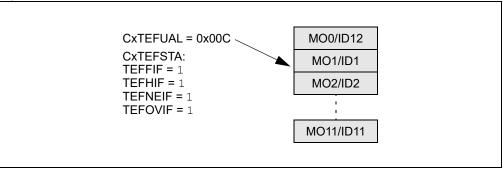

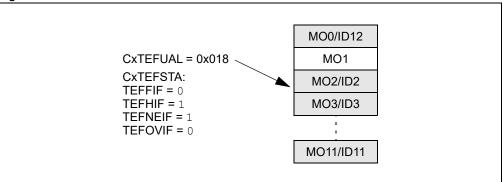

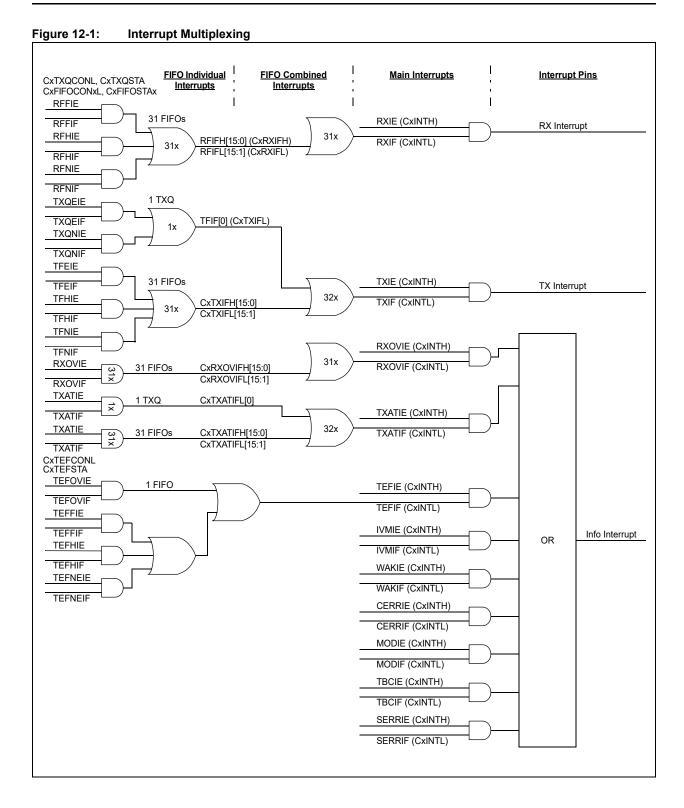

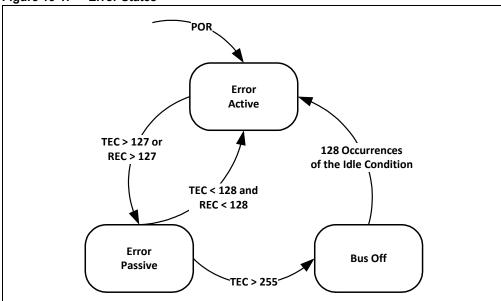

whether this bit is clear before taking any action