# ATF1502AS 5V 32-Macrocell CPLD Data Sheet

### **Features**

- High-Density, High-Performance, Electrically-Erasable Complex Programmable Logic Device:

- 32 macrocells

- 5 product terms per macrocell, expandable up to 40 per macrocell

- 44 pins

- 7.5 ns maximum pin-to-pin delay

- Registered operation up to 125 MHz

- Enhanced routing resources

- In-System Programmability (ISP) via JTAG

- · Flexible Logic Macrocell:

- D/T/Latch configurable flip-flops

- Global and individual register control signals

- Global and individual output enable

- Programmable output slew rate

- Programmable output open-collector option

- Maximum logic utilization by burying a register with a COM output

- · Advanced Power Management Features:

- Automatic 10 µA Standby (ATF1502ASL)

- Pin-controlled 1 mA Standby mode (typical)

- Programmable pin-keeper circuits on inputs and I/Os

- Reduced-power feature per macrocell

- Available in Commercial and Industrial Temperature Ranges

- · Robust EEPROM Technology:

- 100% tested

- Completely reprogrammable

- 10,000 Program/Erase cycles

- 20-year data retention

- 2000V ESD protection

- 200 mA latch-up immunity

- JTAG Boundary-Scan Testing to IEEE Std. 1149.1-1990 and 1149.1a-1993 Supported

- PCI-Compliant

- · Security Fuse Feature

- Green (Pb/Halide-Free/RoHS Compliant) Package Options

### **Enhanced Features**

- Improved Connectivity (Additional Feedback Routing, Alternate Input Routing)

- Output Enable Product Terms

- · Transparent-Latch Mode

- Combinatorial Output with Registered Feedback within any Macrocell

- · Three Global Clock Pins

- ITD (Input Transition Detection) Circuits on Global Clocks, Inputs and I/O (ATF1502ASL)

- · Fast Registered Input from Product Term

- · Programmable "Pin-keeper" Option

- · Vcc Power-Up Reset Option

- Pull-Up Option on JTAG Pins (TMS and TDI)

- · Advanced Power Management Features:

- Individual macrocell power option

- Edge-controlled power-down (ATF1502ASL)

- Disable ITD on global clocks (ATF1502ASL)

### **Packages**

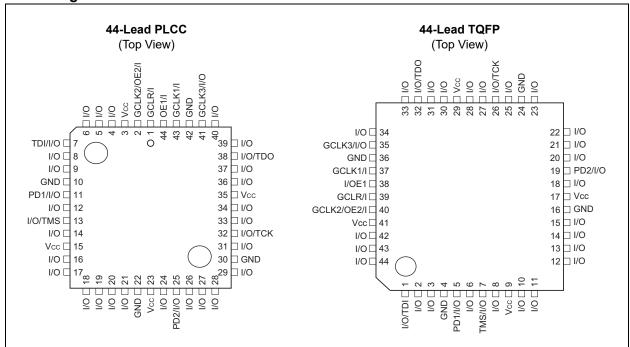

- · 44-Lead PLCC

- · 44-Lead TQFP

### **Description**

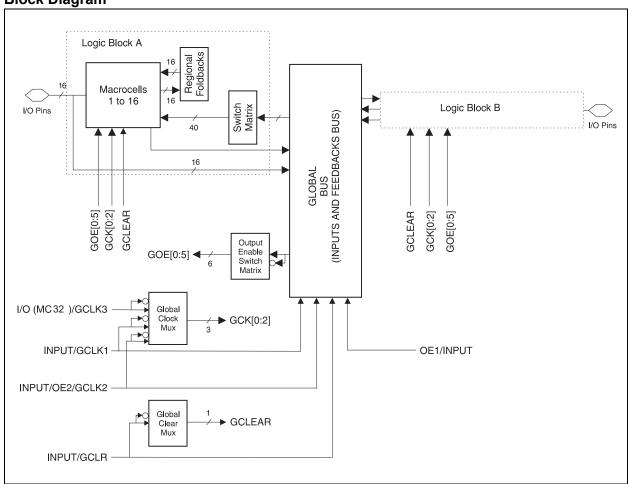

The ATF1502AS(L) is a high-performance, high-density complex programmable logic device (CPLD) that utilizes Microchip's proven electrically-erasable memory technology. With 32 logic macrocells and up to 36 inputs and I/Os, it easily integrates logic from several TTL, SSI, MSI, LSI and classic PLDs. The ATF1502AS(L)'s enhanced routing switch matrices increase usable gate count and the odds of successful pin-locked design modifications.

The ATF1502AS(L) has 32 bidirectional I/O pins and four dedicated input pins. Each dedicated input pin can also serve as a global control signal (register clock, register Reset or output enable). Each of these control signals can be selected for use individually within each macrocell.

Each of the 32 macrocells generates a buried feedback that goes to the global bus. Each input and I/O pin also feeds into the global bus. The switch matrix in each logic block then selects 40 individual signals from the global bus. Each macrocell also generates a foldback logic term that goes to a regional bus.

Cascade logic between macrocells in the ATF1502AS(L) allows fast, efficient generation of complex logic functions. The ATF1502AS(L) contains four such logic chains, each capable of creating sum term logic with a fan-in of up to 40 product terms.

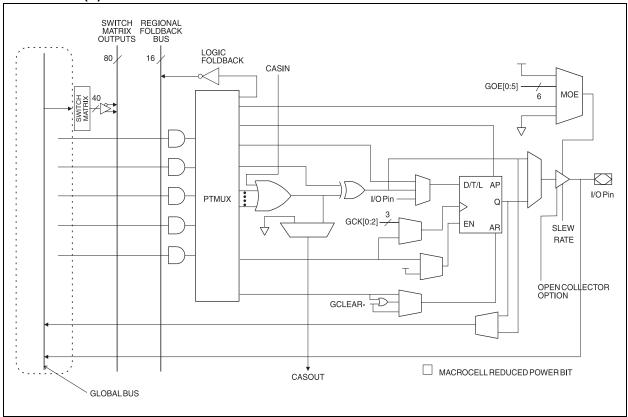

The ATF1502AS(L) macrocell (see ATF1502AS(L) Macrocell) is flexible enough to support highly complex logic functions operating at high speed. The macrocell consists of five sections: product terms and product term select multiplexer, OR/XOR/CASCADE logic, a flip-flop, output select and enable, and logic array inputs.

## ATF1502AS(L) Macrocell

## **Pin Configurations and Pinouts**

## **Block Diagram**

Unused product terms are automatically disabled by the compiler to decrease power consumption. A security fuse, when programmed, protects the contents of the ATF1502AS(L). Two bytes (16 bits) of User Signature are accessible to the user for purposes such as storing project name, part number, revision or date. The User Signature is accessible regardless of the state of the security fuse.

The ATF1502AS(L) device is an in-system programmable (ISP) device. It uses the industry-standard 4-pin JTAG interface (IEEE Std. 1149.1) and is fully compliant with JTAG's Boundary-scan Description Language (BSDL). ISP allows the device to be programmed without removing it from the printed circuit board. In addition to simplifying the manufacturing flow, ISP also allows design modifications to be made in the field via software.

#### PRODUCT TERMS AND SELECT MUX

Each ATF1502AS(L) macrocell has five product terms. Each product term receives as its inputs all signals from both the global bus and regional bus.

The product term select multiplexer (PTMUX) allocates the five product terms as needed to the macrocell logic gates and control signals. The PTMUX programming is determined by the design compiler, which selects the optimum macrocell configuration.

#### OR/XOR/CASCADE LOGIC

The ATF1502AS(L)'s logic structure is designed to efficiently support all types of logic. Within a single macrocell, all the product terms can be routed to the OR gate, creating a 5-input AND/OR sum term. With the addition of the CASIN from neighboring macrocells, this can be expanded to as many as 40 product terms with little additional delay.

The macrocell's XOR gate allows efficient implementation of compare and arithmetic functions. One input to the XOR comes from the OR sum term. The other XOR input can be a product term or a fixed high- or low-level. For combinatorial outputs, the fixed level input allows polarity selection. For registered functions, the fixed levels allow DeMorgan minimization of product terms. The XOR gate is also used to emulate T- and JK-type flip-flops.

### FLIP-FLOP

The ATF1502AS(L)'s flip-flop has very flexible data and control functions. The data input can come from either the XOR gate, from a separate product term or directly from the I/O pin. Selecting the separate product term allows creation of a buried registered feedback within a combinatorial output macrocell. (This feature is automatically implemented by the fitter software).

In addition to D, T, JK and SR operation, the flip-flop can also be configured as a flow-through latch. In this mode, data passes through when the clock is high and is latched when the clock is low.

The clock itself can either be one of the Global CLK Signal (GCK[0:2]) or an individual product term. The flip-flop changes state on the clock's rising edge. When the GCK signal is used as the clock, one of the macrocell product terms can be selected as a clock enable. When the clock enable function is active and the enable signal (product term) is low, all clock edges are ignored. The flip-flop's Asynchronous Reset signal (AR) can be either the Global Clear (GCLEAR), a product term, or always off. AR can also be a logic OR of GCLEAR with a product term. The Asynchronous Preset (AP) can be a product term or always off.

### EXTRA FEEDBACK

The ATF1502AS(L) macrocell output can be selected as registered or combinatorial. The extra buried feedback signal can be either combinatorial or a registered signal, regardless of whether the output is combinatorial or registered. (This enhancement function is automatically implemented by the fitter software.) Feedback of a buried combinatorial output allows the creation of a second latch within a macrocell.

#### I/O CONTROL

The output enable multiplexer (MOE) controls the output enable signal. Each I/O can be individually configured as an input, output or for bidirectional operation. The output enable for each macrocell can be selected from the true or compliment of the two output enable pins, a subset of the I/O pins, or a subset of the I/O macrocells. This selection is automatically done by the fitter software when the I/O is configured as an input, all macrocell resources are still available, including the buried feedback, expander and cascade logic.

### **GLOBAL BUS/SWITCH MATRIX**

The global bus contains all input and I/O pin signals as well as the buried feedback signal from all 32 macrocells. The switch matrix in each logic block receives as its inputs all signals from the global bus. Under software control, up to 40 of these signals can be selected as inputs to the logic block.

### **FOLDBACK BUS**

Each macrocell also generates a foldback product term. This signal goes to the regional bus and is available to sixteen macrocells. The foldback is an inverse polarity of one of the macrocell's product terms. The sixteen foldback terms in each region allow generation of high fan-in sum terms (up to sixteen product terms) with little additional delay.

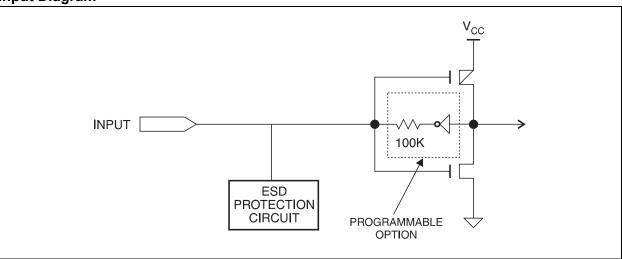

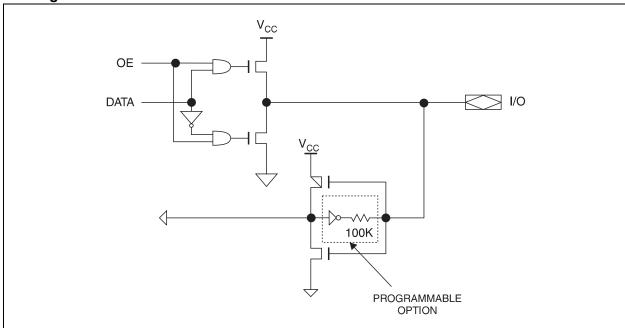

# Programmable Pin-Keeper Option for Inputs and I/Os

The ATF1502AS(L) offers the option of programming all input and I/O pins so that pin-keeper circuits can be utilized. When any pin is driven high or low and then subsequently left floating, it will stay at that previous high or low level. This circuitry prevents unused input and I/O lines from floating to intermediate voltage levels, which causes unnecessary power consumption and system noise. The keeper circuits eliminate the need for external pull-up resistors and eliminate their DC power consumption.

## **Input Diagram**

# I/O Diagram

### **Speed/Power Management**

The ATF1502AS(L) has several built-in speed and power management features. The ATF1502ASL contains circuitry that automatically puts the device into a low-power Standby mode when no logic transitions are occurring. This not only reduces power consumption during inactive periods, but also provides proportional power savings for most applications running at system speeds below 10 MHz.

To reduce power, each ATF1502AS(L) macrocell has a reduced-power bit feature. This feature allows individual macrocells to be configured for maximum power savings. This feature may be selected as a design option.

The ATF1502AS(L) also has an optional Power-Down mode. In this mode, current drops to below 5 mA. When the power-down option is selected, either PD1 or PD2 pins (or both) can be used to power down the part. The power-down option is selected in the design software or design source file. When enabled, the device goes into power-down when either PD1 or PD2 is high. In the Power-Down mode, all internal logic signals are latched and held, as are any enabled outputs.

All pin transitions are ignored until the PD pin is brought low. When the power-down feature is enabled, the PD1 or PD2 pin cannot be used as a logic input or output. However, the pin's macrocell may still be used to generate buried foldback and cascade logic signals.

All power-down AC characteristic parameters are computed from external input or I/O pins, with reduced-power bit turned on. For macrocells in Reduced-Power mode (reduced-power bit turned on), the reduced-power adder, trpa, must be added to the AC parameters, which include the data paths tlad, tlac, tlc, tacl or tach, ten and tsexp.

The ATF1502AS(L) macrocell also has an option whereby the power can be reduced on a per macrocell basis. By enabling this power-down option, macrocells that are not used in an application can be turned down, thereby reducing the overall power consumption of the device. This option is automatically set by the device fitter software.

Each output also has individual slew rate control. This may be used to reduce system noise by slowing down outputs that do not need to operate at maximum speed. Outputs default to slow switching and may be specified as fast switching in the design software or design file.

### **Design Software Support**

ATF1502AS(L) designs are supported by Microchip's ProChip Designer<sup>®</sup> and WinCUPL software tools as well as Precision Synthesis from Mentor Graphics as described in the "Programmable Logic Device Design Software Overview".

### **Power-Up Reset**

The ATF1502AS(L) is designed with a Power-up Reset, a feature critical for state machine initialization. At a point delayed slightly from VCC crossing VRST, all registers will be initialized and the state of each output will depend on the polarity of its buffer. However, due to the asynchronous nature of Reset and uncertainty of how VCC actually rises in the system, the following conditions are required:

- The Vcc rise must be monotonic

- After Reset occurs, all input and feedback setup times must be met before driving the clock pin high

- The clock must remain stable during Power-up Reset

The ATF1502AS(L) has two options for the hysteresis about the Reset level, VRST, Small and Large. Users of the POF2JED conversion utility should include the flag "-power\_reset" on the command line after "file-name.POF". To allow the registers to be properly reinitialized with the Large hysteresis option selected, the following condition is added:

If Vcc falls below 2.0V, it must shut off completely before the device is turned on again

When the Large hysteresis option is active, ICC is reduced by several hundred microamps as well.

Details on the power Reset hysteresis feature are available in the "ATF15XX Power-on Reset Hysteresis Feature" application note.

### **Security Fuse Usage**

A single fuse is provided to prevent unauthorized copying of the ATF1502AS(L) fuse patterns. Once programmed, fuse verify is inhibited. However, the 16-bit User Signature remains accessible.

### **Programming**

ATF1502AS(L) devices are in-system programmable (ISP) devices utilizing the 4-pin JTAG protocol. This capability eliminates package handling normally required for programming and facilitates rapid design iterations and field changes.

Microchip provides ISP hardware and software to allow programming of the ATF1502AS(L) via the PC. ISP is performed by using either a download cable, a comparable board tester or a simple microprocessor interface.

To facilitate ISP programming by the Automated Test Equipment (ATE) vendors, Serial Vector Format (SVF) files can be created by Microchip provided software utilities.

ATF1502AS(L) devices can also be programmed using standard third-party programmers. With a third-party programmer, the JTAG ISP port can be disabled, thereby allowing four additional I/O pins to be used for logic.

Refer to Programming of PLDs application note for more details.

## **ISP Programming Protection**

The ATF1502AS(L) has a special feature that locks the device and prevents the inputs and I/O from driving if the programming process is interrupted for any reason. The inputs and I/O default to high Z state during such a condition. In addition, the pin-keeper option preserves the former state during device programming, if this circuit was previously programmed on the device. This prevents disturbing the operation of other circuits in the system while the ATF1502AS(L) is being programmed via ISP.

All ATF1502AS(L) devices are initially shipped in the erased state, thereby making them ready to use for ISP.

### 1.0 ELECTRICAL SPECIFICATIONS

# Absolute Maximum Ratings (†)

| Temperature under bias                                   | 40°C to +85°C  |

|----------------------------------------------------------|----------------|

| Storage temperature                                      | 65°C to +150°C |

| Junction temperature under bias                          | +135°C         |

| Voltage on any pin with respect to ground <sup>(1)</sup> | -2.0V to +7.0V |

**† NOTICE:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

**Note 1:** Minimum voltage is -0.6V DC, which may undershoot to -2.0V for pulses of less than 20 ns. Maximum output pin voltage is Vcc + 0.75V DC, which may overshoot to 7.0V for pulses of less than 20 ns.

#### TABLE 1-1: DC AND AC OPERATING CONDITIONS

|                                 | Commercial   | Industrial     |

|---------------------------------|--------------|----------------|

| Operating Temperature (Ambient) | 0°C to +70°C | -40°C to +85°C |

| Vcc Power Supply                | 5V ± 5%      | 5V ± 10%       |

# TABLE 1-2: DC CHARACTERISTICS

| Symbol              | Parameter                                | Minimum | Typical | Maximum   | Units |                                             | Condition                 |                           |  |

|---------------------|------------------------------------------|---------|---------|-----------|-------|---------------------------------------------|---------------------------|---------------------------|--|

| lıL                 | Input or I/O Low Leakage<br>Current      | _       | -2      | -10       | μA    | VIN = GI                                    | VIN = GND                 |                           |  |

| lıн                 | Input or I/O High Leakage<br>Current     | 1       | 2       | 10        | μA    | VIN = V                                     | cc                        |                           |  |

| loz                 | Tri-State Output Off-State Current       | -40     |         | 40        | μA    | Vo = Vo                                     | c or GND                  |                           |  |

|                     |                                          | _       | 60      | _         | mA    | Comm.                                       | Std mode                  | Vcc = Max                 |  |

| Icc1                | Power Supply Current,                    | _       | 75      | _         | mA    | Ind.                                        | Statillode                | VIN = 0, VCC              |  |

| ICC I               | Standby                                  | _       | 10      | _         | μA    | Comm.                                       | "I "I -                   | Vcc = Max                 |  |

|                     |                                          | _       | 10      | _         | μA    | Ind.                                        | "L" mode                  | VIN = 0, VCC              |  |

| Icc2                | Power Supply Current,<br>Power-Down Mode | _       | 1       | 5         | mA    |                                             | "PD"<br>mode              | Vcc = Max<br>Vin = 0, Vcc |  |

| Icc3 <sup>(1)</sup> | Reduced Power Mode                       | _       | 35      | _         | mA    | Comm.                                       | Ctd made                  | Vcc = Max                 |  |

| 1003                | Supply Current, Standby                  | _       | 40      | _         | mA    | Ind.                                        | Std mode                  | VIN = 0, VCC              |  |

| VIL                 | Input Low Voltage                        | -0.3    | _       | 0.8       | V     |                                             |                           |                           |  |

| VIH                 | Input High Voltage                       | 2.0     | _       | Vcc + 0.3 | V     |                                             |                           |                           |  |

| Vol                 | Output Low Voltage (TTL)                 | _       | _       | 0.45      | V     | VIN = VIH or VIL<br>VCC = Min, IOL = 12 mA  |                           |                           |  |

| Vol                 | Output Low Voltage<br>(CMOS)             | _       | _       | 0.2       | ٧     | VIN = VIH or VIL<br>VCC = Min, IOL = 0.1 mA |                           |                           |  |

| Vон                 | Output High Voltage (TTL)                | 2.4     | _       | _         | V     | VIN = VI<br>VCC = M                         | н or VIL<br>1in, Ioн = -4 | I.0 mA                    |  |

Note 1: When macrocell reduced-power feature is enabled.

TABLE 1-3: PIN CAPACITANCE

|      | Typical | Maximum | Units | Conditions             |

|------|---------|---------|-------|------------------------|

| CIN  | 8       | 10      | pF    | VIN = 0V; f = 1.0 MHz  |

| Cı/o | 8       | 10      | pF    | Vout = 0V; f = 1.0 MHz |

- Note 1: Typical values for nominal supply voltage. This parameter is only sampled and is not 100% tested.

- 2: The OGI pin (high-voltage pin during programming) has a maximum capacitance of 12 pF.

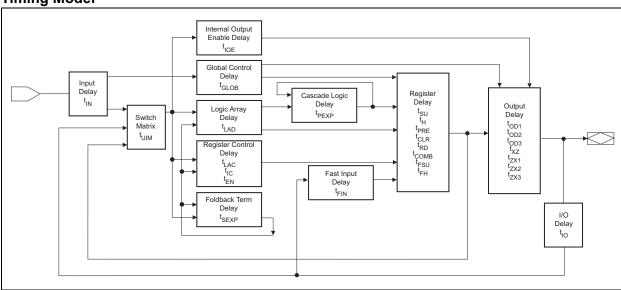

## **Timing Model**

TABLE 1-4: AC CHARACTERISTICS

| Complete | Downwardow.                                      | -         | 7   | -1   | 10   | -25  |      | l lusita |

|----------|--------------------------------------------------|-----------|-----|------|------|------|------|----------|

| Symbol   | Parameter                                        | Min. Max. |     | Min. | Max. | Min. | Max. | Units    |

| tPD1     | Input or Feedback to Non-Registered Output       | _         | 7.5 | _    | 10   | _    | 25   | ns       |

| tPD2     | I/O Input or Feedback to Non-Registered Feedback | _         | 7   | _    | 9    | _    | 25   | ns       |

| tsu      | Global Clock Setup Time                          | 6         | _   | 7    | _    | 20   | _    | ns       |

| tH       | Global Clock Hold Time                           | 0         | _   | 0    | _    | 0    | _    | ns       |

| tFSU     | Global Clock Setup Time of Fast Input            | 3         | _   | 3    | _    | 5    | _    | ns       |

| tFH      | Global Clock Hold Time of Fast Input             | 0.5       | _   | 0.5  | _    | 2    | _    | ns       |

| tCOP     | Global Clock to Output Delay                     | _         | 4.5 | _    | 5    | _    | 13   | ns       |

| tch      | Global Clock High Time                           | 3         | _   | 4    | _    | 7    | _    | ns       |

| tcL      | Global Clock Low Time                            | 3         | _   | 4    | _    | 7    | _    | ns       |

| tasu     | Array Clock Setup Time                           | 3         | _   | 3    | _    | 5    | _    | ns       |

| tah      | Array Clock Hold Time                            | 2         | _   | 3    | _    | 6    | _    | ns       |

| tACOP    | Array Clock Output Delay                         | _         | 7.5 | _    | 10   | _    | 25   | ns       |

Note 1: The trpa parameter must be added to the tLAD, tLAC, tIC, tACL or tACH, tEN and tSEXP parameters for macrocells running in the Reduced-Power mode.

TABLE 1-4: AC CHARACTERISTICS (CONTINUED)

| 0      | Para series                                                                           | -     | 7    | -1   | 10   | -2   | 25   | 11    |

|--------|---------------------------------------------------------------------------------------|-------|------|------|------|------|------|-------|

| Symbol | Parameter                                                                             | Min.  | Max. | Min. | Max. | Min. | Max. | Units |

| tach   | Array Clock High Time                                                                 | 3     | _    | 4    | _    | 10   | _    | ns    |

| tACL   | Array Clock Low Time                                                                  | 3     | _    | 4    | _    | 10   | _    | ns    |

| tcnt   | Minimum Clock Global Period                                                           | _     | 8    | _    | 10   | _    | 22   | ns    |

| fCNT   | Maximum Internal Global Clock Frequency                                               | 125   | _    | 100  | _    | 50   | _    | MHz   |

| tacnt  | Minimum Array Clock Period                                                            | _     | 8    | _    | 10   | _    | 22   | ns    |

| facnt  | Maximum Internal Array Clock Frequency                                                | 125   | _    | 100  | _    | 50   | _    | MHz   |

| fMAX   | Maximum Clock Frequency                                                               | 166.7 | _    | 125  | _    | 60   | _    | MHz   |

| tın    | Input Pad and Buffer Delay                                                            | _     | 0.5  | _    | 0.5  | _    | 2    | ns    |

| tio    | I/O Input Pad and Buffer Delay                                                        | _     | 0.5  | _    | 0.5  | _    | 2    | ns    |

| tFIN   | Fast Input Delay                                                                      | _     | 1    | _    | 1    | _    | 2    | ns    |

| tsexp  | Foldback Term Delay                                                                   | _     | 4    | _    | 5    | _    | 12   | ns    |

| tPEXP  | Cascade Logic Delay                                                                   | _     | 0.8  | _    | 0.8  | _    | 2    | ns    |

| tlad   | Logic Array Delay                                                                     | _     | 3    | _    | 5    | _    | 8    | ns    |

| tLAC   | Logic Control Delay                                                                   | _     | 3    | _    | 5    | _    | 8    | ns    |

| tioe   | Internal Output Enable Delay                                                          | _     | 2    | _    | 2    | _    | 4    | ns    |

| top1   | Output Buffer and Pad Delay (Slow slew rate = OFF; Vcc = 5.0V; CL = 35 pF)            | _     | 2    | _    | 1.5  | _    | 6    | ns    |

| tzx1   | Output Buffer Enable Delay (Slow slew rate = OFF; Vccio = 5.0V; CL = 35 pF)           | _     | 4.0  | _    | 5.0  | _    | 10   | ns    |

| tzx2   | Output Buffer Enable Delay (Slow slew rate = OFF; VCCIO = 3.3V; CL = 35 pF)           | _     | 4.5  | _    | 5.5  | _    | 10   | ns    |

| tzx3   | Output Buffer Enable Delay<br>(Slow slew rate = ON; Vccio = 5.0V/3.3V;<br>CL = 35 pF) | _     | 9    | _    | 9    | _    | 12   | ns    |

| txz    | Output Buffer Disable Delay (CL = 5 pF)                                               | _     | 4    | _    | 5    | _    | 8    | ns    |

| tsu    | Register Setup Time                                                                   | 3     | _    | 3    | _    | 6    | _    | ns    |

| tн     | Register Hold Time                                                                    | 2     | _    | 3    | _    | 6    | _    | ns    |

| trsu   | Register Setup Time of Fast Input                                                     | 3     | _    | 3    | _    | 3    | _    | ns    |

| tFH    | Register Hold Time of Fast Input                                                      | 0.5   | _    | 0.5  | _    | 5    | _    | ns    |

| trd    | Register Delay                                                                        | _     | 1    | _    | 2    | _    | 2    | ns    |

| tCOMB  | Combinatorial Delay                                                                   | _     | 1    | _    | 2    | _    | 2    | ns    |

| tic    | Array Clock Delay                                                                     | _     | 3    | _    | 5    | _    | 8    | ns    |

| tEN    | Register Enable Time                                                                  | _     | 3    | _    | 5    | _    | 8    | ns    |

| tGLOB  | Global Control Delay                                                                  | _     | 1    | _    | 1    | _    | 1    | ns    |

**Note 1:** The trpa parameter must be added to the tLAD, tLAC, tIC, tACL or tACH, tEN and tSEXP parameters for macrocells running in the Reduced-Power mode.

TABLE 1-4: AC CHARACTERISTICS (CONTINUED)

| Cymphol | Parameter                          | -7 |      | -7   |      | -10  |      | -25   |  | - Units |  |

|---------|------------------------------------|----|------|------|------|------|------|-------|--|---------|--|

| Symbol  | Symbol Parameter –                 |    | Max. | Min. | Max. | Min. | Max. | Units |  |         |  |

| tpre    | Register Preset Time               | _  | 2    | _    | 3    | _    | 6    | ns    |  |         |  |

| tclr    | Register Clear Time                | _  | 2    | _    | 3    | _    | 6    | ns    |  |         |  |

| tuim    | Switch Matrix Delay                | _  | 1    | _    | 1    | _    | 2    | ns    |  |         |  |

| trpa    | Reduced-Power Adder <sup>(1)</sup> | _  | 10   | _    | 11   | _    | 15   | ns    |  |         |  |

**Note 1:** The tRPA parameter must be added to the tLAD, tLAC, tIC, tACL or tACH, tEN and tSEXP parameters for macrocells running in the Reduced-Power mode.

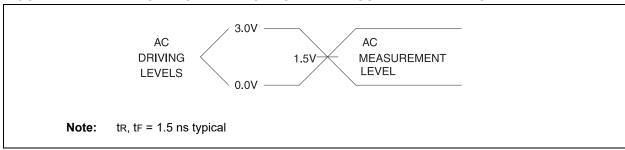

FIGURE 1-1: INPUT TEST WAVEFORMS AND MEASUREMENT LEVELS

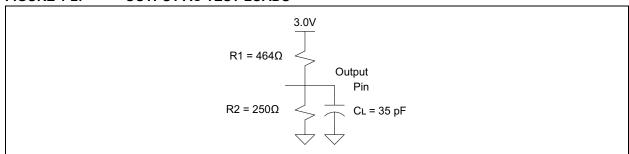

### FIGURE 1-2: OUTPUT AC TEST LOADS

## **Power-Down Mode**

The ATF1502AS(L) includes an optional pin-controlled power-down feature. When this mode is enabled, the PD pin acts as the power-down pin. When the PD pin is high, the device supply current is reduced to less than 5 mA. During power-down, all output data and internal logic states are latched internally and held. Therefore, all registered and combinatorial output data remain valid. Any outputs that were in a high Z state at the onset will remain at high Z. During power-down, all input signals except the Power-Down pin are blocked.

Input and I/O hold latches remain active to ensure that pins do not float to indeterminate levels, further reducing system power. The Power-Down mode feature is enabled in the logic design file or as a design software option. Designs using the Power-Down pin may not use the PD pin as a logic array input. However, all other PD pin macrocell resources may still be used, including the buried feedback and foldback product term array inputs.

TABLE 1-5: POWER-DOWN AC CHARACTERISTICS<sup>(1,2)</sup>

| Cymbal | Symbol Parameter -                            |           | 7  | -1   | 10   | -2   | 25   | Units |

|--------|-----------------------------------------------|-----------|----|------|------|------|------|-------|

| Symbol | Parameter                                     | Min. Max. |    | Min. | Max. | Min. | Max. | Units |

| tivdh  | Valid I, I/O before PD High                   | 7         | _  | 10   | _    | 25   | _    | ns    |

| tgvdh  | Valid OE <sup>(2)</sup> before PD High        | 7         | _  | 10   | _    | 25   | _    | ns    |

| tcvdh  | Valid Clock <sup>(2)</sup> before PD High     | 7         | _  | 10   | _    | 25   | _    | ns    |

| tDHIX  | I, I/O Don't Care after PD High               | _         | 12 | _    | 15   | _    | 35   | ns    |

| tDHGX  | OE <sup>(2)</sup> Don't Care after PD High    | _         | 12 | _    | 15   | _    | 35   | ns    |

| tDHCX  | Clock <sup>(2)</sup> Don't Care after PD High | _         | 12 | _    | 15   | _    | 35   | ns    |

| tdliv  | PD Low to Valid I, I/O                        | _         | 1  | _    | 1    | _    | 1    | μs    |

| tDLGV  | PD Low to Valid OE (Pin or Term)              | _         | 1  | _    | 1    | _    | 1    | μs    |

| tDLCV  | PD Low to Valid Clock (Pin or Term)           | _         | 1  | _    | 1    | _    | 1    | μs    |

| tDLOV  | PD Low to Valid Output                        | _         | 1  | _    | 1    | _    | 1    | μs    |

Note 1: For slow slew outputs, add tsso.

2: Pin or product term.

#### JTAG-BST/ISP Overview

The JTAG boundary-scan testing is controlled by the Test Access Port (TAP) controller in the ATF1502AS(L). The boundary-scan technique involves the inclusion of a shift-register stage (contained in a boundary-scan cell) adjacent to each component so that signals at component boundaries can be controlled and observed using scan testing principles. Each input pin and I/O pin has its own boundary-scan cell (BSC) in order to support boundary-scan testing.

The ATF1502AS(L) does not include a Test Reset (TRST) input pin because the TAP controller is automatically reset at power-up. The five JTAG modes supported include: SAMPLE/PRELOAD, EXTEST, BYPASS, IDCODE and HIGHZ.

The ATF1502AS(L) has the option of using four JTAG-standard I/O pins for boundary-scan testing (BST) and in-system programming (ISP) purposes.

The ATF1502AS(L) is programmable through the four JTAG pins using the IEEE standard JTAG programming protocol established by IEEE Standard 1149.1, using 5V TTL/CMOS-level programming signals from the ISP interface for in-system programming. The JTAG feature is a programmable option. If JTAG (BST or ISP) is not needed, then the four JTAG control pins are available as I/O pins.

## JTAG Boundary-Scan Cell (BSC)

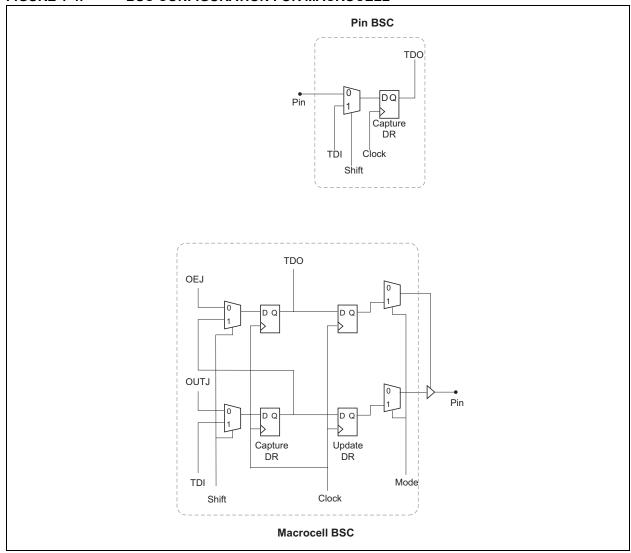

The ATF1502AS(L) contains up to 32 I/O pins and four input pins, depending on the device type and package type selected. Each input pin and I/O pin has its own boundary-scan cell (BSC) in order to support boundary-scan testing, as described in detail by IEEE Standard 1149.1. A typical BSC consists of three capture registers or scan registers and up to two update registers.

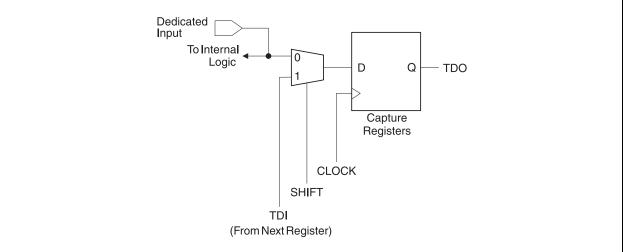

There are two types of BSCs: one for input or I/O pin and one for the macrocells. The BSCs in the device are chained together through the capture registers. Input to the capture register chain is fed in from the TDI pin while the output is directed to the TDO pin. Capture registers are used to capture active device data signals, to shift data in and out of the device and to load data into the update registers. Control signals are generated internally by the JTAG TAP controller. The BSC configuration for the input and I/O pins and macrocells are shown in Figure 1-3 and Figure 1-4. The BSCs and BSC configuration are also described in BSDL files.

FIGURE 1-3: BSC CONFIGURATION FOR INPUT AND I/O PINS (EXCEPT JTAG TAP PINS)

Note: The ATF1502AS(L) has pull-up option on TMS and TDI pins. This feature is selected as a design option.

FIGURE 1-4: BSC CONFIGURATION FOR MACROCELL

### **PCI Compliance**

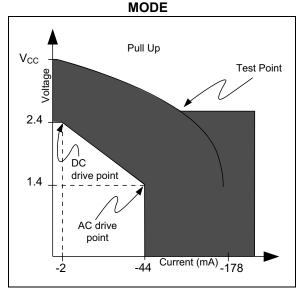

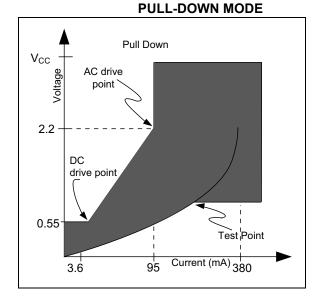

The ATF1502AS(L) supports the growing need in the industry to support the Peripheral Component Interconnect (PCI) interface standard in PCI-based designs and specifications. The PCI interface calls for high-current drivers that are much larger than the traditional TTL drivers. In general, PLDs and FPGAs parallel outputs to support the high-current load required by the PCI interface. The ATF1502AS(L) allows this without contributing to system noise while delivering low output-to-output skew.

FIGURE 1-5: PCI

VOLTAGE-TO-CURRENT

CURVES FOR +5.0V

SIGNALING IN PULL-UP

FIGURE 1-6: PCI

VOLTAGE-TO-CURRENT

CURVES FOR +5.0V

SIGNALING IN

TABLE 1-6: PCI DC CHARACTERISTICS

| Symbol | Parameter                                 | Min. | Max.      | Units | Conditions        |

|--------|-------------------------------------------|------|-----------|-------|-------------------|

| Vcc    | Supply Voltage                            | 4.75 | 5.25      | V     |                   |

| VIH    | Input High Voltage                        | 2.0  | Vcc + 0.5 | V     |                   |

| VIL    | Input Low Voltage                         | -0.5 | 0.8       | V     |                   |

| lін    | Input High Leakage Current <sup>(1)</sup> | _    | 70        | μΑ    | VIN = 2.7V        |

| lıL    | Input Low Leakage Current <sup>(1)</sup>  | _    | -70       | μΑ    | VIN = 0.5V        |

| Voн    | Output High Voltage                       | 2.4  | _         | V     | IOUT = -2 mA      |

| Vol    | Output Low Voltage                        | _    | 0.55      | V     | IOUT = 3 mA, 6 mA |

| CIN    | Input Pin Capacitance                     | _    | 10        | pF    |                   |

| CCLK   | CLK Pin Capacitance                       | _    | 12        | pF    |                   |

| CIDSEL | IDSEL Pin Capacitance                     | _    | 8         | pF    |                   |

| LPIN   | Pin Inductance                            | _    | 20        | nH    |                   |

Note 1: Leakage current is with pin-keeper off.

TABLE 1-7: PCI AC CHARACTERISTICS

| Symbol   | Parameter                                 | Min.                     | Max.                      | Units | Conditions        |

|----------|-------------------------------------------|--------------------------|---------------------------|-------|-------------------|

|          |                                           | -44                      | _                         | mA    | 0 < Vout ≤ 1.4    |

| lou(Ac)  | OH(AC) Switching Current High (Test High) | -44 + (Vout - 1.4)/0.024 | _                         | mA    | 1.4 < Vout < 2.4  |

| IOH(AC)  |                                           | _                        | Equation A <sup>(1)</sup> | mA    | 3.1 < Vout < Vcc  |

|          |                                           | _                        | -142                      | μA    | Vout = 3.1V       |

|          |                                           | 95                       | _                         | mA    | Vout > 2.2V       |

| lo. (AC) | Switching Current Low                     | Vout/0.023               | _                         | mA    | 2.2 > Vout > 0    |

| IOL(AC)  | (Test Point)                              | _                        | Equation B <sup>(2)</sup> | mA    | 0.1 > Vout >0     |

|          |                                           | _                        | 206                       | mA    | Vout = 0.71       |

| ICL      | Low Clamp Current                         | -25 + (Vin + 1)/0.015    | _                         | mA    | -5 < VIN ≤ -1     |

| SLEWR    | Output Rise Slew Rate                     | 1                        | 5                         | V/ns  | 0.4V to 2.4V load |

| SLEWF    | Output Fall Slew Rate                     | 1                        | 5                         | V/ns  | 2.4V to 0.4V load |

**Note 1:** Equation A: IOH = 11.9 (VOUT - 5.25) \* (VOUT + 2.45) for VCC > VOUT > 3.1V.

**<sup>2:</sup>** Equation B : IOL = 78.5 \* VOUT \* (4.4 - VOUT) for 0V < VOUT < 0.71V.

# 2.0 PINOUTS

TABLE 2-1: DEDICATED PINOUTS

| Dedicated Pin                                  | 44-Lead PLCC   | 44-Lead TQFP  |

|------------------------------------------------|----------------|---------------|

| INPUT/OE2 <sup>(1)</sup> /GCLK2 <sup>(2)</sup> | 2              | 40            |

| INPUT/GCLR <sup>(3)</sup>                      | 1              | 39            |

| INPUT/OE1 <sup>(1)</sup>                       | 44             | 38            |

| INPUT/GCLK1 <sup>(2)</sup>                     | 43             | 37            |

| I/O /GCLK3 <sup>(2)</sup>                      | 41             | 35            |

| I/O / PD (1,2) <sup>(4)</sup>                  | 11, 25         | 5, 19         |

| I/O / TDI (JTAG) <sup>(5)</sup>                | 7              | 1             |

| I/O / TMS (JTAG) <sup>(5)</sup>                | 13             | 7             |

| I/O / TCK (JTAG) <sup>(5)</sup>                | 32             | 26            |

| I/O / TDO (JTAG) <sup>(5)</sup>                | 38             | 32            |

| GND <sup>(6)</sup>                             | 10, 22, 30, 42 | 4, 16, 24, 36 |

| Vcc <sup>(7)</sup>                             | 3, 15, 23, 35  | 9, 17, 29, 41 |

| N/C                                            | _              | _             |

| # of Signal Pins                               | 36             | 36            |

| # User I/O Pins                                | 32             | 32            |

**Note 1:** OE (1, 2) = Global OE pins

2: GCLK (1, 2, 3) = Global Clock pins

3: GCLR = Global Clear pin

**4:** PD (1, 2) = Power-Down pins

5: TDI, TMS, TCK. TDO = JTAG pins used for boundary-scan testing or in-system programming

6: GND = Ground pins

7: Vcc = Vcc pins for the device

TABLE 2-2: I/O PINOUTS

| MC             | Logic Block | 44-Lead PLCC | 44-Lead TQFP |

|----------------|-------------|--------------|--------------|

| 1              | Α           | 4            | 42           |

| 2              | Α           | 5            | 43           |

| 3              | Α           | 6            | 44           |

| 4/TDI          | А           | 7            | 1            |

| 5              | A           | 8            | 2            |

| 6              | А           | 9            | 3            |

| 7/ <b>PD1</b>  | Α           | 11           | 5            |

| 8              | А           | 12           | 6            |

| 9/ <b>TMS</b>  | А           | 13           | 7            |

| 10             | A           | 14           | 8            |

| 11             | А           | 16           | 10           |

| 12             | А           | 17           | 11           |

| 13             | А           | 18           | 12           |

| 14             | А           | 19           | 13           |

| 15             | A           | 20           | 14           |

| 16             | A           | 21           | 15           |

| 17             | В           | 41           | 35           |

| 18             | В           | 40           | 34           |

| 19             | В           | 39           | 33           |

| 20/ <b>TDO</b> | В           | 38           | 32           |

| 21             | В           | 37           | 31           |

| 22             | В           | 36           | 30           |

| 23             | В           | 34           | 28           |

| 24             | В           | 33           | 27           |

| 25/ <b>TCK</b> | В           | 32           | 26           |

| 26             | В           | 31           | 25           |

| 27             | В           | 29           | 23           |

| 28             | В           | 28           | 22           |

| 29             | В           | 27           | 21           |

| 30             | В           | 26           | 20           |

| 31/ <b>PD2</b> | В           | 25           | 19           |

| 32             | В           | 24           | 18           |

### 3.0 DEVICE CHARACTERISTICS

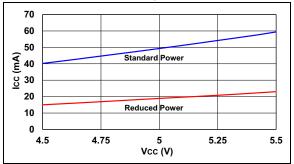

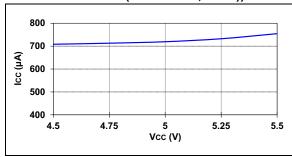

FIGURE 3-1: SUPPLY CURRENT VS.

SUPPLY VOLTAGE – ATF1502AS (TA = +25°C,

F = 0

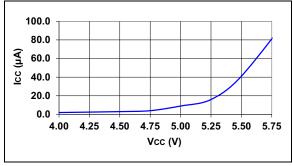

FIGURE 3-2: SUPPLY CURRENT VS. SUPPLY VOLTAGE – ATF1502AS(L)

$(TA = +25^{\circ}C, F = 0)$

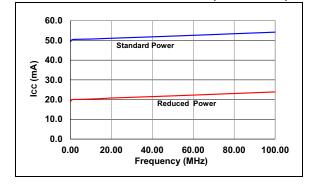

FIGURE 3-3: SUPPLY CURRENT VS.

FREQUENCY –

ATF1502AS (TA = +25°C)

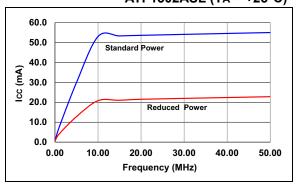

FIGURE 3-4: SUPPLY CURRENT VS. FREQUENCY

ATF1502ASL (TA = +25°C)

FIGURE 3-5: SUPPLY CURRENT VS. SUPPLY VOLTAGE –

PIN-CONTROLLED

POWER-DOWN MODE

$(TA = +25^{\circ}C, F = 0))$

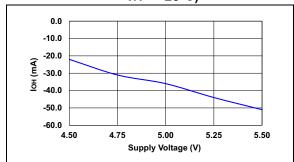

FIGURE 3-6: OUTPUT SOURCE

CURRENT VS. SUPPLY VOLTAGE (Voh = 2.4V,

TA = +25°C)

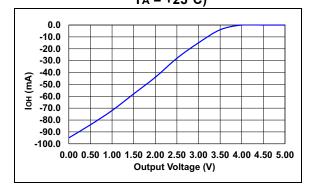

FIGURE 3-7: OUTPUT SOURCE CURRENT VS. OUTPUT VOLTAGE (Vcc = 5V, TA = +25°C)

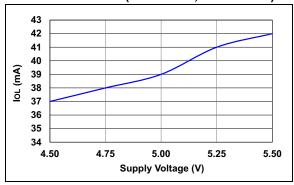

FIGURE 3-8: OUTPUT SINK CURRENT VS. SUPPLY VOLTAGE (Vol = 0.5V, TA = +25°C)

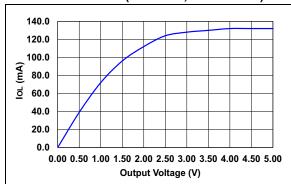

FIGURE 3-9: OUTPUT SINK CURRENT VS. OUTPUT VOLTAGE (Vcc = 5V, Ta = +25°C)

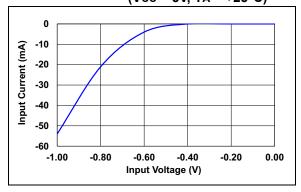

FIGURE 3-10: INPUT CLAMP CURRENT VS. INPUT VOLTAGE (Vcc = 5V, Ta = +25°C)

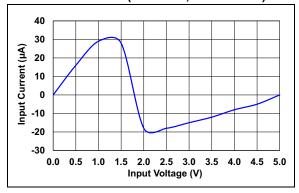

FIGURE 3-11: INPUT CURRENT VS. INPUT VOLTAGE (Vcc = 5V, Ta = +25°C)

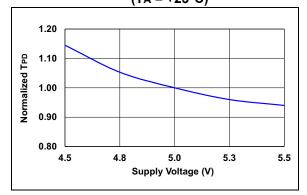

FIGURE 3-12: NORMALIZED TPD VS. SUPPLY VOLTAGE (TA = +25°C)

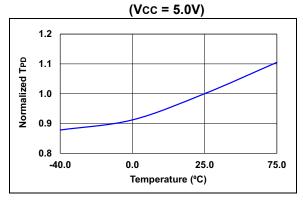

FIGURE 3-13: NORMALIZED TPD VS. TEMPERATURE

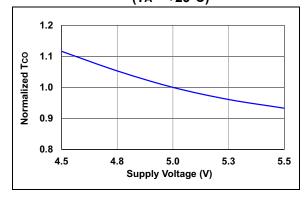

FIGURE 3-14: NORMALIZED TCO VS. SUPPLY VOLTAGE (TA = +25°C)

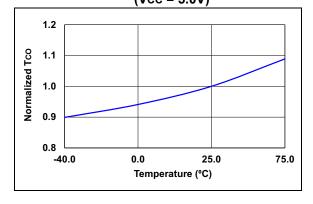

FIGURE 3-15: NORMALIZED TCO VS. TEMPERATURE (Vcc = 5.0V)

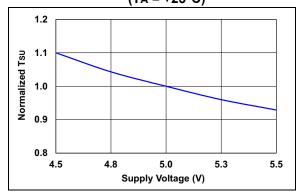

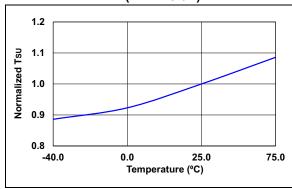

FIGURE 3-16: NORMALIZED Tsu VS. SUPPLY VOLTAGE (TA = +25°C)

FIGURE 3-17: NORMALIZED Tsu VS. TEMPERATURE (Vcc = 5.0V)

### 4.0 PACKAGING INFORMATION

## 4.1 Package Marking Information

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

This packages are RoHs compliant. The JEDEC<sup>®</sup> designator can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

### 4.2 Thermal Resistance

The following table summarizes the thermal resistance data for the package types available.

TABLE 4-1: THERMAL RESISTANCE DATA

| Package Type | θ <b>JA</b> | θ <b>јс</b> |

|--------------|-------------|-------------|

| 44-Lead PLCC | 30°C/W      | 16°C/W      |

| 44-Lead TQFP | 40°C/W      | 8°C/W       |

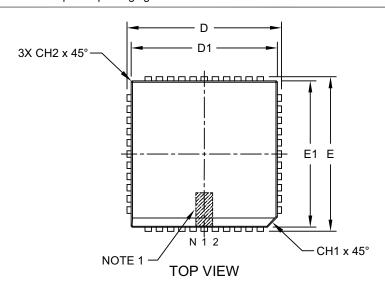

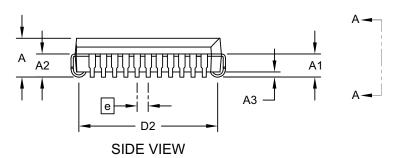

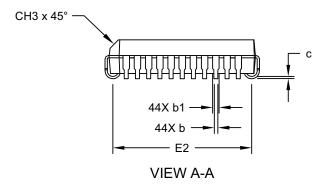

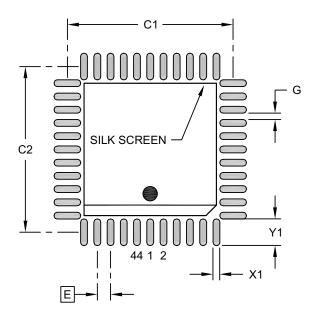

# 44-Lead Plastic Leaded Chip Carrier (L) - Square [PLCC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-048-L Rev C Sheet 1 of 2

# 44-Lead Plastic Leaded Chip Carrier (L) - Square [PLCC]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           |               | INCHES |         |      | MILLIMETE | RS    |       |  |

|---------------------------|---------------|--------|---------|------|-----------|-------|-------|--|

| Dimension                 | n Limits      | MIN    | NOM     | MAX  | MIN       | NOM   | MAX   |  |

| Number of Pins            | N             |        | 44      | 44   | 44        |       |       |  |

| Pitch                     | е             |        | .050    |      | 1.27      |       |       |  |

| Overall Height            | Α             | .165   | .172    | .180 | 4.19      | 4.37  | 4.57  |  |

| Contact Height            | A1            | .090   | .105    | .120 | 2.29      | 2.67  | 3.05  |  |

| Molded Package to Contact | A2            | .062   | -       | .083 | 1.57      | -     | 2.11  |  |

| Standoff §                | A3            | .020   | -       | -    | 0.51      | -     | -     |  |

| Corner Chamfer            | CH1           | .042   | -       | .048 | 1.07      | -     | 1.22  |  |

| Chamfers                  | CH2           | -      | -       | .020 | -         | -     | 0.51  |  |

| Side Chamfer              | CH3           | .042   | -       | .056 | 1.07      | -     | 1.42  |  |

| Overall Width             | E             | .685   | .690    | .695 | 17.40     | 17.53 | 17.65 |  |

| Overall Length            | D             | .685   | .690    | .695 | 17.40     | 17.53 | 17.65 |  |

| Molded Package Width      | E1            | .650   | .653    | .656 | 16.51     | 16.59 | 16.66 |  |

| Molded Package Length     |               | .650   | .653    | .656 | 16.51     | 16.59 | 16.66 |  |

| Footprint Width E2        |               | .582   | .610    | .638 | 14.78     | 15.49 | 16.21 |  |

| Footprint Length D2       |               | .582   | .610    | .638 | 14.78     | 15.49 | 16.21 |  |

| Lead Thickness            | s c .00750125 |        | 0.19    | -    | 0.32      |       |       |  |

| Upper Lead Width          | b1            | .026   | .026032 |      | 0.66      | -     | 0.81  |  |

| Lower Lead Width          | b             | .013   | -       | .021 | 0.33      | -     | 0.53  |  |

#### Notes:

Note:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .005" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-048-L Rev C Sheet 2 of 2

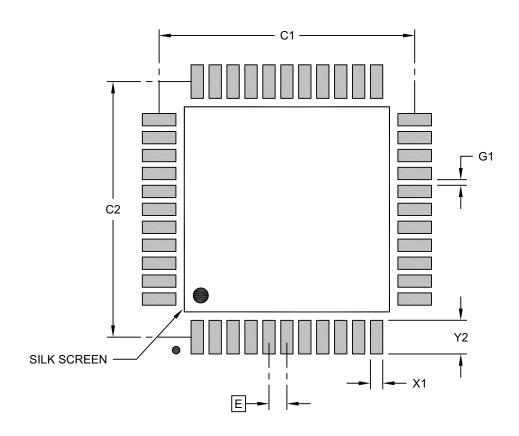

# 44-Lead Plastic Leaded Chip Carrier (L) - Square [PLCC]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                                 | Units |      |          |      | MII  | LLIMETE  | RS   |

|---------------------------------|-------|------|----------|------|------|----------|------|

| Dimension Limits                |       | MIN  | NOM      | MAX  | MIN  | NOM      | MAX  |

| Contact Pitch                   | Е     |      | .050 BSC | ;    |      | 1.27 BSC | ;    |

| Contact Pad Spacing             | C1    |      | .626     |      |      | 15.90    |      |

| Contact Pad Spacing             | C2    |      | .626     |      |      | 15.90    |      |

| Contact Pad Width (X44)         | X1    |      |          | .026 |      |          | 0.66 |

| Contact Pad Length (X44)        | Y1    |      |          | .100 |      |          | 2.54 |

| Contact Pad to Center Pad (X40) | G     | .008 |          |      | 0.20 |          |      |

### Notes:

Note:

- Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- 2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-2048-L Rev C

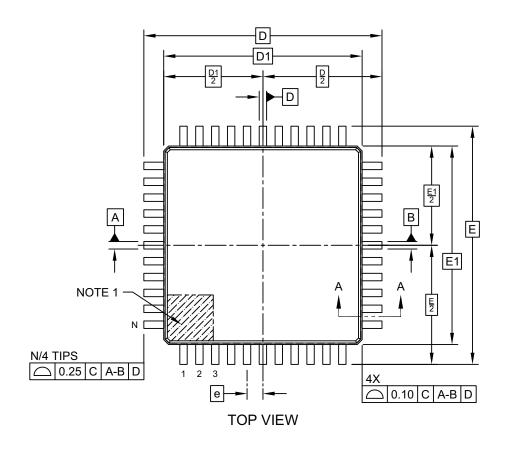

# 44-Lead Plastic Thin Quad Flatpack (3EB) - 10x10x1.0 mm Body [TQFP] Atmel Legacy Global Package Code AIX

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-21019-3EB Rev A Sheet 1 of 2

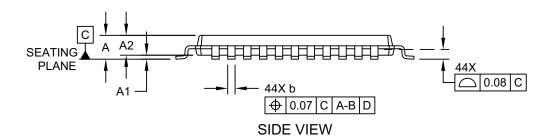

# 44-Lead Plastic Thin Quad Flatpack (3EB) - 10x10x1.0 mm Body [TQFP] Atmel Legacy Global Package Code AIX

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |            | MILLIMETER: | s    |  |  |

|--------------------------|------------------|------------|-------------|------|--|--|

| Dir                      | Dimension Limits |            |             |      |  |  |

| Number of Terminals      |                  |            |             |      |  |  |

| Pitch                    | е                |            | 0.80 BSC    |      |  |  |

| Overall Height           | Α                | -          | -           | 1.20 |  |  |

| Standoff                 | A1               | 0.05       | -           | 0.15 |  |  |

| Molded Package Thickness | A2               | 0.95       | 1.00        | 1.05 |  |  |

| Overall Length           | D                |            | 12.00 BSC   |      |  |  |

| Molded Package Length    | D1               |            | 10.00 BSC   |      |  |  |

| Overall Width            | E                | 12.00 BSC  |             |      |  |  |

| Molded Package Width     | E1               | 10.00 BSC  |             |      |  |  |

| Terminal Width           | b                | 0.30 - 0.4 |             |      |  |  |

| Terminal Thickness       | С                | 0.09       | -           | 0.20 |  |  |

| Terminal Length          | L                | 0.45       | 0.60        | 0.75 |  |  |

| Footprint                | L1               |            | 1.00 REF    | -    |  |  |

| Lead Bend Radius         | R1               | 0.08       |             |      |  |  |

| Lead Bend Radius         | R2               | 0.08       | -           | 0.20 |  |  |

| Foot Angle               | θ                | 0°         | 3.5°        | 7°   |  |  |

| Lead Angle               | Θ1               | 0°         | -           | -    |  |  |

| Terminal-to-Exposed-Pad  | <b>6</b> 2       | 11°        | 12°         | 13°  |  |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-21019-3EB Rev A Sheet 2 of 2

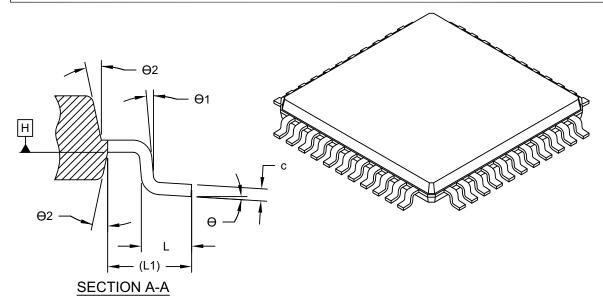

# 44-Lead Plastic Thin Quad Flatpack (3EB) - 10x10x1.0 mm Body [TQFP] Atmel Legacy Global Package Code AIX

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

### RECOMMENDED LAND PATTERN

|                                 | Units           |      |       |      |  |

|---------------------------------|-----------------|------|-------|------|--|

| Dimension                       | MIN             | NOM  | MAX   |      |  |

| Contact Pitch                   | Contact Pitch E |      |       |      |  |

| Contact Pad Spacing             | C1              |      | 11.40 |      |  |

| Contact Pad Spacing             |                 |      | 11.40 |      |  |

| Contact Pad Width (X20)         | X1              |      |       | 0.55 |  |

| Contact Pad Length (X20)        | Y1              |      |       | 1.50 |  |

| Contact Pad to Center Pad (X20) | G1              | 0.25 |       | ·    |  |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-23019-3EB Rev A

# **APPENDIX A: REVISION HISTORY**

# **Revision A (11/2021)**

Updated to the Microchip template. Microchip DS20006619A replaces Atmel document 0995.

### THE MICROCHIP WEBSITE

Microchip provides online support via our website at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip website at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://microchip.com/support

## PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NOXX                | <u>X</u>   | ¥                                                  | <u>xxx</u>    | <u>-D</u> | <u>(1</u> 1) | Ex                          | ample   | es:                           |                                                                                                                        |

|--------------------------|------------|----------------------------------------------------|---------------|-----------|--------------|-----------------------------|---------|-------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Device Speed<br>Grade    | Package    | Temperature                                        | Lead<br>Count | •         | nd Reel      | a)                          | ATF150  | 02AS-7AX44:                   | Commercial temp.,TQFP package.                                                                                         |

| Grade                    | Туре       | Range                                              | Count         | Opti      | on           | b)                          | ATF150  | 02AS-7AX44-T:                 | Commercial temp., Tape and Reel, TQFP package.                                                                         |

| Device:                  | ATF1502AS  |                                                    |               |           | D            | c)                          | ATF150  | 02AS-7JX44:                   | Commercial temp., PLCC package.                                                                                        |

|                          | ATF1502ASL | _ = 5V Low-Pow                                     | er 32 MC      | CPLD      |              | d) ATF1502AS-7JX44-T: Comme |         |                               | Commercial temp., Tape and Reel, PLCC package.                                                                         |

| Smood Crade:             | 7 = 7      | 7 F ma (tpp)                                       |               |           |              | e)                          | ATF150  | 02AS-10AU44:                  | Industrial temp., TQFP package.                                                                                        |

| Speed Grade:             |            | 7.5 ns (tPD)<br>10 ns (tPD)                        |               |           |              | ,                           |         |                               | : Industrial temp., Tape and Reel,                                                                                     |

|                          |            | 25 ns (tPD)                                        |               |           |              | .,                          |         | 02.10 .0.10                   | TQFP package.                                                                                                          |

|                          | 25 - 2     | 23 113 (170)                                       |               |           |              | a)                          | ATF150  | 02AS-10JU44:                  | Industrial temp., PLCC package.                                                                                        |

|                          |            |                                                    |               |           |              |                             |         |                               | Industrial temp., TQFP package.                                                                                        |

| Package Type:            | J = F      | PLCC (Plastic J-lead                               | ded Chin (    | Carrier)  |              | ,                           |         |                               | Industrial temp., PLCC package.                                                                                        |

| , admago Type.           |            | TQFP (Thin Profile F                               |               |           | ckage)       | ''                          | AII 130 | 02A0L-200044.                 | mudstriartemp., i 200 package.                                                                                         |

| Temperature              | U = -      | 40°C to +85°C (Indi                                | ustrial)      |           |              |                             |         |                               |                                                                                                                        |

| Range:                   | X =        | 0°C to +70°C (Com                                  | mercial)      |           |              |                             |         |                               |                                                                                                                        |

| Lead Count:              | 44 = 4     | 14 Leads                                           |               |           |              | N                           | ote 1:  | alog part nu<br>used for orde | el identifier only appears in the cat-<br>mber description. This identifier is<br>ering purposes and is not printed on |

| Tape and Reel<br>Option: |            | Standard packaging<br>Tape and Reel <sup>(1)</sup> | (tube or t    | ray)      |              |                             |         |                               | ackage. Check with your Microchip for package availability with the el option.                                         |

|                          |            |                                                    |               |           |              |                             |         |                               |                                                                                                                        |

## ORDERING INFORMATION

# ATF1502AS(L) Green Package Options (Pb/Halide-Free/RoHS Compliant)

| tpD (ns) | tcop (ns) | fmax (MHz) | Ordering Code     | Package | Operation Range             |

|----------|-----------|------------|-------------------|---------|-----------------------------|

| 7.5      | 4.5       | 166.7      | ATF1502AS-7AX44   | 44A     | Commercial (0°C to +70°C)   |

| 7.5      | 4.5       | 100.7      | ATF1502AS-7JX44   | 44J     | Commercial (0 C to +70 C)   |

| 10       | 5         | 125        | ATF1502AS-10AU44  | 44A     | Industrial (-40°C to +85°C) |

| 10       | 5         | 125        | ATF1502AS-10JU44  | 44J     | muusinai (-40 C to +65 C)   |

| 25       | 13        | 60         | ATF1502ASL-25AU44 | 44A     | Industrial (-40°C to +85°C) |

| 25       | 13        | 00         | ATF1502ASL-25JU44 | 44J     |                             |

#### Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable" Code protection is constantly evolving. Microchip is committed to

continuously improving the code protection features of our products.

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at <a href="https://www.microchip.com/en-us/support/design-help/client-support-services">https://www.microchip.com/en-us/support/design-help/client-support-services</a>.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, TrueTime, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the LLS A

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, GridTime, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, NVM Express, NVMe, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, Symmcom, and Trusted Time are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2021, Microchip Technology Incorporated and its subsidiaries.

All Rights Reserved.

ISBN: 978-1-5224-9131-6

# Worldwide Sales and Service

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/ support

Support Web Address:

www.microchip.com

Atlanta Duluth, GA

Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

Boston

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Tel: 281-894-5983 Indianapolis Noblesville, IN

Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

Canada - Toronto Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

**China - Beijing** Tel: 86-10-8569-7000

China - Chengdu Tel: 86-28-8665-5511

**China - Chongqing** Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

**China - Guangzhou** Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

**China - Nanjing** Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

**China - Shanghai** Tel: 86-21-3326-8000

**China - Shenyang** Tel: 86-24-2334-2829

**China - Shenzhen** Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

China - Wuhan

Tel: 86-27-5980-5300 China - Xian

Tel: 86-29-8833-7252

**China - Xiamen** Tel: 86-592-2388138

**China - Zhuhai** Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune Tel: 91-20-4121-0141

**Japan - Osaka** Tel: 81-6-6152-7160

Japan - Tokyo

Tel: 81-3-6880- 3770 Korea - Daegu

Tel: 82-53-744-4301

Korea - Seoul Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

**Singapore** Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

#### **EUROPE**

**Austria - Wels** Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen Tel: 45-4485-5910

Fax: 45-4485-2829

**Finland - Espoo** Tel: 358-9-4520-820

France - Paris

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

Germany - Garching Tel: 49-8931-9700

**Germany - Haan** Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-72400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611

Fax: 39-0331-466781 Italy - Padova

Tel: 39-049-7625286 **Netherlands - Drunen** Tel: 31-416-690399

Fax: 31-416-690340 **Norway - Trondheim** Tel: 47-7288-4388

**Poland - Warsaw** Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Gothenberg** Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820