### Power Supply Rejection Ratio of Low Dropout Voltage Regulators

Author: Mihai Sterescu

Microchip Technology Inc.

#### INTRODUCTION

This application note introduces the Power Supply Rejection Ratio (PSRR) and illustrates how to measure and correctly evaluate the PSRR of a low dropout voltage regulator.

#### **PSRR AND OUTPUT NOISE**

The Power Supply Rejection Ratio is the ability of a device, such as a Low Dropout Voltage regulator, to reject the various perturbations that can be found in its input supply rail by providing a greatly attenuated signal at the output. Generally, the main source of the perturbation will be the output ripple of the DC/DC converters that typically power LDOs.

High PSRR LDOs are recommended for powering line ripple sensitive devices such as: RF applications, ADCs/DACs, FPGAs, MPUs, and audio applications.

One important clarification must be made: PSRR is **NOT** the same with output noise. PSRR is a measure of rejection. It shows what the part will output based on the given input.

Output NOISE is typically referred to in a data sheet as  $e_N$ . This is the sum of all the noise sources developed internally by the part and some of the external noise sources. Internal noise sources are flicker or 1/f noise, burst noise, shot noise and thermal noise. External noise can either be electromagnetically induced noise or generated by mechanical stress that causes the piezoelectric effect.

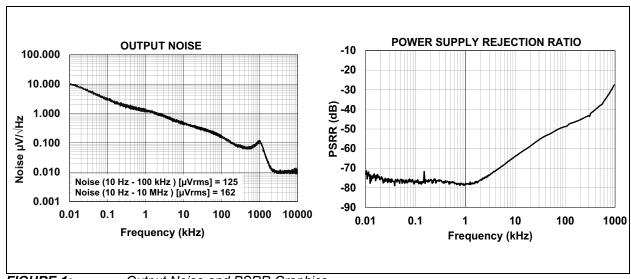

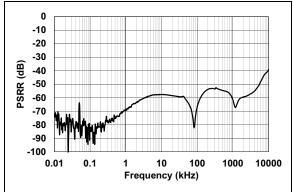

Figure 1 displays a side-by-side comparison of the two distinct specifications. The Output Noise, plotted as a graph of spectral noise density, indicates how much "noise" or output ripple is internally generated by the part itself over a given frequency range, while being powered from an ideal DC power supply or battery. To ensure that the noise measurement obtained is accurate, it should be carried out in a shielded environment, that in turn blocks most of the external noise sources from interfering with the measurement. The PSRR graph in Figure 1 indicates the amount of attenuation the LDO provides at different frequencies.

FIGURE 1: Output Noise and PSRR Graphics.

#### **PSRR SHORT INTRODUCTION**

There are two common ways to mathematically express the PSRR value. The first is based on the definition itself, which measures rejection:

# EQUATION 1: PSRR AS A MEASURE OF REJECTION RATIO

$$PSRR = 20 \times log \frac{V_{IN}}{V_{OUT}}$$

The second method expresses the value as a measure of gain:

# EQUATION 2: PSRR AS A MEASURE OF GAIN RATIO

$$PSRR = 20 \times log \frac{V_{OUT}}{V_{IN}}$$

This can be used in order to better explain PSRR.

It should be noted that  $V_{OUT}$  and  $V_{IN}$  from Equation 1 and Equation 2 are AC values.

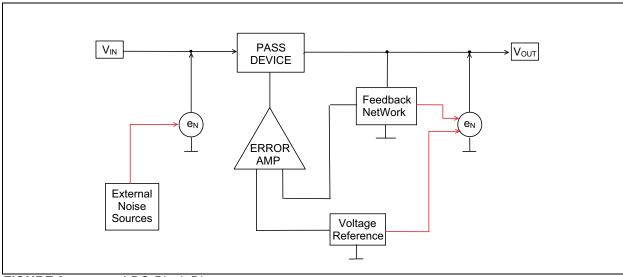

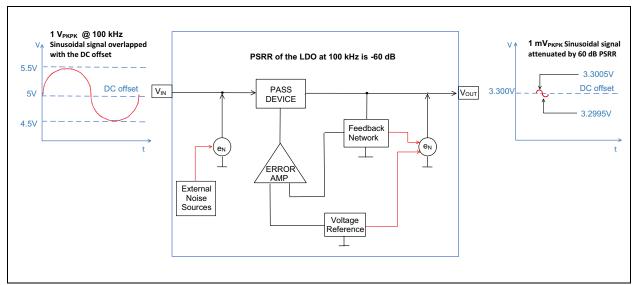

Figure 2 shows the functional blocks of the LDO.

FIGURE 2: LDO Block Diagram.

One of the elements which determine the PSRR of an LDO is the AC gain of the error amplifier.

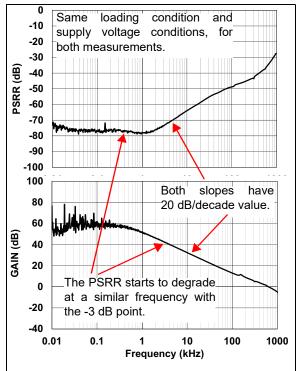

It can be considered that the PSRR curve follows the gain curve as shown in **Figure 3**, until the closed loop gain reaches the crossover frequency.

The AC and DC gain of the error amplifier is similar until the error amplifier reaches the rolloff frequency. This is why the PSRR degradation usually occurs at higher frequencies. When the gain reaches the crossover frequency, the operational amplifier can no longer control the loop and, as a result, no longer has an impact on the PSRR value.

Although the PSRR is largely controlled by the operational amplifier, it is also determined by other elements which impact the curve at its extremities. The voltage reference has an impact from 0 Hz to around a couple of tens of Hz. In this range, the PSRR is mostly controlled by the band gap reference as well as the control loop. For frequencies that are higher than the crossover frequency, the PSRR is influenced by the output capacitor (as long as the crossover frequency is lower than the resonance frequency of the capacitor)

and by the parasitic elements that can be found from the input to the output of the LDO in the final assembled package.

FIGURE 3: PSRR vs. GAIN (MIC47050 Example).

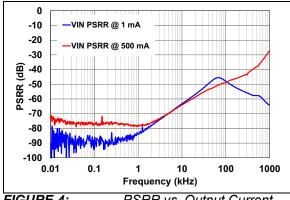

The PSRR value of an LDO generally degrades as a function of output current, meaning that the worst value of the PSRR can be seen for maximum output current.

FIGURE 4: PSRR vs. Output Current (MIC47050 Example).

Another factor that impacts the PSRR is the value of the output capacitor. Even if in some cases the PSRR value can be improved by using a higher capacitance, this value is not considerable, given that most LDOs have been optimized to work with the typical recommendations of the output capacitor.

#### **PSRR MEASUREMENT**

PSRR can be measured at a specific frequency or a determined frequency range. The typical range is 10 Hz to 1 MHz. It can, however, be extended to 10 MHz for parts that have a superior PSRR, such as the Ripple Blocker™ product line. Adequate hardware is needed to supply the LDO under test, which makes it necessary to over-impose a sinusoidal signal with the DC offset required to power the part.

The supply voltage used for powering the LDO during the PSRR test must meet the following conditions:

#### **EQUATION 3: SUPPLY VOLTAGE**

$$V_{IN} = DC_{COMPONENT} + AC_{COMPONENT}$$

## EQUATION 4: SUPPLY VOLTAGE TYPICAL VALUE

$$V_{IN} = \left(V_R + V_{HEADROOM} + \frac{V_{PKPK}}{2}\right) + V_{PKPK}$$

# EQUATION 5: SUPPLY VOLTAGE FOR MINIMUM SUPPLY VOLTAGE CONSTRAINT

$$V_{IN} = \left(V_{IN(MIN)} + \frac{V_{PKPK}}{2}\right) + V_{PKPK}$$

V<sub>R</sub> is the output voltage of the LDO.

$V_{\mbox{\scriptsize HEADROOM}}$  is typically 1V for some LDOs or for linear voltage regulators this value can be higher than 1V so it needs to be adjusted accordingly).  $V_{\mbox{\scriptsize HEADROOM}}$  is composed from the value given by the dropout voltage of the pass transistor and an additional saturation voltage that is needed to prevent the pass transistor from entering triode region of operation. When the pass transistor goes from saturation region of operation to triode, this transition will cause the loop gain to drop which in turn will cause the PSRR to degrade.

$V_{IN(MIN)}$  is the minimum input voltage required by an LDO. When  $V_R + V_{HEADROOM}$  is lower than the  $V_{IN(MIN)}$ , the constraint for the input voltage is then calculated using **Equation 5**.

For example: if there is an LDO with the minimum input voltage of 2.5V and a  $V_R$  = 1V, then using **Equation 4** is not sufficient to meet the minimum input supply condition and, as a result, the part might not even start.

$V_{PKPK}$  is the AC signal amplitude and generally has a value of 0.5V. The value can be adjusted to accommodate the required value as long as the operating conditions are met.

When powering the part, the LDO must be prevented from entering the dropout region of operation. Consequently, the proper operating conditions, as noted in the respective product's data sheet, must be assured.

For example: the LDO has a dropout of 1V, the amplitude of the sinusoidal signal used is 500 mV $_{\rm PKPK}$  and V $_{\rm R}$  is set to 5V with a value for the DC offset of 6V.

The supply needs to be 250 mV higher to prevent the part from entering in dropout when the negative swing of the of sine occurs.

Alongside the aforementioned factors that impact the PSRR of the part, not having the correct input supply voltage degrades the PSRR as well. For this reason, it must be ensured that the LDO never operates in dropout.

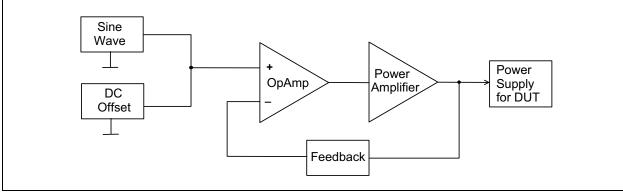

To generate the  $V_{\text{IN}}$  supply, special hardware is used. The block diagram is illustrated in **Figure 5.**

FIGURE 5: PSRR Supply Board.

The general structure of the supply system required to carry out the PSRR test is displayed in **Figure 5**. The board adds the sine wave signal to the DC Offset, with a secondary power stage amplifier being required to ensure that adequate power is delivered to the DUT (Device Under Test). A control loop is required to have the required input voltage powering the DUT.

Before starting the measurement, the input capacitor should be removed from the DUT. This measure applies to most LDOs and voltage regulators and is required to prevent the distortion and/or attenuation of the sinusoidal signal used to drive the board. This also allows the PSRR measurement to be performed strictly with respect to the rejection ability of the LDO.

For the aforementioned power supply board, the source of the sinusoidal signal determines how the PSRR is being measured. Depending on the source used, the PSRR can be measured in two ways:

- · using a signal generator and an oscilloscope

- · using a network analyzer

The first method utilizes a signal generator and an oscilloscope. The method will enable the analysis of the PSRR for a single frequency point. However, this method is not accurate for high PSRR values. This is limited by the dynamic range of the oscilloscope, which is not as high as the range of the network analyzer. (note that there are high-end solutions for oscilloscopes, which have the capability to perform the PSRR in a similar way to a network analyzer).

For information on how to set up and probe the DUT in order to have greater measurement accuracy, see **Appendix A: "Setup probing and connections"**.

The PSRR measurement is then performed by setting the signal generator to output a constant frequency signal with the required amplitude and using the oscilloscope to measure the difference between the input and output signals.

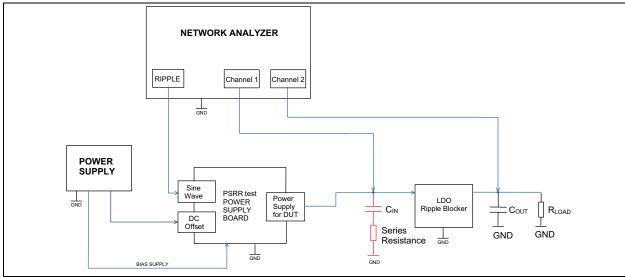

The second method involves the use of a network analyzer. The network analyzer is configured to perform the measurement required and the calculations in **Equation 2**. This is done by selecting the corresponding channels and making the appropriate connections to the input and output of the DUT (the configuration and/or the labeling is done separately for each device, so the user has to identify and make the connection required for their setup). **Figure 6** illustrates a typical setup for the PSRR measurement.

By using the network analyzer, there is no need for an additional signal generator, given that the device outputs a sine wave in the specific bandwidth (10 Hz to 10 MHz) required to connect to the PSRR supply board.

While configuring the network analyzer care must be taken in choosing Intermediate Filter (IF) bandwidth required for the measurement. If the measurement is done at the typical starting frequency of 10 Hz, the value of the IF filter must be lower than 10 Hz to accurately measure the PSRR up to hundreds of Hertz.

If the first measurement displays too many artifacts, then it is advised to use an averaged measurement to obtain a much cleaner graph.

FIGURE 6: PSRR Measurement Setup.

# PSRR MEASUREMENT FOR RIPPLE BLOCKERS

The Ripple Blocker family of linear regulators provides excellent PSRR. However, the measurement of the PSRR may pose problems. This is due to the architecture having stability problems when an input capacitor is not used during transitory events. As a result, the PSRR measurement needs to be performed by using an input capacitor with additional series resistance of around 5  $\Omega$ . This not only applies to Ripple Blockers, but other LDOs that have stability problems when an input capacitor is not present.

Adding the additional series resistance to the capacitor reduces the distortion and attenuation that occurs at high frequencies. The attenuation itself is caused by the capacitor shorting all high-frequency signals to ground.

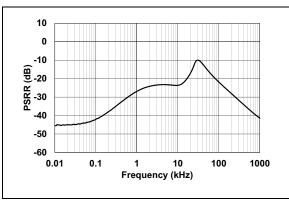

**Figure 7** and **Figure 9** illustrate orders of magnitude and the differences between two types of LDO, a low  $I_Q$  LDO and a high PSRR LDO. The figures do not imply that the values used apply as presented for all the parts that are assigned to the two categories (note that this is a worst case scenario; it is the system designer duty to decide if the results are affecting the application and/or the system requirements needed).

FIGURE 7: PSRR of Low I<sub>O</sub> LDO.

**Figure 7** shows a typical PSRR curve for a very low  $I_Q$  part. This part is not intended to filter the extremely noisy input supplies and is to be directly powered from batteries.

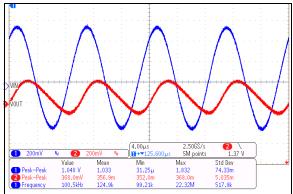

The following case will be considered: for a generic low  $I_Q$  part which at 100kHz provides only 10 dB of attenuation, meaning that if a 1  $V_{PKPK}$  sinusoidal signal is applied to its input then around 300 m $V_{PKPK}$  of sinusoidal oscillations still persist. For more details, see Figure 8.

FIGURE 8: Inadequate LDO PSRR for the Application.

The same scenario can be analyzed with the low  $I_Q$  LDO replaced with a Ripple Blocker or another LDO with superior PSRR. For this scenario, see the curve in Figure 9.

FIGURE 9: PSRR for Ripple Blockers or LDOs with Superior PSRR.

For this example, the PSRR generated at 100 kHz is better than the -60 dB. As a result, for a 1  $V_{PKPK}$  sinusoidal signal on its input, the output will only have around 1 m $V_{PKPK}$  sinusoidal oscillations on the output.

FIGURE 10: PSRR Attenuation Visual Aid.

#### **CONCLUSIONS**

PSRR needs to be considered when looking at an LDO and when doing a large power delivery architecture for systems, especially if the application is sensitive to line ripple. Taking into account the variation of the PSRR at different operating points will enable the desired functionally in the final system.

#### APPENDIX A: SETUP PROBING AND CONNECTIONS

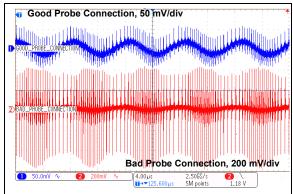

When probing high-frequency signals or signals which can easily be corrupted by ambient noise, certain methods of good practice must be employed.

If an oscilloscope probe is used to measure the output and input signals from the DUT, the length of the ground connection between the oscilloscope probe and the chosen test point must be as short as possible.

FIGURE 11: Oscilloscope Probe Connection.

The impact of this change is displayed in Figure 12.

FIGURE 12: Signal Integrity for the Connections with Both Channels at 300 MHz Bandwidth and Probing the Same Signal.

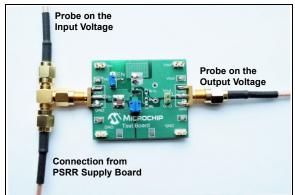

The connection between the PSRR supply board and the DUT should be as short as possible, made by using shielded cables. The cables used should not be longer than needed to avoid unnecessary losses. If coaxial cables and SMA type connectors are used, it is the user's duty to ensure that the power level that is driven through the cables and connectors does not exceed their ratings.

FIGURE 13: Shielded Cable Connection.

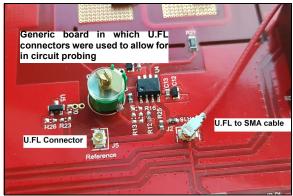

If this type of setup is not available, a coaxial cable with a very short ground lead, using a 2.54 mm pin header and socket, is sufficient. See Figure 14 for more details. For both setups, a limited number of connections can be made before the quality of the contact starts degrading and can cause unwanted interferences with the measurements.

FIGURE 14: Shielded Cable Connection

Another efficient way to allow for probing an existing design is the use of U.FL connectors and ferrite beads or 0  $\Omega$  resistors between the input supply of the DUT and the existing PDN (Power Delivery Network). This allows the decoupling of the DUT from the PDN.

FIGURE 15: Circuit Probing for Final Circuit.

Additionally, when choosing a load type, it is best to use a resistive load instead of an electronic load. Doing so prevents other external sources from interfering with the system under test.

#### **REVISION HISTORY**

Revision A (June 2019)

Original release of this document.

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### **Trademarks**

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, SAM-BA, SpyNIC, SST, SST Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A. Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, INICnet, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, memBrain, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM, net. PICkit, PICtail, PowerSmart, PureSilicon. QMatrix, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2018, Microchip Technology Incorporated, All Rights Reserved. ISBN: 978-1-5224-4577-7

#### **Worldwide Sales and Service**

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/ support

Web Address:

www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

Boston

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Dallas Addison, TX

Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323

Fax: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

**Raleigh, NC** Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

China - Beijing Tel: 86-10-8569-7000

China - Chengdu Tel: 86-28-8665-5511

**China - Chongqing** Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

**China - Nanjing** Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

China - Shanghai Tel: 86-21-3326-8000

**China - Shenyang** Tel: 86-24-2334-2829

**China - Shenzhen** Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

**China - Wuhan** Tel: 86-27-5980-5300

China - Xian

Tel: 86-29-8833-7252 **China - Xiamen** Tel: 86-592-2388138

**China - Zhuhai** Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune Tel: 91-20-4121-0141

**Japan - Osaka** Tel: 81-6-6152-7160

**Japan - Tokyo** Tel: 81-3-6880- 3770

Korea - Daegu

Tel: 82-53-744-4301

Korea - Seoul Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

**Singapore** Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

#### **EUROPE**

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Garching Tel: 49-8931-9700

**Germany - Haan** Tel: 49-2129-3766400

**Germany - Heilbronn** Tel: 49-7131-67-3636

**Germany - Karlsruhe** Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

**Italy - Padova** Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

**Poland - Warsaw** Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Gothenberg** Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820