# **AT21CS Series Reset and Discovery**

#### **APPLICATION NOTE**

#### Introduction

This application note discusses the Atmel<sup>®</sup> AT21CS Series Reset function and the AT21CS Series Discovery function. Additionally, a comparison between the Atmel Single-Wire Discovery event and the Maxim/Dallas One-Wire discovery event is discussed to facilitate the understanding of which device type is on the bus.

# **Table of Contents**

| Int | roduction                                                         | 1  |  |  |  |

|-----|-------------------------------------------------------------------|----|--|--|--|

| 1.  | Overview                                                          |    |  |  |  |

|     | 1.1. Atmel Single-Wire Protocol and the AT21CS Series             | 3  |  |  |  |

|     | 1.2. Device Reset/Power-up and Discovery Response                 | 3  |  |  |  |

| 2.  | Atmel Single-Wire Reset/Discharge and Discovery Response Waveform | 4  |  |  |  |

| 3.  | Atmel Single-Wire and Maxim One-Wire Discovery Difference         | 8  |  |  |  |

| 4.  | Revision History                                                  | 10 |  |  |  |

#### 1. Overview

### 1.1. Atmel Single-Wire Protocol and the AT21CS Series

The AT21CS Series has only two pins, GND and SI/O. The SI/O pin is the only signal between the Master microcontroller and the Slave (the AT21CS Series) hence the name Atmel Single-Wire. The SI/O signal is pulled high using an external pull-up resistor that is tied to the Master's power source. The SI/O signal must idle (rest) at a high state due to the pull up. The open collector (open drain) Master I/O port pin must signal the Slave by pulling SI/O low as seen in the Atmel Single-Wire protocol. Since there is no reset signal pin, the Reset event is achieved as defined in the Atmel Single-Wire protocol. Even though there is no  $V_{CC}$  (power pin), the AT21CS Series extracts power from the Atmel Single-Wire protocol sent to it. Data sent to the device over the Single-Wire bus is interpreted by the state of the SI/O pin during specific time intervals or slots.

## 1.2. Device Reset/Power-up and Discovery Response

A Reset and Discovery Response sequence is used by the Master to reset the device, as well as to perform a general bus call to determine if any devices are present on the bus. This sequence is comprised of two events, a Reset/Discharge event followed by a Discovery query.

The AT21CS Series responds to the Discovery query if the SI/O signal was previously held low for a sufficient amount of time to create a Reset event or a Discharge event. The Reset event is needed to enable the Discovery response from the AT21CS Series as defined in the Atmel Single-Wire protocol. If the AT21CS Series is busy internally executing a command, the Reset event is ignored, and therefore the device does not respond to the Discovery query. The application firmware should utilize the Reset event if the system experienced uncontrolled power brown out events while the device was idle. After power has stabilized, a forced Reset event guarantees the device is ready for operation.

A Discharge event also enables the Discovery response from the AT21CS Series. The Discharge event requires the Master to hold SI/O low for a longer time than for the Reset event. The Discharge event is utilized to override the internal busy state of the device by depleting the internally stored charge necessary for device internal operation.

**Note:** A Discharge event immediately stops completion of any internal operation. The user should not expect the interrupted operation to have been completed properly. Atmel recommends utilizing only the Discharge event to immediately stop any internal AT21CS Series operations.

The AT21CS Series Discovery response is a feature that distinguishes Atmel Single-Wire devices from other One-Wire protocol devices on the market. The Atmel AT21CS Series Discovery sequence is detailed in the AT21CS Series datasheet. Atmel recommends utilizing this sequence if the system has a mix of One-Wire protocol devices.

# 2. Atmel Single-Wire Reset/Discharge and Discovery Response Waveform

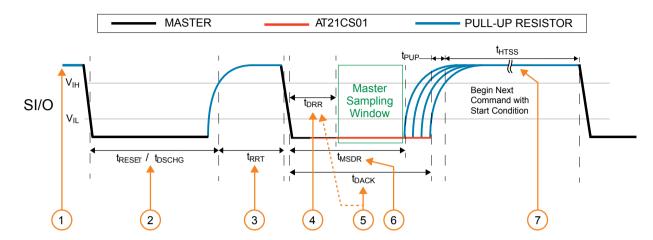

Figure 2-1. Reset and Discovery Response Waveform

When the system first powers up, the AT21CS Series is in a standby mode waiting for the Master to send the Discovery protocol.

- **Event 1** The SI/O signal is pulled high by the pull up resistor. At power-up, SI/O follows the V<sub>CC</sub> rampup waveform. This waveform begins after system power is stable.

- **Event 2** Master initiates a reset by holding SI/O low for t<sub>RESET</sub>, and then releasing SI/O (stop driving low). Alternately, the Master can hold SI/O low for t<sub>DSCHG</sub> to interrupt an internal operation, and then release SI/O.

- **Event 3** SI/O transitions to the high state after the Master releases SI/O. After the time specified by t<sub>RRT</sub> (Reset Recovery Time), the Master drives SI/O low to request a Discovery Response Acknowledge from the slave device.

- **Event 4** The Master continues holding SI/O low for during the entire t<sub>DRR</sub> interval.

- **Event 5** The slave device detects SI/O low within the  $t_{DRR}$  interval and concurrently holds SI/O low for  $t_{DACK}$ . The slave device releases SI/O after  $t_{DACK}$ .

- **Event 6** The Master samples SI/O state at t<sub>MSDR</sub>. Since t<sub>DACK</sub> is longer than t<sub>MSDR</sub>, the Master sees the correct state on SI/O before the Slave device releases SI/O at the end of t<sub>DACK</sub>. A low inside this window means that the Slave AT21CS Series is present on the bus.

- **Event 7** The Master must wait for t<sub>HTSS</sub> to create a Start condition before continuing with the first command.

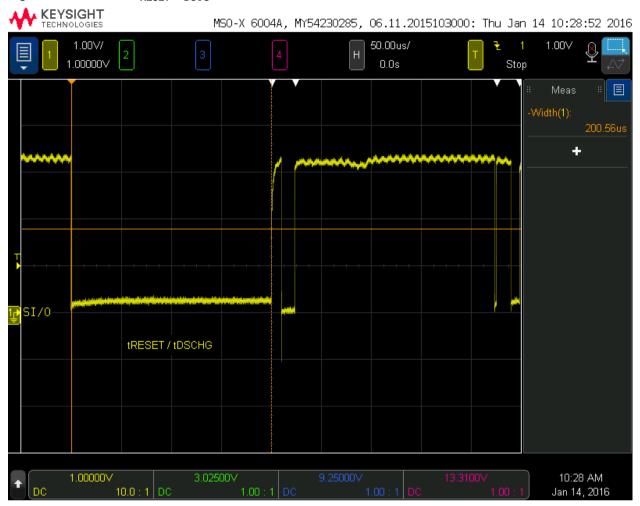

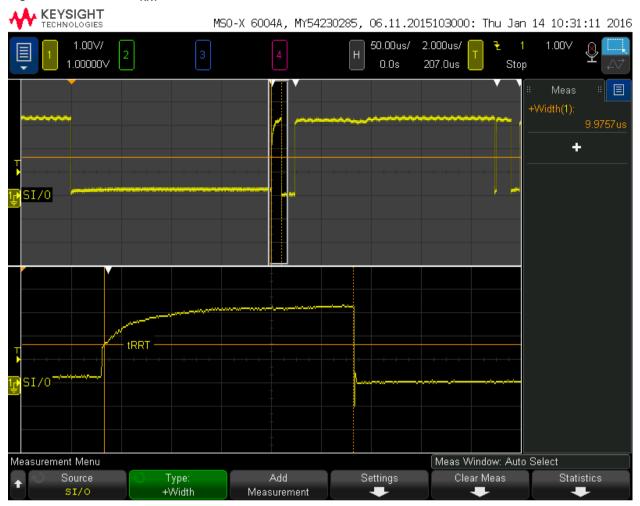

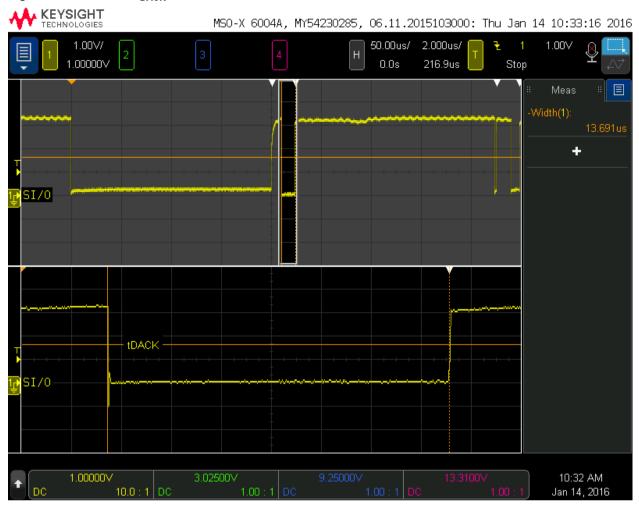

The Atmel AT21CSMK100 Single-Wire Memory Product Evaluation Kit was utilized to make oscilloscope captures to illustrate the AT21CS01 reset/discovery response. The duration of the measured datasheet parameters are seen in the waveform measurement window to the top right of a capture.

**Note:** The DC low level when the Atmel AT90USB1287 host microcontroller in the AT21CSMK100 Kit is driving the SI/O bus low is slightly higher (still a good  $V_{\rm IL}$  level) than when the AT21CS is driving SI/O low. This is due to the I/O driver strength of the host and the slave. The waveforms were made at pins 5 (SI/O) and 9 (GND) of the AT21CSMK100 Kit slave socket board.

Figure 2-2. Datasheet  $t_{\mbox{\scriptsize RESET}}$  /  $t_{\mbox{\scriptsize DSCG}}$  Measurement

Figure 2-3. Datasheet t<sub>RRT</sub> Measurement

Figure 2-4. Datasheet t<sub>DACK</sub> Measurement

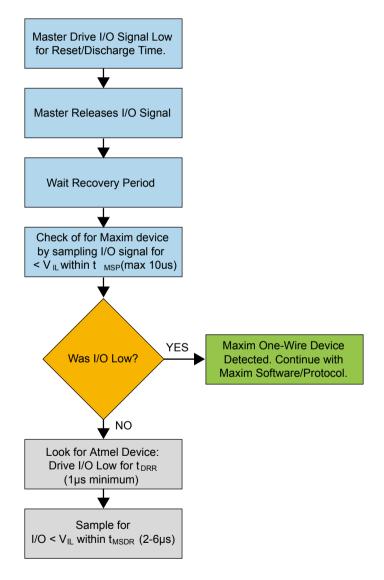

## 3. Atmel Single-Wire and Maxim One-Wire Discovery Difference

When initiating communications with both an Atmel Single-Wire device and a Maxim One-Wire device, the Master must drive the I/O signal low (reset/discharge) to begin the Discovery query. After the I/O signal is driven low for the required reset/discharge time, the Master releases the I/O signal. The Atmel device expects the Master to initiate a low on the I/O signal to query for a Discovery Response in comparison to the Maxim device which initiates the low I/O signal to acknowledge it is present on the bus. Therefore, the Master can easily determine which single-wire slave is on the bus by sampling the state of the I/O signal within  $t_{\rm MSDR}$ . If the Master initiated the low on the I/O signal and Atmel is present, the I/O signal is low. If the Master did not initiate the low on the I/O signal and the I/O signal is low, Maxim is present.

Figure 3-1. Single-Wire and Maxim One-Wire Discovery Flow

Table 3-1. Reset and Discovery Response Timing

|        |                                                        | Standard Speed <sup>(1)</sup> |     | High Speed |                         |       |

|--------|--------------------------------------------------------|-------------------------------|-----|------------|-------------------------|-------|

| Symbol | Parameter and Condition                                | Min                           | Max | Min        | Max                     | Units |

| tRESET | Reset Low Time, Device in Inactive State               | 480                           | _   | 48         | _                       | μs    |

| tDSCHG | Discharge Low Time, Device in Active Write Cycle (twR) | 150                           | _   | 150        | _                       | μs    |

| tRRT   | Reset Recovery Time                                    | N/A                           | N/A | 8          | _                       | μs    |

| tDRR   | Discovery Response Request                             | N/A                           | N/A | 1          | 2 - tpup <sup>(2)</sup> | μs    |

| tDACK  | Discovery Response Acknowledge Time                    | N/A                           | N/A | 8          | 24                      | μs    |

| tMSDR  | Master Strobe Discovery Response Time                  | N/A                           | N/A | 2          | 6                       | μs    |

| tHTSS  | SI/O High Time for Start / Stop Condition              | N/A                           | N/A | 150        | _                       | μs    |

#### Note:

- Due to the fact that the device defaults to High Speed Mode upon reset, the Reset and Discovery Response Timing after t<sub>RESET</sub> does not apply for Standard Speed Mode. High Speed Mode timing applies in all cases after t<sub>RESET</sub>.

- 2.  $t_{PUP}$  is the time required once the SI/O line is released to be pulled up from  $V_{IL}$  to  $V_{IH}$ . This value is application specific and is a function of the loading capacitance on the SI/O line as well as the  $R_{PUP}$  chosen.

- 3. AC measurement test conditions for the table above:

- Loading capacitance on SI/O: 100pF

- $R_{PUP}$  (bus line pull-up resistor to  $V_{PUP}$ ): 1kΩ;  $V_{PUP}$ : 2.7V

# 4. Revision History

| Doc Rev. | Date    | Comments                  |

|----------|---------|---------------------------|

| Α        | 02/2016 | Initial document release. |

**Atmel Corporation**

1600 Technology Drive, San Jose, CA 95110 USA

T: (+1)(408) 441.0311

F: (+1)(408) 436.4200

www.atmel.com

© 2016 Atmel Corporation. / Rev.: Atmel-8976A-SEEPROM-AT21CS-Resest-Discovery\_Application Note-02/2016

Atmel®, Atmel logo and combinations thereof, Enabling Unlimited Possibilities®, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. Other terms and product names may be trademarks of others.

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.