## SST25VF040B to SST25PF040C Migration

#### 1.0 INTRODUCTION

The Serial Flash 25 Series family features a four-wire, SPI-compatible interface that allows for a low pin-count package which occupies less board space and ultimately lowers total system costs. SPI serial flash memory is manufactured with proprietary, high-performance CMOS SuperFlash® technology. The split-gate cell

design and thick-oxide tunneling injector attain better reliability and manufacturability compared with alternate approaches.

This document lists all the firmware and hardware changes required to migrate from SST25VF040B to SST25PF040C. Refer to the SST25VF040B (DS20005051) and SST25PF040C data sheets (DS20005397) for more information.

TABLE 1-1: SUMMARY OF CHANGES REQUIRED FOR ALL PART NUMBERS AND PACKAGES

| Current Part                                            | Recommended Upgrade                    | Board Layout/<br>Footprint Change | Firmware Change |

|---------------------------------------------------------|----------------------------------------|-----------------------------------|-----------------|

| SST25VF040B-50-4I-SAE/SAF<br>(8-lead SOIC, 150 mm body) | SST25PF040C-40I/SN<br>(8-lead SOIC)    | No                                | Yes             |

| SST25VF040B-50-4I-S2AE/S2AF (8-lead SOIC, 200 mm body)  | SST25PF040C-40I/SN<br>(8-lead SOIC)    | Yes                               | Yes             |

| SST25VF040B-50-4I-QAE/QAF<br>(8-contact WSON)           | SST25PF040C-40I/MF<br>(8-contact WDFN) | No                                | Yes             |

TABLE 1-2: PIN LAYOUT COMPARISON, 8-CONTACT PACKAGE

| Pin No. | SST25VF040B | SST25PF040C |

|---------|-------------|-------------|

| 1       | CE#         | CE#         |

| 2       | SO          | SO/SIO1     |

| 3       | WP#         | WP#         |

| 4       | VSS         | VSS         |

| 5       | SI          | SI/SIO0     |

| 6       | SCK         | SCK         |

| 7       | HOLD#       | HOLD#       |

| 8       | VDD         | VDD         |

# 2.0 MIGRATION CONSIDERATIONS

The following topics should be considered when migrating from SST25VF040B to SST25PF040C.

#### 2.1 Protection at Power-Up

SST25VF040B powers up with the memory protected. This protection must be removed, by clearing the protection bits in the status register, before executing Program or Erase operations.

The SST25VF040B status register has BP0, BP1, BP2, BP3, and BPL protection bits. To clear all protection set these bits to '0', see Table 2-1. These protection bits are volatile and are set to '1' after power up.

Similarly, SST25PF040C offers BP0, BP1, BP2, BPL, and TB as protection bits in the status register, see Table 2-2. However, these protection bits are non-volatile, and the state of protection will remain same before and after a power cycle. Similar to SST25VF040B, the SST25PF040C can execute Program or Erase commands after clearing the protection bits.

TABLE 2-1: SOFTWARE STATUS REGISTER – SST25VF040B

| Bit | Name | Function                                                                                   | Default at<br>Power-up | Read/Write |

|-----|------|--------------------------------------------------------------------------------------------|------------------------|------------|

| 0   | BUSY | 1 = Internal Write operation is in progress 0 = No internal Write operation is in progress | 0                      | R          |

| 1   | WEL  | L 1 = Device is memory Write enabled 0 = Device is not memory Write enabled                |                        | R          |

| 2   | BP0  | Indicate current level of block write protection (See Table 2-3)                           | 1                      | R/W        |

| 3   | BP1  | Indicate current level of block write protection (See Table 2-3)                           | 1                      | R/W        |

| 4   | BP2  | Indicate current level of block write protection (See Table 2-3)                           | 1                      | R/W        |

| 5   | BP3  | Indicate current level of block write protection (See Table 2-3)                           | 0                      | R/W        |

| 6   | AAI  | Auto Address Increment Programming status 1 = AAI programming mode 0 = Byte-Program mode   | 0                      | R          |

| 7   | BPL  | 1 = BP3, BP2, BP1, BP0 are read-only bits<br>0 = BP3, BP2, BP1, BP0 are read/writable      | 0                      | R/W        |

#### TABLE 2-2: SOFTWARE STATUS REGISTER -SST25PF040C

| Bit | Name             | Function                                                                                                                        | Default at<br>Power-up | Read/Write |

|-----|------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------|------------|

| 0   | BUSY             | <ul><li>1 = Internal Write operation is in progress</li><li>0 = No internal Write operation is in progress</li></ul>            | 0                      | R          |

| 1   | WEL              | 1 = Device is memory Write enabled<br>0 = Device is not memory Write enabled                                                    | 0                      | R          |

| 2   | BP0 <sup>1</sup> | Indicate current level of block write protection (See Table 2-4)                                                                | 0 or 1                 | R/W        |

| 3   | BP1 <sup>1</sup> | Indicate current level of block write protection (See Table 2-4)                                                                | 0 or 1                 | R/W        |

| 4   | BP2 <sup>1</sup> | Indicate current level of block write protection (See Table 2-4)                                                                | 0 or 1                 | R/W        |

| 5   | TB <sup>1</sup>  | 1 = 1/8, 1/4, or 1/2 Bottom Memory Blocks are protected (See Table 2-4)<br>0 = 1/8, 1/4, or 1/2 Top Memory Blocks are protected | 0 or 1                 | R/W        |

| 6   | RES              | Reserved for future use                                                                                                         | 0                      | N/A        |

| 7   | BPL <sup>1</sup> | 1 = BP0, BP1, BP2, TB, and BPL are read-only bits<br>0 = BP0, BP1, BP2, TB, and BPL are read/writable                           | 0 or 1                 | R/W        |

<sup>1.</sup> BP0, BP1, BP2, TB, and BPL bits are non-volatile memory bits.

The protection bits for SST25PF040C offer both upper and lower memory-block protection. The memory-block protection for SST25VF040B is shown in Table 2-3 and the protection for SST25PF040C is shown in Table 2-4.

TABLE 2-3: SOFTWARE STATUS REGISTER BLOCK PROTECTION – SST25VF040B<sup>1</sup>

|                                      | Status Register Bit <sup>2</sup> |     |     | 2   | Protected Memory Address |

|--------------------------------------|----------------------------------|-----|-----|-----|--------------------------|

| Protection Level                     |                                  | BP2 | BP1 | BP0 | 4 Mbit                   |

| None                                 | Х                                | 0   | 0   | 0   | None                     |

| Upper 1/8 Top Memory Block Protected | Х                                | 0   | 0   | 1   | 070000H-07FFFFH          |

| Upper 1/4 Top Memory Block Protected | Х                                | 0   | 1   | 0   | 060000H-07FFFFH          |

| Upper 1/2 Top Memory Block Protected | Х                                | 0   | 1   | 1   | 040000H-07FFFFH          |

| All Blocks                           | Х                                | 1   | 0   | 0   | 000000H-07FFFH           |

| All Blocks                           | Х                                | 1   | 0   | 1   | 000000H-07FFFH           |

| All Blocks                           | Х                                | 1   | 1   | 0   | 000000H-07FFFFH          |

| All Blocks                           | Х                                | 1   | 1   | 1   | 000000H-07FFFFH          |

<sup>1.</sup> X = Don't Care (RESERVED) default is "0

TABLE 2-4: SOFTWARE STATUS REGISTER BLOCK PROTECTION -SST25PF040C

|                                        | Status Register Bit |     |     |     |                          |

|----------------------------------------|---------------------|-----|-----|-----|--------------------------|

| Protection Level                       |                     | BP2 | BP1 | BP0 | Protected Memory Address |

| 0 (Full Memory Array unprotected)      | Х                   | 0   | 0   | 0   | None                     |

| T1 (1/8 Top Memory Block protected)    | 0                   | 0   | 0   | 1   | 070000H-07FFFFH          |

| T2 (1/4 Top Memory Block protected)    | 0                   | 0   | 1   | 0   | 060000H-07FFFFH          |

| T3 (1/2 Top Memory Block protected)    | 0                   | 0   | 1   | 1   | 040000H-07FFFFH          |

| B1 (1/8 Bottom Memory Block protected) | 1                   | 0   | 0   | 1   | 000000H-00FFFFH          |

| B2 (1/4 Bottom Memory Block protected) | 1                   | 0   | 1   | 0   | 000000H-01FFFFH          |

| B3 (1/2 Bottom Memory Block protected) | 1                   | 0   | 1   | 1   | 000000H-03FFFFH          |

| 4 (Full Memory Block protected)        | Х                   | 1   | Х   | Х   | 000000H-07FFFFH          |

#### 2.2 JEDEC Device ID

The JEDEC Device ID for SST25VF040B is BF258DH. The JEDEC Device ID for SST25PF040C is 620613H.

#### 2.3 Communication Protocol

Both SST25VF040B and SST25PF040C use SPI protocol. SST25PF040C also supports Dual-Output Read and Dual-I/O Read.

SST25VF040B supports a maximum clock frequency of 50 MHz while SST25PF040C supports a maximum clock frequency of 40 MHz.

<sup>2.</sup> Default at power-up for BP2, BP1, and BP0 is '111'. (All Blocks Protected)

#### 2.4 Commands Compatibility

Most operation commands of SST25VF040B are compatible with SST25PF040C with minimal changes required. See Table 2-5.

TABLE 2-5: OPERATION COMMAND COMPATIBILITY

| SST25VF040B Device Operation Instructions | OpCode        | Compatible with SST25PF040C | Comments                                                                                                              |

|-------------------------------------------|---------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Read                                      | 03H           | Yes                         |                                                                                                                       |

| High-Speed Read                           | 0BH           | Yes                         |                                                                                                                       |

| 4 KByte Sector-Erase                      | 20H           | Yes                         |                                                                                                                       |

| 32KByte Block Erase                       | 52H           | Change Required             | This command is not supported by SST25PF040C.                                                                         |

| 64KByte Block Erase                       | D8H           | Yes                         |                                                                                                                       |

| Chip-Erase                                | 60H or<br>C7H | Yes                         |                                                                                                                       |

| Byte-Program                              | 02H           | Yes                         |                                                                                                                       |

| AAI Word-Program                          | ADH           | Change Required             | SST25PF040C does not support AAI Word-Program. Instead, perform page programming using the 02H command.               |

| RDSR                                      | 05H           | Yes                         |                                                                                                                       |

| EWSR                                      | 50H           | Change Required             | Not supported by SST25PF040C                                                                                          |

| WRSR                                      | 01H           | Yes                         |                                                                                                                       |

| WREN                                      | 06H           | Yes                         |                                                                                                                       |

| WRDI                                      | 04H           | Yes                         |                                                                                                                       |

| RDID                                      | 90H or<br>ABH | Change Required             | 90H command is not supported by SST25PF040C. However, ABH is supported.                                               |

| JEDEC-ID                                  | 9FH           | Change Required             | Device ID is different between two parts.                                                                             |

| EBSY                                      | 70H           | Change Required             | SST25PF040C does not support Hardware End-of-Write detection. Therefore, the device does not support the 70H command. |

| DBSY                                      | 80H           | Change Required             | SST25PF040C does not support Hardware End-of-Write detection. Therefore, the device does not support the 80H command. |

New operation commands that need to be developed are listed in Table 2-6.

TABLE 2-6: NEW OPERATION COMMANDS

| Instruction                               | OpCode |  |  |  |

|-------------------------------------------|--------|--|--|--|

| Required Instruction                      |        |  |  |  |

| Page Programming                          | 02     |  |  |  |

| Instructions to Add Capability (optional) |        |  |  |  |

| Deep Power-Down Mode                      | В9Н    |  |  |  |

| Release DPD Mode                          | ABH    |  |  |  |

| Fast Read Dual Output                     | 3BH    |  |  |  |

| Fast Read Dual I/O                        | ВВН    |  |  |  |

# 2.4.1 32-KBYTE BLOCK ERASE NOT SUPPORTED

SST25PF040C does not support 32-KByte Block Erase and thus the firmware must be modified to instead make use of either 4-KByte Sector Erase or 64-KByte Block Erase.

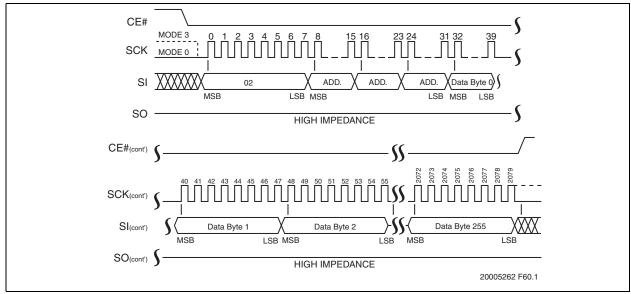

# 2.4.2 PAGE PROGRAMMING SUPPORTED

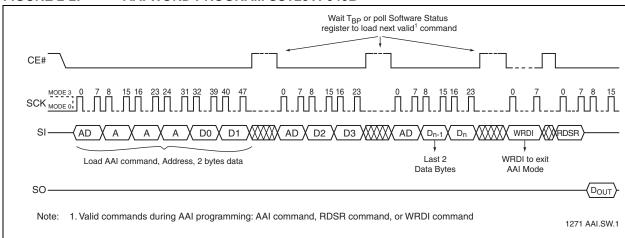

SST25VF040B allow Byte Program and AAI Word Program instructions for programming. SST25PF040C allow Page Program instruction for programming.

Byte Program and AAI Word Program allow programming one and two bytes of data respectively, while the Page Program instruction allows programming one to 256 bytes of data at a time.

For SST25VF040B, the maximum time to program one byte of data using Byte Program instruction, or two bytes of data using AAI-word Program instruction, is 10µs. For SST25PF040C, the maximum time to pro-

gram 256 bytes of data, using Page Program instruction, is 5 ms. If less than 256 bytes of data is programmed, it would take less than the 5 ms maximum time. Before proceeding to the next instruction,

the controller can either wait the maximum program time or keep reading the status register to detect end of programming.

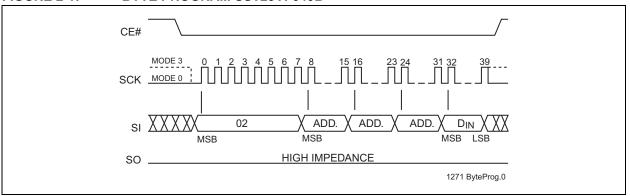

The Byte Program, AAI Word-Program, and Page-Program instructions are shown in Figures 2-1 –2-3.

FIGURE 2-1: BYTE PROGRAM SST25VF040B

#### FIGURE 2-2: AAI WORD PROGRAM SST25VF040B

#### FIGURE 2-3: PAGE PROGRAM INSTRUCTION SST25PF040C

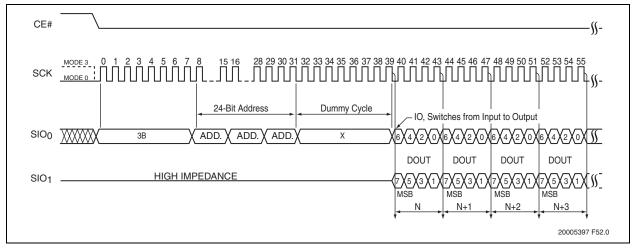

# 2.4.3 SPI DUAL-OUTPUT READ AND SPI DUAL I/O READ COMMANDS

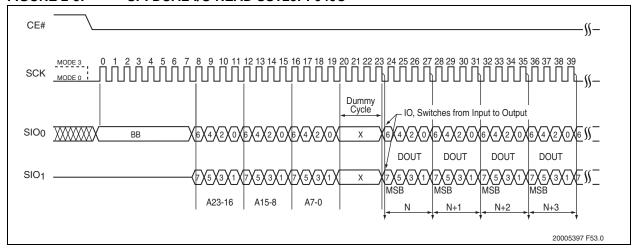

SST25PF040C supports SPI Dual-Output Read and SPI Dual-I/O Read commands. If the host controller can support these two commands then the Read performance

can be doubled when compared to SST25VF040B. See Figure 2-4 for SPI Dual-Output Read command operation and Figure 2-5 for SPI Dual-I/O Read command operation.

#### FIGURE 2-4: SPI DUAL-OUTPUT READ SST25PF040C

#### FIGURE 2-5: SPI DUAL-I/O READ SST25PF040C

#### 3.0 CONCLUSION

This document describes the aspects to consider when migrating from SST25VF040B to SST25PF040C. SST25PF040C operates over a wide voltage-range of 2.3 - 3.6V and features ultra-low standby current for battery-powered, energy-sensitive designs.

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the

intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### **Trademarks**

The Microchip name and logo, the Microchip logo, AnyRate, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, KeeLoq logo, Kleer, LANCheck, LINK MD, MediaLB, MOST, MOST logo, MPLAB, OptoLyzer, PIC, PICSTART, PIC32 logo, RightTouch, SpyNIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, ETHERSYNCH, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and QUIET-WIRE are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Any Capacitor, Anyln, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, RightTouch logo, REAL ICE, Ripple Blocker, Serial Quad I/O, SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2016, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-0478-1

#### Worldwide Sales and Service

#### **AMERICAS**

**Corporate Office** 2355 West Chandler Blvd. Chandler, AZ 85224-6199

Tel: 480-792-7200 Fax: 480-792-7277 **Technical Support:**

http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614

Fax: 678-957-1455 Austin, TX

Tel: 512-257-3370 **Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX

Tel: 281-894-5983 Indianapolis

Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

Canada - Toronto Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong

Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongging Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

China - Hangzhou Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR Tel: 852-2943-5100 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao Tel: 86-532-8502-7355

Fax: 86-532-8502-7205 China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

China - Wuhan Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

Fax: 86-27-5980-5118

Fax: 86-29-8833-7256

#### ASIA/PACIFIC

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631

Fax: 91-11-4160-8632 India - Pune

Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

Japan - Tokyo Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or

82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065

Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung

Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Dusseldorf** Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

Germany - Munich Tel: 49-89-627-144-0

Fax: 49-89-627-144-44 Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw

Tel: 48-22-3325737

Spain - Madrid Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

07/14/15