#### Document Number: MC10XS3425 Rev. 6.0, 8/2018

# Quad high-side switch (dual 10 mOhm, dual 25 mOhm)

The 10XS3425 is one in a family of devices designed for low-voltage automotive lighting applications. Its four low  $R_{DS(on)}$  MOSFETs (dual 10  $m\Omega/\text{dual}$  25  $m\Omega)$  can control four separate 55 W/28 W bulbs, and/or Xenon modules, and/or LEDs.

Programming, control and diagnostics are accomplished using a 16-bit SPI interface. Its output with selectable slew-rate improves electromagnetic compatibility (EMC) behavior. Additionally, each output has its own parallel input or SPI control for pulse-width modulation (PWM) control if desired. The 10XS3425 allows the user to program via the SPI the fault current trip levels and duration of acceptable lamp inrush. The device has Fail-safe mode to provide fail-safe functionality of the outputs in case of MCU damaged. This device is powered by SMARTMOS technology.

#### **Features**

- Four protected 10 m $\Omega$  and 25 m $\Omega$  high-side switches (at 25 °C)

- Operating voltage range of 6.0 to 20 V with sleep current  $<5.0~\mu\text{A},$  extended mode from 4.0 to 28 V

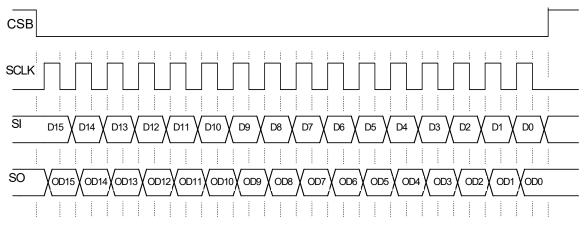

- 8.0 MHz 16-bit 3.3 V and 5.0 V SPI control and status reporting with daisy chain capability

- PWM module using external clock or calibratable internal oscillator with programmable output delay management

- Smart overcurrent shutdown, severe short-circuit, overtemperature protections with time limited autoretry, and fail-safe mode, in case of MCU damage

- Output off or on openload detection compliant to bulbs or leds and short to battery detection, analog current feedback with selectable ratio and board temperature feedback

#### 10XS3425

#### **HIGH-SIDE SWITCH**

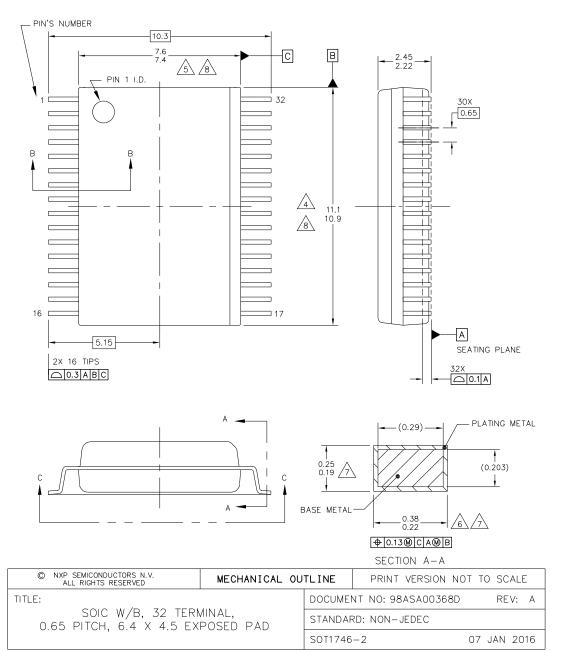

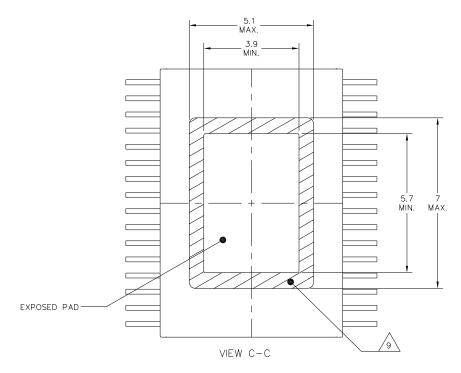

EK SUFFIX (PB-FREE) 98ASA00368D 32-PIN EXPOSED PAD SOIC

#### **Applications**

- · Low-voltage automotive exterior lighting

- · Low-voltage industrial lighting

- · Halogen lamps

- · Incandescent bulbs

- Light-emitting diodes (LEDs)

- · HID Xenon ballasts

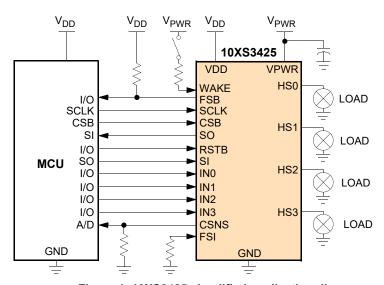

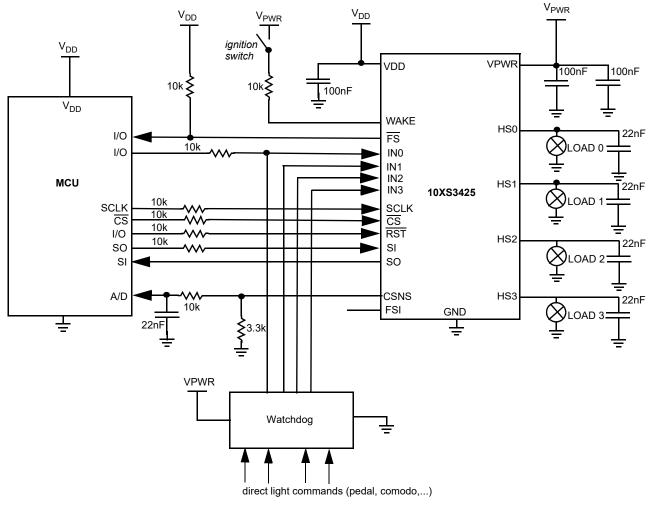

Figure 1. 10XS3425 simplified application diagram

# **Table of Contents**

| 1 | Orderable parts                           | 3    |

|---|-------------------------------------------|------|

| 2 | Internal block diagram                    | 4    |

| 3 | Pin connections                           | 5    |

|   | 3.1 Pinout diagram                        | 5    |

|   | 3.2 Pin definitions                       | 5    |

| 4 | Electrical characteristics                | 7    |

|   | 4.1 Maximum ratings                       | 7    |

|   | 4.2 Static electrical characteristics     | 9    |

|   | 4.3 Dynamic electrical characteristics    | . 14 |

|   | 4.4 Timing diagrams                       | . 21 |

| 5 | Functional description                    |      |

|   | 5.1 Introduction                          |      |

|   | 5.2 Functional pin description            | . 24 |

|   | 5.3 Functional internal block description | . 26 |

| 6 | Functional device operation               | . 27 |

|   | 6.1 SPI protocol description              | . 27 |

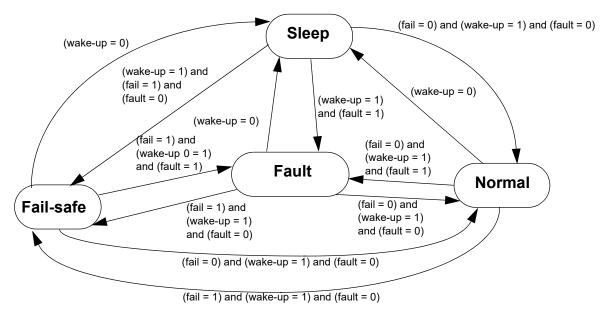

|   | 6.2 Operational modes                     | . 27 |

|   | 6.3 Protection and diagnostic features    | . 32 |

|   | 6.4 Logic commands and registers          | . 36 |

| 7 | Typical applications                      | . 46 |

|   | 7.1 Introduction                          | . 46 |

| 8 | Packaging                                 | . 47 |

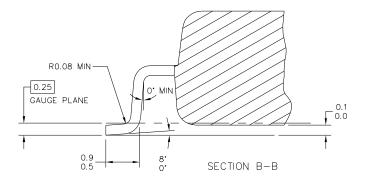

|   | 8.1 Soldering information                 | . 47 |

|   | 8.2 Marking information                   | . 47 |

|   | 8.3 Package mechanical dimensions         | . 47 |

| 9 | Revision history                          | . 51 |

# 1 Orderable parts

This section describes the part numbers available to be purchased along with their differences.

Table 1. Orderable part variations

| Part number <sup>(1)</sup> | Temperature (T <sub>A</sub> ) | Package                 |

|----------------------------|-------------------------------|-------------------------|

| Quad version               |                               |                         |

| MC10XS3425EK               | -40 to 125 °C                 | 32-pin SOIC exposed pad |

#### Notes

Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to <a href="http://www.nxp.com">http://www.nxp.com</a> and perform a part number search.

10XS3425

<sup>1.</sup> To order parts in tape and reel, add the R2 suffix to the part number.

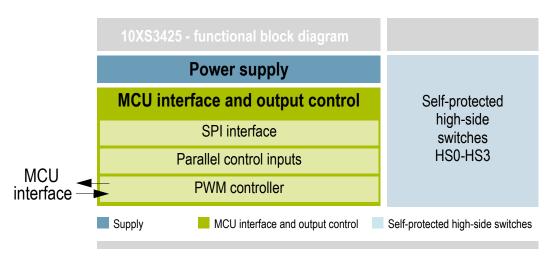

# 2 Internal block diagram

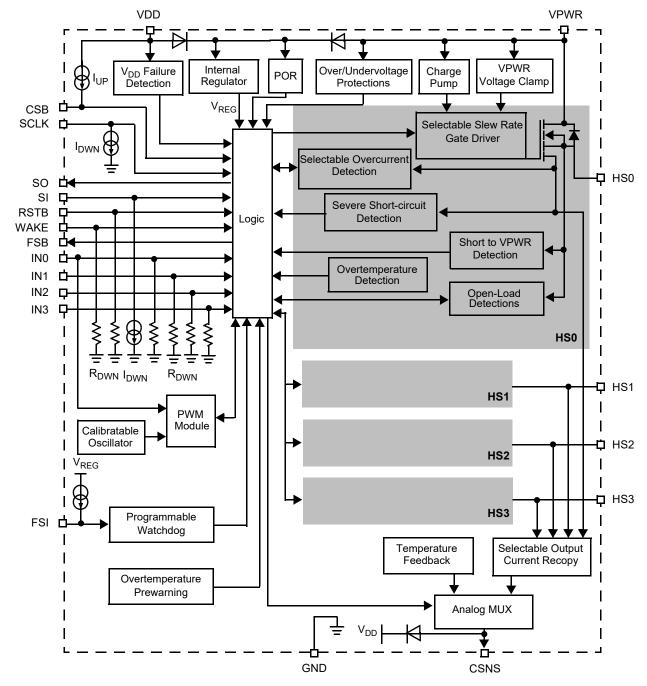

Figure 2. 10XS3425 simplified internal block diagram

# 3 Pin connections

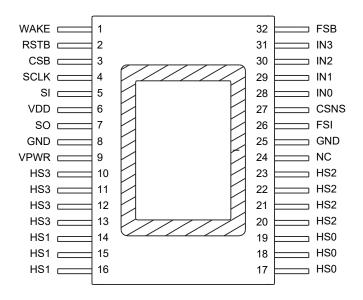

# 3.1 Pinout diagram

#### Transparent top view of package

Figure 3. 10XS3425 pin connections

### 3.2 Pin definitions

A functional description of each pin can be found in the Functional Pin Description section beginning on page 24.

Table 2. 10XS3425 pin definitions

| Pin<br>number | Pin name | Pin function | Formal name              | Definition                                                                                                                                                   |

|---------------|----------|--------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | WAKE     | Input        | Wake                     | This input pin controls the device mode.                                                                                                                     |

| 2             | RSTB     | Input        | Reset                    | This input pin is used to initialize the device configuration and fault registers, as well as place the device in a low-current Sleep mode.                  |

| 3             | CSB      | Input        | Chip select (active low) | This input pin is connected to a chip select output of a master microcontroller (MCU).                                                                       |

| 4             | SCLK     | Input        | Serial clock             | This input pin is connected to the MCU providing the required bit shift clock for SPI communication.                                                         |

| 5             | SI       | Input        | Serial input             | This pin is a command data input pin connected to the SPI Serial Data Output of the MCU or to the SO pin of the previous device of a daisy-chain of devices. |

| 6             | VDD      | Power        | Digital drain voltage    | This pin is an external voltage input pin used to supply power interfaces to the SPI bus.                                                                    |

| 7             | so       | Output       | Serial output            | This output pin is connected to the SPI Serial Data Input pin of the MCU or to the SI pin of the next device of a daisy-chain of devices.                    |

10XS3425

Table 2. 10XS3425 pin definitions (continued)

| Pin<br>number        | Pin name                 | Pin function | Formal name               | Definition                                                                                                                                                                                                                                                                                    |

|----------------------|--------------------------|--------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8, 25                | GND                      | Ground       | Ground                    | These pins, internally shorted, are the ground for the logic and analog circuitry of the device. These ground pins must be also shorted in the board.                                                                                                                                         |

| 9, 33                | VPWR                     | Power        | Positive power supply     | This pin connects to the positive power supply and is the source of operational power for the device. Pins 9 and 33 must be externally connected.                                                                                                                                             |

| 10, 11, 12,<br>13    | HS3                      | Output       | High-side output          | Protected 25 m $\Omega$ high-side power output pins to the load.                                                                                                                                                                                                                              |

| 14, 15, 16           | HS1                      | Output       | High-side output          | Protected 10 m $\Omega$ high-side power output pins to the load.                                                                                                                                                                                                                              |

| 17, 18, 19           | HS0                      | Output       | High-side output          | Protected 10 m $\Omega$ high-side power output pins to the load.                                                                                                                                                                                                                              |

| 20, 21, 22,<br>23    | HS2                      | Output       | High-side output          | Protected 25 m $\Omega$ high-side power output pins to the load.                                                                                                                                                                                                                              |

| 24                   | NC                       | N/A          | No connect                | This pin may not be connected.                                                                                                                                                                                                                                                                |

| 26                   | FSI                      | Input        | Fail-safe input           | This input enables the watchdog timeout feature.                                                                                                                                                                                                                                              |

| 27                   | CSNS                     | Output       | Output current monitoring | This pin reports an analog value proportional to the designated HS[0:3] output current or the temperature of the GND flag (pin 14). It is used externally to generate a ground-referenced voltage for the microcontroller (MCU). Current recopy and temperature feedback is SPI programmable. |

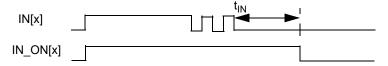

| 28<br>29<br>30<br>31 | IN0<br>IN1<br>IN2<br>IN3 | Input        | Direct inputs             | Each direct input controls the device mode. The IN[0:3] high-side input pins are used to directly control HS0:HS3 high-side output pins.  The PWM frequency can be generated from IN0 pin to PWM module in case of external clock is set.                                                     |

| 32                   | FSB                      | Output       | Fault status (active low) | This pin is an open drain configured output requiring an external pull-up resistor to VDD for fault reporting.                                                                                                                                                                                |

10XS3425

# 4 Electrical characteristics

### 4.1 Maximum ratings

#### Table 3. Maximum ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                                                      | Ratings                                                                                                                                                                                                                           | Value                        | Unit | Notes |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|-------|

| lectrical rating                                            | s                                                                                                                                                                                                                                 |                              |      |       |

| V <sub>PWR(SS)</sub>                                        | VPWR supply voltage range  • Load dump at 25 °C (400 ms)  • Maximum operating voltage  • Reverse battery                                                                                                                          | 41<br>28<br>-18              | V    |       |

| $V_{DD}$                                                    | VDD supply voltage range                                                                                                                                                                                                          | -0.3 to 5.5                  | V    |       |

| $V_{DIG}$                                                   | Input/output voltage                                                                                                                                                                                                              | -0.3 to 5.5                  | V    | (5)   |

| V <sub>SO</sub>                                             | SO and CSNS output voltage                                                                                                                                                                                                        | -0.3 to V <sub>DD</sub> +0.3 | V    |       |

| I <sub>DIG</sub>                                            | Digital input/output current in Clamp mode                                                                                                                                                                                        | 100                          | μA   |       |

| I <sub>CL(WAKE)</sub>                                       | WAKE input clamp current                                                                                                                                                                                                          | 2.5                          | mA   |       |

| I <sub>CL(CSNS)</sub>                                       | CSNS input clamp current                                                                                                                                                                                                          | 2.5                          | mA   |       |

| V <sub>HS[0:3]</sub>                                        | HS [0:3] voltage  • Positive  • Negative                                                                                                                                                                                          | 41<br>-24                    | V    |       |

| V <sub>PWR</sub> - V <sub>HS</sub>                          | High-side breakdown voltage                                                                                                                                                                                                       | 47                           | V    |       |

| I <sub>HS[0:3]</sub>                                        | Output current                                                                                                                                                                                                                    | 6.0                          | Α    | (2)   |

| E <sub>CL[0:1]</sub>                                        | HS[0,1] output clamp energy using single pulse method                                                                                                                                                                             | 60                           | mJ   | (3)   |

| E <sub>CL[2:3]</sub>                                        | HS[2,3] output clamp energy using single pulse method                                                                                                                                                                             | 25                           | mJ   | (3)   |

| V <sub>ESD1</sub><br>V <sub>ESD2</sub><br>V <sub>ESD3</sub> | ESD voltage (V <sub>PWR</sub> pins 9 and 33 must be externally connected.)  • Human Body Model (HBM) for HS[0:3], VPWR and GND  • Human Body Model (HBM) for other pins  • Charge Device Model (CDM)  Corner pins (1, 13, 19, 21) | ±8000<br>±2000<br>±750       | V    | (4)   |

| $V_{ESD4}$                                                  | All other pins (2-12, 14-18, 20, 22-24)                                                                                                                                                                                           | ±500                         |      |       |

| hermal ratings                                              |                                                                                                                                                                                                                                   |                              |      |       |

| T <sub>A</sub><br>T <sub>J</sub>                            | Operating temperature                                                                                                                                                                                                             | -40 to 125<br>-40 to 150     | °C   |       |

| T <sub>STG</sub>                                            | Storage temperature                                                                                                                                                                                                               | -55 to 150                   | °C   |       |

#### Notes

- 2. Continuous high-side output current rating so long as maximum junction temperature is not exceeded. Calculation of maximum output current using package thermal resistance is required.

- 3. Active clamp energy using single-pulse method (L = 2.0 mH,  $R_L$  = 0  $\Omega$ ,  $V_{PWR}$  = 14 V,  $T_J$  = 150  $^{\circ}$ C initial).

- 4. Pins 9 and 33 must be externally connected. ESD testing is performed in accordance with the Human Body Model (HBM) ( $C_{ZAP} = 100 \text{ pF}$ ,  $R_{ZAP} = 1500 \Omega$ ), the Machine Model (MM) ( $C_{ZAP} = 200 \text{ pF}$ ,  $R_{ZAP} = 0 \Omega$ ), and the Charge Device Model (CDM), Robotic ( $C_{ZAP} = 4.0 \text{ pF}$ ).

- 5. Input / Output pins are: IN[0:3], RSTB, FSI, SI, SCLK, CSB, and FSB

10XS3425

#### Table 3. Maximum ratings (continued)

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                               | Ratings                                                             | Value     | Unit | Notes    |

|--------------------------------------|---------------------------------------------------------------------|-----------|------|----------|

| Thermal resistar                     | nce                                                                 |           | •    | •        |

| R <sub>θJC</sub><br>R <sub>θJA</sub> | Thermal resistance     • Junction to Case     • Junction to Ambient | 0.5<br>23 | °C/W | (6), (7) |

| T <sub>SOLDER</sub>                  | Peak Pin Reflow Temperature During Solder Mounting                  | 260       | °C   | (8)      |

#### Notes

- 6. Thermal resistance between the die and the solder pad on the bottom of the package. Interface resistance is ignored

- 7. Device mounted on a 2s2p test board per JEDEC JESD51-2. 15  $^{\circ}$ C/W of R<sub> $\theta$ JA</sub> can be reached in a real application case (4 layers board).

- 8. Pin soldering temperature limit is for 40 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

### 4.2 Static electrical characteristics

#### Table 4. Static electrical characteristics

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  20 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                      | Characteristic                                                                                                                                                                                                                      | Min        | Тур        | Max       | Unit                  | Notes |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|-----------|-----------------------|-------|

| Power inputs                | 3                                                                                                                                                                                                                                   | - J        |            |           |                       |       |

| $V_{PWR}$                   | Battery supply voltage range • Fully operational • Extended mode                                                                                                                                                                    | 6.0<br>4.0 | _<br>_     | 20<br>28  | V                     | (9)   |

| V <sub>PWR</sub><br>(CLAMP) | Battery clamp voltage                                                                                                                                                                                                               | 41         | 47         | 53        | V                     | (10)  |

| I <sub>PWR(ON)</sub>        | V <sub>PWR</sub> operating supply current • Outputs commanded ON, HS[0:3] open, IN[0:3] > V <sub>IH</sub>                                                                                                                           | _          | 6.5        | 20        | mA                    |       |

| I <sub>PWR(SBY)</sub>       | V <sub>PWR</sub> supply current • Outputs commanded OFF, OFF openload detection disabled, HS[0:3] shorted to the ground with V <sub>DD</sub> = 5.5 V WAKE > V <sub>IH</sub> or RSTB > V <sub>IH</sub> and IN[0:3] < V <sub>IL</sub> | -          | 6.5        | 7.5       | mA                    |       |

| I <sub>PWR(SLEEP)</sub>     | Sleep state supply current $V_{PWR}$ = 12 V, RSTB = WAKE = IN[0:3] < $V_{IL}$ , HS[0:3] shorted to ground • $T_A$ = 25 °C • $T_A$ = 85 °C                                                                                           | _<br>_     | 1.0        | 5.0<br>30 | μА                    |       |

| V <sub>DD(ON)</sub>         | V <sub>DD</sub> supply voltage                                                                                                                                                                                                      | 3.0        | _          | 5.5       | V                     |       |

| I <sub>DD(ON)</sub>         | V <sub>DD</sub> supply current at V <sub>DD</sub> = 5.5 V • No SPI communication • 8.0 MHz SPI communication                                                                                                                        | -<br>-     | 1.6<br>5.0 | 2.2       | mA                    | (11)  |

| I <sub>DD(SLEEP)</sub>      | V <sub>DD</sub> sleep state current at V <sub>DD</sub> = 5.5 V                                                                                                                                                                      | _          | _          | 5.0       | μΑ                    |       |

| V <sub>PWR(OV)</sub>        | Overvoltage shutdown threshold                                                                                                                                                                                                      | 28         | 32         | 36        | V                     |       |

| V <sub>PWR</sub><br>(OVHYS) | Overvoltage shutdown hysteresis                                                                                                                                                                                                     | 0.2        | 0.8        | 1.5       | V                     |       |

| V <sub>PWR(UV)</sub>        | Undervoltage shutdown threshold                                                                                                                                                                                                     | 3.3        | 3.9        | 4.3       | V                     | (12)  |

| V <sub>SUPPLY</sub> (POR)   | V <sub>PWR</sub> and V <sub>DD</sub> power-on reset threshold                                                                                                                                                                       | 0.5        | _          | 0.9       | V <sub>PWR</sub> (UV) |       |

| V <sub>PWR(UV)</sub><br>_UP | Recovery undervoltage threshold                                                                                                                                                                                                     | 3.4        | 4.1        | 4.5       | V                     |       |

| $V_{DD(FAIL)}$              | V <sub>DD</sub> supply failure threshold (for V <sub>PWR</sub> > V <sub>PWR(UV)</sub> )                                                                                                                                             | 2.2        | 2.5        | 2.8       | ٧                     |       |

#### Notes

- 9. In extended mode, the functionality is guaranteed but not the electrical parameters. From 4.0 to 6.0 V voltage range, the device is only protected with the thermal shutdown detection.

- 10. Measured with the outputs open.

- 11. Typical value guaranteed per design.

- 12. Output will automatically recover with time limited autoretry to instructed state when V<sub>PWR</sub> voltage is restored to normal as long as the V<sub>PWR</sub> degradation level did not go below the undervoltage power-on reset threshold. This applies to all internal device logic that is supplied by V<sub>PWR</sub> and assumes that the external V<sub>DD</sub> supply is within specification.

10XS3425

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  20 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                 | Characteristic                                                                                                                                                                                                                                                                                                                                                         | Min              | Тур              | Max                       | Unit | Notes |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|---------------------------|------|-------|

| Outputs HS0            | TO HS3                                                                                                                                                                                                                                                                                                                                                                 |                  | 1                |                           | ı    |       |

| R <sub>DS_01(on)</sub> | $\begin{aligned} & \text{HS}[0,1] \text{ output Drain-to-Source ON resistance } (I_{\text{HS}} = 5.0 \text{ A}, T_{\text{A}} = 25 \text{ °C}) \\ & \bullet \text{V}_{\text{PWR}} = 4.5 \text{ V} \\ & \bullet \text{V}_{\text{PWR}} = 6.0 \text{ V} \\ & \bullet \text{V}_{\text{PWR}} = 10 \text{ V} \\ & \bullet \text{V}_{\text{PWR}} = 13 \text{ V} \end{aligned}$ | -<br>-<br>-<br>- | -<br>-<br>-<br>- | 36<br>16<br>10<br>10      | mΩ   |       |

| R <sub>DS_01(on)</sub> | HS[0,1] output Drain-to-Source ON resistance (I <sub>HS</sub> = 5.0 A, T <sub>A</sub> = 150 °C)  • V <sub>PWR</sub> = 4.5 V  • V <sub>PWR</sub> = 6.0 V  • V <sub>PWR</sub> = 10 V  • V <sub>PWR</sub> = 13 V                                                                                                                                                          | -<br>-<br>-<br>- | -<br>-<br>-<br>- | 62<br>27<br>17<br>17      | mΩ   |       |

| R <sub>SD_01(on)</sub> | HS[0,1] output Source-to-Drain ON resistance ( $I_{HS}$ = -5.0 A, $V_{PWR}$ = -18 V) • $T_A$ = 25 °C • $T_A$ = 150 °C                                                                                                                                                                                                                                                  |                  | _<br>_           | 15<br>20                  | mΩ   | (13)  |

| R <sub>DS_23(on)</sub> | $\begin{aligned} & \text{HS}[2,3] \text{ output Drain-to-Source ON resistance } (I_{\text{HS}} = 5.0 \text{ A}, T_{\text{A}} = 25 \text{ °C}) \\ & \bullet \text{V}_{\text{PWR}} = 4.5 \text{ V} \\ & \bullet \text{V}_{\text{PWR}} = 6.0 \text{ V} \\ & \bullet \text{V}_{\text{PWR}} = 10 \text{ V} \\ & \bullet \text{V}_{\text{PWR}} = 13 \text{ V} \end{aligned}$ | -<br>-<br>-<br>- | -<br>-<br>-<br>- | 90<br>40<br>25<br>25      | mΩ   |       |

| R <sub>DS_23(on)</sub> | HS[2,3] output Drain-to-Source ON resistance (I <sub>HS</sub> = 5.0 A, T <sub>A</sub> = 150 °C)  • V <sub>PWR</sub> = 4.5 V  • V <sub>PWR</sub> = 6.0 V  • V <sub>PWR</sub> = 10 V  • V <sub>PWR</sub> = 13 V                                                                                                                                                          | -<br>-<br>-<br>- | -<br>-<br>-<br>- | 153<br>68<br>42.5<br>42.5 | mΩ   |       |

| R <sub>SD_23(on)</sub> | HS[2,3] output Source-to-Drain ON resistance ( $I_{HS}$ = -5.0 A, $V_{PWR}$ = -18 V)<br>• $T_A$ = 25 °C<br>• $T_A$ = 150 °C                                                                                                                                                                                                                                            | -<br>-           | -<br>-           | 37.5<br>50                | mΩ   | (13)  |

| R <sub>SHORT_01</sub>  | HS[0,1] maximum severe short-circuit impedance detection                                                                                                                                                                                                                                                                                                               | 28               | 67               | 100                       | mΩ   | (14)  |

| R <sub>SHORT_23</sub>  | HS[2,3] maximum severe short-circuit Impedance detection                                                                                                                                                                                                                                                                                                               | 70               | 160              | 200                       | mΩ   | (14)  |

| l <sub>OFF</sub>       | HS[0-3] output leakage current in OFF state  • in Sleep mode  • in Normal mode (OS_dis = 1 and OLOFF_dis = 1)                                                                                                                                                                                                                                                          | _<br>_           | _<br>_           | 5.0<br>30                 | μА   |       |

#### Notes

<sup>13.</sup> Source-Drain ON Resistance (reverse Drain-to-Source ON resistance) with negative polarity V<sub>PWR</sub>.

<sup>14.</sup> Short-circuit impedance calculated from HS[0:3] to GND pins. Value guaranteed per design.

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  20 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol               | Characteristic                                                                                                         | Min  | Тур     | Max   | Unit | Notes |

|----------------------|------------------------------------------------------------------------------------------------------------------------|------|---------|-------|------|-------|

| Outputs HS0          | TO HS3 (continued)                                                                                                     | I.   |         | I.    | I    | 1     |

|                      | HS[0,1] output overcurrent detection levels (6.0 V ≤ V <sub>HS[0:3]</sub> ≤ 20 V)                                      |      |         |       |      |       |

| OCHI1                | ( = no[0.0] = ,                                                                                                        | 77.6 | 101.6   | 125.6 |      |       |

| OCHI2                |                                                                                                                        | 46.4 | 62      | 77.6  |      |       |

| OC1                  |                                                                                                                        | 43.6 | 55.6    | 67.6  |      |       |

| OC2                  |                                                                                                                        | 40.2 | 48.8    | 57.4  |      |       |

| OC3                  |                                                                                                                        | 31.6 | 40.4    | 49.2  | Α    |       |

| OC4                  |                                                                                                                        | 26.2 | 33.2    | 40.2  |      |       |

| OCLO4                |                                                                                                                        | 19.2 | 24.3    | 29.4  |      |       |

| OCLO3                |                                                                                                                        | 12.1 | 15.3    | 18.4  |      |       |

| OCLO2                |                                                                                                                        | 10.3 | 13.1    | 15.9  |      |       |

| OCLO1                |                                                                                                                        | 6.2  | 8.3     | 10.3  |      |       |

|                      | HS[0,1] current sense ratio (6.0 V ≤ HS[0:3] ≤ 20 V, CSNS ≤ 5.0 V)                                                     |      |         |       |      |       |

| C <sub>SR0</sub>     | CSNS_ratio bit = 0                                                                                                     | _    | 1/9900  | _     | _    | (15)  |

| C <sub>SR1</sub>     | CSNS_ratio bit = 1                                                                                                     | _    | 1/58500 | _     |      |       |

|                      | HS[0,1] current sense ratio ( $C_{SR0}$ ) accuracy (6.0 V $\leq$ V <sub>HS[0:1]</sub> $\leq$ 20 V) At 25 °C and 125 °C |      |         |       |      |       |

|                      | • I <sub>HS[0:1]</sub> = 12.5 A                                                                                        | -12  | _       | 12    |      |       |

|                      | • I <sub>HS[0:1]</sub> = 5.0 A                                                                                         | -13  | _       | 13    |      |       |

|                      | • I <sub>HS[0:1]</sub> = 3.0 A                                                                                         | -16  | _       | 16    |      |       |

| C <sub>SR0_ACC</sub> | • I <sub>HS[0:1]</sub> = 1.5 A<br>At -40 °C                                                                            | -20  | _       | 20    | %    |       |

|                      | • I <sub>HS[0:1]</sub> = 12.5 A                                                                                        | -18  | _       | 18    |      |       |

|                      | • I <sub>HS[0:1]</sub> = 5.0 A                                                                                         | -20  | _       | 20    |      |       |

|                      | • I <sub>HS[0:1]</sub> = 3.0 A                                                                                         | -25  | _       | 25    |      |       |

|                      | • I <sub>HS[0:1]</sub> = 1.5 A                                                                                         | -30  | _       | 30    |      |       |

#### Notes

15. Current sense ratio =  $I_{CSNS} / I_{HS[0:3]}$

|                             | 0010 110[0.0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          |             |                      |      |      |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------|----------------------|------|------|

| C <sub>SR0_ACC</sub> (CAL)  | HS[0,1] current recopy accuracy with one calibration point $(6.0 \text{ V} \leq \text{V}_{\text{HS[0:1]}} \leq 20 \text{ V})$ • $I_{\text{HS[0:1]}} = 5.0 \text{ A}$                                                                                                                                                                                                                                                                                                                                           | -5.0                     | -           | 5.0                  | %    | (16) |

| $\Delta(C_{SR0})/\Delta(T)$ | HS[0,1] CSR0 current recopy temperature drift $(6.0 \text{ V} \le \text{V}_{\text{HS}[0:1]} \le 20 \text{ V})$ • $I_{\text{HS}[0:1]} = 5.0 \text{ A}$                                                                                                                                                                                                                                                                                                                                                          | -                        | -           | 0.04                 | %/°C | (17) |

| C <sub>SR1_ACC</sub>        | $\begin{split} & \text{HS[0,1] current sense ratio } (C_{SR1}) \text{ accuracy } (6.0 \text{ V} \leq \text{V}_{\text{HS[0:1]}} \leq 20 \text{ V}) \\ & \text{At } 25 ^{\circ}\text{C} \text{ and } 125 ^{\circ}\text{C} \\ & \bullet \text{ I}_{\text{HS[0:1]}} = 12.5 \text{ A} \\ & \bullet \text{ I}_{\text{HS[0:1]}} = 75\text{A} \\ & \text{At } \text{-40 }^{\circ}\text{C} \\ & \bullet \text{ I}_{\text{HS[0:1]}} = 12.5 \text{ A} \\ & \bullet \text{ I}_{\text{HS[0:1]}} = 75 \text{ A} \end{split}$ | -17<br>-12<br>-25<br>-30 | -<br>-<br>- | 17<br>12<br>25<br>30 | %    |      |

| C <sub>SR1_ACC</sub> (CAL)  | HS[0,1] current recopy accuracy with one calibration point (6.0 V $\leq$ V <sub>HS[0:1]</sub> $\leq$ 20 V) • I <sub>HS[0:1]</sub> = 12.5 A                                                                                                                                                                                                                                                                                                                                                                     | -5.0                     | -           | 5.0                  | %    | (16) |

| V <sub>CL(CSNS)</sub>       | Current sense clamp voltage • CSNS Open; I <sub>HS[0:3]</sub> = 5.0 A with C <sub>SR0</sub> ratio                                                                                                                                                                                                                                                                                                                                                                                                              | V <sub>DD</sub> +0.25    | _           | V <sub>DD</sub> +1.0 | V    |      |

#### Notes

- 16. Based on statistical analysis. It is not production tested.

- 17. Based on statistical data: delta (C<sub>SR0</sub>)/delta (T) = {(measured I<sub>CSNS</sub> at T<sub>1</sub> measured I<sub>CSNS</sub> at T<sub>2</sub>) / measured I<sub>CSNS</sub> at room} / {T<sub>1</sub>-T<sub>2</sub>}. Not production tested.

10XS3425

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  20 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                                              | Characteristic                                                                                                                                                                                                                                                                                                                                                                                              | Min                                                                      | Тур                                                                     | Max                                                                       | Unit | Notes |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------|------|-------|

| OUTPUTS HS                                          | 60 TO HS3 (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                                       |                                                                          |                                                                         | I.                                                                        | I    |       |

| I <sub>OLD(OFF)</sub>                               | OFF openload detection source current                                                                                                                                                                                                                                                                                                                                                                       | 30                                                                       | _                                                                       | 100                                                                       | μА   | (18)  |

| V <sub>OLD(THRES)</sub>                             | OFF openload fault detection voltage threshold                                                                                                                                                                                                                                                                                                                                                              | 2.0                                                                      | 3.0                                                                     | 4.0                                                                       | V    |       |

| I <sub>OLD(ON_LED)</sub>                            | ON openload fault detection current threshold with LED ( $V_{HS[0:3]} = V_{PWR}$ -0.75 V                                                                                                                                                                                                                                                                                                                    | 2.5                                                                      | 5.0                                                                     | 10                                                                        | mA   |       |

| I <sub>OLD(ON)</sub>                                | ON openload fault detection current threshold  • HS[0,1]  • HS[2,3]                                                                                                                                                                                                                                                                                                                                         | 80<br>55                                                                 | 360<br>165                                                              | 660<br>330                                                                | mA   |       |

| V <sub>OSD(THRES)</sub>                             | Output short to V <sub>PWR</sub> detection voltage threshold  • Output programmed OFF                                                                                                                                                                                                                                                                                                                       | V <sub>PWR</sub> -1.2                                                    | V <sub>PWR</sub> -0.8                                                   | V <sub>PWR</sub> -0.4                                                     | V    |       |

| $V_{CL}$                                            | Output negative clamp voltage  • 0.5 A ≤ I <sub>HS[0:3]</sub> ≤ 5.0 A, output programmed OFF                                                                                                                                                                                                                                                                                                                | -22                                                                      | _                                                                       | -16                                                                       | V    |       |

| T <sub>SD</sub>                                     | Output overtemperature shutdown for 4.5 V < V <sub>PWR</sub> < 28 V                                                                                                                                                                                                                                                                                                                                         | 155                                                                      | 175                                                                     | 195                                                                       | °C   |       |

| OCHI1 OCHI2 OC1 OC2 OC3 OC4 OCLO4 OCLO3 OCLO2 OCLO2 | HS[2,3] output overcurrent detection levels (6.0 V $\leq$ V <sub>HS[0:3]</sub> $\leq$ 20 V)                                                                                                                                                                                                                                                                                                                 | 38.8<br>23.2<br>21.8<br>17.3<br>14.7<br>12.2<br>9.2<br>5.8<br>4.6<br>2.9 | 50.8<br>31<br>27.3<br>22.9<br>19.2<br>15.8<br>11.9<br>7.6<br>6.3<br>4.1 | 62.8<br>38.8<br>32.8<br>28.4<br>23.7<br>19.4<br>14.5<br>9.3<br>8.0<br>5.3 | А    |       |

| C <sub>SR0</sub><br>C <sub>SR1</sub>                | HS[2,3] current sense ratio (6.0 V $\leq$ HS[2:3] $\leq$ 20 V, CSNS $\leq$ 5.0 V)<br>CSNS_ratio bit = 0<br>CSNS_ratio bit = 1                                                                                                                                                                                                                                                                               |                                                                          | 1/4670<br>1/27270                                                       | -<br>-                                                                    | _    | (19)  |

| C <sub>SR0_ACC</sub>                                | $\begin{split} & \text{HS}[2,3] \text{ current sense ratio } (C_{\text{SR}0}) \text{ accuracy } (6.0 \text{ V} \leq \text{V}_{\text{HS}[2:3]} \leq 20 \text{ V}) \\ & \bullet \text{I}_{\text{HS}[2:3]} = 6.25 \text{ A} \\ & \bullet \text{I}_{\text{HS}[2:3]} = 2.5 \text{ A} \\ & \bullet \text{I}_{\text{HS}[2:3]} = 1.5 \text{ A} \\ & \bullet \text{I}_{\text{HS}[2:3]} = 0.75 \text{ A} \end{split}$ | -13<br>-16<br>-17<br>-20                                                 | -<br>-<br>-<br>-                                                        | 13<br>16<br>17<br>20                                                      | %    |       |

| C <sub>SR0_ACC</sub> (CAL)                          | HS[2,3] current recopy accuracy with one calibration point $ (6.0 \text{ V} \leq \text{V}_{\text{HS}[2:3]} \leq 20 \text{ V}) \\ \bullet \text{I}_{\text{HS}[2:3]} = 2.5 \text{ A} $                                                                                                                                                                                                                        | -5.0                                                                     | -                                                                       | 5.0                                                                       | %    | (20)  |

#### Notes

#### 10XS3425

<sup>18.</sup> Output OFF openload detection current is the current required to flow through the load for the purpose of detecting the existence of an open load condition when the specific output is commanded OFF. Pull-up current is measured for V<sub>HS</sub> = V<sub>OLD(THRES)</sub>

<sup>19.</sup> Current sense ratio = I<sub>CSNS</sub> / I<sub>HS[0:3]</sub>

<sup>20.</sup> Based on statistical analysis. It is not production tested.

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  20 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                      | Characteristic                                                                                                                                                                                                                                                                                | Min                  | Тур           | Max                  | Unit | Notes |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------|----------------------|------|-------|

| Outputs HS0                 | TO HS3 (continued)                                                                                                                                                                                                                                                                            |                      | I             |                      | ı    | .1    |

| $\Delta(C_{SR0})/\Delta(T)$ | HS[2,3] $C_{SR0}$ current recopy temperature drift (6.0 V $\leq$ V <sub>HS[2:3]</sub> $\leq$ 20 V) • I <sub>HS[2:3]</sub> = 2.5 A                                                                                                                                                             | -                    | _             | 0.04                 | %/°C | (21)  |

| C <sub>SR1_ACC</sub>        | $\begin{aligned} & \text{HS}[2,3] \text{ current sense ratio } (C_{SR1}) \text{ accuracy } (6.0 \text{ V} \leq \text{V}_{\text{HS}[2:3]} \leq 20 \text{ V}) \\ & \bullet \text{ I}_{\text{HS}[2:3]} = 6.25 \text{ A} \\ & \bullet \text{ I}_{\text{HS}[2:3]} = 18.75 \text{ A} \end{aligned}$ | -20<br>-18           | -<br>-        | +20<br>+18           | %    |       |

| C <sub>SR1_ACC</sub> (CAL)  | HS[2,3] current recopy accuracy with one calibration point $(6.0 \text{ V} \leq \text{V}_{\text{HS}[2:3]} \leq 20 \text{ V})$ • I <sub>HS[2:3]</sub> = 6.2 A                                                                                                                                  | -5.0                 | -             | 5.0                  | %    | (21)  |

| Control interf              | face                                                                                                                                                                                                                                                                                          |                      |               |                      |      |       |

| V <sub>IH</sub>             | Input logic high-voltage                                                                                                                                                                                                                                                                      | 2.0                  | -             | V <sub>DD</sub> +0.3 | V    | (22)  |

| V <sub>IL</sub>             | Input logic low-voltage                                                                                                                                                                                                                                                                       | -0.3                 | -             | 0.8                  | V    | (22)  |

| I <sub>DWN</sub>            | Input logic pull-down current (SCLK, SI)                                                                                                                                                                                                                                                      | 5.0                  | _             | 20                   | μΑ   | (25)  |

| I <sub>UP</sub>             | Input logic pull-up current (CSB)                                                                                                                                                                                                                                                             | 5.0                  | -             | 20                   | μΑ   | (26)  |

| C <sub>SO</sub>             | SO, FSB tri-state capacitance                                                                                                                                                                                                                                                                 | _                    | _             | 20                   | pF   | (23)  |

| R <sub>DWN</sub>            | Input logic pull-down resistor (RSTB, WAKE and IN[0:3])                                                                                                                                                                                                                                       | 125                  | 250           | 500                  | kΩ   |       |

| C <sub>IN</sub>             | Input capacitance                                                                                                                                                                                                                                                                             | _                    | 4.0           | 12                   | pF   | (23)  |

| V <sub>CL(WAKE)</sub>       | Wake input clamp voltage • I <sub>CL(WAKE)</sub> < 2.5 mA                                                                                                                                                                                                                                     | 18                   | 25            | 32                   | V    | (24)  |

| V <sub>F(WAKE)</sub>        | Wake input forward voltage • I <sub>CL(WAKE)</sub> = -2.5 mA                                                                                                                                                                                                                                  | -2.0                 | _             | -0.3                 | V    |       |

| V <sub>SOH</sub>            | SO high state output voltage • I <sub>OH</sub> = 1.0 mA                                                                                                                                                                                                                                       | V <sub>DD</sub> -0.4 | _             | _                    | V    |       |

| $V_{SOL}$                   | SO and FSB low state output voltage • I <sub>OL</sub> = -1.0 mA                                                                                                                                                                                                                               | _                    | _             | 0.4                  | V    |       |

| Control interf              | ace                                                                                                                                                                                                                                                                                           |                      |               |                      |      |       |

| I <sub>SO(LEAK)</sub>       | SO, CSNS and FSB tri-state leakage current<br>• CSB = $V_{IH}$ and 0.0 V $\leq$ $V_{SO} \leq$ $V_{DD}$ , or FSB = 5.5 V, or CSNS = 0.0 V                                                                                                                                                      | -2.0                 | 0             | 2.0                  | μА   |       |

| RFS                         | FSI external pull-down resistance Watchdog disabled Watchdog enabled                                                                                                                                                                                                                          | -<br>10              | 0<br>Infinite | 1.0<br>_             | kΩ   | (27)  |

#### Notes

- 21. Based on statistical analysis. It is not production tested.

- 22. Upper and lower logic threshold voltage range applies to SI, CSB, SCLK, RSTB, IN[0:3], and WAKE input signals. The WAKE and RSTB signals may be supplied by a derived voltage referenced to V<sub>PWR</sub>.

- 23. Input capacitance of SI, CSB, SCLK, RSTB, IN[0:3], and WAKE. This parameter is guaranteed by process monitoring but is not production tested.

- 24. The current must be limited by a series resistance when using voltages > 7.0 V.

- 25. Pull-down current is with  $V_{SI} \ge 1.0 \text{ V}$  and  $V_{SCLK} \ge 1.0 \text{ V}$ .

- 26. Pull-up current is with  $V_{CSB} \le 2.0 \text{ V}$ . CSB has an active internal pull-up to  $V_{DD}$ .

- 27. In Fail-safe, HS[0:3] depends respectively on ON[0:3]. FSI has an active internal pull-up to  $V_{REG} \cong 3.0 \text{ V}$ .

10XS3425

# 4.3 Dynamic electrical characteristics

#### Table 5. Dynamic electrical characteristics

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  20 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol               | Characteristic                                                                                                                                                                                           | Min | Тур  | Max  | Unit  | Notes     |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|-------|-----------|

| ower outpu           | ut timing HS0 TO HS3                                                                                                                                                                                     |     | I.   |      |       | 1         |

| SR <sub>R00</sub>    | HS[0,1] output rising medium slew rate (medium speed slew rate / SR[1:0] = 00)                                                                                                                           | 300 | 650  | 1200 | mV/μs |           |

| SR <sub>F00</sub>    | HS[0,1] output falling medium slew rate (medium speed slew rate / SR[1:0] = 00)                                                                                                                          | 300 | 720  | 1200 | mV/μs |           |

| DS <sub>R_00</sub>   | HS[0,1] driver output matching slew rate (SRR /SRF)  • PWR = 14 V at 25 °C and for medium speed slew rate (SR[1:0] = 00)                                                                                 | 0.8 | 0.9  | 1.2  |       |           |

| SR <sub>R01</sub>    | HS[0,1] output rising slow slew rate (slow speed slew rate / SR[1:0] = 01)                                                                                                                               | 150 | 330  | 600  | mV/μs |           |

| SR <sub>F01</sub>    | HS[0,1] output falling slow slew rate (slow speed slew rate / SR[1:0] = 01)                                                                                                                              | 150 | 370  | 600  | mV/μs |           |

| SR <sub>R10</sub>    | HS[0,1] output rising fast slew rate (fast speed slew rate / SR[1:0] = 10)                                                                                                                               |     | 1250 | 2400 | mV/μs |           |

| SR <sub>F10</sub>    | HS[0,1] output falling fast slew rate (fast speed slew rate / SR[1:0] = 10)                                                                                                                              | 600 | 1450 | 2400 | mV/μs |           |

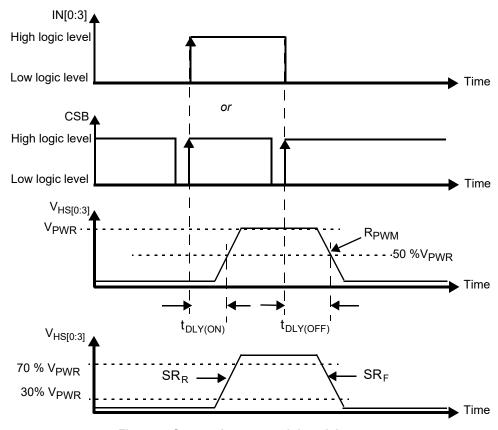

| t <sub>DLY_ON</sub>  | HS[0:1] outputs turn-on delay time  • VPWR = 14 for medium speed slew rate (SR[1:0] = 00)                                                                                                                |     | 64   | 100  | μs    | (28),(29) |

| t <sub>DLY_OFF</sub> | HS[0:1] outputs turn-off delay time  • VPWR = 14 for medium speed slew rate (SR[1:0] = 00)                                                                                                               | 10  | 32   | 60   | μs    | (28),(29) |

| $\Delta t_{RF}$      | HS[0:1] driver output matching time (t <sub>DLY(ON)</sub> - t <sub>DLY(OFF)</sub> )  • VPWR = 14 V, f <sub>PWM</sub> = 240 Hz, PWM duty cycle = 50 %, at 25 °C for medium speed slew rate (SR[1:0] = 00) | 10  | 32   | 60   | μs    | (28),(29) |

| SR <sub>R00</sub>    | HS[2,3] output rising medium slew rate (medium speed slew rate / SR[1:0] = 00)                                                                                                                           | 200 | 470  | 800  | mV/μs |           |

| SR <sub>F00</sub>    | HS[2,3] output falling medium slew rate (medium speed slew rate / SR[1:0] = 00)                                                                                                                          | 200 | 570  | 800  | mV/μs |           |

| DS <sub>R_00</sub>   | HS[2,3] driver output matching slew rate (SRR /SRF)  • VPWR = 14 V at 25 °C and for medium speed slew rate (SR[1:0] = 00)                                                                                | 0.6 | 0.8  | 1.0  |       |           |

| SR <sub>R01</sub>    | HS[2,3] output rising slow slew rate (slow speed slew rate / SR[1:0] = 01)                                                                                                                               | 100 | 230  | 400  | mV/μs |           |

| SR <sub>F01</sub>    | HS[2,3] output falling slow slew rate (slow speed slew rate / SR[1:0] = 10)                                                                                                                              | 100 | 300  | 400  | mV/μs |           |

#### Notes

10XS3425

<sup>28.</sup> Turn ON delay time measured from rising edge of any signal (IN[0:3] and CSB) that would turn the output ON to  $V_{HS[0:3]} = V_{PWR} / 2$  with  $R_L = 5.0 \Omega$  resistive load.

<sup>29.</sup> Turn OFF delay time measured from falling edge of any signal (IN[0:3] and CSB) that would turn the output OFF to  $V_{HS[0:3]} = V_{PWR} / 2$  with  $R_L = 5.0 \Omega$  resistive load.

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  20 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol               | Characteristic                                                                                                                                                                  | Min | Тур               | Max     | Unit  | Notes |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------|---------|-------|-------|

| Power output         | t timing HS0 TO HS3 (Continued)                                                                                                                                                 |     | '                 |         | l.    | u u   |

| SR <sub>R10</sub>    | HS[2,3] output rising fast slew rate (fast speed slew rate / SR[1:0] = 10)                                                                                                      | 400 | 900               | 1600    | mV/μs |       |

| SR <sub>F10</sub>    | HS[2,3] output falling fast slew rate (fast speed slew rate / SR[1:0] = 10)                                                                                                     | 400 | 1140              | 1600    | mV/μs |       |

| t <sub>DLY_ON</sub>  | HS[2,3] outputs turn-on delay time  • VPWR = 14 V for medium speed slew rate (SR[1:0] = 00)                                                                                     |     | 87                | 160     | μs    |       |

| t <sub>DLY_OFF</sub> | HS[2,3] outputs turn-off delay time  • VPWR = 14 V for medium speed slew rate (SR[1:0] = 00)                                                                                    |     | 36                | 65      | μs    |       |

| $\Delta t_{RF}$      | HS[2,3] driver output matching time (tDLY(ON) - tDLY(OFF))  • VPWR = 14 V, f <sub>PWM</sub> = 240 Hz, PWM duty cycle = 50 %, at 25 °C for medium speed slew rate (SR[1:0] = 00) |     | 51                | 110     | μs    |       |

| t <sub>FAULT</sub>   | Fault detection blanking time                                                                                                                                                   | 1.0 | 5.0               | 20      | μs    | (30)  |

| t <sub>DETECT</sub>  | Output shutdown delay time                                                                                                                                                      | _   | 7.0               | 30      | μs    | (31)  |

| t <sub>CNSVAL</sub>  | CSNS valid time                                                                                                                                                                 | _   | 70                | 100     | μs    | (32)  |

| t <sub>WDTO</sub>    | Watchdog timeout                                                                                                                                                                |     | 310               | 400     | ms    | (33)  |

| T <sub>OLLED</sub>   | ON openload fault cyclic detection period with LED  • Internal clock (PWM_en bit = 1 & CLOCK_Set = 1)  • External clock (PWM_en bit = 1 & CLOCK_Set = 0)                        |     | 8.3<br>PWM period | 12<br>- | ms    |       |

#### Notes

- 30. Time necessary to report the fault to FSB pin.

- 31. Time necessary to switch-off the output in case of OT, or OC, or SC, or UV fault detection (from negative edge of FSB pin to HS voltage = 50 % of  $V_{PWR}$ .

- 32. Time necessary for CSNS to be within  $\pm 5.0$  % of the targeted value (from HS voltage = 50 % of  $V_{PWR}$  to  $\pm 5.0$  % of the targeted CSNS value).

- 33. For FSI open, the watchdog timeout delay measured from the rising edge of RST, to HS[0,2] output state depends on the corresponding input command.

Table 5. Dynamic electrical characteristics (continued)

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  20 V, 3.0 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, GND = 0 V, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol              | Characteristic                                     | Min   | Тур      | Max      | Unit | Notes |

|---------------------|----------------------------------------------------|-------|----------|----------|------|-------|

| wer outpu           | tt timing HS0 TO HS3 (continued)                   |       | <u>I</u> | <u> </u> | ı    | 1     |

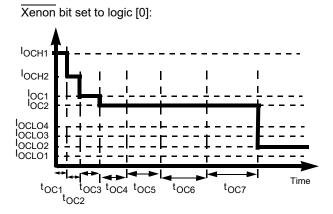

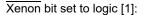

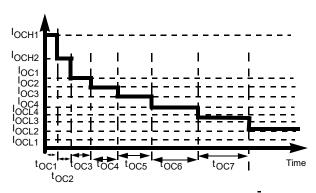

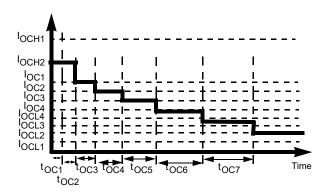

|                     | HS[0,1] output overcurrent time step               |       |          |          |      |       |

|                     | <ul> <li>OC[1:0] = 00 (slow by default)</li> </ul> |       |          |          |      |       |

| t <sub>OC1_00</sub> |                                                    | 4.40  | 6.30     | 8.02     |      |       |

| t <sub>OC2_00</sub> |                                                    | 1.62  | 2.32     | 3.00     |      |       |

| t <sub>OC3_00</sub> |                                                    | 2.10  | 3.00     | 3.90     |      |       |

| t <sub>OC4_00</sub> |                                                    | 2.88  | 4.12     | 5.36     |      |       |

| t <sub>OC5_00</sub> |                                                    | 4.58  | 6.56     | 8.54     |      |       |

| t <sub>OC6_00</sub> |                                                    | 10.16 | 14.52    | 18.88    |      |       |

| t <sub>OC7_00</sub> |                                                    | 73.2  | 104.6    | 134.0    |      |       |

|                     | • OC[1:0] = 01 (fast)                              |       |          |          |      |       |

| t <sub>OC1_01</sub> |                                                    | 1.10  | 1.57     | 2.00     |      |       |

| t <sub>OC2_01</sub> |                                                    | 0.40  | 0.58     | 0.75     |      |       |

| t <sub>OC3_01</sub> |                                                    | 0.52  | 0.75     | 0.98     |      |       |

| t <sub>OC4_01</sub> |                                                    | 0.72  | 1.03     | 1.34     |      |       |

| t <sub>OC5_01</sub> |                                                    | 1.14  | 1.64     | 2.13     |      |       |

| t <sub>OC6_01</sub> |                                                    | 2.54  | 3.63     | 4.72     |      |       |

| t <sub>OC7_01</sub> |                                                    | 18.2  | 26.1     | 34.0     | ms   |       |

| 000.                | • OC[1:0] = 10 (medium)                            |       |          |          |      |       |

| t <sub>OC1_10</sub> |                                                    | 2.20  | 3.15     | 4.01     |      |       |

| t <sub>OC2_10</sub> |                                                    | 0.81  | 1.16     | 1.50     |      |       |

| t <sub>OC3_10</sub> |                                                    | 1.05  | 1.50     | 1.95     |      |       |

| t <sub>OC4_10</sub> |                                                    | 1.44  | 2.06     | 2.68     |      |       |

| t <sub>OC5_10</sub> |                                                    | 2.29  | 3.28     | 4.27     |      |       |

| t <sub>OC6_10</sub> |                                                    | 5.08  | 7.26     | 9.44     |      |       |

| t <sub>OC7_10</sub> |                                                    | 36.6  | 52.3     | 68.0     |      |       |

| 501_10              | • OC[1:0] = 11 (very slow)                         |       |          |          |      |       |

| t <sub>OC1_11</sub> |                                                    | 8.8   | 12.6     | 16.4     |      |       |

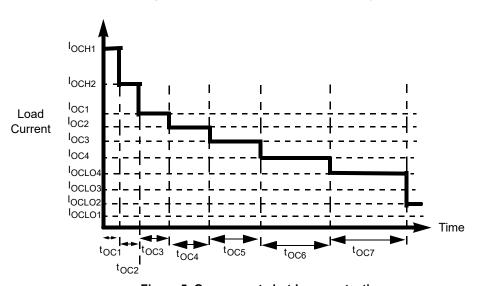

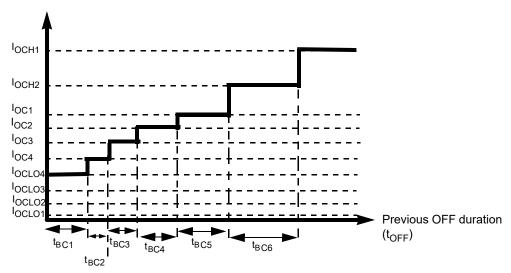

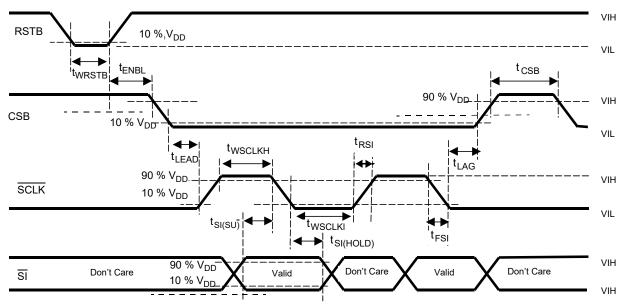

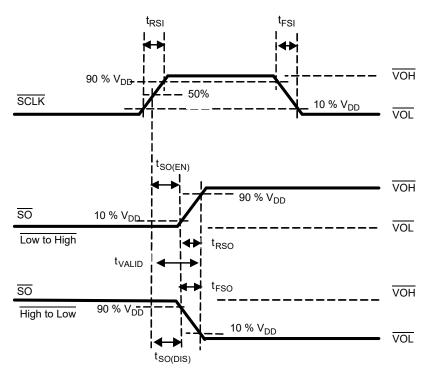

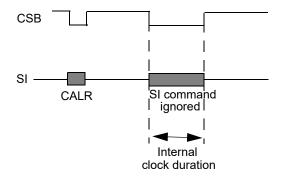

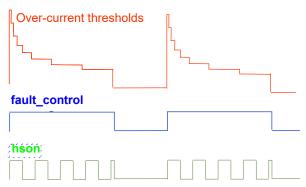

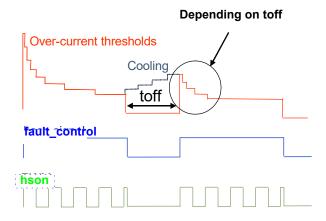

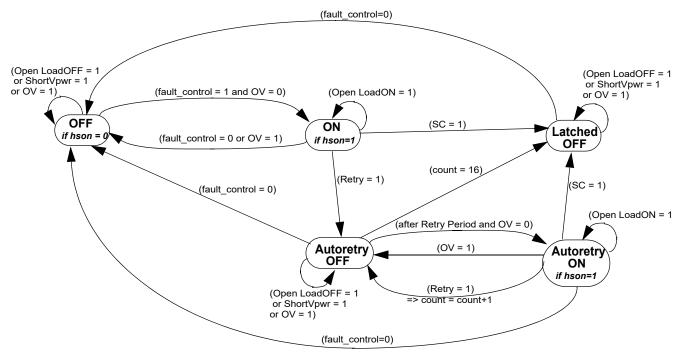

| t <sub>OC2_11</sub> |                                                    | 3.2   | 4.6      | 21.4     |      |       |